Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 11                                                                          |

| Program Memory Size        | 1.5KB (1K x 12)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 72 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c505t-20i-sl |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE OF CONTENTS

| 1.0   | General Description                    | 3  |

|-------|----------------------------------------|----|

| 2.0   | PIC16C505 Device Varieties             |    |

| 3.0   | Architectural Overview                 | 7  |

| 4.0   | Memory Organization                    |    |

|       | I/O Port                               |    |

| 6.0   | Timer0 Module and TMR0 Register        | 23 |

| 7.0   | Special Features of the CPU            | 27 |

| 8.0   | Instruction Set Summary                | 39 |

| 9.0   | Development Support.                   | 51 |

| 10.0  | Electrical Characteristics - PIC16C505 | 55 |

| 11.0  | DC and AC Characteristics - PIC16C505  | 69 |

| 12.0  | Packaging Information                  | 73 |

| PIC16 | C505 Product Identification System     | 87 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1). The Special Function Registers can be classified into two sets. The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

| Address            | Name   | Bit 7         | Bit 6        | Bit 5      | Bit 4       | Bit 3       | Bit 2        | Bit 1  | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets <sup>(2)</sup> |

|--------------------|--------|---------------|--------------|------------|-------------|-------------|--------------|--------|-------|-------------------------------|------------------------------------------------|

| 00h                | INDF   | Uses conte    | nts of FSF   | to addres  | s data me   | mory (not a | physical reg | ister) |       | xxxx xxxx                     | uuuu uuuu                                      |

| 01h                | TMR0   | 8-bit real-ti | me clock/c   | ounter     |             |             |              |        |       | xxxx xxxx                     | uuuu uuuu                                      |

| 02h <sup>(1)</sup> | PCL    | Low order     | B bits of PC | C          |             |             |              |        |       | 1111 1111                     | 1111 1111                                      |

| 03h                | STATUS | RBWUF         | _            | PAO        | TO          | PD          | Z            | DC     | С     | 0001 1xxx                     | q00q quuu <sup>(1)</sup>                       |

| 04h                | FSR    | Indirect dat  | a memory     | address p  | ointer      |             |              |        |       | 110x xxxx                     | 11uu uuuu                                      |

| 05h                | OSCCAL | CAL5          | CAL4         | CAL3       | CAL2        | CAL1        | CAL0         | _      | _     | 1000 00                       | uuuu uu                                        |

| N/A                | TRISB  | —             |              | I/O contro | l registers |             |              |        |       | 11 1111                       | 11 1111                                        |

| N/A                | TRISC  | —             |              | I/O contro | l registers |             |              |        |       | 11 1111                       | 11 1111                                        |

| N/A                | OPTION | RBWU          | RBPU         | TOCS       | TOSE        | PSA         | PS2          | PS1    | PS0   | 1111 1111                     | 1111 1111                                      |

| 06h                | PORTB  | —             |              | RB5        | RB4         | RB3         | RB2          | RB1    | RB0   | xx xxxx                       | uu uuuu                                        |

| 07h                | PORTC  | —             |              | RC5        | RC4         | RC3         | RC2          | RC1    | RC0   | xx xxxx                       | uu uuuu                                        |

# TABLE 4-1:SPECIAL FUNCTION REGISTER (SFR) SUMMARY

Legend: Shaded cells not used by Port Registers, read as '0', — = unimplemented, read as '0', x = unknown, u = unchanged, q = depends on condition.

Note 1: If reset was due to wake-up on pin change, then bit 7 = 1. All other rests will cause bit 7 = 0.

Note 2: Other (non-power-up) resets include external reset through MCLR, watchdog timer and wake-up on pin change reset.

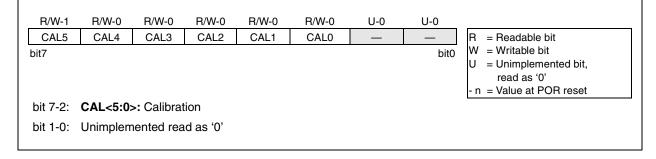

#### 4.5 OSCCAL Register

The Oscillator Calibration (OSCCAL) register is used to calibrate the internal 4 MHz oscillator. It contains six bits for calibration

| Note: | Please note that erasing the device will       |

|-------|------------------------------------------------|

|       | also erase the pre-programmed internal         |

|       | calibration value for the internal oscillator. |

|       | The calibration value must be read prior to    |

|       | erasing the part, so it can be repro-          |

|       | grammed correctly later.                       |

After you move in the calibration constant, do not change the value. See Section 7.2.5

#### REGISTER 4-3: OSCCAL REGISTER (ADDRESS 05h) PIC16C505

# TABLE 5-1: SUMMARY OF PORT REGISTERS

| Address | Name   | Bit 7 | Bit 6 | Bit 5      | Bit 4                | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other Resets |

|---------|--------|-------|-------|------------|----------------------|-------|-------|-------|-------|-------------------------------|------------------------------|

| N/A     | TRISB  | —     | _     | I/O contro | /O control registers |       |       |       |       | 11 1111                       | 11 1111                      |

| N/A     | TRISC  | —     | _     | I/O contro | l registers          |       |       |       |       | 11 1111                       | 11 1111                      |

| N/A     | OPTION | RBWU  | RBPU  | TOCS       | TOSE                 | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                    |

| 03h     | STATUS | RBWUF | _     | PAO        | TO                   | PD    | Z     | DC    | С     | 0001 1xxx                     | q00q quuu <sup>(1)</sup>     |

| 06h     | PORTB  | —     | —     | RB5        | RB4                  | RB3   | RB2   | RB1   | RB0   | xx xxxx                       | uu uuuu                      |

| 07h     | PORTC  |       |       | RC5        | RC4                  | RC3   | RC2   | RC1   | RC0   | xx xxxx                       | uu uuuu                      |

Legend: Shaded cells not used by Port Registers, read as '0', — = unimplemented, read as '0', x = unknown, u = unchanged, q = depends on condition.

Note 1: If reset was due to wake-up on pin change, then bit 7 = 1. All other rests will cause bit 7 = 0.

#### 5.5 I/O Programming Considerations

#### 5.5.1 BI-DIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU, bit5 to be set and the PORTB value to be written to the output latches. If another bit of PORTB is used as a bidirectional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}\,,~{\tt BSF},$  etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wiredand"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

; Initial PORTB Settings ; PORTB<5:3> Inputs ; PORTB<2:0> Outputs ; ; PORTB latch PORTB pins -----; BCF ;--01 -ppp --11 pppp PORTB, 5 BCF PORTB, 4 ;--10 -ppp --11 pppp MOVLW 007h ;

TRIS PORTB

; ;Note that the user may have expected the pin ;values to be --00 pppp. The 2nd BCF caused ;RB5 to be latched as the pin value (High).

;--10 -ppp

--11 pppp

#### 5.5.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction causes that file to be read into the CPU. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

# 6.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Edge select for external clock

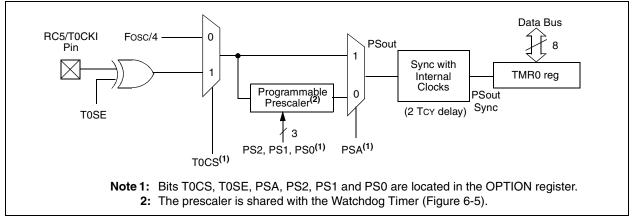

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the TOCS bit (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1.

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. Section 6.2 details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

#### FIGURE 6-1: TIMER0 BLOCK DIAGRAM

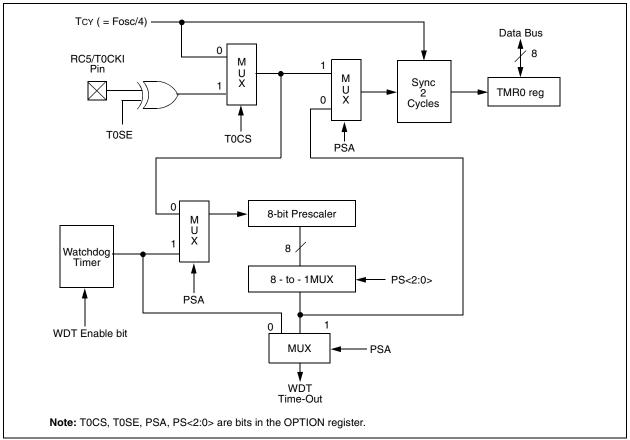

#### 6.2 **Prescaler**

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer (WDT), respectively (Section 7.6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMRO register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a RESET, the prescaler contains all '0's.

#### 6.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device

RESET, following instruction the sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

|          | •           | ,                        |

|----------|-------------|--------------------------|

| 1.CLRWDT |             | ;Clear WDT               |

| 2.CLRF   | TMR0        | ;Clear TMR0 & Prescaler  |

| 3.MOVLW  | '00xx1111'b | ;These 3 lines (5, 6, 7) |

| 4.OPTION |             | ; are required only if   |

|          |             | ; desired                |

| 5.CLRWDT |             | ;PS<2:0> are 000 or 001  |

| 6.MOVLW  | '00xx1xxx'b | ;Set Postscaler to       |

| 7.OPTION |             | ; desired WDT rate       |

|          |             |                          |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

#### EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

|        | (**        |                     |

|--------|------------|---------------------|

| CLRWDT |            | ;Clear WDT and      |

|        |            | ;prescaler          |

| MOVLW  | 'xxxx0xxx' | ;Select TMR0, new   |

|        |            | ;prescale value and |

|        |            | ;clock source       |

|        |            |                     |

OPTION

#### **BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER** FIGURE 6-5:

#### 7.2.5 INTERNAL 4 MHz RC OSCILLATOR

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at VDD = 5V and  $25^{\circ}C$ , see Electrical Specifications section for information on variation over voltage and temperature.

In addition, a calibration instruction is programmed into the last address of memory, which contains the calibration value for the internal RC oscillator. This location is always protected, regardless of the code protect settings. This value is programmed as a MOVLW XX instruction where XX is the calibration value, and is placed at the reset vector. This will load the W register with the calibration value upon reset and the PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

**Note:** Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be read prior to erasing the part so it can be reprogrammed correctly later.

For the PIC16C505, only bits <7:2> of OSCCAL are implemented.

#### 7.3 <u>RESET</u>

The device differentiates between various kinds of reset:

- a) Power on reset (POR)

- b) MCLR reset during normal operation

- c) MCLR reset during SLEEP

- d) WDT time-out reset during normal operation

- e) WDT time-out reset during SLEEP

- f) Wake-up from SLEEP on pin change

Some registers are not reset in any way, they are unknown on POR and unchanged in any other reset. Most other registers are reset to "reset state" on poweron reset (POR), MCLR, WDT or wake-up on pin change reset during normal operation. They are not affected by a WDT reset during SLEEP or MCLR reset during SLEEP, since these resets are viewed as resumption of normal operation. The exceptions to this are TO, PD and RBWUF bits. They are set or cleared differently in different reset situations. These bits are used in software to determine the nature of reset. See Table 7-3 for a full description of reset states of all registers.

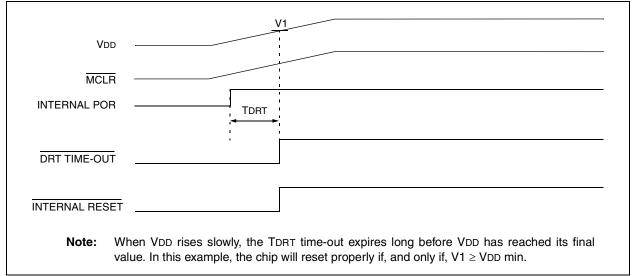

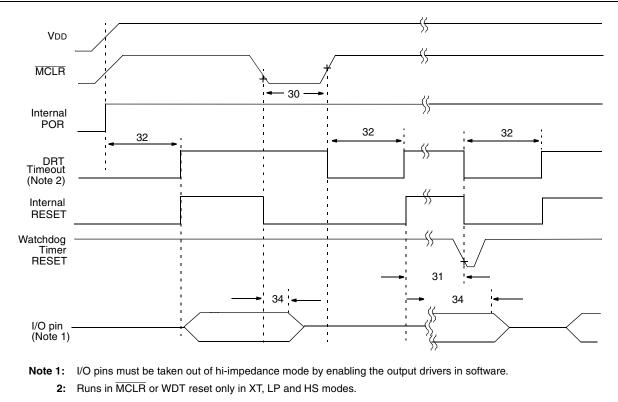

#### FIGURE 7-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

#### 7.5 Device Reset Timer (DRT)

In the PIC16C505, the DRT runs any time the device is powered up. DRT runs from RESET and varies based on oscillator selection and reset type (see Table 7-5).

The DRT operates on an internal RC oscillator. The processor is kept in RESET as long as the DRT is active. The DRT delay allows VDD to rise above VDD min. and for the oscillator to stabilize.

Oscillator circuits based on crystals or ceramic resonators require a certain time after power-up to establish a stable oscillation. The on-chip DRT keeps the device in a RESET condition for approximately 18 ms after MCLR has reached a logic high (VIHMCLR) level. Thus, programming RB3/MCLR/VPP as MCLR and using an external RC network connected to the MCLR input is not required in most cases, allowing for savings in cost-sensitive and/or space restricted applications, as well as allowing the use of the RB3/MCLR/VPP pin as a general purpose input.

The Device Reset time delay will vary from chip to chip due to VDD, temperature and process variation. See AC parameters for details.

The DRT will also be triggered upon a Watchdog Timer time-out. This is particularly important for applications using the WDT to wake from SLEEP mode automatically.

Reset sources are POR, MCLR, WDT time-out and Wake-up on pin change. (See Section 7.9.2, Notes 1, 2, and 3, page 37.)

#### 7.6 <u>Watchdog Timer (WDT)</u>

The Watchdog Timer (WDT) is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the external RC oscillator of the RB5/OSC1/CLKIN pin and the internal 4 MHz oscillator. That means that the WDT will run even if the main processor clock has been stopped, for example, by execution of a SLEEP instruction. During normal operation or SLEEP, a WDT reset or wake-up reset generates a device RESET.

The  $\overline{\text{TO}}$  bit (STATUS<4>) will be cleared upon a Watchdog Timer reset.

The WDT can be permanently disabled by programming the configuration bit WDTE as a '0' (Section 7.1). Refer to the PIC16C505 Programming Specifications to determine how to access the configuration word.

TABLE 7-5: DRT (DEVICE RESET TIMER PERIOD)

| ,                           |                 |                      |  |  |  |  |  |  |  |

|-----------------------------|-----------------|----------------------|--|--|--|--|--|--|--|

| Oscillator<br>Configuration | POR Reset       | Subsequent<br>Resets |  |  |  |  |  |  |  |

| IntRC &<br>ExtRC            | 18 ms (typical) | 300 μs<br>(typical)  |  |  |  |  |  |  |  |

| HS, XT & LP                 | 18 ms (typical) | 18 ms (typical)      |  |  |  |  |  |  |  |

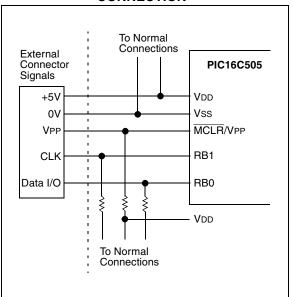

#### 7.12 In-Circuit Serial Programming

The PIC16C505 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB1 and RB0 pins low while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see programming specification). RB1 becomes the programming clock and RB0 becomes the programming data. Both RB1 and RB0 are Schmitt Trigger inputs in this mode.

After reset, a 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C505 Programming Specifications.

A typical in-circuit serial programming connection is shown in Figure 7-15.

#### FIGURE 7-15: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| INCF                                                    | Increment f                                                                                                                                                            |  |  |  |  |  |  |  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                                                 | [label] INCF f,d                                                                                                                                                       |  |  |  |  |  |  |  |

| Operands:                                               | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |  |  |

| Operation:                                              | (f) + 1 $\rightarrow$ (dest)                                                                                                                                           |  |  |  |  |  |  |  |

| Status Affected:                                        | Z                                                                                                                                                                      |  |  |  |  |  |  |  |

| Encoding:                                               | 0010 10df ffff                                                                                                                                                         |  |  |  |  |  |  |  |

| Description:                                            | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in register<br>'f'. |  |  |  |  |  |  |  |

| Words:                                                  | 1                                                                                                                                                                      |  |  |  |  |  |  |  |

| Cycles:                                                 | 1                                                                                                                                                                      |  |  |  |  |  |  |  |

| Example:                                                | INCF CNT, 1                                                                                                                                                            |  |  |  |  |  |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0xFF<br>= 0                                                                                                                                                          |  |  |  |  |  |  |  |

|                     | Increment f, Skip if 0                                                                                                                                                 |  |  |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:             | [label] INCFSZ f,d                                                                                                                                                     |  |  |  |  |  |

| Operands:           | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |

| Operation:          | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                       |  |  |  |  |  |

| Status Affected:    | None                                                                                                                                                                   |  |  |  |  |  |

| Encoding:           | 0011 11df ffff                                                                                                                                                         |  |  |  |  |  |

| Description:        | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in register<br>'f'. |  |  |  |  |  |

|                     | If the result is 0, then the next<br>instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a two<br>cycle instruction.     |  |  |  |  |  |

| Words:              | 1                                                                                                                                                                      |  |  |  |  |  |

| Cycles:             | 1(2)                                                                                                                                                                   |  |  |  |  |  |

| Example:            | HERE INCFSZ CNT, 1<br>GOTO LOOP                                                                                                                                        |  |  |  |  |  |

|                     | CONTINUE •                                                                                                                                                             |  |  |  |  |  |

|                     | uction                                                                                                                                                                 |  |  |  |  |  |

| Before Instru       |                                                                                                                                                                        |  |  |  |  |  |

| Before Instru<br>PC | = address (HERE)                                                                                                                                                       |  |  |  |  |  |

# 9.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>®</sup> for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

# 9.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

# 9.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 9.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

# 9.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

# 9.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 9.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

# 9.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 9.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 9.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 9.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

# 9.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

# 9.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

# 9.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 10.1 DC CHARACTERISTICS:

#### PIC16C505-04 (Commercial, Industrial, Extended) PIC16C505-20(Commercial, Industrial, Extended)

Standard Operating Co Operating Temperature

Standard Operating Conditions (unless otherwise specified) Operating Temperature  $0^{\circ}C \le TA \le +70^{\circ}C$  (commercial)

DC Characteristics Power Supply Pins  $0^{\circ}C \le TA \le +70^{\circ}C$  (commercial) -40^{\circ}C \le TA \le +85^{\circ}C (industrial)

$-40^{\circ}C \le TA \le +125^{\circ}C$  (extended)

| Parm.<br>No. | Characteristic                                                  | Sym   | Min   | Typ <sup>(1)</sup>          | Max                         | Units                      | Conditions                                                                                                                                                                                                                                |

|--------------|-----------------------------------------------------------------|-------|-------|-----------------------------|-----------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D001         | Supply Voltage                                                  | Vdd   | 3.0   |                             | 5.5                         | V                          | See Figure 10-1 through Figure 10-3                                                                                                                                                                                                       |

| D002         | RAM Data Retention<br>Voltage <sup>(2)</sup>                    | Vdr   | _     | 1.5*                        | _                           | V                          | Device in SLEEP mode                                                                                                                                                                                                                      |

| D003         | VDD Start Voltage to ensure<br>Power-on Reset                   | VPOR  | —     | Vss                         | —                           | V                          | See section on Power-on Reset for details                                                                                                                                                                                                 |

| D004         | VDD Rise Rate to ensure<br>Power-on Reset                       | SVDD  | 0.05* | —                           | —                           | V/ms                       | See section on Power-on Reset for details                                                                                                                                                                                                 |

| D010         | Supply Current <sup>(3)</sup>                                   | IDD   | <br>  | 0.8<br>0.6<br>3<br>4<br>4.5 | 1.4<br>1.0<br>7<br>12<br>16 | mA<br>mA<br>mA<br>mA<br>mA | Fosc = 4MHz, VDD = 5.5V, WDT disabled (Note 4)*<br>Fosc = 4MHz, VDD = 3.0V, WDT disabled (Note 4)<br>Fosc = 10MHz, VDD = 3.0V, WDT disabled (Note 6)<br>Fosc = 20MHz, VDD = 4.5V, WDT disabled<br>Fosc = 20MHz, VDD = 5.5V, WDT disabled* |

|              |                                                                 |       | —     | 19                          | 27                          | μA                         | Fosc = 32kHz, VDD = 3.0V, WDT disabled (Note 6)                                                                                                                                                                                           |

| D020         | Power-Down Current <sup>(5)</sup>                               | IPD   |       | 0.25<br>0.4<br>3<br>5       | 4<br>5.5<br>8<br>14         | μΑ<br>μΑ<br>μΑ<br>μΑ       | VDD = 3.0V (Note 6)<br>$VDD = 4.5V^* (Note 6)$<br>VDD = 5.5V, Industrial<br>VDD = 5.5V, Extended Temp.                                                                                                                                    |

| D022         | WDT Current <sup>(5)</sup>                                      | ΔIWDT | _     | 2.2                         | 5                           | μA                         | VDD = 3.0V (Note 6)                                                                                                                                                                                                                       |

| 1A           | LP Oscillator Operating<br>Frequency<br>RC Oscillator Operating | Fosc  | 0     | _                           | 200                         | kHz                        | All temperatures                                                                                                                                                                                                                          |

|              | Frequency<br>XT Oscillator Operating                            |       | 0     | _                           | 4                           | MHz                        | All temperatures                                                                                                                                                                                                                          |

|              | Frequency<br>HS Oscillator Operating                            |       | 0     | _                           | 4                           | MHz                        | All temperatures                                                                                                                                                                                                                          |

|              | Frequency                                                       |       | 0     |                             | 20                          | MHz                        | All temperatures                                                                                                                                                                                                                          |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

**3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, TOCKI = VDD,  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

4: Does not include current through Rext. The current through the resistor can be estimated by the formula: IR = VDD/2Rext (mA) with Rext in kOhm.

5: The power down current in SLEEP mode does not depend on the oscillator type. Power down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

6: Commercial temperature range only.

| VDD (Volts) | Temperature (°C) | Min   | Тур    | Max  | Units |

|-------------|------------------|-------|--------|------|-------|

|             |                  | RB0/R | B1/RB4 |      |       |

| 2.5         | -40              | 38K   | 42K    | 63K  | W     |

|             | 25               | 42K   | 48K    | 63K  | W     |

|             | 85               | 42K   | 49K    | 63K  | W     |

|             | 125              | 50K   | 55K    | 63K  | W     |

| 5.5         | -40              | 15K   | 17K    | 20K  | W     |

|             | 25               | 18K   | 20K    | 23K  | W     |

|             | 85               | 19K   | 22K    | 25K  | W     |

|             | 125              | 22K   | 24K    | 28K  | W     |

|             |                  | R     | B3     |      |       |

| 2.5         | -40              | 285K  | 346K   | 417K | W     |

|             | 25               | 343K  | 414K   | 532K | W     |

|             | 85               | 368K  | 457K   | 532K | W     |

|             | 125              | 431K  | 504K   | 593K | W     |

| 5.5         | -40              | 247K  | 292K   | 360K | W     |

|             | 25               | 288K  | 341K   | 437K | W     |

|             | 85               | 306K  | 371K   | 448K | W     |

|             | 125              | 351K  | 407K   | 500K | W     |

# TABLE 10-1: PULL-UP RESISTOR RANGES - PIC16C505

\* These parameters are characterized but not tested.

#### FIGURE 10-7: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16C505

#### TABLE 10-5: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C505

| AC Characteristics |      | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^\circ C \leq TA \leq +70^\circ C \mbox{ (commercial)} \\ & -40^\circ C \leq TA \leq +85^\circ C \mbox{ (industrial)} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ (extended)} \\ \mbox{Operating Voltage VDD range is described in Section 10.1} \end{array}$ |       |                    |       |       |                          |  |  |

|--------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|-------|-------|--------------------------|--|--|

| Parameter<br>No.   | Sym  | Characteristic                                                                                                                                                                                                                                                                                                                                                                              | Min   | Typ <sup>(1)</sup> | Мах   | Units | Conditions               |  |  |

| 30                 | TmcL | MCLR Pulse Width (low)                                                                                                                                                                                                                                                                                                                                                                      | 2000* |                    | —     | ns    | VDD = 5.0 V              |  |  |

| 31                 | Twdt | Watchdog Timer Time-out Period<br>(No Prescaler)                                                                                                                                                                                                                                                                                                                                            | 9*    | 18*                | 30*   | ms    | VDD = 5.0 V (Commercial) |  |  |

| 32                 | Tdrt | Device Reset Timer Period(2)                                                                                                                                                                                                                                                                                                                                                                | 9*    | 18*                | 30*   | ms    | VDD = 5.0 V (Commercial) |  |  |

| 34                 | Tioz | I/O Hi-impedance from MCLR Low                                                                                                                                                                                                                                                                                                                                                              | _     | _                  | 2000* | ns    |                          |  |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### TABLE 10-6: DRT (DEVICE RESET TIMER PERIOD - PIC16C505

| Oscillator Configuration | POR Reset       | Subsequent Resets |  |  |

|--------------------------|-----------------|-------------------|--|--|

| IntRC & ExtRC            | 18 ms (typical) | 300 μs (typical)  |  |  |

| XT, HS & LP              | 18 ms (typical) | 18 ms (typical)   |  |  |

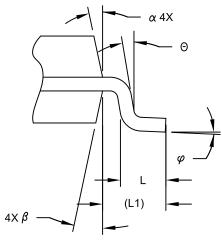

# 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW C

|                          | MILLIMETERS |          |     |      |  |  |

|--------------------------|-------------|----------|-----|------|--|--|

| Dimension Lir            | MIN         | NOM      | MAX |      |  |  |

| Number of Pins           | N           |          | 14  |      |  |  |

| Pitch                    | е           | 1.27 BSC |     |      |  |  |

| Overall Height           | А           |          |     | 1.75 |  |  |

| Molded Package Thickness | A2          | 1.25     | -   | -    |  |  |

| Standoff §               | A1          | 0.10     | -   | 0.25 |  |  |

| Overall Width            | E           | 6.00 BSC |     |      |  |  |

| Molded Package Width     | E1          | 3.90 BSC |     |      |  |  |

| Overall Length           | D           | 8.65 BSC |     |      |  |  |

| Chamfer (Optional)       | h           | 0.25     | -   | 0.50 |  |  |

| Foot Length              | L           | 0.40     | -   | 1.27 |  |  |

| Footprint                | L1          | 1.04 REF |     |      |  |  |

| Lead Angle               | Θ           | 0°       | -   | -    |  |  |

| Foot Angle               | φ           | 0°       | -   | 8°   |  |  |

| Lead Thickness           | С           | 0.10     | -   | 0.25 |  |  |

| Lead Width               | b           | 0.31     | -   | 0.51 |  |  |

| Mold Draft Angle Top     | α           | 5°       | -   | 15°  |  |  |

| Mold Draft Angle Bottom  | β           | 5°       | -   | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2

# PIC18F66K80 FAMILY

NOTES:

NOTES: