# E. Analog Devices Inc./Maxim Integrated - <u>ZLF645E0H2064G Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                           |

|----------------------------|--------------------------------------------------------------------|

| Core Processor             | Z8 LXMC                                                            |

| Core Size                  | 8-Bit                                                              |

| Speed                      | 8MHz                                                               |

| Connectivity               | UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, WDT                             |

| Number of I/O              | 16                                                                 |

| Program Memory Size        | 64KB (64K x 8)                                                     |

| Program Memory Type        | FLASH                                                              |

| EEPROM Size                |                                                                    |

| RAM Size                   | 1K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.9V ~ 3.6V                                                        |

| Data Converters            |                                                                    |

| Oscillator Type            | <u> </u>                                                           |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                      |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                     |

| Supplier Device Package    | 20-SSOP                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/zlf645e0h2064g |

|                            |                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| Architectural Overview           |

|----------------------------------|

| Features                         |

| Interrupt Sources                |

| Additional Features 2            |

| Functional Block Diagram 4       |

| Pin Description                  |

| I/O Port Pin Functions           |

| RESET (Input, Active Low) 18     |

| Port 0                           |

| Port 1                           |

| Port 2                           |

| Port 3                           |

| Comparator Inputs 28             |

| Comparator Outputs 28            |

| Port 4                           |

| Port Configuration Register 30   |

| Port 0/1 Mode Register 31        |

| Port 0 Register                  |

| Port 1 Register                  |

| Port 2 Mode Register             |

| Port 2 Register                  |

| Port 3 Mode Register             |

| Port 3 Register                  |

| Port 4 Mode Register             |

| Port 4 Register                  |

| Memory and Registers 41          |

| Flash Program/Constant Memory 41 |

| Register File                    |

| Stack                            |

| Register Pointer Example 45      |

| Linear Memory Addressing 45      |

| Register Pointer Register    48  |

| Stack Pointer Register           |

### Table 24. Stack Pointer Register Low Byte (SPL)

| Bit          | 7             | 6         | 5       | 4           | 3          | 2       | 1   | 0   |  |

|--------------|---------------|-----------|---------|-------------|------------|---------|-----|-----|--|

| Field        | Stack Pointer |           |         |             |            |         |     |     |  |

| Reset        | Х             | Х         | Х       | Х           | Х          | Х       | Х   | Х   |  |

| R/W          | R/W           | R/W       | R/W     | R/W         | R/W        | R/W     | R/W | R/W |  |

| Address      |               |           | Bank Ir | ndependent: | FFh; Linea | r: 0FFh |     |     |  |

| Bit Position | Value         | Descripti | on      |             |            |         |     |     |  |

| [7:0]        | 00-FF         | Stack Poi | nter    |             |            |         |     |     |  |

#### Table 25. Stack Pointer Register High Byte (SPH) or User Data Register (USER)

| Bit     | 7   | 6                           | 5       | 4          | 3          | 2       | 1        | 0 |  |  |

|---------|-----|-----------------------------|---------|------------|------------|---------|----------|---|--|--|

| Field   |     | Stack Pointer               |         |            |            |         |          |   |  |  |

| Reset   | Х   | X X X X X X X X             |         |            |            |         |          |   |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |         |            |            |         |          |   |  |  |

| Address |     | <u>.</u>                    | Bank In | dependent: | FEh; Linea | r: 0FEh | <u>.</u> |   |  |  |

Notes:

- 1. For devices with 1K bytes of RAM and with 16-bit stack pointer mode enabled, the upper 6 bits of this register are unused for stack addressing. For devices with 512 bytes of RAM and with 16-bit stack pointer mode enabled, the upper 7 bits of this register are unused for stack addressing.

- 2. When ZLF645 MCU is not in 16-bit stack pointer mode, this register is available to store use user data and its functionality is identical to other Maxim<sup>®</sup> Crimzon products such as the ZLP12840 and ZLR64400 MCUs. When available for user data, this register must not be used as a counter for the DJNZ instruction.

for the command will default to the maximum memory size. The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. Also, data is discarded for writes to protected areas of the Flash's main or information Page 3 areas based upon the settings of the read/write protect option bits in User Option Byte 1 (OPT1) register.

```

ICP \leftarrow 0AH

ICP \leftarrow Flash Memory Address[15:8]

ICP \leftarrow Flash Memory Address[7:0]

ICP \leftarrow Size[15:8]

ICP \leftarrow Size[7:0]

ICP \leftarrow 1-memsize data bytes

```

• Read Flash Memory (0BH)—The Read Flash Memory command is used to read data from the Flash's main memory area or Information Area. This command is equivalent to the CPU reading the memory through the LDC and LDCI instructions. Data can be read 1 to 'memsize' bytes at a time where memsize represents the size (32 KB or 64 KB) of the Flash memory for the product option chosen (The memsize number of bytes can be written by setting the size to 0). Depending on the settings of the read/write protect option bits in User Option Byte 1 register, reads to protected areas of the Flash's main memory area will return FFH for the data.

```

ICP \leftarrow 0BH

ICP \leftarrow Flash Memory Address[15:8]

ICP \leftarrow Flash Memory Address[7:0]

ICP \leftarrow Size[15:8]

ICP \leftarrow Size[7:0]

ICP \rightarrow 1-65536 data bytes

```

• **Read Flash Main Memory CRC (0EH)**—The Read Flash Main Memory CRC command computes and returns the Cyclic Redundancy Check (CRC) of the Flash's Main Memory using the 16-bit CRC-CCITT polynomial. If the device is not in ICP mode, this command returns FFFFH for the CRC value. Unlike most other ICP Read commands, there is a delay from issuing of the command until the ICP returns the data. The ICP reads the Main Memory, calculates the CRC value, and returns the result. The delay is a function of the Flash main memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Flash main memory.

```

ICP \leftarrow 0EHICP \rightarrow CRC[15:8]ICP \rightarrow CRC[7:0]

```

• **Read ICP Autobaud Register (1BH)**— The Read ICP Autobaud register command reads the 12-bit ICP autobaud value set during autobaud detection.

```

ICP \leftarrow 1BH

ICP \rightarrow (4'b0000, Autobaud[11:8])

```

### **TEST Mode Register**

The TEST Mode register is used to enable various device test or Flash memory access modes. At present this register only provides configuration for a single mode where, once programmed, Flash memory accesses bypass the devices Flash Controller and are done through the devices I/O pins. A complete description of this mode is available in the Flash Byte Programming Interface section. This register can only be read or written using the ICP Read/Write Test Mode Register commands.

#### Table 31. TEST Mode Register (TESTMODE)

| Bits  | 7   | 6 | 5          | 4                              | 3        | 2   | 1 0 |   |

|-------|-----|---|------------|--------------------------------|----------|-----|-----|---|

| Field |     | I | Reserved F | lash Controller<br>Bypass Mode | Reserved |     |     |   |

| Reset | 0   | 0 | 0          | 0                              | 0        | 0   | 0   | 0 |

| R/W   | R/W | R | R          | R                              | R        | R/W | R   | R |

| Bit Position | Value | Description                                        |

|--------------|-------|----------------------------------------------------|

| [7:3]        | —     | Reserved— Must be written to 1. Reads return 0.    |

| [2]          |       | Flash Controller Bypass Mode                       |

|              | 0     | The device is not in Flash Controller Bypass Mode. |

|              | 1     | The device is in Flash Controller Bypass mode.     |

| [1:0]        | —     | Reserved—Must be written to 1. Reads return 0.     |

# **Exiting ICP Mode**

The ZLF645 MCU is taken out of ICP mode under any of the following conditions:

- Initiating a POR with P36 held High during the entire reset period.

- Lowering V<sub>DD</sub> until the ZLF645 MCU reaches a Voltage Brownout reset state.

#### Flash Memory Flash Protect Program Read Page Erase Mass Erase Block **Option Bits** Main FLRWP=1, Yes Yes Yes Yes Memory FLPROT1=1 FLRWP=0, Main No No No Yes Memory FLPROT1=X Main FLRWP=1, Yes<sup>1</sup> Yes<sup>1</sup> Yes<sup>1</sup> Yes FLPROT1=0 Memory FLRWP=1, Information Yes<sup>2</sup> Yes<sup>2</sup> Yes<sup>2</sup> Yes Area FLPROT1=1 Information FLRWP=1, Yes<sup>2</sup> No No Yes Area FLPROT1=0 Information FLRWP=0. Yes<sup>2</sup> No No Yes Area FLPROT1=1

#### Table 40.Flash Byte Programming Functions Summary

Notes

1. Program, Read, and Page Erase access is limited to the upper half address space of the main memory only.

2. Only Page 3 of the Information Area is accessible for Program, Read, and Page Erase operations.

- 9. Before disabling the transmitter, read the transmit completion status bit, UST[1]. If UST[1]=0, continue to monitor the bit until it changes to 1, which indicates that all data in the Transmit Data and Internal Shift registers has been transmitted.

- **Caution:** Data written while the transmit enable bit is clear (UCTL[7]=0) will not be transmitted. Data written while the transmit data status bit is clear (UST[2]=0) overwrites the previous value written, so the previous written value will not be transmitted. Disabling the UART transmitter while the transmit completion status bit is clear (UST[1]=0) can corrupt the byte being transmitted.

#### **Receiving Data Using the Polled Method**

Follow the steps below to configure the UART for polled data reception:

- 1. Write to the BCNST register to set the appropriate baud rate.

- 2. Write to the UART Control register (UCTL) to:

- (a) Set the receive enable bit (UCTL[6]) to enable the UART for data reception

- (b) Enable parity (if appropriate) and select either even- or odd-parity

- 3. Check the receive status bit in the UART Status register, bit UST[7], to determine if the Receive Data register contains a valid data byte (indicated by a 1). If UST[7] is set to 1 to indicate available data, continue to Step 4. If the Receive Data register is empty (indicated by a 0), continue to monitor the UST[7] bit awaiting reception of the valid data.

- 4. Read data from the UART Receive Data register.

- 5. Return to Step 3 to receive additional data.

#### **Receiving Data Using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions).

Follow the steps below to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART BRG Constant registers to set the appropriate baud rate.

- 2. Execute DI instruction to disable interrupts.

- 3. Write to the Interrupt Control registers to enable the UART receiver interrupt and set the appropriate priority.

- 4. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 5. Write to the UART Control register (UCTL) to:

- (a) Set the receive enable bit (UCTL[6]) to enable the UART for data reception

- (b) Enable parity, if appropriate, and select either even- or odd-parity

- 6. Execute an EI instruction to enable interrupts.

| <b>Bit Position</b> | Value | Description                                                               |

|---------------------|-------|---------------------------------------------------------------------------|

| [6]                 |       | Parity Error—Set when a parity error occurs; cleared when URDATA is read. |

|                     | 0     | No parity error occurs.                                                   |

|                     | 1     | Parity error occurs.                                                      |

| [5]                 |       | Overrun Error—Set when an overrun error occurs; cleared when              |

|                     |       | URDATA is read.                                                           |

|                     | 0     | No overrun error occurs.                                                  |

|                     | 1     | Overrun error occurs.                                                     |

| [4]                 |       | Framing Error—Set when a framing error occurs; cleared when               |

|                     |       | URDATA is read.                                                           |

|                     | 0     | No framing error occurs.                                                  |

|                     | 1     | Framing error occurs.                                                     |

| [3]                 |       | Break—Set when a break is detected; cleared when URDATA is read.          |

|                     | 0     | No break occurs.                                                          |

|                     | 1     | Break occurs.                                                             |

| [2]                 |       | Transmit Data Status—Set when the UART is ready to transmit; cleared when |

|                     |       | TRDATA is written.                                                        |

|                     | 0     | Do not write to the UART Transmit Data register.                          |

|                     | 1     | UART Transmit Data register ready to receive additional data.             |

| [1]                 |       | Transmit Completion Status                                                |

|                     | 0     | Data is currently transmitting.                                           |

|                     | 1     | Transmission is complete.                                                 |

| [0]                 | Read  | Noise Filter—Detects noise during data reception.                         |

|                     | 0     | No noise detected.                                                        |

|                     | 1     | Noise detected.                                                           |

|                     | Write |                                                                           |

|                     | 0     | Turn off noise filter.                                                    |

|                     | 1     | Turn on noise filter.                                                     |

# **UART Control Register**

The UART Control register controls the UART. In addition to setting bit 5, you must also set appropriate bit in the Interrupt Mask register (see Table 65 on page 133).

**Note:** This register is not reset after a Stop Mode Recovery.

| Bit          | 7                                                                                                                                                                                                                                                                                                                                                                            | 6                           | 5                            | 4                | 3                | 2             | 1         | 0                      |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------|------------------|------------------|---------------|-----------|------------------------|

| Field        | Transmitter<br>Enable                                                                                                                                                                                                                                                                                                                                                        | Receiver<br>Enable          | UART<br>Interrupts<br>Enable | Parity<br>Enable | Parity<br>Select | Send<br>Break | Stop Bits | Baud Rate<br>Generator |

| Reset        | 0                                                                                                                                                                                                                                                                                                                                                                            | 0                           | 0                            | 0                | 0                | 0             | 0         | 0                      |

| R/W          | R/W                                                                                                                                                                                                                                                                                                                                                                          | R/W                         | R/W                          | R/W              | R/W              | R/W           | R/W       | R/W                    |

| Address      |                                                                                                                                                                                                                                                                                                                                                                              |                             | Bank Ir                      | ndependent:      | F3h; Linea       | r: 0F3h       |           |                        |

| Bit Position | n Value                                                                                                                                                                                                                                                                                                                                                                      | Descriptio                  | 'n                           |                  |                  |               |           |                        |

| [7]          | 0<br>1                                                                                                                                                                                                                                                                                                                                                                       | Transmitter<br>Transmitter  |                              |                  |                  |               |           |                        |

| [6]          | 0<br>1                                                                                                                                                                                                                                                                                                                                                                       | Receiver d<br>Receiver e    |                              |                  |                  |               |           |                        |

| [5]          | 0<br>1                                                                                                                                                                                                                                                                                                                                                                       |                             | rrupts disab<br>rrupts enabl |                  |                  |               |           |                        |

| [4]          | 0<br>1                                                                                                                                                                                                                                                                                                                                                                       | Parity disal<br>Parity enat |                              |                  |                  |               |           |                        |

| [3]          | 0<br>1                                                                                                                                                                                                                                                                                                                                                                       | Even parity<br>Odd parity   |                              |                  |                  |               |           |                        |

| [2]          | 0<br>1                                                                                                                                                                                                                                                                                                                                                                       | No break is<br>Send Brea    | s sent.<br>k (force Tx c     | output to 0).    |                  |               |           |                        |

| [1]          | 0<br>1                                                                                                                                                                                                                                                                                                                                                                       |                             |                              |                  |                  |               |           |                        |

| [0]          | <ul> <li>I wo stop bits.</li> <li>Baud Rate Generator—When the transmitter and receiver are disabled, the BRG can be used as an additional timer. When setting this bit, clear bits [7:6] in this register. Also set bit [5] if an interrupt is required when the BRG is reloaded.</li> <li>BRG used as Baud Rate Generator for UART.</li> <li>BRG used as timer.</li> </ul> |                             |                              |                  |                  |               |           |                        |

#### Table 45. UART Control Register (UCTL)

# **UART Baud Rate Generator Constant Register**

The UART baud rate generator determines the frequency at which UART data is received and transmitted. This baud rate is determined by the following equation:

UART Data Rate (bps) = System Clock Frequency (Hz) 16 x UART Baud Rate Divisor Value (BCNST)

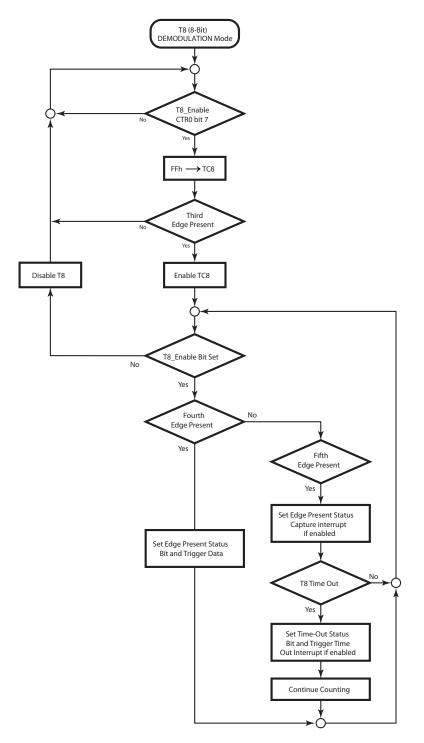

#### **T8 DEMODULATION Mode**

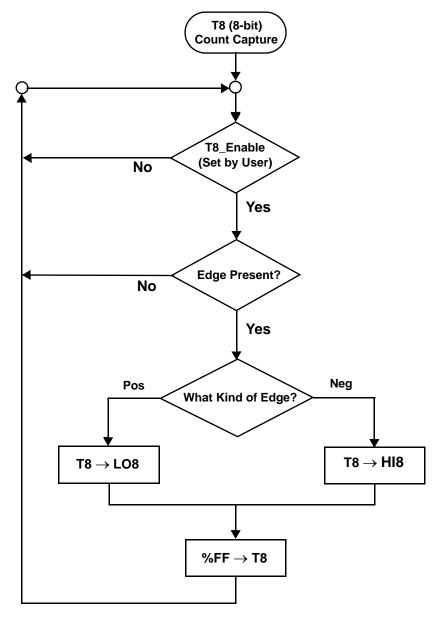

You must program TC8L and TC8H to FFh. After T8 is enabled, when the first edge (rising, falling, or both depending on CTR1 bits [5:4]) is detected, it starts to count down. When a subsequent edge (rising, falling, or both depending on CTR1 bits [5:4]) is detected during counting, the current value of T8 is complemented and put into one of the capture registers.

If it is a positive edge, data is put into LO8; if it is a negative edge, data is put into HI8. From that point, one of the edge detect status bits (CTR1, bits [1:0]) is set, and an interrupt can be generated if enabled (CTR0, bit 2). Meanwhile, T8 is loaded with FFh and starts counting again. If T8 reaches 0, the time-out status bit (CTR0, bit 5) is set, and an interrupt can be generated if enabled (CTR0, bit 1). T8 then continues counting from FFh (see Figure 32 on page 106).

106

When bit 4 of CTR3 is enabled, the flow of the demodulation sequence is altered. The third edge makes T8 active, and the fourth and fifth edges are captured. The capture interrupt is activated after the fifth event occurs. This mode is useful for capturing the carrier duty cycle as well as the frequency at which the first cycle is corrupted. See Figure 33 and Figure 34.

Figure 34. DEMODULATION Mode Flowchart with Bit 4 of CTR3 Set

#### **Timer 16 Capture Low Register**

The Timer 16 Capture Low register (see Table 51) holds the captured data from the output of the 16-bit Counter/Timer 16. This register contains the least significant byte (LSB) of the data.

• **Note:** This register is not reset after a Stop Mode Recovery.

Table 51. Timer 16 Capture Low Register (LO16)

| Bit          | 7                              | 6                         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|--------------|--------------------------------|---------------------------|---|---|---|---|---|---|--|--|

| Field        | T16_Capture_LO                 |                           |   |   |   |   |   |   |  |  |

| Reset        | 0                              | 0                         | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| R/W          | R                              | R                         | R | R | R | R | R | R |  |  |

| Address      |                                | Bank D: 08h; Linear: D08h |   |   |   |   |   |   |  |  |

| Bit Position | Bit Position Value Description |                           |   |   |   |   |   |   |  |  |

[7:0] 0hh–FFh **T16\_Capture\_LO**—Read returns captured data. Writes have no effect.

#### **Counter/Timer 16 High Hold Register**

The Counter/Timer 16 High Hold register (see Table 52) contains the high byte of the value loaded into the T16 timer.

**Note:** This register is not reset after a Stop Mode Recovery.

#### Table 52. Counter/Timer 16 High Hold Register (TC16H)

| Bit          | 7                         | 6        | 5       | 4            | 3   | 2   | 1   | 0   |  |  |

|--------------|---------------------------|----------|---------|--------------|-----|-----|-----|-----|--|--|

| Field        | T16_Data_HI               |          |         |              |     |     |     |     |  |  |

| Reset        | 0                         | 0        | 0       | 0            | 0   | 0   | 0   | 0   |  |  |

| R/W          | R/W                       | R/W      | R/W     | R/W          | R/W | R/W | R/W | R/W |  |  |

| Address      | Bank D: 07h; Linear: D07h |          |         |              |     |     |     |     |  |  |

| Bit Position | n Value Description       |          |         |              |     |     |     |     |  |  |

| [7:0]        | 0hh–FFh                   | T16 Data | HI-Read | /Write Data. |     |     |     |     |  |  |

## **Voltage Brownout Standby**

An on-chip voltage comparator circuit (VBO) checks that the  $V_{DD}$  is at the required level for correct operation of the device in terms of Flash memory reads. A second on-chip comparator circuit (subVBO) checks that the  $V_{DD}$  level is high enough for proper operation of the VBO circuit. If the  $V_{DD}$  level drops below the VBO trip point, the ZLF645 will be held in a reset state as long as  $V_{DD}$  remains below this trip point value, and the XTAL1 and XTAL2 oscillator circuitry will be disabled thereby stopping the clock input to the ZLF645 and saving power. If the  $V_{DD}$  level continues to drop below the subVBO trip point, the ZLF645 will remain in a reset state and the VBO comparator circuit will be disabled for further power savings. When the power level returns to a value above the VBO trip point, the device performs a power-on reset and functions normally.

## **STOP Mode**

STOP instruction turns OFF the internal clock and external crystal oscillation, thus reducing the MCU supply current to a very low level. For STOP mode current specifications, see Table 80 on page 165.

To enter STOP mode, first flush the instruction pipeline to avoid suspending execution in mid-instruction. Execute a NOP instruction (OpCode = FFh) immediately before the appropriate sleep instruction, as given below:

| FF | NOP  | ; | clear | the  | pipeline |

|----|------|---|-------|------|----------|

| бF | STOP | ; | enter | STOP | , mode   |

STOP mode is terminated only by a reset, such as WDT time-out, POR, or one of the Stop Mode Recovery events as described in Stop Mode Recovery Event Sources on page 144. This condition causes the processor to restart the application program at address 000Ch.

Unlike a normal POR or WDT reset, a Stop Mode Recovery reset does not reset the contents of some registers and bits. Register bits not reset by a Stop Mode Recovery are highlighted in grey in the register tables. Register bit SMR[7] is set to 1 by a Stop Mode Recovery.

# HALT Mode

HALT instruction turns off the internal CPU clock, but not the XTAL oscillation. The counter/timers, UART, and interrupts (IRQ0, IRQ1, IRQ2, IRQ3, IRQ4, and IRQ5) remain active. The devices are recovered by interrupts, either externally or internally generated. An interrupt request must be executed (enabled) to exit HALT mode. After the interrupt service routine, the program continues from the instruction after HALT mode.

#### Table 69. Stop Mode Recovery Register (SMR)

| ,            |                                  |                                                                                                | 1                                               |                                            | 1                                              |                                     | 1                              |                                                          |

|--------------|----------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------------|-------------------------------------|--------------------------------|----------------------------------------------------------|

| Bit          | 7                                | 6                                                                                              | 5                                               | 4                                          | 3                                              | 2                                   | 1                              | 0                                                        |

| Field        | Stop<br>Flag                     | Stop Mode<br>Recovery Level                                                                    |                                                 |                                            |                                                |                                     | Reset Time<br>Reduction        | SCLK/TCLK<br>Divide-by-16                                |

| Reset        | 0                                | 0                                                                                              | 1                                               | 0                                          | 0                                              | 0                                   | 0                              | 0                                                        |

| R/W          | R                                | W                                                                                              | W                                               | W                                          | W                                              | W                                   | W                              | W                                                        |

| Address      |                                  |                                                                                                | Bar                                             | nk F: 0E                                   | 3h; Linea                                      | r: F0Bh                             |                                |                                                          |

| Bit Position | ו Va                             | lue Description                                                                                |                                                 |                                            |                                                |                                     |                                |                                                          |

| [7]          |                                  | Stop Flag—Ind<br>Recovery. A wr<br>Power-on reset<br>Stop Mode Rec                             | ite to this                                     |                                            |                                                |                                     | power-on res                   | et or Stop Mode                                          |

| [6]          |                                  | Stop Mode Re<br>initiated by a Lo<br>(see Figure 44 of<br>Low.<br>1 High.                      | w or Hig                                        | h level a                                  |                                                |                                     |                                | selected SMR is                                          |

| [5]          |                                  | Stop Delay—C<br>or resonator clo<br>O Off.<br>1 On.                                            |                                                 |                                            | t delay af                                     | ter recov                           | ery. Must be 1                 | if using a crystal                                       |

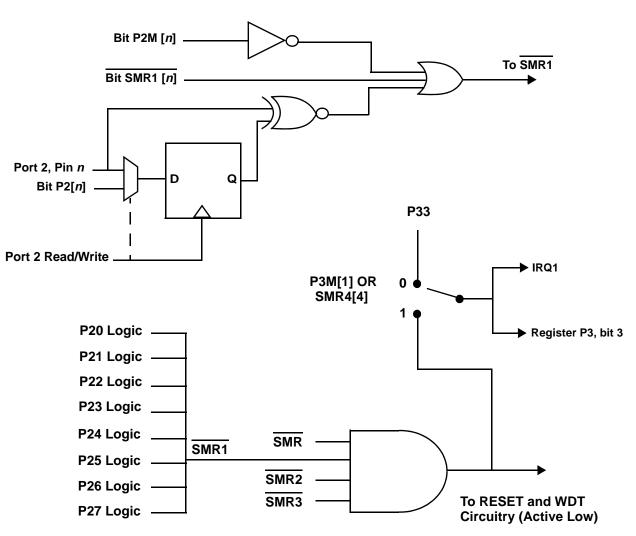

| [4:2]        | 00<br>01<br>01<br>10<br>10<br>11 | source at the X<br>changed by a S<br>configured as o<br>No SMR registe<br>Reserved.<br>10 P31. | (OR gate<br>Stop Mod<br>utput or s<br>er source | e input<br>e Reco <sup>.</sup><br>selecteo | (see <mark>Fig</mark><br>very. The<br>d in SMR | <mark>ure 44</mark> o<br>e followin | n page 145).<br>g equations ig | covery wake-up<br>This value is not<br>nore any Port pin |

149

Individual Port 2 Pin SMR Logic, n = 0 - 7

Figure 45. SMR1 Register-Controlled Event Sources

#### Table 81. Clock, Reset, Timers, and SMR Timing (Continued)

|    |                    |                                            |                 | T <sub>A</sub> = 0 °C to +70 °C<br>8.0 MHz |                 |       | WDTMR<br>(Bits 6, 5, 4, |

|----|--------------------|--------------------------------------------|-----------------|--------------------------------------------|-----------------|-------|-------------------------|

| No | Symbol             | Parameter                                  | V <sub>CC</sub> | Min                                        | Max             | Units | (Bits 0, 0, 4,<br>1, 0) |

| 13 | T <sub>POR</sub>   | Power-on reset                             | 1.9–3.6         | 2.5                                        | 10 <sup>5</sup> | ms    |                         |

| 14 | f <sub>iramp</sub> | Frequency of input signal for IR amplifier | _               | 0                                          | 500             | kHz   |                         |

#### Notes

1. Timing Reference uses 0.9  $V_{CC}$  for a logic 1 and 0.1  $V_{CC}$  for a logic 0. 2. Interrupt request through Port 3 (P33:P31).

3. SMR – bit 5 = 1.

4. SMR - bit 5 = 0.

5. If bit 1 of the SMR register is programmed to 1, this value is 2.5 ms as measured from the time the oscillator input to XTAL1 reaches a peak to peak voltage oscillation of at least 300 mV.

|    |                   |                                         | T <sub>A</sub> = 0 °C to +70 °C<br>8.0 MHz |     |        |                                                          |

|----|-------------------|-----------------------------------------|--------------------------------------------|-----|--------|----------------------------------------------------------|

| No | Symbol            | Parameter                               | Min                                        | Max | Units  | Condition                                                |

| 1  | I <sub>FLP</sub>  | Flash Memory Programming<br>Current     | —                                          | 10  | mA     | _                                                        |

| 2  | I <sub>FLE</sub>  | Flash Memory Page/Mass<br>Erase Current | _                                          | 6   | mA     | _                                                        |

| 3  | I <sub>RD</sub>   | Flash Dynamic Read Current              | —                                          | 420 | а      | Assumes reads<br>every clock cycle<br>with a 1 MHz clock |

| 4  | V <sub>FLPE</sub> | Flash Memory Program/<br>Erase Voltage  | 2.3                                        | 3.6 | V      | _                                                        |

| 5  | V <sub>FLR</sub>  | Flash Memory Read Voltage               | 1.8                                        | 3.6 | V      | _                                                        |

| 6  | T <sub>PROG</sub> | Flash Programming Time                  | 30                                         | 60  | us     | —                                                        |

| 7  | Тре               | Flash Page Erase Time                   | 10                                         |     | ms     | _                                                        |

| 8  | Tme               | Flash Mass Erase Time                   | 10                                         |     | ms     | _                                                        |

| 9  | Tdr               | Flash Data Retention Time               | 10                                         |     | years  | Temp=25 °C                                               |

| 10 | Fen               | Flash Program/Erase<br>Endurance        | 20,000                                     | —   | cycles | —                                                        |

#### Table 82. Flash Memory Electrical Characteristics and Timing

# Packaging

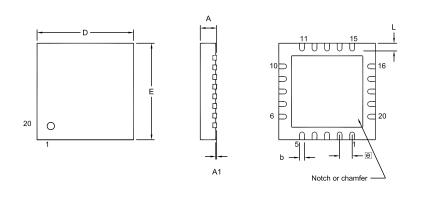

Figure 50 displays the 20-pin quad flat no-lead (QFN) package for the ZLF645 Series of Flash MCUs.

| SYMBOL  | MILLIMETER |      | INCH      |       |  |

|---------|------------|------|-----------|-------|--|

| STNIBUL | MIN        | MAX  | MIN       | MAX   |  |

| А       | 0.80       | 1.00 | 0.031     | 0.039 |  |

| A1      | -          | 0.05 | -         | 0.002 |  |

| b       | 0.25       | 0.35 | 0.010     | 0.014 |  |

| D       | 4.95       | 5.05 | 0.195     | 0.199 |  |

| E       | 4.95       | 5.05 | 0.195     | 0.199 |  |

| e       | 0.65 BSC   |      | 0.026 BSC |       |  |

| L       | 0.35       | 0.45 | 0.014     | 0.018 |  |

1. CONTROLLING DIMENSIONS : mm 2. MAX. COPLANARITY : 0.08 mm 0.003"

INCH

MAX

.040

.165

.021

.065

.055

.015 1.470

1.415

.620

.555

.515

.660

.150

.075

.070

.090

.060

.100 BSC

MÍN

.015

.125

.015

.055

.045

.009

1.440

1.390

.600

.535

.505

.610

.120

.055

.055

.060

.040

182

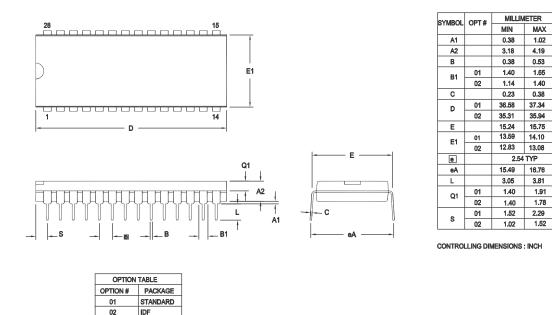

Figure 56 displays the 28-pin plastic dual inline package (PDIP) for the ZLF645 Series of Flash MCUs.

Note: Zllog supplies both options for production. Component layout PCB design should cover bigger option 01.

#### Figure 56. 28-Pin PDIP Package Diagram

188

internal signals 135 comparator inputs 28 outputs 28 condition codes 161 conditions, test 164 connection, power 3 constant memory 41 constant, baud rate 97, 98 counter/timer block diagram 99 capture flowchart 106 input circuit 101 output configuration 27 crystal 134 crystal oscillator pins (XTAL1, XTAL2) 134, 135 Customer Support 193

# D

data format, UART 87 data handling, UART 91 DC characteristics 165 demodulation changing mode 121 flowchart 106, 107 timer 105, 110 demodulation mode flowchart 108 device block diagram 4 features 1 diagram, package 176, 177, 178, 179, 180, 181, 182, 183 divisor, baud rate 97, 98

# Ε

electrical characteristics 163 error handling, UART 91 example BCNST register 94 register pointer 45

## F

fast recovery, stop mode 143 features, device 1 flags register 160 flash option bit configuration - reset 171 flash memory 67, 82 arrrangement 68 byte programming 74 code protection 73 configurations 67 control register definitions 75 flash status register 77 flow chart 72 frequency high and low byte registers 79 mass erase 75 operation 69 operation timing 69 page erase 74 page select register 77, 78 flowchart demodulation mode 106, 107, 108 timer transmit 102 UART receive 92 format, UART data 87 FPS register 77, 78 FSTAT register 77 functional block diagram 4

# Η

h suffix 104 HALT mode 143 handshaking, UART 90

# I

ICP architecture 54 auto-baud detector/generator 55 baud rate limits 56 block diagram 54 commands 57

192

Timer 16 Capture High Register (HI16) 115 Timer 16 Capture Low Register (L016) 116 Timer 16 Control register (CTR2) 124 Timer 16 High Hold register (TC16H) 116 Timer 16 Low Hold Register (TC16L) 117 Timer 8 and Timer 16 Common Functions Register (CTR1) 121 Timer 8 Capture High Register (HI8) 114 Timer 8 Capture Low Register (L08) 115 Timer 8 Control Register (CTR0) 119 Timer 8 High Hold Register (TC8H) 117 Timer 8 Low Hold Register (TC8L) 118 Timer 8/Timer 16 Control Register (CTR3) 126 timing, AC 168 transmit caution, UART 88, 89 transmit mode caution 121 flowchart 102 timer 101, 109

# U

UART architecture 86 baud rate generator 93 block diagram 86 data and error handling 91 data format 87 interrupts 90 operation 86 overrun error 91 polled receive 89 polled transmit 87 receive interrupt 89, 90, 92 stop bit 91 transmit caution 88, 89 transmit interrupt 88, 90 UART Control Register (UCTL) 96, 97 UART Receive/Transmit Data Register (URDA-TA/UTDATA) 95 UART Status Register (UST) 95 User Data Register (USER) 48

# V

vector, interrupt 129 voltage brown-out 139, 143 detection 143 detection register 140

# W

Watchdog Timer description 141 watchdog timer diagram 138 Watchdog Timer Mode Register (WDTMR) 142

# X

XTAL1 pin 134 XTAL2 pin 135

# Ζ

ZLR64400 MCU block diagram 4 features 1