# E. Analog Devices Inc./Maxim Integrated - <u>ZLF645E0P2064G Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                    |

|----------------------------|--------------------------------------------------------------------|

| Product Status             | Obsolete                                                           |

| Core Processor             | Z8 LXMC                                                            |

| Core Size                  | 8-Bit                                                              |

| Speed                      | 8MHz                                                               |

| Connectivity               | UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, WDT                             |

| Number of I/O              | 16                                                                 |

| Program Memory Size        | 64KB (64K x 8)                                                     |

| Program Memory Type        | FLASH                                                              |

| EEPROM Size                | -                                                                  |

| RAM Size                   | 1K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.9V ~ 3.6V                                                        |

| Data Converters            | -                                                                  |

| Oscillator Type            | -                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                    |

| Mounting Type              | Through Hole                                                       |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                            |

| Supplier Device Package    | 20-PDIP                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/zlf645e0p2064g |

|                            |                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Enabling The Flash Byte Programming Interface              |      |

|------------------------------------------------------------|------|

| Flash Byte Programming Interface Flash Access Restrictions | . 82 |

| Infrared Learning Amplifier                                | . 84 |

| Universal Asynchronous Receiver/Transmitter                | . 85 |

| Architecture                                               | . 86 |

| Operation                                                  | . 86 |

| Data Format                                                | . 87 |

| Transmitting Data Using Polled Method                      |      |

| Transmitting Data Using Interrupt-Driven Method            |      |

| Receiving Data Using the Polled Method                     |      |

| Receiving Data Using the Interrupt-Driven Method           |      |

| UART Interrupts                                            |      |

| UART Baud Rate Generator                                   |      |

| UART Receive Data Register/UART Transmit Data Register     |      |

| UART Status Register                                       |      |

| UART Control Register                                      | . 96 |

| UART Baud Rate Generator Constant Register                 | . 97 |

| Timers                                                     | . 99 |

| Counter/Timer Functional Blocks                            | 100  |

| Input Circuit                                              | 100  |

| T8 TRANSMIT Mode                                           | 101  |

| T8 DEMODULATION Mode                                       | 105  |

| T16 TRANSMIT Mode                                          | 109  |

| T16 DEMODULATION Mode                                      | 110  |

| PING-PONG Mode                                             | 111  |

| Timer Output                                               | 112  |

| Counter/Timer Registers                                    | 114  |

| Timer 8 Capture High Register                              |      |

| Timer 8 Capture Low Register                               |      |

| Timer 16 Capture High Register                             |      |

| Timer 16 Capture Low Register                              |      |

| Counter/Timer 16 High Hold Register                        |      |

| Counter/Timer 16 Low Hold Register                         |      |

| Counter/Timer 8 High Hold Register                         |      |

| Counter/Timer 8 Low Hold Register                          |      |

| Counter/Timer 8 Control Register                           |      |

| T8 and T16 Common Functions Register                       |      |

| Counter/Timer 16 Control Register                          | 124  |

| Timer 8/Timer 16 Control Register                          |      |

Table 5 lists the function and signal directions of each pin within the 20-pin PDIP, SOIC, and SSOP packages sequentially by pin number.

| Pin No | Symbol          | Function           | Signal Direction |

|--------|-----------------|--------------------|------------------|

| 1      | P25             | Port 2, bit 5      | Input/Output     |

| 2      | P26             | Port 2, bit 6      | Input/Output     |

| 3      | P27             | Port 2, bit 7      | Input/Output     |

| 4      | P07             | Port 0, bit 7      | Input/Output     |

| 5      | V <sub>DD</sub> | Power Supply       | Input            |

| 6      | XTAL2           | Crystal oscillator | Output           |

| 7      | XTAL1           | Crystal oscillator | Input            |

| 8      | P31             | Port 3, bit 1      | Input            |

| 9      | P32             | Port 3, bit 2      | Input            |

| 10     | P33             | Port 3, bit 3      | Input            |

| 11     | P34             | Port 3, bit 4      | Input/Output     |

| 12     | P36             | Port 3, bit 6      | Output           |

| 13     | P00             | Port 0, bit 0      | Input/Output     |

|        | P30             | Port 3, bit 0      | Input            |

| 14     | P01             | Port 0, bit 1      | Input/Output     |

| 15     | V <sub>SS</sub> | Ground In          | put              |

| 16     | P20             | Port 2, bit 0      | Input/Output     |

| 17     | P21             | Port 2, bit 1      | Input/Output     |

| 18     | P22             | Port 2, bit 2      | Input/Output     |

| 19     | P23             | Port 2, bit 3      | Input/Output     |

| 20     | P24             | Port 2, bit 4      | Input/Output     |

#### Table 5. 20-Pin PDIP/SOIC/SSOP Sequential Pin Identification

|     |         | In-Circuit |                |            |           |       |         |

|-----|---------|------------|----------------|------------|-----------|-------|---------|

| Pin | I/O     | Programmer | Counter/Timers | Comparator | Interrupt | IRAMP | UART    |

| P30 | IN      |            |                | REF1       |           |       |         |

| P31 | IN      |            | IN             | AN1        | IRQ2      | IR1   |         |

| P32 | IN      |            |                | AN2        | IRQ0      |       | UART Rx |

| P33 | IN      |            |                | REF2       | IRQ1      |       |         |

| P34 | IN/OUT  | ICP        | Т8             | AO1        |           | IROUT |         |

| P35 | OUT     |            | T16            |            |           |       |         |

| P36 | OUT T8/ | T16        |                |            |           |       |         |

| P37 | OUT     |            |                | AO2        |           |       |         |

|     |         |            |                |            |           |       |         |

#### Table 12. Summary of Port 3 Pin Functions

Port 3 also provides output for each of the counter/timers and AND/OR Logic (see Figure 10). Control is performed by programming CTR1 bit 5 and bit 4, CTR0 bit 0, and CTR2 bit 0.

#### Table 28. In-Circuit Programmer Commands (Continued)

| ICP Command                        | Command<br>Byte | Enabled when NOT<br>in FLASH CONTROL<br>mode? | Disabled by<br>Flash Read/Write Protect<br>Option Bits (FLRWP and/or<br>FLPROT1)                                                                                                                                                               |

|------------------------------------|-----------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read Flash Controller<br>Registers | 09H             | No                                            | _                                                                                                                                                                                                                                              |

| Write Flash Memory                 | 0AH             | No                                            | If FLRWP en abled, comm and is<br>disabled for en tire Flash main<br>memory an d p age 3 of the<br>Information Ar ea. If FLPROT1<br>enabled, command disabled for<br>page 3 of the Information Are a<br>and lower half of main memory<br>only. |

| Read Flash Memory                  | 0BH             | No                                            | If FLRWP en abled, comm and is<br>disabled for t he F lash m ain<br>memory. If FLPROT1 ena bled,<br>command disabled for the lower<br>half of main memory only.                                                                                |

| Reserved                           | 0CH – 0DH       | _                                             | Disabled                                                                                                                                                                                                                                       |

| Read Program Memory CRC            | 0EH             | No                                            | _                                                                                                                                                                                                                                              |

| Reserved                           | 0FH –1AH        | _                                             | _                                                                                                                                                                                                                                              |

| Read ICP Autobaud Register         | 1BH             | Yes                                           | _                                                                                                                                                                                                                                              |

| Reserved                           | 1CH – EFH       | _                                             | _                                                                                                                                                                                                                                              |

| Write Test Mode Register           | F0H             | Yes                                           | -                                                                                                                                                                                                                                              |

| Read Test Mode Register            | F1H             | Yes                                           | -                                                                                                                                                                                                                                              |

| Reserved                           | F2H – FFH       | —                                             | -                                                                                                                                                                                                                                              |

In the following bulleted list of ICP commands, data and commands sent from the host to the ICP are identified by 'ICP  $\leftarrow$  Command/Data'. Data sent from the ICP back to the host is identified by 'ICP  $\rightarrow$  Data':

• **Read ICP Revision (00H)**—The Read ICP Revision command determines the version of the ICP. If ICP commands are added, removed, or changed, the revision number changes.

```

\begin{split} & \text{ICP} \leftarrow 00\text{H} \\ & \text{ICP} \rightarrow \text{ICPRev}[15:8] \text{ (Major revision number)} \\ & \text{ICP} \rightarrow \text{ICPRev}[7:0] \text{ (Minor revision number)} \end{split}

```

for the command will default to the maximum memory size. The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. Also, data is discarded for writes to protected areas of the Flash's main or information Page 3 areas based upon the settings of the read/write protect option bits in User Option Byte 1 (OPT1) register.

```

ICP \leftarrow 0AH

ICP \leftarrow Flash Memory Address[15:8]

ICP \leftarrow Flash Memory Address[7:0]

ICP \leftarrow Size[15:8]

ICP \leftarrow Size[7:0]

ICP \leftarrow 1-memsize data bytes

```

• Read Flash Memory (0BH)—The Read Flash Memory command is used to read data from the Flash's main memory area or Information Area. This command is equivalent to the CPU reading the memory through the LDC and LDCI instructions. Data can be read 1 to 'memsize' bytes at a time where memsize represents the size (32 KB or 64 KB) of the Flash memory for the product option chosen (The memsize number of bytes can be written by setting the size to 0). Depending on the settings of the read/write protect option bits in User Option Byte 1 register, reads to protected areas of the Flash's main memory area will return FFH for the data.

```

ICP \leftarrow 0BH

ICP \leftarrow Flash Memory Address[15:8]

ICP \leftarrow Flash Memory Address[7:0]

ICP \leftarrow Size[15:8]

ICP \leftarrow Size[7:0]

ICP \rightarrow 1-65536 data bytes

```

• **Read Flash Main Memory CRC (0EH)**—The Read Flash Main Memory CRC command computes and returns the Cyclic Redundancy Check (CRC) of the Flash's Main Memory using the 16-bit CRC-CCITT polynomial. If the device is not in ICP mode, this command returns FFFFH for the CRC value. Unlike most other ICP Read commands, there is a delay from issuing of the command until the ICP returns the data. The ICP reads the Main Memory, calculates the CRC value, and returns the result. The delay is a function of the Flash main memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Flash main memory.

```

ICP \leftarrow 0EHICP \rightarrow CRC[15:8]ICP \rightarrow CRC[7:0]

```

• **Read ICP Autobaud Register (1BH)**— The Read ICP Autobaud register command reads the 12-bit ICP autobaud value set during autobaud detection.

```

ICP \leftarrow 1BH

ICP \rightarrow (4'b0000, Autobaud[11:8])

```

3. The CPU writes to the Page Select (PGS) register.

Figure 20 displays the basic Flash Controller operation considering code based CPU Flash accesses and based upon the programming of the Flash Controllers Flash Control (FCTL), Sector Protect (FSEC), and Page Select (FPS) Registers. As mentioned previously for ICP based Flash accesses, the only modification to Figure 20 is that the programming of the Sector Protect (FSEC) register is ignored and the ICP has programming and erase access to a page independent of whether it resides in a protected sector. Figure 20 does not display the effects of the Flash read/write protect bits of User Option byte 1.

If either of these bits is enabled, their function takes priority over the operation description displayed in Figure 20 in terms of when a page erase or byte programming access is allowed (for more details, see Flash Code Protection Against External Access on page 73).

#### **Flash Status Register**

The Flash Status (FSTAT) register (see Table 34) indicates the current state of the Flash Controller. This register can be read any time. The read-only Flash Status (FSTAT) register shares its Register File address with the Write-only Flash Control (FCTL) register.

| Bits    | 7    | 6     | 5     | 4             | 3             | 2   | 1 | 0 |

|---------|------|-------|-------|---------------|---------------|-----|---|---|

| Field   | Rese | erved | FSTAT |               |               |     |   |   |

| Reset   | 0    | 0     | 0     | 0             | 0             | 0   | 0 | 0 |

| R/W     | R    | R     | R     | R             | R             | R   | R | R |

| Address |      |       | Bar   | nk F, Registe | er address: ( | )1H |   |   |

#### Table 34. Flash Status Register (FSTAT)

| Bit Position | Value  | Description                                   |  |

|--------------|--------|-----------------------------------------------|--|

| [7:6]        | _      | Reserved—Reads as 0's.                        |  |

| [5:0]        |        | FSTAT—Flash Controller Status                 |  |

|              | 000000 | Flash Controller locked.                      |  |

|              | 000001 | First unlock command received (73H written).  |  |

|              | 000010 | Second unlock command received (8CH written). |  |

|              | 000011 | Flash Controller unlocked.                    |  |

|              | 000100 | Sector protect register selected.             |  |

|              | 001xxx | Program operation in progress.                |  |

|              | 010xxx | Page erase operation in progress.             |  |

|              | 100xxx | Mass erase operation in progress.             |  |

### Flash Page Select Register

The Flash Page Select (FPS) register (see Table 35) shares address space with the Flash Sector Protect (FSEC) register. Unless the Flash Controller is in 'locked' state and its Flash Control (FCTL) register is written with 5EH, writes to this address target the Flash Page Select (FPS) register.

The FPS register is used to select one page within the Flash Main Memory or Information Block for programming or erasure depending upon whether its IFEN bit is 0 or 1 respectively. Each Flash Main Memory Page contains 512 bytes of Flash memory. During a Page Erase operation to the Main Memory, the page that will be erased is the one containing the 512 Flash memory locations where bits 15 through 9 of their addresses is equal to bits 6 through 0 of FPS register. For Main Memory programming operations, bits 15 through 9 of the address to be programmed must equal bits 6 through 0 of the FPS register for the Flash Controller to execute the operation. For page erase or programming operations to the Flash's Information Block as indicated by the IFEN bit being 1, the programming or

### UART Receive Data Register/UART Transmit Data Register

The UART Receive/Transmit Data register (see Table 43) is used to send and retrieve data from the UART channel. When the UART receives a data byte, it can be read from this register. The UART receive interrupt is cleared when this register is used. Data written to this register is transmitted by the UART.

#### Table 43. UART Receive/Transmit Data Register (URDATA/UTDATA)

| Bit          | 7                     | 6          | 5       | 4          | 3          | 2       | 1   | 0   |  |

|--------------|-----------------------|------------|---------|------------|------------|---------|-----|-----|--|

| Field        | UART Receive/Transmit |            |         |            |            |         |     |     |  |

| Reset        | Х                     | Х          | Х       | Х          | Х          | Х       | Х   | Х   |  |

| R/W          | R/W                   | R/W        | R/W     | R/W        | R/W        | R/W     | R/W | R/W |  |

| Address      |                       |            | Bank li | ndependent | F1h; Linea | r: 0F1h |     | l   |  |

| Bit Position | Descrip               | tion       |         |            |            |         |     |     |  |

| [7:0]        | UART R                | eceive/Tra | nsmit   |            |            |         |     |     |  |

## UART Status Register

When read, returns received data. When written, transmits written data.

The UART Status register (see Table 44) displays the status of the UART. Bits [6:3] are cleared by reading the UART Receive/Transmit register (F1h).

#### Table 44. UART Status Register (UST)

| Bit         | 7                                   | 6         | 5          | 4         | 3           | 2           | 1         | 0        |  |

|-------------|-------------------------------------|-----------|------------|-----------|-------------|-------------|-----------|----------|--|

|             | Receive                             | Parity    | Overrun    | Framing   | Break       | Transmit    | Transmit  | Noise    |  |

| Field       | Status                              | Error     | Error      | Error     |             | Data        | Complete  | Filter   |  |

| Reset       | 0                                   | 0         | 0          | 0         | 0           | 0           | 1         | 0        |  |

| R/W         | R/W                                 | R/W       | R/W        | R/W       | R/W         | R/W         | R/W       | R/W      |  |

| Address     | Bank Independent: F2h; Linear: 0F2h |           |            |           |             |             |           |          |  |

| Bit Positio | n Value                             | Descripti | on         |           |             |             |           |          |  |

| [7]         |                                     | Receive S | Status—Set | when data | s received; | cleared who | en URDATA | is read. |  |

|             | 0 UART Receive Data register empty. |           |            |           |             |             |           |          |  |

|             | 1 UART Receive Data register full.  |           |            |           |             |             |           |          |  |

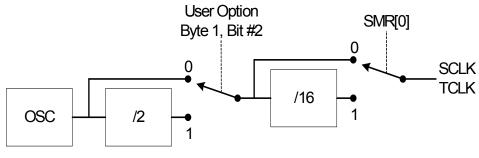

The system clock is usually the crystal clock divided by 2. When the UART baud rate generator is used as an additional timer, a Read from this register returns the actual value of the count of the BRG in progress and not the reload value. See Table 46.

**Note:** *This register is not reset after a Stop Mode Recovery.*

#### Table 46. UART Baud Rate Generator Constant Register (BCNST)

| Bit          | 7                                                                                                                                                                                                                  | 6                            | 5       | 4           | 3          | 2       | 1   | 0   |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------|-------------|------------|---------|-----|-----|--|--|

| Field        |                                                                                                                                                                                                                    | Baud Rate Generator Constant |         |             |            |         |     |     |  |  |

| Reset        | 1                                                                                                                                                                                                                  | 1 1 1 1 1 1 1 1              |         |             |            |         |     |     |  |  |

| R/W          | R/W                                                                                                                                                                                                                | R/W                          | R/W     | R/W         | R/W        | R/W     | R/W | R/W |  |  |

| Address      |                                                                                                                                                                                                                    |                              | Bank Ir | ndependent: | F4h; Linea | :: 0F4h |     |     |  |  |

| Bit Position | Descrip                                                                                                                                                                                                            | otion                        |         |             |            |         |     |     |  |  |

| [7:0]        | Baud Rate Generator Constant<br>When read, returns the actual timer count value (when UCTL[0]=1).<br>When written, sets the Baud Rate Generator Constant.<br>The actual baud rate frequency = XTAL ÷ (32 x BCNST). |                              |         |             |            |         |     |     |  |  |

When T8 is enabled, the output T8\_OUT switches to the initial value (CTR1, bit 1). If the initial value (CTR1, bit 1) is 0, TC8L is loaded; otherwise, TC8H is loaded into the counter.

In SINGLE-PASS mode (CTR0, bit 6), T8 counts down to 0 and stops, T8\_OUT toggles, the time-out status bit (CTR0, bit 5) is set, and a time-out interrupt can be generated if it is enabled (CTR0, bit 1).

In MODULO-N mode, on reaching terminal count, T8\_OUT is toggled, but no interrupt is generated. From that point, T8 loads a new count (if the T8\_OUT level now is 0), TC8L is loaded; if it is 1, TC8H is loaded. T8 counts down to 0, toggles T8\_OUT, and sets the time-out status bit (CTR0, bit 5), thereby generating an interrupt if enabled (CTR0, bit 1). One cycle is thus completed. T8 then loads from TC8H or TC8L according to the T8\_OUT level and repeats the cycle. See Figure 29.

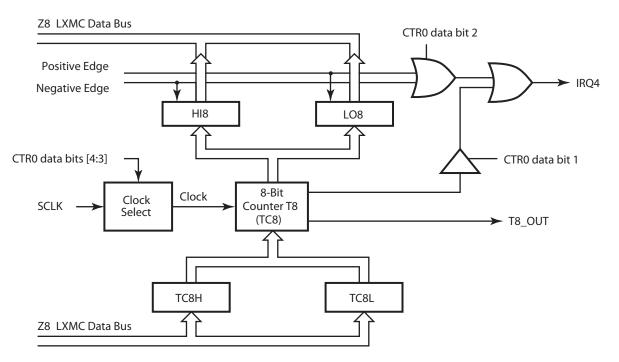

Figure 29. 8-Bit Counter/Timer Circuits

You can modify the values in TC8H or TC8L at any time. The new values take effect when they are loaded.

**Caution:** An initial count of 1 is not allowed (a non-function occurs). An initial count of 0 causes TC8 to count from 0 to FFh to FEh.

<u>/!</u>\

#### **T8 DEMODULATION Mode**

You must program TC8L and TC8H to FFh. After T8 is enabled, when the first edge (rising, falling, or both depending on CTR1 bits [5:4]) is detected, it starts to count down. When a subsequent edge (rising, falling, or both depending on CTR1 bits [5:4]) is detected during counting, the current value of T8 is complemented and put into one of the capture registers.

If it is a positive edge, data is put into LO8; if it is a negative edge, data is put into HI8. From that point, one of the edge detect status bits (CTR1, bits [1:0]) is set, and an interrupt can be generated if enabled (CTR0, bit 2). Meanwhile, T8 is loaded with FFh and starts counting again. If T8 reaches 0, the time-out status bit (CTR0, bit 5) is set, and an interrupt can be generated if enabled (CTR0, bit 1). T8 then continues counting from FFh (see Figure 32 on page 106).

| Name | Source                          | Vector Location<br>(Program Memory) | Comments                                          |

|------|---------------------------------|-------------------------------------|---------------------------------------------------|

| IRQ0 | P32, UART Rx                    | 0,1                                 | External (P32), Rising, Falling<br>Edge Triggered |

| IRQ1 | P33, UART Tx, BRG,<br>SMR Event | 2, 3                                | External (P33), Falling Edge<br>Triggered         |

| IRQ2 | P31                             | 4, 5                                | External (P31), Rising, Falling<br>Edge Triggered |

| IRQ3 | Timer 16                        | 6, 7                                | Internal                                          |

| IRQ4 | Timer 8                         | 8, 9                                | Internal                                          |

| IRQ5 | Low-Voltage Detection           | 10, 11                              | Internal                                          |

#### Table 61. Interrupt Types, Sources, and Vectors

When more than one interrupt is pending, priorities are resolved by a programmable priority encoder controlled by the Interrupt Priority Register. An interrupt machine cycle activates when an interrupt request is granted. As a result, all subsequent interrupts are disabled, and the Program Counter and Status Flags are saved. The cycle then branches to the Program Memory vector location reserved for that interrupt.

All ZLF645 MCU interrupts are vectored through locations in the Program Memory. This memory location and the next byte contain the 16-bit address of the interrupt service routine for that particular interrupt request. To accommodate polled interrupt systems, interrupt inputs are masked, and the Interrupt Request Register is polled to determine which of the interrupt requests require service.

An interrupt resulting from AN1 is mapped into IRQ2, and an interrupt from AN2 is mapped into IRQ0. Interrupts IRQ2 and IRQ0 can be rising, falling, or both edge triggered. These interrupts are user-programmable. The software can poll to identify the state of the pin.

Figure 42. SCLK/TCLK Circuit

### **Voltage Brownout Standby**

An on-chip voltage comparator circuit (VBO) checks that the  $V_{DD}$  is at the required level for correct operation of the device in terms of Flash memory reads. A second on-chip comparator circuit (subVBO) checks that the  $V_{DD}$  level is high enough for proper operation of the VBO circuit. If the  $V_{DD}$  level drops below the VBO trip point, the ZLF645 will be held in a reset state as long as  $V_{DD}$  remains below this trip point value, and the XTAL1 and XTAL2 oscillator circuitry will be disabled thereby stopping the clock input to the ZLF645 and saving power. If the  $V_{DD}$  level continues to drop below the subVBO trip point, the ZLF645 will remain in a reset state and the VBO comparator circuit will be disabled for further power savings. When the power level returns to a value above the VBO trip point, the device performs a power-on reset and functions normally.

### **STOP Mode**

STOP instruction turns OFF the internal clock and external crystal oscillation, thus reducing the MCU supply current to a very low level. For STOP mode current specifications, see Table 80 on page 165.

To enter STOP mode, first flush the instruction pipeline to avoid suspending execution in mid-instruction. Execute a NOP instruction (OpCode = FFh) immediately before the appropriate sleep instruction, as given below:

| FF | NOP  | ; | clear | the  | pipeline |

|----|------|---|-------|------|----------|

| бF | STOP | ; | enter | STOP | , mode   |

STOP mode is terminated only by a reset, such as WDT time-out, POR, or one of the Stop Mode Recovery events as described in Stop Mode Recovery Event Sources on page 144. This condition causes the processor to restart the application program at address 000Ch.

Unlike a normal POR or WDT reset, a Stop Mode Recovery reset does not reset the contents of some registers and bits. Register bits not reset by a Stop Mode Recovery are highlighted in grey in the register tables. Register bit SMR[7] is set to 1 by a Stop Mode Recovery.

### HALT Mode

HALT instruction turns off the internal CPU clock, but not the XTAL oscillation. The counter/timers, UART, and interrupts (IRQ0, IRQ1, IRQ2, IRQ3, IRQ4, and IRQ5) remain active. The devices are recovered by interrupts, either externally or internally generated. An interrupt request must be executed (enabled) to exit HALT mode. After the interrupt service routine, the program continues from the instruction after HALT mode.

### **AC Characteristics**

Figure 49 and Table 81 lists the alternating current (AC) characteristics of ZLF645 Flash MCU.

Figure 49. AC Timing Diagram

## **Flash Option Bits**

Programmable Flash Option Bits allow user configuration of certain aspects of ZLF645 MCU functionality. This configuration data is stored in the Flash memory Information Block and then read into option byte shadow registers during the last portion of the ZLF645 MCUs reset period.

Features available for control through the Flash Option Bits include:

- Port 0 low nibble pull-ups

- Port 0 high nibble pull-ups

- Port 1 low nibble pull-ups

- Port 1 high nibble pull-ups

- Port 2 pull-ups

- Port 3 low nibble pull-ups

- Port 4 pull-ups

- WDT always enabled

- Flash protect entire main memory

- Flash protect lower half main memory

- XTAL1 to System Clock (no division enable)

- 16-bit Stack addressiblity enable

### Operation

#### **Option Bit Shadow Register Loading By Reset**

For each Flash memory option bit, there is an associated option bit shadow register that is used to register the value of the option bit. The output of the option bit shadow registers are used by the ZLF645 MCU to enable various features and functions for the ZLF645 MCU. Each time the Flash Memory Information Block Option Bits are programmed or erased, the device must be reset for the change in ZLF645 configuration to take effect.

A POR or Stop Mode Recovery Reset with SMR bit 5 set to 1, loads the option bits from the Flash memory to the Option Bit Shadow registers during the last few clock cycles of the reset period. In some cases, in order to provide a required value before being loaded, the Option Bit Shadow registers are reset to a predefined value on the start of the reset period.

## Index

### **Numerics**

11890 **Figure Title** Figure 34. Resets and WDT 138 12-bit address map 47 16-bit counter/timer circuits 109 20-pin package pins 6, 8, 9 PDIP package 179, 183 SOIC package 178 SSOP package 177 28-pin package pins 11, 13, 16 PDIP package 182 SOIC package 181 SSOP package 176, 180 32178 **Figure Title** Figure 17. T8 OUT in MODULO-N Mode 104 40203 **Figure Title** Figure 16. T8 OUT in SINGLE-PASS Mode 104 60053 Table Title Table 32. Stop Mode Recovery Register 2 155 64329 Table Title Table 37. Stop Mode Recovery Register 4 156 8-bit counter/timer circuits 103

### Α

absolute maximum ratings 163 AC characteristics 168, 169 AC timing 168 active low notation 3 address 12-bit linear 47 notation 157 amplifier, infrared 84 AND caution 119 architecture UART 86 asynchronous data 87

### В

baud rate generator description 93 example 94 interrupt 93

Baud Rate Generator Constant register (BCNST)

97, 98

block diagram counter/timer 99 interrupt 128 MCU 4 reset and watch-dog timer 138 UART 86

brown-out, voltage 143

brownout, voltage 139

### С

capacitance 164 caution stopping timer 104 timer count 103 timer modes 121 timer registers 110 UART transmit 88, 89 characteristics AC 168, 169 DC 165 clock 134

190

timer/counter circuit 113 timer/counter configuration 27 overline, in text 3 overrun, UART 91

### Ρ

package diagram 176, 177, 178, 179, 180, 181, 182, 183 package information 176 parity, UART data 87 pin description 5 pin function port 0 20 port 2 21, 28 port 3 23 port 3 summary 26 ping-pong mode 111, 112 pins 20-pin package 6, 8, 9 28-pin package 11, 13, 16 polled UART receive 89 polled UART transmit 87 port 0 configuration 20 pin function 20 Port 0 Mode Register (P01M) 31 Port 0 Register (P0) 32 port 2 configuration 22 pin function 21, 28 Port 2 Mode Register (P2M) 34, 39 Port 2 Register (P2) 33, 35, 40 port 3 configuration 24 counter/timer output 27 pin function 23 pin function 26 Port 3 Mode Register (P3M) 36 Port 3 Register (P3) 37 Port Configuration Register (PCON) 28, 30 power connection 3 power management 137 power-on reset timer 139

program memory map 41 programming summary 157

### R

ratings, maximum 163 register BCNST 98 CTR1 121 CTR3 126 flash high and low byte (FFREQH and FRE-EOL) 79 flash page select (FPS) 77, 78 flash status (FSTAT) 77 HI16 115 HI8 114 ICP control 64 ICP status 65 **IMR 133 IPR 130** IRQ 130, 131 LO16 116 LO8 115 LVD 140 P0 32 P01M 31 P2 33, 35, 40 P2M 34, 39 P3 37 P3M 36 PCON 28, 30 **Register Pointer register 48** RP 48 **SMR 146** SMR1 150 SMR2 152 SMR3 155 SMR4 156 SPL 48, 49 UCTL 96, 97 URDATA 95 **USER 48 UST 95**

191

UTDATA 95 WDTMR 142 register file 12-bit address 47 address summary 50 description 42 memory map 43 register pointer detail 44 example 45 **Register Pointer Register 48** Register Pointer Register (RP) 48 Register Pointer register (RP) 48 reset block diagram 138 delay bypass 143 features 137 POR timer 139 status 143 timer terminal count 119

### S

SCLK signal 135 single-pass mode 104 source interrupt 129 stop mode recovery 144 stop-mode recovery 145, 149, 151 stack 42 Stack Pointer Register (SPL) 48, 49 standard test conditions 164 standby, brown-out 139 standby, brownout 143 status reset 143 **UART 95** stop bit, UART 91 stop mode fast recovery 143 Stop Mode Recovery Register (SMR) 146 Stop Mode Recovery Register 1 (SMR1) 150 Stop Mode Recovery Register 2 (SMR2) 152 Stop Mode Recovery Register 3 (SMR3) 155

Stop Mode Recovery Register 4 (SMR4) 156 stop-mode description 143 recovery events 144, 147, 150, 152 recovery interrupt 144 recovery source 144, 145, 149, 151 recovery status 143 Stop-Mode Recovery Register 4 (SMR4) 156 suffix, h 104 symbols address 157 instruction 159 operand 157

### Т

T16\_OUT signal modulo-N mode 110 T8\_OUT signal modulo-N mode 104 single-pass mode 104 TCLK signal 135 terminal count, reset 119 test conditions 164 test load 164 timer block diagram 99 changing mode 121 description 99 input circuit 100, 101 output circuit 113 output configuration 27 output description 112 reset 139 starting count caution 103 stopping caution 104 T16 demodulation 110 T16 transmit 109 T16 OUT signal 110 T8 demodulation 105 T8 transmit 101 T8\_OUT signal 104 transmit flowchart 102 transmit versus demodulation mode 121

192

Timer 16 Capture High Register (HI16) 115 Timer 16 Capture Low Register (L016) 116 Timer 16 Control register (CTR2) 124 Timer 16 High Hold register (TC16H) 116 Timer 16 Low Hold Register (TC16L) 117 Timer 8 and Timer 16 Common Functions Register (CTR1) 121 Timer 8 Capture High Register (HI8) 114 Timer 8 Capture Low Register (L08) 115 Timer 8 Control Register (CTR0) 119 Timer 8 High Hold Register (TC8H) 117 Timer 8 Low Hold Register (TC8L) 118 Timer 8/Timer 16 Control Register (CTR3) 126 timing, AC 168 transmit caution, UART 88, 89 transmit mode caution 121 flowchart 102 timer 101, 109

### U

UART architecture 86 baud rate generator 93 block diagram 86 data and error handling 91 data format 87 interrupts 90 operation 86 overrun error 91 polled receive 89 polled transmit 87 receive interrupt 89, 90, 92 stop bit 91 transmit caution 88, 89 transmit interrupt 88, 90 UART Control Register (UCTL) 96, 97 UART Receive/Transmit Data Register (URDA-TA/UTDATA) 95 UART Status Register (UST) 95 User Data Register (USER) 48

### V

vector, interrupt 129 voltage brown-out 139, 143 detection 143 detection register 140

### W

Watchdog Timer description 141 watchdog timer diagram 138 Watchdog Timer Mode Register (WDTMR) 142

### X

XTAL1 pin 134 XTAL2 pin 135

### Ζ

ZLR64400 MCU block diagram 4 features 1