# E. Analog Devices Inc./Maxim Integrated - <u>ZLF645E0P2864G Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                    |

|----------------------------|--------------------------------------------------------------------|

| Product Status             | Obsolete                                                           |

| Core Processor             | Z8 LXMC                                                            |

| Core Size                  | 8-Bit                                                              |

| Speed                      | 8MHz                                                               |

| Connectivity               | UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, WDT                             |

| Number of I/O              | 24                                                                 |

| Program Memory Size        | 64KB (64K × 8)                                                     |

| Program Memory Type        | FLASH                                                              |

| EEPROM Size                | -                                                                  |

| RAM Size                   | 1K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.9V ~ 3.6V                                                        |

| Data Converters            | -                                                                  |

| Oscillator Type            | -                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                    |

| Mounting Type              | Through Hole                                                       |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                           |

| Supplier Device Package    | 28-PDIP                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/zlf645e0p2864g |

|                            |                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

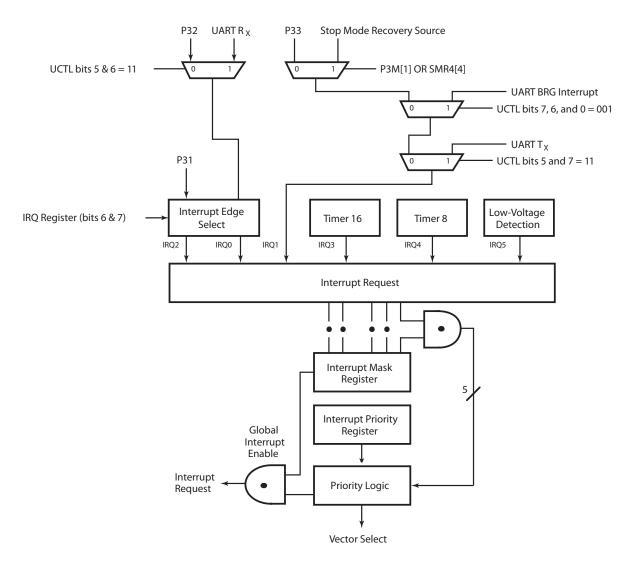

## **Interrupt Sources**

The ZLF645 MCU supports 23 interrupt sources with 6 interrupt vectors, as given below:

- Three external interrupts.

- Two from T8, T16 time-out and capture.

- Three from UART Tx, UART Rx, and UART BRG.

- One from LVD.

- Fourteen from SMR source P20-P27, P30-P33, P00, and P07:

- Any change in logic from P20-P27, P30-P33 can generate an interrupt or SMR

## **Additional Features**

The additional features of ZLF645 MCU include:

- IR learning amplifier.

- Low power consumption—11 mW (typical).

- Three standby modes:

- STOP—1.7  $\mu$ A (typical)

- HALT-0.6 mA (typical)

- Low-voltage reset

- Intelligent counter/timer architecture to automate generation or reception and demodulation of complex waveform, and pulsed signals:

- One programmable 8-bit counter/timer with two capture registers and two load registers

- One programmable 16-bit counter/timer with one 16-bit capture register pair and one 16-bit load register pair

- Programmable input glitch filter for pulse reception

- The UART baud rate generator can be used as another 8-bit timer, when the UART is not in use

- Six priority interrupts:

- Three external/UART interrupts

- Two assigned to counter/timers

- One low-voltage detection interrupt

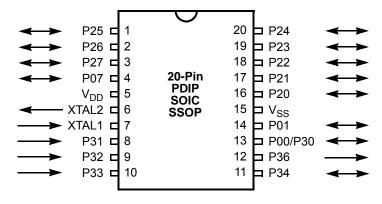

Figure 3 displays the pin configuration for ZLF645 MCU 20-pin PDIP, SOIC, and SSOP packages.

Figure 3. 20-Pin PDIP/SOIC/SSOP Pin Configuration

8

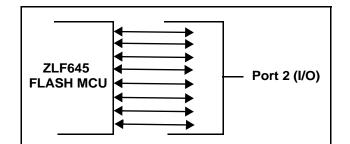

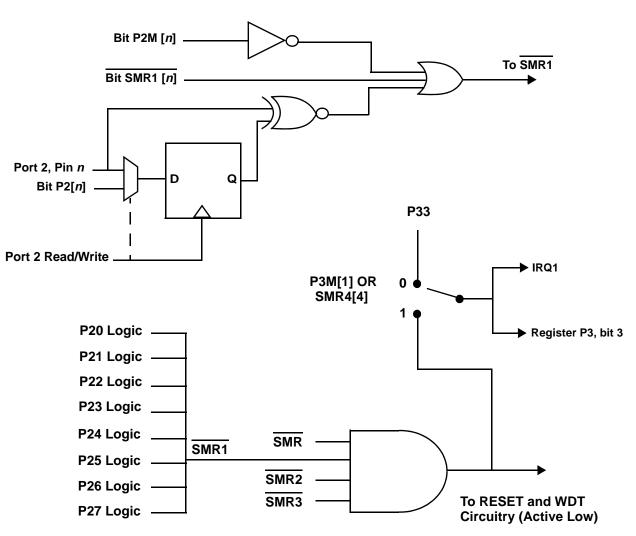

## Port 2

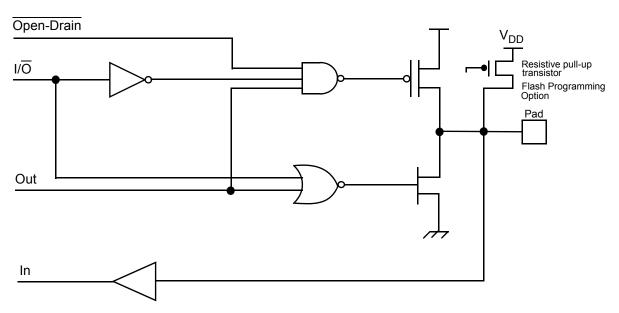

Port 2 is an 8-bit bidirectional CMOS-compatible I/O port. Its eight I/O lines can be independently configured under software control as inputs or outputs. Port 2 is always available for I/O operation. A flash programming option bit is available to connect eight pull-up transistors on this port. Bits programmed as outputs are globally programmed as either push/pull or open-drain. The Power-On Reset function resets with the eight bits of Port 2 [P27:20] configured as inputs.

Port 2 also has an 8-bit input OR and AND gate and edge detection circuitry, which can be used to recover from the STOP mode. P20 can be programmed to access the edge-detection circuitry in DEMODULATION mode. Figure 8 displays the Port 2 configuration.

Figure 8. Port 2 Configuration

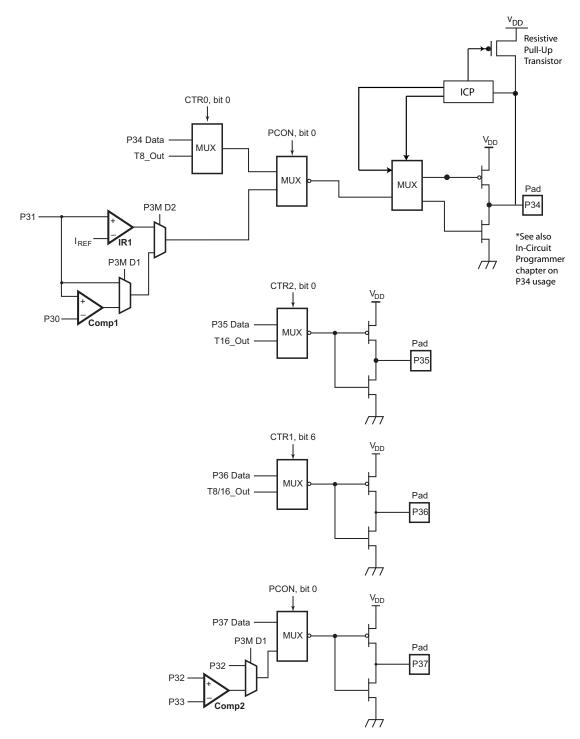

Figure 10. Port 3 Counter/Timer Output Configuration

# **Port Configuration Register**

The Port Configuration register (see Table 13) configures the Port 0 output mode and the comparator output on Port 3. The PCON register is located in expanded register Bank F, address 00h.

## Table 13. Port Configuration Register (PCON)

| Bit     | 7 | 7 6 5 4 3 2 1 0           |       |   |                       |                       |                       |                              |  |  |

|---------|---|---------------------------|-------|---|-----------------------|-----------------------|-----------------------|------------------------------|--|--|

| Field   |   | Rese                      | erved |   | Port 4<br>Output Mode | Port 0<br>Output Mode | Port 1<br>Output Mode | Comp/IR Amp<br>Output Port 3 |  |  |

| Reset   | Х | Х                         | Х     | Х | 1                     | 1                     | 1                     | 0                            |  |  |

| R/W     |   | w w w w                   |       |   |                       |                       |                       |                              |  |  |

| Address |   | Bank F: 00h; Linear: F00h |       |   |                       |                       |                       |                              |  |  |

| Bit Position | Value | Description                                                             |

|--------------|-------|-------------------------------------------------------------------------|

| [7:4] —      |       | Reserved—Must be written to 1; reads 11111b.                            |

| [3]          |       | Port 4 Output Mode—Controls the output mode of Port 4.                  |

|              | 0     | Open-drain                                                              |

|              | 1     | Push/pull                                                               |

| [2]          |       | Port 0 Output Mode—Controls the output mode of Port 0.                  |

|              |       | Write only; read returns 1.                                             |

|              | 0     | Open-drain                                                              |

|              | 1     | Push/pull                                                               |

| [1]          |       | Port 1 Output Mode—Controls the output mode of Port 1.                  |

|              |       | Write only, read returns 1                                              |

|              | 0     | Open-drain                                                              |

|              | 1     | Push/pull                                                               |

| [0]          |       | Comparator or IR Amplifier Output Port 3—Select digital outputs or      |

|              |       | comparator, and IR amplifier outputs on P34 and P37.                    |

|              |       | Write only; read returns 1.                                             |

|              | 0     | P34 and P37 outputs are digital.                                        |

|              | 1     | P34 is Comparator 1 or IR Amplifier output, P37 is Comparator 2 output. |

**Note:** *PCON register is not reset after a Stop Mode Recovery. Also, for package types other than the 48-pin package, writes to bit 3 and bit 1 have no effect.*

>

# **Register File Summary**

Table 26 lists each linear (12-bit) register file address to the associated register, mnemonic, and reset value. The table also lists the register bank (or banks) and corresponding 8-bit address (if any) for each register and a page link to the detailed register table.

Throughout this document, an 'X' denotes an undefined digit. A '—' (dash) in a table cell indicates that the corresponding attribute does not apply to the listed item. Reset value digits (highlighted in grey) are not reset by a Stop Mode Recovery. Register bit SMR[7] (shown in **boldface**) is set to 1 instead of reset by a Stop Mode recovery.

| Bank  | 8-Bit                                                                                                                                                      | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Mnemonic                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0–3   | 00                                                                                                                                                         | Port 0 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P0                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0–3   | 01                                                                                                                                                         | Port 1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P1                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0–3   | 02                                                                                                                                                         | Port 2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P2                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0–3   | 03                                                                                                                                                         | Port 3 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P3                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0Xh                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0–3   | 04                                                                                                                                                         | Port 4 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P4                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0     | 05–0F                                                                                                                                                      | General-Purpose Registers<br>(Bank 0 Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0,D,F | 10–EF                                                                                                                                                      | General-Purpose Registers<br>(Banks 0, D, F)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| All   | F0                                                                                                                                                         | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                                         | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| All   | F1                                                                                                                                                         | UART Receive/Transmit Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | URDATA/<br>UTDATA                                                                                                                                                                                                                                                                                                                                                                                                                                         | XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| All   | F2                                                                                                                                                         | UART Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | UST                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0000_0010b                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| All   | F3                                                                                                                                                         | UART Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | UCTL                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| All   | F4                                                                                                                                                         | UART Baud Rate Generator Constant Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BCNST                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| All   | F5                                                                                                                                                         | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| All   | F6                                                                                                                                                         | Port 2 Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P2M                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| All   | F7                                                                                                                                                         | Port 3 Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P3M                                                                                                                                                                                                                                                                                                                                                                                                                                                       | XXXX_X000b                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| All   | F8                                                                                                                                                         | Port 0/1 Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P01M                                                                                                                                                                                                                                                                                                                                                                                                                                                      | X1XX_1XX1b                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 0–3<br>0–3<br>0–3<br>0–3<br>0,–3<br>0<br>0,–3<br>0<br>0,–3<br>0<br>0,–3<br>0<br>0<br>4<br>1<br>All<br>All<br>All<br>All<br>All<br>All<br>All<br>All<br>All | 0-3       01         0-3       02         0-3       03         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       04         0-3       05         0-4       F1         0-5       F3         0-6       F5         0-1       F6         0-1       F7 | 0-300Port 0 Register0-301Port 1 Register0-302Port 2 Register0-303Port 3 Register0-304Port 4 Register0-304Port 4 Register005-0FGeneral-Purpose Registers<br>(Bank 0 Only)0,D,F10-EFGeneral-Purpose Registers<br>(Banks 0, D, F)AllF0ReservedAllF1UART Receive/Transmit Data RegisterAllF2UART Status RegisterAllF3UART Control RegisterAllF5ReservedAllF5ReservedAllF5ReservedAllF5ReservedAllF5ReservedAllF6Port 2 Mode RegisterAllF7Port 3 Mode Register | 0-300Port 0 RegisterP00-301Port 1 RegisterP10-302Port 2 RegisterP20-303Port 3 RegisterP30-304Port 4 RegisterP4005-0FGeneral-Purpose Registers<br>(Bank 0 Only)0,D,F10-EFGeneral-Purpose Registers<br>(Banks 0, D, F)AllF0ReservedAllF1UART Receive/Transmit Data Register<br>UTDATA<br>UTDATAUSTAllF2UART Status RegisterUCTLAllF3UART Control Register<br>RegisterUCTLAllF5ReservedAllF5ReservedP2MAllF5ReservedP2MAllF5Port 2 Mode RegisterP2MAllF7Port 3 Mode RegisterP3M | 0-300Port 0 RegisterP0XXh0-301Port 1 RegisterP1XXh0-302Port 2 RegisterP2XXh0-303Port 3 RegisterP30Xh0-304Port 4 RegisterP4XXh005-0FGeneral-Purpose Registers<br>(Bank 0 Only)XXh0,D,F10-EFGeneral-Purpose Registers<br>(Banks 0, D, F)XXhAllF0ReservedAllF1UART Receive/Transmit Data Register<br>(UTDATA0000_0010bAllF3UART Control RegisterUCTL00hAllF4UART Baud Rate Generator Constant<br>RegisterBCNSTFFhAllF5ReservedAllF5ReservedAllF7Port 3 Mode RegisterP3MXXXX_X000b |

## Table 26. Register File Address Summary

Address (Hex)

19-4572; Rev 0; 4/09

This command when executed returns a value of 0132H which is the revision ID assigned for the ZLF645 MCU.

• **Read ICP Status Register (02H)**—The Read ICP Status register command reads the ICPSTAT register.

```

ICP \leftarrow 02H

ICP \rightarrow ICPSTAT[7:0]

```

• Write ICP Control Register (04H)—The Write ICP Control register command writes the data that follows the command to the ICPCTL register.

```

ICP \leftarrow 04H

ICP \leftarrow ICPCTL[7:0]

```

• **Read ICP Control Register (05H)**—The Read ICP Control register command reads the value of the ICPCTL register.

```

ICP \leftarrow 05H

ICP \rightarrow ICPCTL[7:0]

```

• Write Flash Controller Registers (08H)—The Write Flash Controller register command allows writes to the Flash Controller registers. This command configures the Flash Controller for Flash memory accesses through the Write Flash Memory and Read Flash Memory commands. If the device is not in FLASH CONTROL mode, the register address and data values are discarded.

```

ICP \leftarrow 08H

ICP \leftarrow Register Address[15:0] ("OFH" for all Flash Ctrl Regs)

ICP \leftarrow Register Address[7:0]

ICP \leftarrow Size[7:0]

ICP \leftarrow 1-256 data bytes

```

Read Flash Controller Registers (09H)—The Read Flash Controller command allows reads of the Flash Controller registers. If the device is not in FLASH CONTROL mode this command returns FFH for all the register values.

```

ICP \leftarrow 09H

ICP \leftarrow Register Address[15:0] ("OFH" for all Flash Ctrl Regs)

ICP \leftarrow Register Address[7:0]

ICP \leftarrow Size[7:0]

ICP \rightarrow 1-256 data bytes

```

• Write Flash Memory (0AH)—The Write Flash Memory command is used to write data to the main memory area or Information Area of the Flash memory. The command has equivalent functionality to the CPU writing the memory through the LDC and LDCI instructions. Data can be written 1 to memsize bytes at a time where memsize represents the size (32 KB or 64 KB) of the Flash memory for the product option chosen (The memsize number of bytes can be written by setting the size to 0). Should a size value greater than the maximum memory size be given by the user, the actual size value

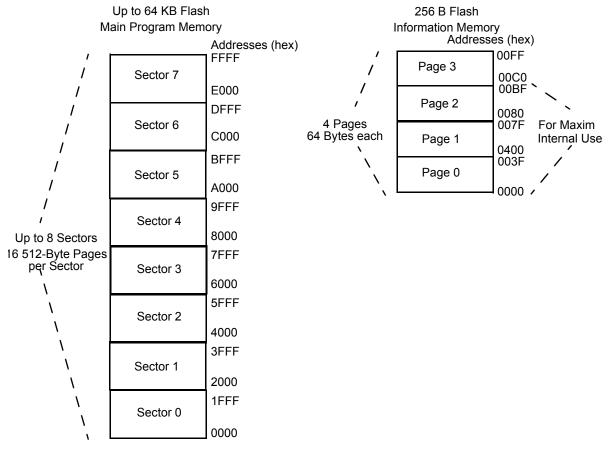

Figure 19. Flash Memory Arrangement

## **Flash Information Block**

The Flash Information Block of Flash memory is divided into two sections. Page 3 of the Information Block is accessible by you or Flash programmer vendor for programming, reading, or erasure through the ZLF645's ICP interface or it's Flash Byte Programming Interface only, as described in the section Flash Byte Programming Interface on page 82. The CPU has no access to this area of memory. User Option Bytes 0 and 1 use addresses 00FE and 00FF respectively of the Page 3 area and contain programmable bits with pre-defined functions.

The Flash read/write protect bits in User Option Byte 1 control the level of Page 3 access allowed to you along with the User's level of access to the Flash's main memory. Bytes 00C0 through 00FD of Page 3 have no pre-defined function and are available to you for other operations.

# UART Receive Data Register/UART Transmit Data Register

The UART Receive/Transmit Data register (see Table 43) is used to send and retrieve data from the UART channel. When the UART receives a data byte, it can be read from this register. The UART receive interrupt is cleared when this register is used. Data written to this register is transmitted by the UART.

## Table 43. UART Receive/Transmit Data Register (URDATA/UTDATA)

| Bit          | 7 6 5 4 3 2 1 0                     |                 |       |  |  |  |  |  |  |  |

|--------------|-------------------------------------|-----------------|-------|--|--|--|--|--|--|--|

| Field        | UART Receive/Transmit               |                 |       |  |  |  |  |  |  |  |

| Reset        | Х                                   | x x x x x x x x |       |  |  |  |  |  |  |  |

| R/W          | R/W R/W R/W R/W R/W R/W R/W         |                 |       |  |  |  |  |  |  |  |

| Address      | Bank Independent: F1h; Linear: 0F1h |                 |       |  |  |  |  |  |  |  |

| Bit Position | on Description                      |                 |       |  |  |  |  |  |  |  |

| [7:0]        | UART R                              | eceive/Tra      | nsmit |  |  |  |  |  |  |  |

# UART Status Register

When read, returns received data. When written, transmits written data.

The UART Status register (see Table 44) displays the status of the UART. Bits [6:3] are cleared by reading the UART Receive/Transmit register (F1h).

#### Table 44. UART Status Register (UST)

| Bit         | 7                                                                      | 6                                   | 0       |         |       |          |          |        |  |

|-------------|------------------------------------------------------------------------|-------------------------------------|---------|---------|-------|----------|----------|--------|--|

|             | Receive                                                                | Parity                              | Overrun | Framing | Break | Transmit | Transmit | Noise  |  |

| Field       | Status                                                                 | Error                               | Error   | Error   |       | Data     | Complete | Filter |  |

| Reset       | 0                                                                      | 0                                   | 0       | 0       | 0     | 0        | 1        | 0      |  |

| R/W         | R/W                                                                    | W R/W R/W R/W R/W R/W R/W R/W       |         |         |       |          |          | R/W    |  |

| Address     | Bank Independent: F2h; Linear: 0F2h                                    |                                     |         |         |       |          |          |        |  |

| Bit Positio | n Value                                                                | Descripti                           | on      |         |       |          |          |        |  |

| [7]         | Receive Status—Set when data is received; cleared when URDATA is read. |                                     |         |         |       |          |          |        |  |

|             | 0                                                                      | 0 UART Receive Data register empty. |         |         |       |          |          |        |  |

|             | 1 UART Receive Data register full.                                     |                                     |         |         |       |          |          |        |  |

100

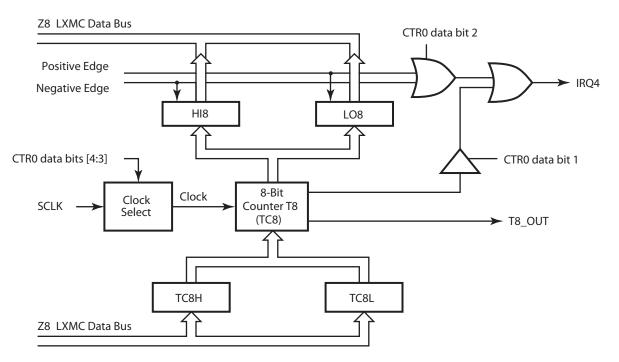

Table 47 summarizes the timer control registers. Some timer functions can also be affected by control registers for other peripheral functions.

| <br>              |  |

|-------------------|--|

| <br>Address (Hex) |  |

Table 47. Timer Control Registers

| 12-Bit | Bank | 8-Bit | Register Description                  | Mnemonic | Reset      | Page<br>No |

|--------|------|-------|---------------------------------------|----------|------------|------------|

| D00    | D    | 00    | Counter/Timer 8 Control Register      | CTR0     | 0000_0000b | 119        |

| D01    | D    | 01    | Timer 8 and Timer 16 Common Functions | CTR1     | 0000_0000b | 121        |

| D02    | D    | 02    | Counter/Timer 16 Control Register     | CTR2     | 0000_000b  | 124        |

| D03    | D    | 03    | Timer 8/Timer 16 Control Register     | CTR3     | 0000_0XXXb | 126        |

| D04    | D    | 04    | Counter/Timer 8 Low Hold Register     | TC8L     | 00h        | 118        |

| D05    | D    | 05    | Counter/Timer 8 High Hold Register    | TC8H     | 00h        | 117        |

| D06    | D    | 06    | Counter/Timer 16 Low Hold Register    | TC16L    | 00h        | 117        |

| D07    | D    | 07    | Counter/Timer 16 High Hold Register   | TC16H    | 00h        | 116        |

| D08    | D    | 08    | Timer 16 Capture Low Register         | LO16     | 00h        | 116        |

| D09    | D    | 09    | Timer 16 Capture High Register        | HI16     | 00h        | 115        |

| D0A    | D    | 0A    | Timer 8 Capture Low Register          | LO8      | 00h        | 115        |

| D0B    | D    | 0B    | Timer 8 Capture High Register         | HI8      | 00h        | 114        |

## **Counter/Timer Functional Blocks**

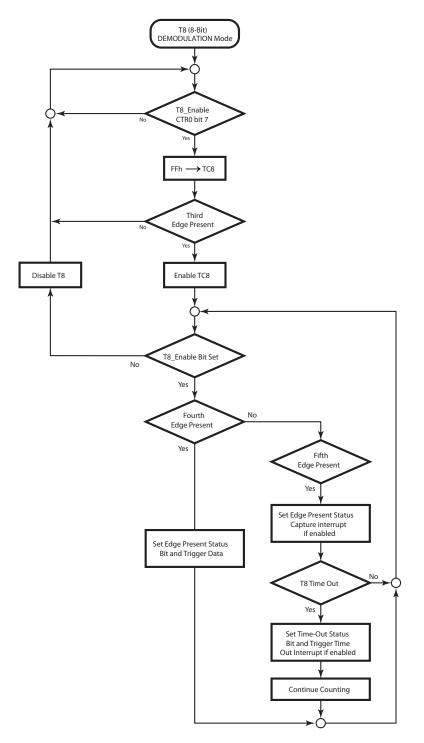

The ZLF645 MCU infrared timer contains a glitch filter for removing noise from the input when demodulating an input carrier. Each timer features its own demodulating mode and can be simultaneously used to generate a signal output. The T8 timer has the ability to capture only one cycle of a carrier wave of a high-frequency waveform.

## Input Circuit

Depending on the setting of register bits P3M[2:1] and CTR1[6], the timer/counter input circuit monitors one of the following conditions:

- The P31 digital signal, if CTR1[6]=0 and P3M[2:1]=00.

- The P31 analog comparator output, if CTR1[6]=0 and P3M[2:1]=01.

- The P31 IR amplifier output, if CTR1[6]=0 and P3M[2]=1.

- The P20 digital signal, if CTR1[6]=1.

When T8 is enabled, the output T8\_OUT switches to the initial value (CTR1, bit 1). If the initial value (CTR1, bit 1) is 0, TC8L is loaded; otherwise, TC8H is loaded into the counter.

In SINGLE-PASS mode (CTR0, bit 6), T8 counts down to 0 and stops, T8\_OUT toggles, the time-out status bit (CTR0, bit 5) is set, and a time-out interrupt can be generated if it is enabled (CTR0, bit 1).

In MODULO-N mode, on reaching terminal count, T8\_OUT is toggled, but no interrupt is generated. From that point, T8 loads a new count (if the T8\_OUT level now is 0), TC8L is loaded; if it is 1, TC8H is loaded. T8 counts down to 0, toggles T8\_OUT, and sets the time-out status bit (CTR0, bit 5), thereby generating an interrupt if enabled (CTR0, bit 1). One cycle is thus completed. T8 then loads from TC8H or TC8L according to the T8\_OUT level and repeats the cycle. See Figure 29.

Figure 29. 8-Bit Counter/Timer Circuits

You can modify the values in TC8H or TC8L at any time. The new values take effect when they are loaded.

**Caution:** An initial count of 1 is not allowed (a non-function occurs). An initial count of 0 causes TC8 to count from 0 to FFh to FEh.

<u>/!</u>\

107

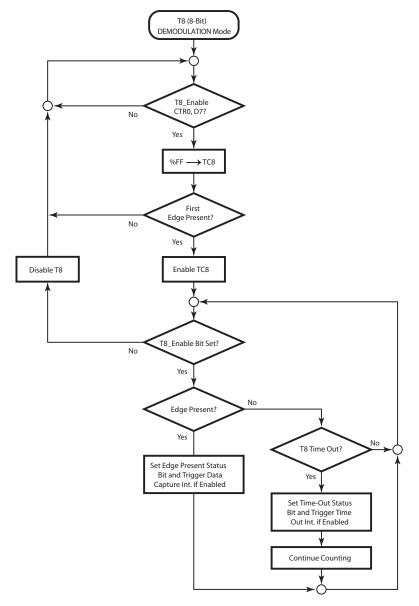

Figure 33. DEMODULATION Mode Flowchart

Figure 34. DEMODULATION Mode Flowchart with Bit 4 of CTR3 Set

## **Counter/Timer 16 Low Hold Register**

The Counter/Timer 16 Low Hold register (see Table 53) contains the low byte of the value loaded into the T16 timer.

**Note:** This register is not reset after a Stop Mode Recovery.

## Table 53. Counter/Timer 16 Low Hold Register (TC16L)

| Bit                            | 7                         | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5        | 4            | 3 | 2 | 1 | 0 |  |  |

|--------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|---|---|---|---|--|--|

| Field                          |                           | T16_Data_LO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |              |   |   |   |   |  |  |

| Reset                          | 0                         | 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |              |   |   |   |   |  |  |

| R/W                            | R/W                       | R/W         R/W |          |              |   |   |   |   |  |  |

| Address                        | Bank D: 06h; Linear: D06h |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |              |   |   |   |   |  |  |

| Bit Position Value Description |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |              |   |   |   |   |  |  |

| [7:0]                          | 0hh–FFh                   | T16_Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _LO—Read | I/Write Data |   |   |   |   |  |  |

## **Counter/Timer 8 High Hold Register**

The Counter/Timer 8 High Hold register (see Table 54) contains the value to be counted while the T8 output is 1.

Note: This register is not reset after a Stop Mode Recovery.

## Table 54. Counter/Timer 8 High Hold Register (TC8H)

| Field         T8_Level_HI           Reset         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <t< th=""><th>Bit</th><th>7</th><th colspan="11">7 6 5 4 3 2 1 0</th></t<>                                                                                               | Bit     | 7                         | 7 6 5 4 3 2 1 0                                                 |  |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------|-----------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Field   |                           | T8_Level_HI                                                     |  |  |  |  |  |  |  |  |  |  |

| R/W         R/W <th>Reset</th> <th>0</th> <th colspan="8">0 0 0 0 0 0 0 0 0</th> | Reset   | 0                         | 0 0 0 0 0 0 0 0 0                                               |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W     | R/W                       | R/W         R/W         R/W         R/W         R/W         R/W |  |  |  |  |  |  |  |  |  |  |

| Address Bank D: 05h; Linear: D05h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Address | Bank D: 05h; Linear: D05h |                                                                 |  |  |  |  |  |  |  |  |  |  |

| Bit Position | Value   | Description                  |

|--------------|---------|------------------------------|

| [7:0]        | 0hh–FFh | T8_Level_HI—Read/Write Data. |

Figure 40. Interrupt Block Diagram

| <b>Bit Position</b> | Value | Description                   |

|---------------------|-------|-------------------------------|

| {[4:3], [0]}        |       | Group Priority                |

|                     | 000   | Reserved                      |

|                     | 001   | C > A > B                     |

|                     | 010   | A > B > C                     |

|                     | 011   | A > C > B                     |

|                     | 100   | B > C > A                     |

|                     | 101   | C > B > A                     |

|                     | 110   | B > A > C                     |

|                     | 111   | Reserved                      |

| [2]                 |       | Group B Priority (IRQ0, IRQ2) |

|                     | 0     | IRQ2 > IRQ0                   |

|                     | 1     | IRQ0 > IRQ2                   |

| [1]                 |       | Group C Priority (IRQ1, IRQ4) |

|                     | 0     | IRQ1 > IRQ4                   |

|                     | 1     | IRQ4 > IRQ1                   |

# Interrupt Request Register