Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 120MHz                                                                 |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART, USB, USB OTG |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                              |

| Number of I/O              | 64                                                                     |

| Program Memory Size        | 1MB (1M x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                           |

| Data Converters            | A/D 38x16b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 121-LFBGA                                                              |

| Supplier Device Package    | 121-MAPBGA (8x8)                                                       |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mk22fn1m0vmc12            |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Ordering Information<sup>1</sup>

| Part Number    | Mer        | nory      | Maximum number of I\O's |

|----------------|------------|-----------|-------------------------|

|                | Flash (KB) | SRAM (KB) |                         |

| MK22FX512VMC12 | 512 KB     | 128       | 86                      |

| MK22FN1M0VMC12 | 1 MB       | 128       | 86                      |

1. To confirm current availability of ordererable part numbers, go to http://www.freescale.com and perform a part number search.

#### **Related Resources**

| Туре                | Description                                                                                                                      | Resource                                    |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Selector<br>Guide   | The Freescale Solution Advisor is a web-based tool that features interactive application wizards and a dynamic product selector. | Solution Advisor                            |

| Product Brief       | The Product Brief contains concise overview/summary information to enable quick evaluation of a device for design suitability.   | K20PB <sup>1</sup>                          |

| Reference<br>Manual | The Reference Manual contains a comprehensive description of the structure and function (operation) of a device.                 | K22P121M50SF5RM <sup>1</sup>                |

| Data Sheet          | The Data Sheet includes electrical characteristics and signal connections.                                                       | K22P121M50SF5 <sup>1</sup>                  |

| Package<br>drawing  | Package dimensions are provided in package drawings.                                                                             | MAPBGA 121-pin:<br>98ASA00344D <sup>1</sup> |

1. To find the associated resource, go to http://www.freescale.com and perform a search using this term.

## 2.2.3 Voltage and current operating behaviors Table 4. Voltage and current operating behaviors

| Symbol           | Description                                                                                          | Min.                  | Тур   | Max. | Unit | Notes            |

|------------------|------------------------------------------------------------------------------------------------------|-----------------------|-------|------|------|------------------|

| V <sub>OH</sub>  | Output high voltage — high drive strength                                                            |                       |       |      |      |                  |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -8mA                                  | V <sub>DD</sub> – 0.5 | —     | _    | v    |                  |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OH</sub> = -3mA                                 | V <sub>DD</sub> – 0.5 | —     | _    | V    |                  |

|                  | Output high voltage — low drive strength                                                             |                       |       |      |      |                  |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -2mA                                  | V <sub>DD</sub> – 0.5 | —     | _    | V    |                  |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OH</sub> = -0.6mA                               | V <sub>DD</sub> – 0.5 | —     | _    | V    |                  |

| I <sub>OHT</sub> | Output high current total for all ports                                                              |                       |       | 100  | mA   |                  |

| V <sub>OL</sub>  | Output low voltage — high drive strength                                                             |                       |       |      |      | 1                |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 9mA                                   | _                     | —     | 0.5  | V    |                  |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OL}} = 3\text{mA}$    | _                     | —     | 0.5  | V    |                  |

|                  | Output low voltage — low drive strength                                                              |                       |       |      |      | -                |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 2mA                                   | —                     | —     | 0.5  | V    |                  |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OL}} = 0.6 \text{mA}$ | —                     | —     | 0.5  | V    |                  |

| I <sub>OLT</sub> | Output low current total for all ports                                                               |                       |       | 100  | mA   |                  |

| I <sub>IND</sub> | Input leakage current, digital pins<br>• $V_{SS} \le V_{IN} \le V_{IL}$                              |                       |       |      |      | <sup>2</sup> , 3 |

|                  | All digital pins                                                                                     | _                     | 0.002 | 0.5  | μA   |                  |

|                  | • V <sub>IN</sub> = V <sub>DD</sub>                                                                  |                       |       |      |      |                  |

|                  | All digital pins except PTD7                                                                         | _                     | 0.002 | 0.5  | μA   |                  |

|                  | • PTD7                                                                                               | —                     | 0.004 | 1    | μA   |                  |

| I <sub>IND</sub> | Input leakage current, digital pins<br>• V <sub>IL</sub> < V <sub>IN</sub> < V <sub>DD</sub>         |                       |       |      |      | 2                |

|                  | • V <sub>DD</sub> = 3.6 V                                                                            | _                     | 18    | 26   | μA   |                  |

|                  | • V <sub>DD</sub> = 3.0 V                                                                            | _                     | 12    | 19   | μΑ   |                  |

|                  | • V <sub>DD</sub> = 2.5 V                                                                            |                       | 8     | 13   | μΑ   |                  |

|                  | • V <sub>DD</sub> = 1.7 V                                                                            |                       | 3     | 6    | μΑ   |                  |

| I <sub>IND</sub> | Input leakage current, digital pins                                                                  |                       |       |      |      |                  |

|                  | • $V_{DD} < V_{IN} < 5.5 V$                                                                          |                       | 1     | 50   | μA   |                  |

| I <sub>OZ</sub>  | Hi-Z (off-state) leakage current (per pin)                                                           | —                     |       | 0.25 | μA   |                  |

| R <sub>PU</sub>  | Internal pullup resistors                                                                            | 20                    | 35    | 50   | kΩ   | 4                |

| R <sub>PD</sub>  | Internal pulldown resistors                                                                          | 20                    | 35    | 50   | kΩ   | 5                |

1. Open drain outputs must be pulled to  $V_{DD}$ .

- 2. Measured at VDD=3.6V

- 3. Internal pull-up/pull-down resistors disabled.

- 4. Measured at  $V_{\text{DD}}$  supply voltage =  $V_{\text{DD}}$  min and Vinput =  $V_{\text{SS}}$

5. Measured at  $V_{DD}$  supply voltage =  $V_{DD}$  min and Vinput =  $V_{DD}$

## 2.2.4 Power mode transition operating behaviors

All specifications except  $t_{POR}$ , and VLLSx $\rightarrow$ RUN recovery times in the following table assume this clock configuration:

- CPU and system clocks = 100 MHz

- Bus clock = 50 MHz

- FlexBus clock = 50 MHz

- Flash clock = 25 MHz

#### Table 5. Power mode transition operating behaviors

| Symbol           | Description                                                                                                                                                        | Min. | Max. | Unit | Notes |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>POR</sub> | After a POR event, amount of time from the point $V_{DD}$ reaches 1.71 V to execution of the first instruction across the operating temperature range of the chip. | _    | 300  | μs   |       |

|                  | • VLLS0 $\rightarrow$ RUN                                                                                                                                          | —    | 183  | μs   |       |

|                  | • VLLS1 → RUN                                                                                                                                                      | _    | 183  | μs   |       |

|                  | • VLLS2 $\rightarrow$ RUN                                                                                                                                          | _    | 105  | μs   |       |

|                  | • VLLS3 $\rightarrow$ RUN                                                                                                                                          | —    | 105  | μs   |       |

|                  | • LLS → RUN                                                                                                                                                        | —    | 5.0  | μs   |       |

|                  | • VLPS $\rightarrow$ RUN                                                                                                                                           | —    | 4.4  | μs   |       |

|                  | • STOP → RUN                                                                                                                                                       | —    | 4.4  | μs   |       |

# 2.2.5 Power consumption operating behaviors

Table 6. Power consumption operating behaviors

| Symbol              | Description                                                                  | Min. | Тур.  | Max.     | Unit | Notes |

|---------------------|------------------------------------------------------------------------------|------|-------|----------|------|-------|

| I <sub>DDA</sub>    | Analog supply current                                                        | —    | —     | See note | mA   | 1     |

| I <sub>DD_RUN</sub> | Run mode current — all peripheral clocks disabled, code executing from flash |      |       |          |      | 2     |

|                     |                                                                              | —    | 33.57 | 36.2     | mA   |       |

|                     |                                                                              | —    | 33.51 | 36.1     | mA   |       |

Table continues on the next page...

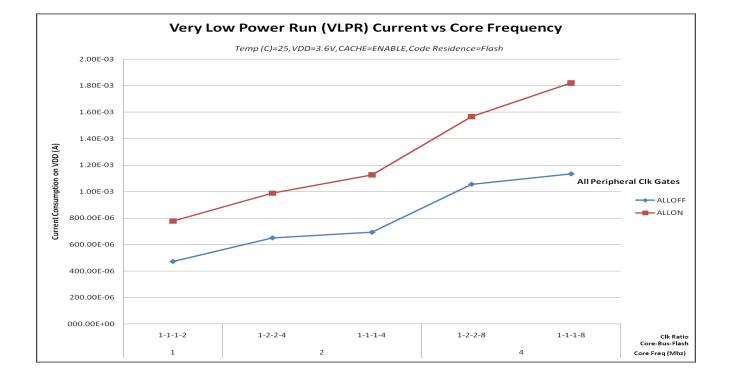

Figure 4. VLPR mode supply current vs. core frequency

## 2.2.6 EMC radiated emissions operating behaviors Table 7. EMC radiated emissions operating behaviors

| Symbol              | Description                        | Frequency<br>band<br>(MHz) | Тур. | Unit | Notes |

|---------------------|------------------------------------|----------------------------|------|------|-------|

| V <sub>RE1</sub>    | Radiated emissions voltage, band 1 | 0.15–50                    | 23   | dBµV | 1, 2  |

| V <sub>RE2</sub>    | Radiated emissions voltage, band 2 | 50–150                     | 27   | dBµV |       |

| V <sub>RE3</sub>    | Radiated emissions voltage, band 3 | 150–500                    | 28   | dBµV |       |

| V <sub>RE4</sub>    | Radiated emissions voltage, band 4 | 500-1000                   | 14   | dBµV |       |

| V <sub>RE_IEC</sub> | IEC level                          | 0.15–1000                  | К    |      | 2, 3  |

Determined according to IEC Standard 61967-1, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 1: General Conditions and Definitions and IEC Standard 61967-2, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 2: Measurement of Radiated Emissions—TEM Cell and Wideband TEM Cell Method. Measurements were made while the microcontroller was running basic application code.

The reported emission level is the value of the maximum measured emission, rounded up to the next whole number, from among the measured orientations in each frequency range.

- 2.  $V_{DD} = 3.3 \text{ V}$ ,  $T_A = 25 \text{ °C}$ ,  $f_{OSC} = 12 \text{ MHz}$  (crystal),  $f_{SYS} = 96 \text{ MHz}$ ,  $f_{BUS} = 48 \text{MHz}$

- 3. Specified according to Annex D of IEC Standard 61967-2, Measurement of Radiated Emissions TEM Cell and Wideband TEM Cell Method

## 2.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

## 2.2.8 Capacitance attributes

#### Table 8. Capacitance attributes

| Symbol            | Description                     | Min. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|

| C <sub>IN_A</sub> | Input capacitance: analog pins  | -    | 7    | pF   |

| C <sub>IN_D</sub> | Input capacitance: digital pins | _    | 7    | pF   |

# 2.3 Switching specifications

# 2.3.1 Device clock specifications

#### Table 9. Device clock specifications

| Symbol               | Description                                            | Min. | Max. | Unit | Notes |

|----------------------|--------------------------------------------------------|------|------|------|-------|

|                      | Normal run mode                                        | Э    |      |      |       |

| f <sub>SYS</sub>     | System and core clock                                  | _    | 120  | MHz  |       |

| f <sub>SYS_USB</sub> | System and core clock when Full Speed USB in operation | 20   | _    | MHz  |       |

| f <sub>BUS</sub>     | Bus clock                                              | —    | 60   | MHz  |       |

| FB_CLK               | FlexBus clock                                          | —    | 50   | MHz  |       |

| f <sub>FLASH</sub>   | Flash clock                                            | —    | 25   | MHz  |       |

| f <sub>LPTMR</sub>   | LPTMR clock                                            | —    | 25   | MHz  |       |

|                      | VLPR mode <sup>1</sup>                                 |      |      |      |       |

| f <sub>SYS</sub>     | System and core clock                                  | _    | 4    | MHz  |       |

| f <sub>BUS</sub>     | Bus clock                                              | _    | 4    | MHz  |       |

Table continues on the next page ...

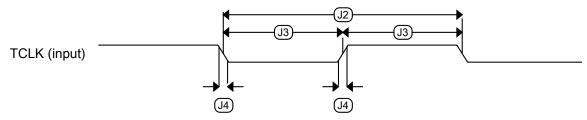

| Symbol | Description                                        | Min. | Max. | Unit |

|--------|----------------------------------------------------|------|------|------|

|        | Boundary Scan                                      | 0    | 10   |      |

|        | JTAG and CJTAG                                     | 0    | 25   |      |

|        | Serial Wire Debug                                  | 0    | 50   |      |

| J2     | TCLK cycle period                                  | 1/J1 |      | ns   |

| J3     | TCLK clock pulse width                             |      |      |      |

|        | Boundary Scan                                      | 50   | _    | ns   |

|        | JTAG and CJTAG                                     | 20   | _    | ns   |

|        | Serial Wire Debug                                  | 10   | —    | ns   |

| J4     | TCLK rise and fall times                           |      | 3    | ns   |

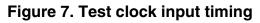

| J5     | Boundary scan input data setup time to TCLK rise   | 20   | —    | ns   |

| J6     | Boundary scan input data hold time after TCLK rise | 2.6  | _    | ns   |

| J7     | TCLK low to boundary scan output data valid        | _    | 25   | ns   |

| J8     | TCLK low to boundary scan output high-Z            | —    | 25   | ns   |

| J9     | TMS, TDI input data setup time to TCLK rise        | 8    | _    | ns   |

| J10    | TMS, TDI input data hold time after TCLK rise      | 1    | _    | ns   |

| J11    | TCLK low to TDO data valid                         | _    | 17   | ns   |

| J12    | TCLK low to TDO high-Z                             | —    | 17   | ns   |

| J13    | TRST assert time                                   | 100  | _    | ns   |

| J14    | TRST setup time (negation) to TCLK high            | 8    |      | ns   |

#### Table 13. JTAG limited voltage range electricals (continued)

### Table 14. JTAG full voltage range electricals

| Symbol | Description                                        | Min. | Max. | Unit |

|--------|----------------------------------------------------|------|------|------|

|        | Operating voltage                                  | 1.71 | 3.6  | V    |

| J1     | TCLK frequency of operation                        |      |      | MHz  |

|        | Boundary Scan                                      | 0    | 10   |      |

|        | JTAG and CJTAG                                     | 0    | 20   |      |

|        | Serial Wire Debug                                  | 0    | 40   |      |

| J2     | TCLK cycle period                                  | 1/J1 |      | ns   |

| JЗ     | TCLK clock pulse width                             |      |      |      |

|        | Boundary Scan                                      | 50   | —    | ns   |

|        | JTAG and CJTAG                                     | 25   | —    | ns   |

|        | Serial Wire Debug                                  | 12.5 | —    | ns   |

| J4     | TCLK rise and fall times                           |      | 3    | ns   |

| J5     | Boundary scan input data setup time to TCLK rise   | 20   | _    | ns   |

| J6     | Boundary scan input data hold time after TCLK rise | 0    |      | ns   |

Table continues on the next page...

| Symbol | Description                                   | Min. | Max. | Unit |

|--------|-----------------------------------------------|------|------|------|

| J7     | TCLK low to boundary scan output data valid   | —    | 25   | ns   |

| J8     | TCLK low to boundary scan output high-Z       | —    | 25   | ns   |

| J9     | TMS, TDI input data setup time to TCLK rise   | 8    | —    | ns   |

| J10    | TMS, TDI input data hold time after TCLK rise | 1.4  | —    | ns   |

| J11    | TCLK low to TDO data valid                    | —    | 22.1 | ns   |

| J12    | TCLK low to TDO high-Z                        | —    | 22.1 | ns   |

| J13    | TRST assert time                              | 100  | —    | ns   |

| J14    | TRST setup time (negation) to TCLK high       | 8    | —    | ns   |

Figure 8. Boundary scan (JTAG) timing

# 3.3.1 MCG specifications

| Symbol                        | Description                           |                                                                     | Min.                            | Тур.   | Max.    | Unit              | Notes           |

|-------------------------------|---------------------------------------|---------------------------------------------------------------------|---------------------------------|--------|---------|-------------------|-----------------|

| f <sub>ints_ft</sub>          |                                       | frequency (slow clock) —<br>t nominal VDD and 25 °C                 | —                               | 32.768 | —       | kHz               |                 |

| f <sub>ints_t</sub>           | Internal reference<br>user trimmed    | frequency (slow clock) —                                            | 31.25                           | _      | 39.0625 | kHz               |                 |

| I <sub>ints</sub>             | Internal reference                    | (slow clock) current                                                | _                               | 20     | —       | μA                |                 |

| $\Delta_{fdco\_res\_t}$       |                                       | med average DCO output<br>I voltage and temperature —<br>Id SCFTRIM | _                               | ± 0.3  | ± 0.6   | %f <sub>dco</sub> | 1               |

| $\Delta f_{dco\_res\_t}$      |                                       | med average DCO output<br>I voltage and temperature —<br>Iy         | _                               | ± 0.2  | ± 0.5   | %f <sub>dco</sub> | 1               |

| $\Delta f_{dco_t}$            |                                       | trimmed average DCO output<br>ltage and temperature                 | —                               | ± 0.5  | ± 2     | %f <sub>dco</sub> | 1,2             |

| $\Delta f_{dco_t}$            |                                       | trimmed average DCO output<br>ed voltage and temperature            | _                               | ± 0.3  | ± 1     | %f <sub>dco</sub> | 1               |

| f <sub>intf_ft</sub>          |                                       | frequency (fast clock) —<br>t nominal VDD and 25°C                  | —                               | 4      | —       | MHz               |                 |

| f <sub>intf_t</sub>           |                                       | frequency (fast clock) —<br>ominal VDD and 25 °C                    | 3                               | —      | 5       | MHz               |                 |

| l <sub>intf</sub>             | Internal reference                    | (fast clock) current                                                | —                               | 25     | —       | μA                |                 |

| f <sub>loc_low</sub>          | Loss of external c<br>RANGE = 00      | lock minimum frequency —                                            | (3/5) x<br>f <sub>ints_t</sub>  | —      | —       | kHz               |                 |

| f <sub>loc_high</sub>         | Loss of external c<br>RANGE = 01, 10, | lock minimum frequency —<br>or 11                                   | (16/5) x<br>f <sub>ints_t</sub> | _      | —       | kHz               |                 |

|                               | 1                                     | FL                                                                  | L                               |        |         |                   | 1               |

| f <sub>fll_ref</sub>          | FLL reference free                    | quency range                                                        | 31.25                           |        | 39.0625 | kHz               |                 |

| f <sub>dco</sub>              | DCO output<br>frequency range         | Low range (DRS=00)<br>640 × f <sub>fll_ref</sub>                    | 20                              | 20.97  | 25      | MHz               | 3, 4            |

|                               |                                       | Mid range (DRS=01)<br>1280 × f <sub>fll ref</sub>                   | 40                              | 41.94  | 50      | MHz               |                 |

|                               |                                       | Mid-high range (DRS=10)                                             | 60                              | 62.91  | 75      | MHz               |                 |

|                               |                                       | 1920 × f <sub>fll_ref</sub><br>High range (DRS=11)                  | 80                              | 83.89  | 100     | MHz               | _               |

|                               |                                       | $2560 \times f_{fll\_ref}$                                          |                                 |        |         |                   |                 |

| f <sub>dco_t_</sub> DMX3<br>2 | DCO output<br>frequency               | Low range (DRS=00)<br>732 × f <sub>fll ref</sub>                    | _                               | 23.99  |         | MHz               | 5, <sup>6</sup> |

|                               |                                       | Mid range (DRS=01)<br>1464 × f <sub>fll ref</sub>                   | _                               | 47.97  | -       | MHz               |                 |

|                               |                                       | $1404 \times 1_{fll\_ref}$<br>Mid-high range (DRS=10)               |                                 | 71.99  |         | MHz               | ļ               |

### Table 15. MCG specifications

| Symbol                   | Description                                                                |                                                                                           | Min.   | Тур.  | Max.                                        | Unit | Notes |

|--------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------|-------|---------------------------------------------|------|-------|

|                          |                                                                            | 2197 × f <sub>fll_ref</sub>                                                               |        |       |                                             |      |       |

|                          |                                                                            | High range (DRS=11)                                                                       | —      | 95.98 | —                                           | MHz  |       |

|                          |                                                                            | $2929 \times f_{fll\_ref}$                                                                |        |       |                                             |      |       |

| J <sub>cyc_fll</sub>     | FLL period jitter                                                          |                                                                                           | _      | 180   | _                                           | ps   |       |

|                          | <ul> <li>f<sub>DCO</sub> = 48 M</li> <li>f<sub>DCO</sub> = 98 M</li> </ul> |                                                                                           | _      | 150   | _                                           |      |       |

| t <sub>fll_acquire</sub> | FLL target freque                                                          | ncy acquisition time                                                                      | —      | _     | 1                                           | ms   | 7     |

|                          |                                                                            | P                                                                                         | LL     |       |                                             |      |       |

| f <sub>vco</sub>         | VCO operating fre                                                          | equency                                                                                   | 48.0   | _     | 120                                         | MHz  |       |

| I <sub>pll</sub>         | PLL operating curves<br>PLL @ 96 M<br>= 2 MHz, V                           | rrent<br>MHz (f <sub>osc_hi_1</sub> = 8 MHz, f <sub>pll_ref</sub><br>DIV multiplier = 48) | _      | 1060  | —                                           | μA   | 8     |

| I <sub>pll</sub>         |                                                                            | rrent<br>MHz (f <sub>osc_hi_1</sub> = 8 MHz, f <sub>pll_ref</sub><br>DIV multiplier = 24) | _      | 600   | —                                           | μA   | 8     |

| f <sub>pll_ref</sub>     | PLL reference fre                                                          | quency range                                                                              | 2.0    | _     | 4.0                                         | MHz  |       |

| J <sub>cyc_pll</sub>     | PLL period jitter (                                                        | RMS)                                                                                      |        |       |                                             |      | 9     |

|                          | • f <sub>vco</sub> = 48 Mł                                                 | Hz                                                                                        | _      | 120   | _                                           | ps   |       |

|                          | • f <sub>vco</sub> = 120 N                                                 | 1Hz                                                                                       | —      | 75    | _                                           | ps   |       |

| J <sub>acc_pll</sub>     | PLL accumulated                                                            | jitter over 1µs (RMS)                                                                     |        |       |                                             |      | 9     |

|                          | • f <sub>vco</sub> = 48 Mł                                                 | Hz                                                                                        | —      | 1350  | _                                           | ps   |       |

|                          | • f <sub>vco</sub> = 120 M                                                 | 1Hz                                                                                       | —      | 600   | -                                           | ps   |       |

| D <sub>lock</sub>        | Lock entry freque                                                          | ncy tolerance                                                                             | ± 1.49 |       | ± 2.98                                      | %    |       |

| D <sub>unl</sub>         | Lock exit frequen                                                          | cy tolerance                                                                              | ± 4.47 | _     | ± 5.97                                      | %    |       |

| t <sub>pll_lock</sub>    | Lock detector det                                                          | ection time                                                                               | _      | _     | $150 \times 10^{-6} + 1075(1/ f_{pll_ref})$ | S    | 10    |

#### Table 15. MCG specifications (continued)

- 1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

- 2. 2 V <= VDD <= 3.6 V.

- 3. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=0.

- The resulting system clock frequencies should not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco\_t</sub>) over voltage and temperature should be considered.

- 5. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=1.

- 6. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

- This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- 8. Excludes any oscillator currents that are also consuming power while PLL is in operation.

- 9. This specification was obtained using a Freescale developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary.

- This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

# 3.3.2 Oscillator electrical specifications

#### 3.3.2.1 Oscillator DC electrical specifications Table 16. Oscillator DC electrical specifications

| Symbol          | Description                                                    | Min. | Тур. | Max. | Unit | Notes |

|-----------------|----------------------------------------------------------------|------|------|------|------|-------|

| V <sub>DD</sub> | Supply voltage                                                 | 1.71 | —    | 3.6  | V    |       |

| IDDOSC          | Supply current — low-power mode (HGO=0)                        |      |      |      |      | 1     |

|                 | • 32 kHz                                                       | _    | 600  | _    | nA   |       |

|                 | • 4 MHz                                                        | _    | 200  | _    | μA   |       |

|                 | • 8 MHz (RANGE=01)                                             | _    | 300  | _    | μA   |       |

|                 | • 16 MHz                                                       | _    | 950  | _    | μA   |       |

|                 | • 24 MHz                                                       | _    | 1.2  | _    | mA   |       |

|                 | • 32 MHz                                                       |      | 1.5  | -    | mA   |       |

| IDDOSC          | Supply current — high gain mode (HGO=1)                        |      |      |      |      | 1     |

|                 | • 32 kHz                                                       |      | 7.5  | _    | μA   |       |

|                 | • 4 MHz                                                        |      | 500  | _    | μA   |       |

|                 | • 8 MHz (RANGE=01)                                             | _    | 650  | _    | μA   |       |

|                 | • 16 MHz                                                       | _    | 2.5  | _    | mA   |       |

|                 | • 24 MHz                                                       | _    | 3.25 | _    | mA   |       |

|                 | • 32 MHz                                                       | _    | 4    | _    | mA   |       |

| C <sub>x</sub>  | EXTAL load capacitance                                         |      |      | _    |      | 2, 3  |

| Cy              | XTAL load capacitance                                          | _    | _    | —    |      | 2, 3  |

| $R_F$           | Feedback resistor — low-frequency, low-power mode (HGO=0)      | _    |      | —    | MΩ   | 2, 4  |

|                 | Feedback resistor — low-frequency, high-gain mode (HGO=1)      | _    | 10   | -    | MΩ   |       |

|                 | Feedback resistor — high-frequency, low-<br>power mode (HGO=0) | _    |      | _    | MΩ   |       |

|                 | Feedback resistor — high-frequency, high-gain mode (HGO=1)     | _    | 1    | _    | MΩ   | -     |

| R <sub>S</sub>  | Series resistor — low-frequency, low-power<br>mode (HGO=0)     | _    | _    | -    | kΩ   |       |

|                 | Series resistor — low-frequency, high-gain mode (HGO=1)        | _    | 200  | -    | kΩ   |       |

|                 | Series resistor — high-frequency, low-power<br>mode (HGO=0)    | _    | _    | -    | kΩ   |       |

|                 | Series resistor — high-frequency, high-gain mode (HGO=1)       |      |      |      |      |       |

Table continues on the next page ...

- 2. When transitioning from FEI or FBI to FBE mode, restrict the frequency of the input clock so that, when it is divided by FRDIV, it remains within the limits of the DCO input clock frequency.

- 3. Proper PC board layout procedures must be followed to achieve specifications.

- 4. Crystal startup time is defined as the time between the oscillator being enabled and the OSCINIT bit in the MCG\_S register being set.

### NOTE

The 32 kHz oscillator works in low power mode by default and cannot be moved into high power/gain mode.

## 3.3.3 32 kHz oscillator electrical characteristics

#### 3.3.3.1 32 kHz oscillator DC electrical specifications Table 18. 32kHz oscillator DC electrical specifications

| Symbol                       | Description                                   | Min. | Тур. | Max. | Unit |

|------------------------------|-----------------------------------------------|------|------|------|------|

| V <sub>BAT</sub>             | Supply voltage                                | 1.71 | _    | 3.6  | V    |

| R <sub>F</sub>               | Internal feedback resistor                    | —    | 100  | _    | MΩ   |

| C <sub>para</sub>            | Parasitical capacitance of EXTAL32 and XTAL32 |      | 5    | 7    | pF   |

| V <sub>pp</sub> <sup>1</sup> | Peak-to-peak amplitude of oscillation         | —    | 0.6  | _    | V    |

1. When a crystal is being used with the 32 kHz oscillator, the EXTAL32 and XTAL32 pins should only be connected to required oscillator components and must not be connected to any other devices.

#### 3.3.3.2 32 kHz oscillator frequency specifications Table 19. 32 kHz oscillator frequency specifications

| Symbol                  | Description                               | Min. | Тур.   | Max.      | Unit | Notes |

|-------------------------|-------------------------------------------|------|--------|-----------|------|-------|

| f <sub>osc_lo</sub>     | Oscillator crystal                        | —    | 32.768 | —         | kHz  |       |

| t <sub>start</sub>      | Crystal start-up time                     | _    | 1000   |           | ms   | 1     |

| V <sub>ec_extal32</sub> | Externally provided input clock amplitude | 700  | _      | $V_{BAT}$ | mV   | 2, 3  |

1. Proper PC board layout procedures must be followed to achieve specifications.

2. This specification is for an externally supplied clock driven to EXTAL32 and does not apply to any other clock input. The oscillator remains enabled and XTAL32 must be left unconnected.

The parameter specified is a peak-to-peak value and V<sub>IH</sub> and V<sub>IL</sub> specifications do not apply. The voltage of the applied clock must be within the range of V<sub>SS</sub> to V<sub>BAT</sub>.

# 3.4 Memories and memory interfaces

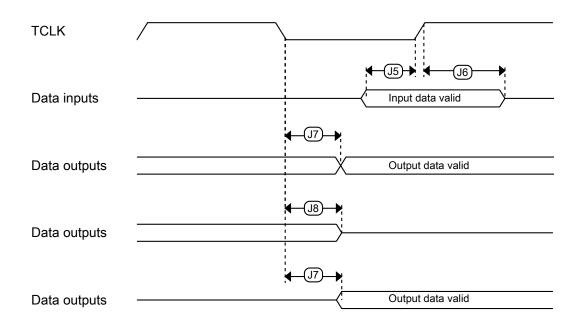

Figure 11. EEPROM backup writes to FlexRAM

## 3.4.2 EzPort switching specifications Table 24. EzPort switching specifications

| Num  | Description                                              | Min.                    | Max.                | Unit |

|------|----------------------------------------------------------|-------------------------|---------------------|------|

|      | Operating voltage                                        | 1.71                    | 3.6                 | V    |

| EP1  | EZP_CK frequency of operation (all commands except READ) | -                       | f <sub>SYS</sub> /2 | MHz  |

| EP1a | EZP_CK frequency of operation (READ command)             | —                       | f <sub>SYS</sub> /8 | MHz  |

| EP2  | EZP_CS negation to next EZP_CS assertion                 | 2 x t <sub>EZP_CK</sub> | —                   | ns   |

| EP3  | EZP_CS input valid to EZP_CK high (setup)                | 5                       | _                   | ns   |

| EP4  | EZP_CK high to EZP_CS input invalid (hold)               | 5                       | —                   | ns   |

| EP5  | EZP_D input valid to EZP_CK high (setup)                 | 2                       | —                   | ns   |

| EP6  | EZP_CK high to EZP_D input invalid (hold)                | 5                       | _                   | ns   |

| EP7  | EZP_CK low to EZP_Q output valid                         | _                       | 18                  | ns   |

| EP8  | EZP_CK low to EZP_Q output invalid (hold)                | 0                       | _                   | ns   |

| EP9  | EZP_CS negation to EZP_Q tri-state                       | _                       | 12                  | ns   |

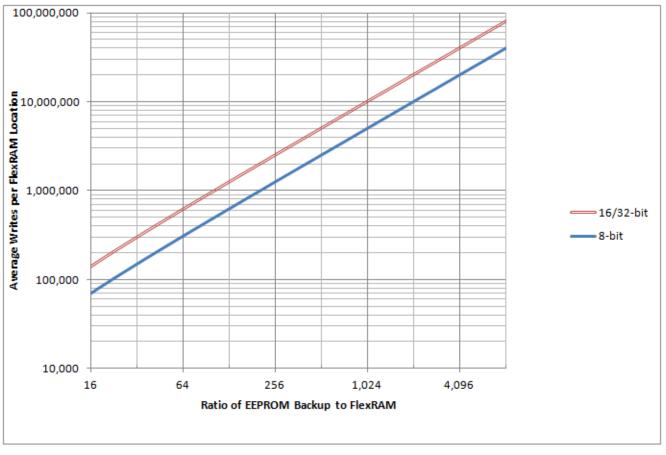

Figure 13. FlexBus read timing diagram

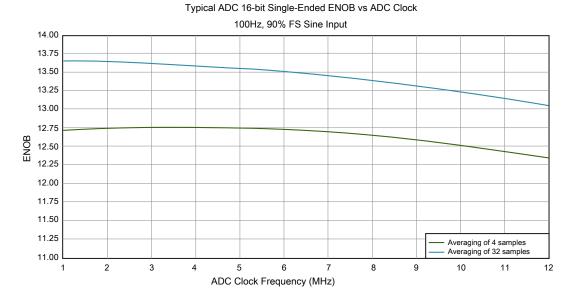

Figure 17. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

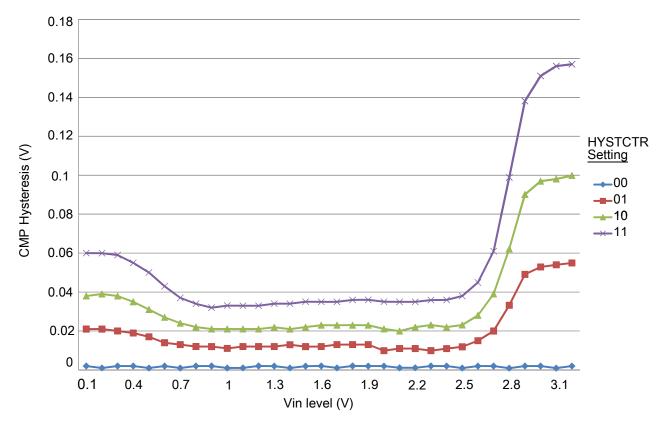

### 3.6.2 CMP and 6-bit DAC electrical specifications Table 29. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                         | Min.                  | Тур. | Max.            | Unit             |

|--------------------|-----------------------------------------------------|-----------------------|------|-----------------|------------------|

| V <sub>DD</sub>    | Supply voltage                                      | 1.71                  | _    | 3.6             | V                |

| IDDHS              | Supply current, High-speed mode (EN=1, PMODE=1)     | -                     |      | 200             | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)      | _                     |      | 20              | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                | V <sub>SS</sub> – 0.3 | _    | V <sub>DD</sub> | V                |

| V <sub>AIO</sub>   | Analog input offset voltage                         | _                     |      | 20              | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>           |                       |      |                 |                  |

|                    | • CR0[HYSTCTR] = 00                                 | _                     | 5    | _               | mV               |

|                    | • CR0[HYSTCTR] = 01                                 | _                     | 10   | _               | mV               |

|                    | • CR0[HYSTCTR] = 10                                 | —                     | 20   | _               | mV               |

|                    | • CR0[HYSTCTR] = 11                                 | —                     | 30   | _               | mV               |

| V <sub>CMPOh</sub> | Output high                                         | V <sub>DD</sub> – 0.5 |      |                 | V                |

| V <sub>CMPOI</sub> | Output low                                          | _                     |      | 0.5             | V                |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN=1, PMODE=1)  | 20                    | 50   | 200             | ns               |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN=1, PMODE=0)   | 80                    | 250  | 600             | ns               |

|                    | Analog comparator initialization delay <sup>2</sup> | _                     |      | 40              | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (enabled)                   |                       | 7    | _               | μA               |

| INL                | 6-bit DAC integral non-linearity                    | -0.5                  | _    | 0.5             | LSB <sup>3</sup> |

| DNL                | 6-bit DAC differential non-linearity                | -0.3                  |      | 0.3             | LSB              |

Figure 19. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 1)

## 3.6.3 12-bit DAC electrical characteristics

#### 3.6.3.1 12-bit DAC operating requirements Table 30. 12-bit DAC operating requirements

| Symbol            | Desciption              | Min. | Max. | Unit | Notes |

|-------------------|-------------------------|------|------|------|-------|

| V <sub>DDA</sub>  | Supply voltage          | 1.71 | 3.6  | V    |       |

| V <sub>DACR</sub> | Reference voltage       | 1.13 | 3.6  | V    | 1     |

| CL                | Output load capacitance | _    | 100  | pF   | 2     |

| ١L                | Output load current     | —    | 1    | mA   |       |

1. The DAC reference can be selected to be  $V_{\text{DDA}}$  or  $V_{\text{REFH}}.$

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC.

#### 3.6.3.2 12-bit DAC operating behaviors Table 31. 12-bit DAC operating behaviors

| Symbol                | Description                                                                            | Min.                      | Тур.     | Max.              | Unit   | Notes |

|-----------------------|----------------------------------------------------------------------------------------|---------------------------|----------|-------------------|--------|-------|

| I <sub>DDA_DACL</sub> | Supply current — low-power mode                                                        |                           | —        | 150               | μΑ     |       |

| I <sub>DDA_DACH</sub> | Supply current — high-speed mode                                                       |                           | —        | 700               | μΑ     |       |

| t <sub>DACLP</sub>    | Full-scale settling time (0x080 to 0xF7F) — low-power mode                             |                           | 100      | 200               | μs     | 1     |

| t <sub>DACHP</sub>    | Full-scale settling time (0x080 to 0xF7F) — high-power mode                            |                           | 15       | 30                | μs     | 1     |

| t <sub>CCDACLP</sub>  | Code-to-code settling time (0xBF8 to<br>0xC08) — low-power mode and high-speed<br>mode | _                         | 0.7      | 1                 | μs     | 1     |

| V <sub>dacoutl</sub>  | DAC output voltage range low — high-<br>speed mode, no load, DAC set to 0x000          | _                         | —        | 100               | mV     |       |

| V <sub>dacouth</sub>  | DAC output voltage range high — high-<br>speed mode, no load, DAC set to 0xFFF         | V <sub>DACR</sub><br>-100 | —        | V <sub>DACR</sub> | mV     |       |

| INL                   | Integral non-linearity error — high speed mode                                         | _                         | —        | ±8                | LSB    | 2     |

| DNL                   | Differential non-linearity error — $V_{DACR} > 2$<br>V                                 |                           | —        | ±1                | LSB    | 3     |

| DNL                   | Differential non-linearity error — V <sub>DACR</sub> = VREF_OUT                        |                           | —        | ±1                | LSB    | 4     |

| VOFFSET               | Offset error                                                                           | _                         | ±0.4     | ±0.8              | %FSR   | 5     |

| E <sub>G</sub>        | Gain error                                                                             |                           | ±0.1     | ±0.6              | %FSR   | 5     |

| PSRR                  | Power supply rejection ratio, $V_{DDA} \ge 2.4 V$                                      | 60                        | —        | 90                | dB     |       |

| T <sub>CO</sub>       | Temperature coefficient offset voltage                                                 | _                         | 3.7      | _                 | μV/C   | 6     |

| T <sub>GE</sub>       | Temperature coefficient gain error                                                     | _                         | 0.000421 | —                 | %FSR/C |       |

| A <sub>C</sub>        | Offset aging coefficient                                                               | _                         | —        | 100               | μV/yr  |       |

| Rop                   | Output resistance (load = $3 \text{ k}\Omega$ )                                        | _                         | —        | 250               | Ω      |       |

| SR                    | Slew rate -80h $\rightarrow$ F7Fh $\rightarrow$ 80h                                    |                           |          |                   | V/µs   |       |

|                       | <ul> <li>High power (SP<sub>HP</sub>)</li> </ul>                                       | 1.2                       | 1.7      | _                 |        |       |

|                       | • Low power (SP <sub>LP</sub> )                                                        | 0.05                      | 0.12     | _                 |        |       |

| СТ                    | Channel to channel cross talk                                                          |                           |          | -80               | dB     |       |

| BW                    | 3dB bandwidth                                                                          |                           |          |                   | kHz    |       |

|                       | <ul> <li>High power (SP<sub>HP</sub>)</li> </ul>                                       | 550                       | _        | _                 |        |       |

|                       | • Low power (SP <sub>LP</sub> )                                                        | 40                        | _        | —                 |        |       |

1. Settling within ±1 LSB

- 2. The INL is measured for 0 + 100 mV to  $V_{\text{DACR}}$  –100 mV

- 3. The DNL is measured for 0 + 100 mV to  $V_{\text{DACR}}$  –100 mV

- 4. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  -100 mV with  $V_{DDA}$  > 2.4 V 5. Calculated by a best fit curve from  $V_{SS}$  + 100 mV to  $V_{DACR}$  100 mV

| Symbol              | Description                                                                                | Min.   | Тур.  | Max.   | Unit | Notes |

|---------------------|--------------------------------------------------------------------------------------------|--------|-------|--------|------|-------|

| V <sub>out</sub>    | Voltage reference output with factory trim at nominal V <sub>DDA</sub> and temperature=25C | 1.1915 | 1.195 | 1.1977 | V    | 1     |

| V <sub>out</sub>    | Voltage reference output — factory trim                                                    | 1.1584 | _     | 1.2376 | V    | 1     |

| V <sub>out</sub>    | Voltage reference output — user trim                                                       | 1.193  | —     | 1.197  | V    | 1     |

| V <sub>step</sub>   | Voltage reference trim step                                                                | —      | 0.5   | —      | mV   | 1     |

| V <sub>tdrift</sub> | Temperature drift (Vmax -Vmin across the full temperature range)                           | _      |       | 80     | mV   | 1     |

| I <sub>bg</sub>     | Bandgap only current                                                                       | _      | _     | 80     | μA   | 1     |

| $\Delta V_{LOAD}$   | Load regulation                                                                            |        |       |        | μV   | 1, 2  |

|                     | • current = ± 1.0 mA                                                                       | _      | 200   | —      |      |       |

| T <sub>stup</sub>   | Buffer startup time                                                                        | _      |       | 100    | μs   | _     |

| V <sub>vdrift</sub> | Voltage drift (Vmax -Vmin across the full voltage range)                                   | _      | 2     | _      | mV   | 1     |

| Table 33. | VREF full-range operating behaviors |

|-----------|-------------------------------------|

|-----------|-------------------------------------|

1. See the chip's Reference Manual for the appropriate settings of the VREF Status and Control register.

2. Load regulation voltage is the difference between the VREF\_OUT voltage with no load vs. voltage with defined load

#### Table 34. VREF limited-range operating requirements

| Sym            | bol | Description | Min. | Max. | Unit | Notes |

|----------------|-----|-------------|------|------|------|-------|

| Τ <sub>4</sub> | Ą   | Temperature | 0    | 50   | °C   | _     |

Table 35. VREF limited-range operating behaviors

| Symbol           | Description                                | Min.  | Max.  | Unit | Notes |

|------------------|--------------------------------------------|-------|-------|------|-------|

| V <sub>out</sub> | Voltage reference output with factory trim | 1.173 | 1.225 | V    | —     |

# 3.7 Timers

See General switching specifications.

# 3.8 Communication interfaces

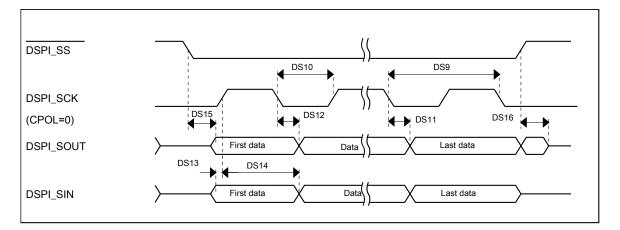

Figure 23. DSPI classic SPI timing — slave mode

## 3.8.6 DSPI switching specifications (full voltage range)

The DMA Serial Peripheral Interface (DSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The tables below provides DSPI timing characteristics for classic SPI timing modes. Refer to the DSPI chapter of the Reference Manual for information on the modified transfer formats used for communicating with slower peripheral devices.

| Num | Description                         | Min.                          | Max.                     | Unit | Notes |

|-----|-------------------------------------|-------------------------------|--------------------------|------|-------|

|     | Operating voltage                   | 1.71                          | 3.6                      | V    | 1     |

|     | Frequency of operation              | —                             | 15                       | MHz  |       |

| DS1 | DSPI_SCK output cycle time          | 4 x t <sub>BUS</sub>          | —                        | ns   |       |

| DS2 | DSPI_SCK output high/low time       | (t <sub>SCK</sub> /2) - 4     | (t <sub>SCK/2)</sub> + 4 | ns   |       |

| DS3 | DSPI_PCSn valid to DSPI_SCK delay   | (t <sub>BUS</sub> x 2) –<br>4 | —                        | ns   | 2     |

| DS4 | DSPI_SCK to DSPI_PCSn invalid delay | (t <sub>BUS</sub> x 2) –<br>4 | _                        | ns   | 3     |

| DS5 | DSPI_SCK to DSPI_SOUT valid         | _                             | 10                       | ns   |       |

| DS6 | DSPI_SCK to DSPI_SOUT invalid       | -4.5                          | —                        | ns   |       |

| DS7 | DSPI_SIN to DSPI_SCK input setup    | 20.5                          | —                        | ns   |       |

| DS8 | DSPI_SCK to DSPI_SIN input hold     | 0                             | _                        | ns   |       |

Table 40. Master mode DSPI timing (full voltage range)

1. The DSPI module can operate across the entire operating voltage for the processor, but to run across the full voltage range the maximum frequency of operation is reduced.

2. The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

3. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

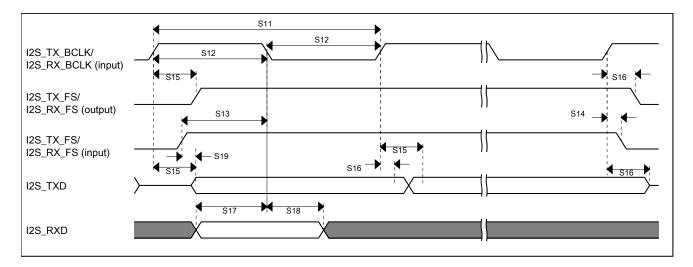

Figure 30. I2S/SAI timing — slave modes

# 3.8.10.2 VLPR, VLPW, and VLPS mode performance over the full operating voltage range

This section provides the operating performance over the full operating voltage for the device in VLPR, VLPW, and VLPS modes.

Table 47. I2S/SAI master mode timing in VLPR, VLPW, and VLPS modes(full voltage range)

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|------|-------------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |

| S1   | I2S_MCLK cycle time                                               | 62.5 | —    | ns          |

| S2   | I2S_MCLK pulse width high/low                                     | 45%  | 55%  | MCLK period |

| S3   | I2S_TX_BCLK/I2S_RX_BCLK cycle time (output)                       | 250  | _    | ns          |

| S4   | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low                      | 45%  | 55%  | BCLK period |

| S5   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output valid   | —    | 45   | ns          |

| S6   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output invalid | 0    | -    | ns          |

| S7   | I2S_TX_BCLK to I2S_TXD valid                                      | —    | 45   | ns          |

| S8   | I2S_TX_BCLK to I2S_TXD invalid                                    |      | —    | ns          |

| S9   | I2S_RXD/I2S_RX_FS input setup before<br>I2S_RX_BCLK               |      | -    | ns          |

| S10  | I2S_RXD/I2S_RX_FS input hold after I2S_RX_BCLK                    | 0    | —    | ns          |

### 3.8.10.4.5 Small package marking

In an effort to save space, small package devices use special marking on the chip. These markings have the following format:

Q ## C F T PP

This table lists the possible values for each field in the part number for small packages (not all combinations are valid):

| Field | Description                | Values                                                                                                                             |  |

|-------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| Q     | Qualification status       | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul>                                         |  |

| ##    | Kinetis family             | • 2# = K21/K22                                                                                                                     |  |

| С     | Speed                      | • H = 120 MHz                                                                                                                      |  |

| F     | Flash memory configuration | <ul> <li>K = 512 KB + Flex</li> <li>1 = 1 MB</li> </ul>                                                                            |  |

| Т     | Temperature range (°C)     | • V = -40 to 105                                                                                                                   |  |

| PP    | Package identifier         | <ul> <li>LL = 100 LQFP</li> <li>MC = 121 MAPBGA</li> <li>LQ = 144 LQFP</li> <li>MD = 144 MAPBGA</li> <li>DC = 121 XFBGA</li> </ul> |  |

This tables lists some examples of small package marking along with the original part numbers:

| Original part number | Alternate part number |

|----------------------|-----------------------|

| MK22FN1M0VMC12       | M22H1VMC              |

## 3.8.10.5 Terminology and guidelines

#### 3.8.10.5.1 Definition: Operating requirement

An *operating requirement* is a specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip.

#### 3.8.10.5.1.1 Example

This is an example of an operating requirement: