Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 56800EX                                                               |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 80MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                            |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                       |

| Number of I/O              | 39                                                                    |

| Program Memory Size        | 96KB (96K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 16K × 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                             |

| Data Converters            | A/D 10x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f84550vlf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- System

- DMA controller

- Integrated power-on reset (POR) and low-voltage interrupt (LVI) and brown-out reset module

- Inter-module crossbar connection

- JTAG/enhanced on-chip emulation (EOnCE) for unobtrusive, real-time debugging

- Operating characteristics

- Single supply: 3.0 V to 3.6 V  $\,$

- 5 V-tolerant I/O

- LQFP packages:

- 48-pin

- 64-pin

| Part                                                   |          |     |          |     |     |     |     |     | MC5 | 6F84     |                  |          |                  |     |     |     |     |     |

|--------------------------------------------------------|----------|-----|----------|-----|-----|-----|-----|-----|-----|----------|------------------|----------|------------------|-----|-----|-----|-----|-----|

| Number                                                 | 789      | 786 | 769      | 766 | 763 | 553 | 550 | 543 | 540 | 587      | 585              | 567      | 565              | 462 | 452 | 451 | 442 | 441 |

| Standard<br>channels                                   | 4        | 1   | 4        | 1   | 1   | 1   | 0   | 1   | 0   | 2x<br>12 | 1x<br>12,<br>1x9 | 2x<br>12 | 1x<br>12,<br>1x9 | 1x9 | 1x9 | 1x6 | 1x9 | 1x6 |

| PWMB<br>with input<br>capture:<br>Standard<br>channels | 1x<br>12 | 1x7 | 1x<br>12 | 1x7 | 0   | 0   | 0   | 0   | 0   | 0        | 0                | 0        | 0                | 0   | 0   | 0   | 0   | 0   |

| DAC                                                    | 1        | 1   | 1        | 1   | 1   | 1   | 1   | 1   | 1   | 1        | 1                | 0        | 0                | 1   | 0   | 0   | 0   | 0   |

| Quad<br>Decoder                                        | 1        | 1   | 1        | 1   | 0   | 0   | 0   | 0   | 0   | 1        | 1                | 1        | 1                | 1   | 1   | 1   | 1   | 1   |

| DMA                                                    | Yes      | Yes | Yes      | Yes | Yes | Yes | Yes | Yes | Yes | Yes      | Yes              | Yes      | Yes              | Yes | Yes | Yes | Yes | Yes |

| CMP                                                    | 4        | 4   | 4        | 4   | 4   | 4   | 3   | 4   | 3   | 4        | 4                | 4        | 4                | 4   | 4   | 3   | 4   | 3   |

| QSCI                                                   | 3        | 3   | 3        | 3   | 2   | 2   | 2   | 2   | 2   | 3        | 3                | 3        | 3                | 2   | 2   | 2   | 2   | 2   |

| QSPI                                                   | 3        | 2   | 3        | 2   | 2   | 2   | 2   | 2   | 2   | 3        | 2                | 3        | 2                | 2   | 2   | 2   | 2   | 2   |

| I2C/SMBus                                              | 2        | 2   | 2        | 2   | 2   | 2   | 2   | 2   | 2   | 2        | 2                | 2        | 2                | 2   | 2   | 2   | 2   | 2   |

| FlexCAN                                                | 1        | 1   | 1        | 1   | 1   | 1   | 1   | 1   | 1   | 1        | 1                | 1        | 1                | 1   | 1   | 1   | 0   | 0   |

| LQFP<br>package<br>pin count                           | 100      | 80  | 100      | 80  | 64  | 64  | 48  | 64  | 48  | 100      | 80               | 100      | 80               | 64  | 64  | 48  | 64  | 48  |

Table 1. 56F844x/5x/7x Family (continued)

1. This total assumes no FlexNVM is used with FlexRAM for EEPROM.

## 1.2 56800EX 32-bit Digital Signal Controller Core

- Efficient 32-bit 56800EX Digital Signal Processor (DSP) engine with modified dual Harvard architecture

- Three internal address buses

- Four internal data buses: two 32-bit primary buses, one 16-bit secondary data bus, and one 16-bit instruction bus

- 32-bit data accesses

- Support for concurrent instruction fetches in the same cycle and dual data accesses in the same cycle

- 20 addressing modes

- As many as 80 million instructions per second (MIPS) at 80 MHz core frequency

- 162 basic instructions

- Instruction set supports both fractional arithmetic and integer arithmetic

- 32-bit internal primary data buses supporting 8-bit, 16-bit, and 32-bit data movement, addition, subtraction, and logical operation

- Single-cycle 16 × 16-bit -> 32-bit and 32 x 32-bit -> 64-bit multiplier-accumulator (MAC) with dual parallel moves

- Up to 16 KW FlexNVM, which can be used as additional program or data flash memory

- Up to 1 KW FlexRAM, which can be configured as enhanced EEPROM (used in conjunction with FlexNVM) or used as additional RAM

## 1.5 Interrupt Controller

- Five interrupt priority levels

- Three user programmable priority levels for each interrupt source: level 0, 1, 2

- Unmaskable level 3 interrupts include: illegal instruction, hardware stack overflow, misaligned data access, SWI3 instruction

- Maskable level 3 interrupts include: EOnCE step counter, EOnCE breakpoint unit, EOnCE trace buffer

- Lowest-priority software interrupt: level LP

- Support for nested interrupt: higher priority level interrupt request can interrupt lower priority interrupt subroutine

- Masking of interrupt priority level managed by the 56800EX core

- Two programmable fast interrupts that can be assigned to any interrupt source

- Notification to System Integration Module (SIM) to restart clock when in wait and stop states

- Ability to relocate interrupt vector table

# 1.6 Peripheral highlights

## 1.6.1 Enhanced Flex Pulse Width Modulator (eFlexPWM)

- Up to 12 output channels in each module

- 16 bits of resolution for center, edge aligned, and asymmetrical PWMs

- PWMA with NanoEdge high resolution

- Fractional delay for enhanced resolution of the PWM period and edge placement

- Arbitrary PWM edge placement

- NanoEdge implementation: 312 ps PWM frequency and duty-cycle resolution

- Each complementary pair can operate with its own PWM frequency base and deadtime values

- 4 time base in each PWM module

- Independent top and bottom deadtime insertion for each complementary pair

- PWM outputs can operate as complementary pairs or independent channels

- Independent control of both edges of each PWM output

- Enhanced input capture and output compare functionality on each input

#### **1.6.7 Queued Serial Communications Interface (QSCI) Modules**

- Operating clock up to two times CPU operating frequency

- Four-word-deep FIFOs available on both transmit and receive buffers

- Standard mark/space non-return-to-zero (NRZ) format

- 13-bit integer and 3-bit fractional baud rate selection

- Full-duplex or single-wire operation

- Programmable 8-bit or 9-bit data format

- Error detection capability

- Two receiver wakeup methods:

- Idle line

- Address mark

- 1/16 bit-time noise detection

#### 1.6.8 Queued Serial Peripheral Interface (QSPI) Modules

- Maximum 25 Mbps baud rate

- Selectable baud rate clock sources for low baud rate communication

- Baud rate as low as Baudrate\_Freq\_in / 8192

- Full-duplex operation

- Master and slave modes

- Double-buffered operation with separate transmit and receive registers

- Four-word-deep FIFOs available on transmit and receive buffers

- Programmable length transmissions (2 bits to 16 bits)

- Programmable transmit and receive shift order (MSB as first bit transmitted)

#### 1.6.9 Inter-Integrated Circuit (I2C)/System Management Bus (SMBus) Modules

- Compatible with I2C bus standard

- Support for System Management Bus (SMBus) specification, version2

- Multi-master operation

- General call recognition

- 10-bit address extension

- Dual slave addresses

- Programmable glitch input filter

#### 1.6.10 Flex Controller Area Network (FlexCAN) Module

• Clock source from PLL or XOSC/CLKIN

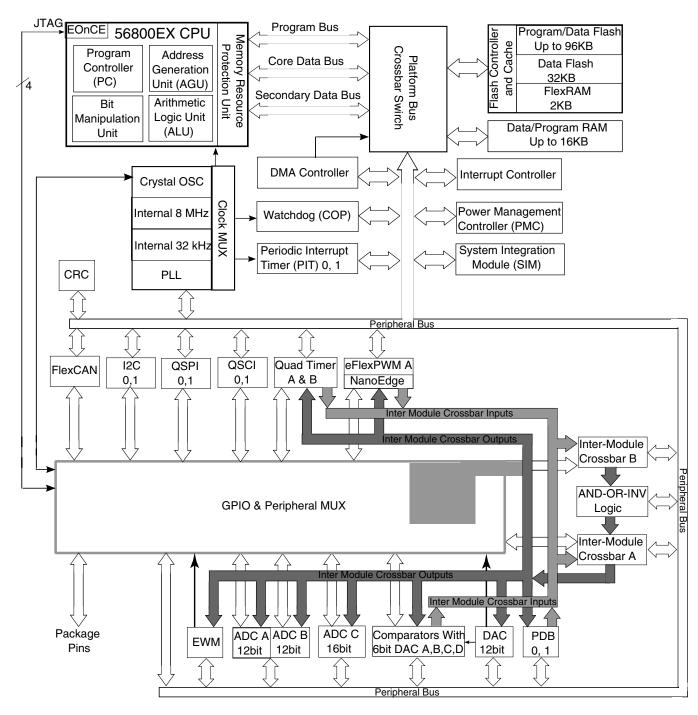

Figure 2. System Diagram

## 4.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

## 4.2 Format

Part numbers for this device have the following format: Q 56F8 4 C F P T PP N

## 4.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description                                                             | Values                                                                                                      |

|-------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Q     | Qualification status                                                    | <ul> <li>MC = Fully qualified, general market flow</li> <li>PC = Prequalification</li> </ul>                |

| 56F8  | DSC family with flash memory and DSP56800/<br>DSP56800E/DSP56800EX core | • 56F8                                                                                                      |

| 4     | DSC subfamily                                                           | • 4                                                                                                         |

| С     | Maximum CPU frequency (MHz)                                             | <ul> <li>4 = 60 MHz</li> <li>5 = 80 MHz</li> <li>7 = 100 MHz</li> </ul>                                     |

| F     | Primary program flash memory size                                       | <ul> <li>4 = 64 KB</li> <li>5 = 96 KB</li> <li>6 = 128 KB</li> <li>8 = 256 KB</li> </ul>                    |

| P     | Pin count                                                               | <ul> <li>0 and 1 = 48</li> <li>2 and 3 = 64</li> <li>4, 5, and 6 = 80</li> <li>7, 8, and 9 = 100</li> </ul> |

| Т     | Temperature range (°C)                                                  | • V = -40 to 105                                                                                            |

| PP    | Package identifier                                                      | <ul> <li>LF = 48LQFP</li> <li>LH = 64LQFP</li> <li>LK = 80LQFP</li> <li>LL = 100LQFP</li> </ul>             |

| Ν     | Packaging type                                                          | <ul> <li>R = Tape and reel</li> <li>(Blank) = Trays</li> </ul>                                              |

## 5.8 Definition: Typical value

A *typical value* is a specified value for a technical characteristic that:

- Lies within the range of values specified by the operating behavior

- Given the typical manufacturing process, is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions

Typical values are provided as design guidelines and are neither tested nor guaranteed.

## 5.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol | Description                                    | Min. | Тур. | Max. | Unit |

|--------|------------------------------------------------|------|------|------|------|

|        | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

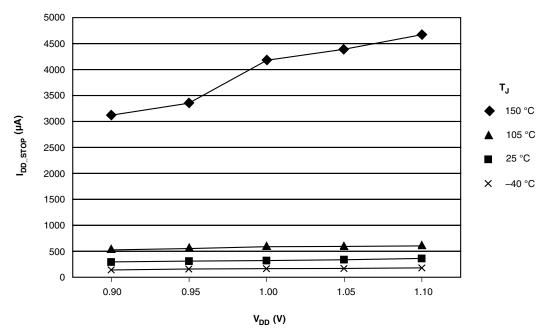

### 5.8.2 Example 2

This is an example of a chart that shows typical values for various voltage and temperature conditions:

MC56F8455x Advance Information Data Sheet, Rev. 2, 06/2012.

## 5.9 Typical value conditions

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description          | Value | Unit |

|-----------------|----------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature  | 25    | C°   |

| V <sub>DD</sub> | 3.3 V supply voltage | 3.3   | V    |

## 6 Ratings

## 6.1 Thermal handling ratings

| Symbol           | Description                   | Min. | Max. | Unit | Notes |

|------------------|-------------------------------|------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | -55  | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | _    | 260  | °C   | 2     |

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

## 6.2 Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level |      | 3    |      | 1     |

1. Determined according to IPC/JEDEC Standard J-STD-020, *Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices*.

# 6.3 ESD handling ratings

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, use normal handling precautions to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with AEC-Q100 Stress Test Qualification. During the device qualification ESD stresses were performed for the human body model (HBM), the machine model (MM), and the charge device model (CDM).

All latch-up testing is in conformity with AEC-Q100 Stress Test Qualification.

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Characteristic <sup>1</sup>                      | Min   | Max   | Unit |

|--------------------------------------------------|-------|-------|------|

| ESD for Human Body Model (HBM)                   | -2000 | +2000 | V    |

| ESD for Machine Model (MM)                       | -200  | +200  | V    |

| ESD for Charge Device Model (CDM)                | -500  | +500  | V    |

| Latch-up current at TA= 85°C (I <sub>LAT</sub> ) | -100  | +100  | mA   |

Table 3. ESD/Latch-up Protection

1. Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted.

# 6.4 Voltage and current operating ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table 4 may affect device reliability or cause permanent damage to the device.

| Table 4. | Absolute N | Maximum | Ratings | $(V_{SS} = 0)$ | V, V <sub>SSA</sub> = 0 V) |

|----------|------------|---------|---------|----------------|----------------------------|

|----------|------------|---------|---------|----------------|----------------------------|

| Characteristic                                         | Symbol             | Notes <sup>1</sup> | Min  | Max | Unit |

|--------------------------------------------------------|--------------------|--------------------|------|-----|------|

| Supply Voltage Range                                   | V <sub>DD</sub>    |                    | -0.3 | 4.0 | V    |

| Analog Supply Voltage Range                            | V <sub>DDA</sub>   |                    | -0.3 | 4.0 | V    |

| ADC High Voltage Reference                             | V <sub>REFHx</sub> |                    | -0.3 | 4.0 | V    |

| Voltage difference V <sub>DD</sub> to V <sub>DDA</sub> | $\Delta V_{DD}$    |                    | -0.3 | 0.3 | V    |

| Voltage difference $V_{SS}$ to $V_{SSA}$               | $\Delta V_{SS}$    |                    | -0.3 | 0.3 | V    |

Table continues on the next page...

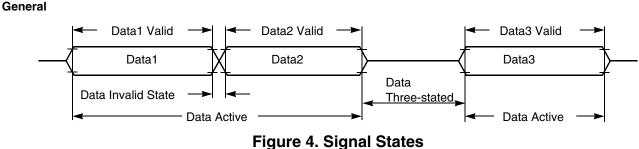

Figure 4. Signal States

## 7.3 Nonswitching electrical specifications

#### 7.3.1 Voltage and current operating requirements

This section includes information about recommended operating conditions.

Recommended  $V_{DD}$  ramp rate is between 1 ms and 200 ms.

NOTE

| Table 5. | Recommended Operating Conditions ( $V_{REFLx} = 0 V$ , $V_{SSA} = 0 V$ , |

|----------|--------------------------------------------------------------------------|

|          | $V_{SS} = 0 V$ )                                                         |

| Characteristic                                                    | Symbol                             | Notes <sup>1</sup> | Min                   | Тур | Мах                    | Unit |

|-------------------------------------------------------------------|------------------------------------|--------------------|-----------------------|-----|------------------------|------|

| Supply voltage <sup>2</sup>                                       | V <sub>DD</sub> , V <sub>DDA</sub> |                    | 2.7                   | 3.3 | 3.6                    | V    |

| ADC (Cyclic) Reference Voltage High                               | V <sub>REFHA</sub>                 |                    | 3.0                   |     | V <sub>DDA</sub>       | V    |

|                                                                   | V <sub>REFHB</sub>                 |                    |                       |     |                        |      |

| ADC (SAR) Reference Voltage High                                  | V <sub>REFHC</sub>                 |                    | 2.0                   |     | V <sub>DDA</sub>       | V    |

| Voltage difference V <sub>DD</sub> to V <sub>DDA</sub>            | ΔVDD                               |                    | -0.1                  | 0   | 0.1                    | V    |

| Voltage difference $V_{SS}$ to $V_{SSA}$                          | ΔVSS                               |                    | -0.1                  | 0   | 0.1                    | V    |

| Input Voltage High (digital inputs)                               | VIH                                | Pin Groups 1, 2    | 0.7 x V <sub>DD</sub> |     | 5.5                    | V    |

| Input Voltage Low (digital inputs)                                | V <sub>IL</sub>                    | Pin Groups 1, 2    |                       |     | 0.35 x V <sub>DD</sub> | V    |

| Oscillator Input Voltage High                                     | VIHOSC                             | Pin Group 4        | 2.0                   |     | V <sub>DD</sub> + 0.3  | V    |

| XTAL driven by an external clock source                           |                                    |                    |                       |     |                        |      |

| Oscillator Input Voltage Low                                      | VILOSC                             | Pin Group 4        | -0.3                  |     | 0.8                    | V    |

| Output Source Current High (at V <sub>OH</sub> min.) <sup>3</sup> | I <sub>ОН</sub>                    |                    |                       |     |                        |      |

| <ul> <li>Programmed for low drive strength</li> </ul>             |                                    | Pin Group 1        | _                     |     | -2                     | mA   |

| <ul> <li>Programmed for high drive strength</li> </ul>            |                                    | Pin Group 1        | _                     |     | -9                     |      |

| Output Source Current Low (at V <sub>OL</sub> max.) <sup>3</sup>  | I <sub>OL</sub>                    |                    |                       |     |                        |      |

| <ul> <li>Programmed for low drive strength</li> </ul>             |                                    | Pin Groups 1, 2    | _                     |     | 2                      | mA   |

| <ul> <li>Programmed for high drive strength</li> </ul>            |                                    | Pin Groups 1, 2    | _                     |     | 9                      |      |

#### 1. Default Mode

- Pin Group 1: GPIO, TDI, TDO, TMS, TCK

- Pin Group 2: RESET, GPIOA7

- Pin Group 3: ADC and Comparator Analog Inputs

# 7.3.5 Power consumption operating behaviors

| Table 9. | Current | Consum    | otion |

|----------|---------|-----------|-------|

|          | ••••••• | 001104111 |       |

| Mode               | Maximum Conditions<br>Frequency |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   | at 3.3 V,<br>j°C |                   | ım at 3.6<br>05°C |

|--------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-------------------|-------------------|

|                    |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                               | I <sub>DD</sub> 1 | I <sub>DDA</sub> | ا <sub>DD</sub> 1 | I <sub>DDA</sub>  |

| RUN                | 80 MHz                          | <ul> <li>80 MHz Device Clock</li> <li>Regulators are in full regulation</li> <li>Relaxation Oscillator on</li> <li>PLL powered on</li> <li>Continuous MAC instructions with fetches from<br/>Program Flash</li> <li>All peripheral modules enabled.</li> <li>TMRs and SCIs using 1X Clock</li> <li>NanoEdge within PWMA using 2X clock</li> <li>ADC/DAC powered on and clocked at 5 MHz<sup>2</sup></li> <li>Comparator powered on</li> </ul> | TBD               | TBD              | TBD               | TBD               |

| WAIT               | 80 MHz                          | <ul> <li>80 MHz Device Clock</li> <li>Regulators are in full regulation</li> <li>Relaxation Oscillator on</li> <li>PLL powered on</li> <li>Processor Core in WAIT state</li> <li>All Peripheral modules enabled.</li> <li>TMRs and SCIs using 1X Clock</li> <li>NanoEdge within PWMA using 2X clock</li> <li>ADC/DAC/Comparator powered off</li> </ul>                                                                                        | TBD               | TBD              | TBD               | TBD               |

| STOP               | 4 MHz                           | <ul> <li>4 MHz Device Clock</li> <li>Regulators are in full regulation</li> <li>Relaxation Oscillator on</li> <li>PLL powered off</li> <li>Processor Core in STOP state</li> <li>All peripheral module and core clocks are off</li> <li>ADC/DAC/Comparator powered off</li> </ul>                                                                                                                                                             | TBD               | TBD              | TBD               | TBD               |

| LPRUN<br>(LsRUN)   | 2 MHz                           | <ul> <li>200 kHz Device Clock from Relaxation Oscillator<br/>(ROSC)</li> <li>ROSC in standby mode</li> <li>Regulators are in standby</li> <li>PLL disabled</li> <li>Repeat NOP instructions</li> <li>All peripheral modules enabled, except NanoEdge<br/>and cyclic ADCs<sup>3</sup></li> <li>Simple loop with running from platform instruction<br/>buffer</li> </ul>                                                                        | TBD               | TBD              | TBD               | TBD               |

| LPWAIT<br>(LsWAIT) | 2 MHz                           | <ul> <li>200 kHz Device Clock from Relaxation Oscillator<br/>(ROSC)</li> <li>ROSC in standby mode</li> <li>Regulators are in standby</li> <li>PLL disabled</li> <li>All peripheral modules enabled, except NanoEdge<br/>and cyclic ADCs<sup>3</sup></li> <li>Processor core in wait mode</li> </ul>                                                                                                                                           | TBD               | TBD              | TBD               | TBD               |

Table continues on the next page...

## 7.4.1 Device clock specifications

Table 12. Device clock specifications

| Symbol             | Description                                                                                                                        | Min.       | Max.     | Unit | Notes |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------|------------|----------|------|-------|

| Normal run mode    |                                                                                                                                    | 9          |          |      |       |

| fsysclk            | <ul><li>Device (system and core) clock frequency</li><li>using relaxation oscillator</li><li>using external clock source</li></ul> | 0.001<br>0 | 80<br>80 | MHz  |       |

| f <sub>IPBUS</sub> | IP bus clock                                                                                                                       |            | 80       | MHz  |       |

# 7.4.2 General Switching Timing

Table 13. Switching Timing

| Symbol | Description                                                                                | Min | Max  | Unit                      | Notes |

|--------|--------------------------------------------------------------------------------------------|-----|------|---------------------------|-------|

|        | GPIO pin interrupt pulse width <sup>1</sup><br>Synchronous path                            | 1.5 |      | IP Bus<br>Clock<br>Cycles | 2     |

|        | Port rise and fall time (high drive strength), Slew disabled 2.7 $\leq V_{DD} \leq 3.6V$ . | 5.5 | 15.1 | ns                        | 3     |

|        | Port rise and fall time (high drive strength), Slew enabled 2.7 $\leq V_{DD} \leq 3.6V$ .  | 1.5 | 6.8  | ns                        | 3     |

|        | Port rise and fall time (low drive strength). Slew disabled . 2.7 $\leq V_{DD} \leq 3.6V$  | 8.2 | 17.8 | ns                        | 4     |

|        | Port rise and fall time (low drive strength). Slew enabled . 2.7 $\leq V_{DD} \leq 3.6V$   | 3.2 | 9.2  | ns                        | 4     |

1. Applies to a pin only when it is configured as GPIO and configured to cause an interrupt by appropriately programming GPIOn\_IPOLR and GPIOn\_IENR.

- 2. The greater synchronous and asynchronous timing must be met.

- 3. 75 pF load

- 4. 15 pF load

# 7.5 Thermal specifications

#### 7.5.1 Thermal operating requirements

Table 14. Thermal operating requirements

| Symbol         | Description                               | Min. | Max. | Unit |

|----------------|-------------------------------------------|------|------|------|

| TJ             | Die junction temperature                  | -40  | 125  | °C   |

| T <sub>A</sub> | Ambient temperature (extended industrial) | -40  | 105  | °C   |

## 7.5.2 Thermal attributes

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and voltage regulator circuits, and it is user-determined rather than being controlled by the MCU design. To account for  $P_{I/O}$  in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  is very small.

| Board type           | Symbol            | Description                                                                                                          | 48 LQFP | 64 LQFP | Unit | Notes |

|----------------------|-------------------|----------------------------------------------------------------------------------------------------------------------|---------|---------|------|-------|

| Single-layer<br>(1s) | R <sub>0JA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient (natural<br>convection)                                             | 70      | 64      | °C/W | 1, 2  |

| Four-layer<br>(2s2p) | R <sub>0JA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient (natural<br>convection)                                             | 46      | 46      | °C/W | 1, 3  |

| Single-layer<br>(1s) | R <sub>ejma</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200 ft./<br>min. air speed)                                        | 57      | 52      | °C/W | 1,3   |

| Four-layer<br>(2s2p) | R <sub>ejma</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200 ft./<br>min. air speed)                                        | 39      | 39      | °C/W | 1,3   |

| _                    | R <sub>0JB</sub>  | Thermal<br>resistance,<br>junction to<br>board                                                                       | 23      | 28      | °C/W | 4     |

| _                    | R <sub>θJC</sub>  | Thermal<br>resistance,<br>junction to case                                                                           | 17      | 15      | °C/W | 5     |

| _                    | Ψ <sub>JT</sub>   | Thermal<br>characterization<br>parameter,<br>junction to<br>package top<br>outside center<br>(natural<br>convection) | 3       | 3       | °C/W | 6     |

See Thermal Design Considerations for more detail on thermal design considerations.

#### Peripheral operating requirements and behaviors

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air) with the single layer board horizontal. For the LQFP, the board meets the JESD51-3 specification.

- 3. Determined according to JEDEC Standard JESD51-6, *Integrated Circuits Thermal Test Method Environmental Conditions Forced Convection (Moving Air)* with the board horizontal.

- 4. Determined according to JEDEC Standard JESD51-8, *Integrated Circuit Thermal Test Method Environmental Conditions—Junction-to-Board*. Board temperature is measured on the top surface of the board near the package.

- 5. Determined according to Method 1012.1 of MIL-STD 883, *Test Method Standard, Microcircuits*, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

- 6. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air).

## 8 Peripheral operating requirements and behaviors

#### 8.1 Core modules

#### 8.1.1 JTAG Timing

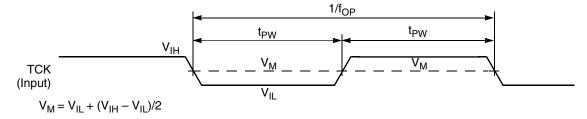

|                            |                 | 5   |           |      |               |

|----------------------------|-----------------|-----|-----------|------|---------------|

| Characteristic             | Symbol          | Min | Мах       | Unit | See<br>Figure |

| TCK frequency of operation | f <sub>OP</sub> | DC  | SYS_CLK/8 | MHz  | Figure 5      |

| TCK clock pulse width      | t <sub>PW</sub> | 50  |           | ns   | Figure 5      |

| TMS, TDI data set-up time  | t <sub>DS</sub> | 5   |           | ns   | Figure 6      |

| TMS, TDI data hold time    | t <sub>DH</sub> | 5   |           | ns   | Figure 6      |

| TCK low to TDO data valid  | t <sub>DV</sub> | —   | 30        | ns   | Figure 6      |

| TCK low to TDO tri-state   | t <sub>TS</sub> | —   | 30        | ns   | Figure 6      |

Figure 5. Test Clock Input Timing Diagram

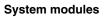

Figure 8. Relaxation Oscillator Temperature Variation (Typical) After Trim (Preliminary)

## 8.4 Memories and memory interfaces

#### 8.4.1 Flash Memory Characteristics Table 22. Flash Timing Parameters

| Characteristic                                  | Symbol        | Min | Тур | Max | Unit |

|-------------------------------------------------|---------------|-----|-----|-----|------|

| Longword Program high-voltage time <sup>1</sup> | thvpgm4       | —   | 63  | 143 | μs   |

| Sector Erase high-voltage time <sup>2</sup>     | thversscr     | —   | 13  | 113 | ms   |

| Erase Block high-voltage time for 256 KB        | thversblk256k | —   | 52  | 452 | ms   |

1. There is additional overhead that is part of the programming sequence. See the device Reference Manual for detail.

2. Specifies page erase time.

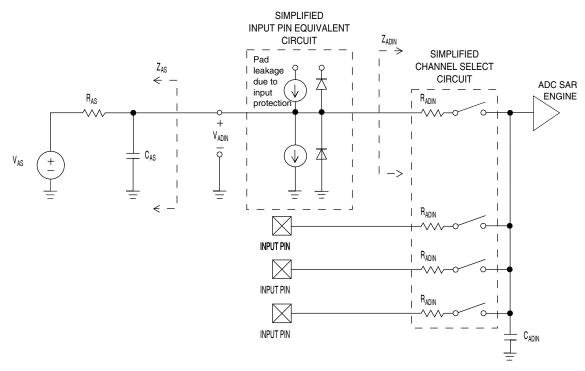

7. For guidelines and examples of conversion rate calculation, download the ADC calculator tool: http://cache.freescale.com/ files/soft\_dev\_tools/software/app\_software/converters/ADC\_CALCULATOR\_CNV.zip?fpsp=1

Figure 10. ADC input impedance equivalency diagram

#### 8.5.2.2 16-bit ADC electrical characteristics Table 27. 16-bit ADC characteristics (V<sub>REFH</sub> = V<sub>DDA</sub>, V<sub>REFL</sub> = V<sub>SSA</sub>)

| Symbol               | Description                  | Conditions <sup>1</sup>              | Min.           | Typ. <sup>2</sup> | Max.         | Unit             | Notes              |

|----------------------|------------------------------|--------------------------------------|----------------|-------------------|--------------|------------------|--------------------|

| I <sub>DDA_ADC</sub> | Supply current               |                                      |                | —                 | 1.7          | mA               | 3                  |

|                      | ADC                          | ADLPC=1, ADHSC=0                     | 1.2            | 2.4               | 3.9          | MHz              | $t_{ADACK} = 1/$   |

|                      | asynchronous<br>clock source | ADLPC=1, ADHSC=1                     | 3.0            | 4.0               | 7.3          | MHz              | f <sub>ADACK</sub> |

| f <sub>ADACK</sub>   |                              | ADLPC=0, ADHSC=0                     | 2.4            | 5.2               | 6.1          | MHz              |                    |

|                      |                              | ADLPC=0, ADHSC=1                     | 4.4            | 6.2               | 9.5          | MHz              |                    |

|                      | Sample Time                  | See Reference Manual chapter         | r for sample t | imes              |              |                  |                    |

| TUE                  | Total unadjusted             | 12 bit modes                         | _              | ±4                | ±6.8         | LSB <sup>4</sup> | 5                  |

|                      | error                        | • <12 bit modes                      |                | ±1.4              | ±2.1         |                  |                    |

| DNL                  | Differential non-            | 16 bit modes                         | _              | -1 to +4          |              | LSB <sup>4</sup> | 5                  |

|                      | linearity                    | 12 bit modes                         | _              | ±0.7              | TBD          |                  |                    |

|                      |                              | • <12 bit modes                      | _              | ±0.2              | -0.3 to 0.5  |                  |                    |

| INL                  | Integral non-                | 16 bit modes                         | —              | ±7.0              |              | LSB <sup>4</sup> | 5                  |

|                      | linearity                    | 12 bit modes                         | —              | ±1.0              | -2.7 to +1.9 |                  |                    |

|                      |                              | <ul> <li>&lt;12 bit modes</li> </ul> |                | ±0.5              | -0.7 to +0.5 |                  |                    |

Table continues on the next page...

#### System modules

| Parameter                           | Conditions/Comments                                                                     | Symbol              | Min                          | Тур        | Max                          | Unit             |

|-------------------------------------|-----------------------------------------------------------------------------------------|---------------------|------------------------------|------------|------------------------------|------------------|

| Integral non-linearity <sup>2</sup> | Range of input digital words:                                                           | INL                 | _                            | +/- 3      | +/- 4                        | LSB <sup>3</sup> |

|                                     | 410 to 3891 (\$19A - \$F33)                                                             |                     |                              |            |                              |                  |

|                                     | 5% to 95% of full range                                                                 |                     |                              |            |                              |                  |

| Differential non-                   | Range of input digital words:                                                           | DNL                 |                              | +/- 0.8    | +/- 0.9                      | LSB <sup>3</sup> |

| linearity <sup>2</sup>              | 410 to 3891 (\$19A - \$F33)                                                             |                     |                              |            |                              |                  |

|                                     | 5% to 95% of full range                                                                 |                     |                              |            |                              |                  |

| Monotonicity                        | > 6 sigma monotonicity,                                                                 |                     |                              | guaranteed |                              | —                |

|                                     | < 3.4 ppm non-monotonicity                                                              |                     |                              |            |                              |                  |

| Offset error <sup>2</sup>           | Range of input digital words:                                                           | V <sub>OFFSET</sub> | —                            | + 25       | + 35                         | mV               |

|                                     | 410 to 3891 (\$19A - \$F33)                                                             |                     |                              |            |                              |                  |

|                                     | 5% to 95% of full range                                                                 |                     |                              |            |                              |                  |

| Gain error <sup>2</sup>             | Range of input digital words: 410 to<br>3891 (\$19A - \$F33) 5% to 95% of<br>full range | E <sub>GAIN</sub>   | _                            | +/- 0.5    | +/- 1.5                      | %                |

|                                     | DAC C                                                                                   | Dutput              |                              |            |                              |                  |

| Output voltage range                | Within 40 mV of either $V_{SSA}$ or $V_{DDA}$                                           | V <sub>OUT</sub>    | V <sub>SSA</sub> +<br>0.04 V |            | V <sub>DDA</sub> - 0.04<br>V | V                |

|                                     | AC Speci                                                                                | fications           |                              |            |                              |                  |

| Signal-to-noise ratio               |                                                                                         | SNR                 |                              | 85         | _                            | dB               |

| Spurious free dynamic<br>range      |                                                                                         | SFDR                | —                            | -72        | —                            | dB               |

| Effective number of bits            |                                                                                         | ENOB                |                              | 11         | —                            | bits             |

#### Table 28. DAC Parameters (continued)

1. Settling time is swing range from  $V_{\text{SSA}}$  to  $V_{\text{DDA}}$

2. No guaranteed specification within 5% of  $V_{DDA}$  or  $V_{SSA}$

3. LSB = 0.806mV

#### 8.5.4 CMP and 6-bit DAC electrical specifications Table 29. Comparator and 6-bit DAC electrical specifications

| Symbol            | Description                                     | Min.                  | Тур. | Max.            | Unit |

|-------------------|-------------------------------------------------|-----------------------|------|-----------------|------|

| V <sub>DD</sub>   | Supply voltage                                  | 2.7                   | —    | 3.6             | V    |

| I <sub>DDHS</sub> | Supply current, High-speed mode (EN=1, PMODE=1) | _                     | —    | 200             | μA   |

| I <sub>DDLS</sub> | Supply current, low-speed mode (EN=1, PMODE=0)  | _                     | —    | 20              | μA   |

| V <sub>AIN</sub>  | Analog input voltage                            | V <sub>SS</sub> – 0.3 | _    | V <sub>DD</sub> | V    |

| V <sub>AIO</sub>  | Analog input offset voltage                     | _                     | _    | 20              | mV   |

Table continues on the next page...

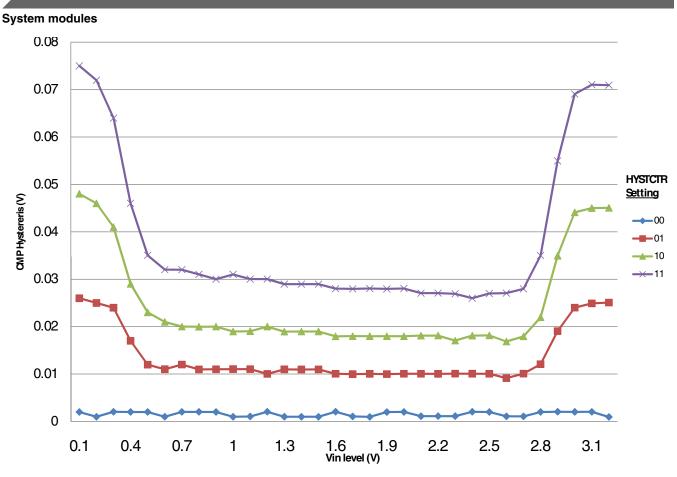

Figure 12. Typical hysteresis vs. Vin level ( $V_{DD}$  = 3.3 V, PMODE = 0)

## 8.6.2 Quad Timer Timing

Parameters listed are guaranteed by design.

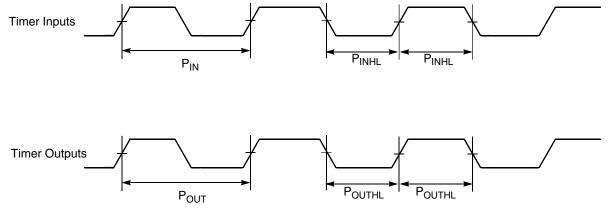

| Characteristic               | Symbol             | Min <sup>1</sup> | Max | Unit | See Figure |

|------------------------------|--------------------|------------------|-----|------|------------|

| Timer input period           | P <sub>IN</sub>    | 2T + 6           | —   | ns   | Figure 14  |

| Timer input high/low period  | P <sub>INHL</sub>  | 1T + 3           | _   | ns   | Figure 14  |

| Timer output period          | P <sub>OUT</sub>   | 25               | _   | ns   | Figure 14  |

| Timer output high/low period | P <sub>OUTHL</sub> | 12.5             | _   | ns   | Figure 14  |

Table 31. Timer Timing

1. T = clock cycle. For 80 MHz operation, T = 12.5 ns.

Figure 14. Timer Timing

### 8.7 Communication interfaces

### 8.7.1 Queued Serial Peripheral Interface (SPI) Timing

Parameters listed are guaranteed by design.

| Characteristic | Symbol         | Min | Max | Unit | See Figure |

|----------------|----------------|-----|-----|------|------------|

| Cycle time     | t <sub>C</sub> |     |     |      | Figure 15  |

| Master         |                | 45  | _   | ns   | Figure 16  |

| Slave          |                | 45  | _   | ns   | Figure 17  |

|                |                |     |     |      | Figure 18  |

Table continues on the next page...

| 64<br>LQFP | 48<br>LQFP | Pin Name | Default | ALTO    | ALT1    | ALT2      | ALT3   |

|------------|------------|----------|---------|---------|---------|-----------|--------|

| 37         | 29         | GPIOC11  | GPIOC11 | CANTX   | SCL1    | TXD1      |        |

| 38         | 30         | GPIOC12  | GPIOC12 | CANRX   | SDA1    | RXD1      |        |

| 39         | -          | GPIOF2   | GPIOF2  | SCL1    | XB_OUT6 |           |        |

| 40         | -          | GPIOF3   | GPIOF3  | SDA1    | XB_OUT7 |           |        |

| 41         | -          | GPIOF4   | GPIOF4  | TXD1    | XB_OUT8 |           |        |

| 42         | _          | GPIOF5   | GPIOF5  | RXD1    | XB_OUT9 |           |        |

| 43         | 31         | VSS      | VSS     |         |         |           |        |

| 44         | 32         | VDD      | VDD     |         |         |           |        |

| 45         | 33         | GPIOE0   | GPIOE0  | PWMA_0B |         |           |        |

| 46         | 34         | GPIOE1   | GPIOE1  | PWMA_0A |         |           |        |

| 47         | 35         | GPIOE2   | GPIOE2  | PWMA_1B |         |           |        |

| 48         | 36         | GPIOE3   | GPIOE3  | PWMA_1A |         |           |        |

| 49         | 37         | GPIOC13  | GPIOC13 | TA3     | XB_IN6  | EWM_OUT_B |        |

| 50         | 38         | GPIOF1   | GPIOF1  | CLKO1   | XB_IN7  | CMPD_O    |        |

| 51         | 39         | GPIOE4   | GPIOE4  | PWMA_2B | XB_IN2  |           |        |

| 52         | 40         | GPIOE5   | GPIOE5  | PWMA_2A | XB_IN3  |           |        |

| 53         | -          | GPIOE6   | GPIOE6  | PWMA_3B | XB_IN4  | PWMB_2B   |        |

| 54         | Ι          | GPIOE7   | GPIOE7  | PWMA_3A | XB_IN5  | PWMB_2A   |        |

| 55         | 41         | GPIOC14  | GPIOC14 | SDA0    | XB_OUT4 |           |        |

| 56         | 42         | GPIOC15  | GPIOC15 | SCL0    | XB_OUT5 |           |        |

| 57         | 43         | VCAP     | VCAP    |         |         |           |        |

| 58         | -          | GPIOF6   | GPIOF6  | TB2     | PWMA_3X | PWMB_3X   | XB_IN2 |

| 59         | -          | GPIOF7   | GPIOF7  | TB3     | CMPC_O  | SS1_B     | XB_IN3 |

| 60         | 44         | VDD      | VDD     |         |         |           |        |

| 61         | 45         | VSS      | VSS     |         |         |           |        |

| 62         | 46         |          |         | GPIOD1  |         |           |        |

| 63         | 47         |          |         | GPIOD3  |         |           |        |

| 64         | 48         |          |         | GPIOD0  |         |           |        |

### 11.2 Pinout diagrams

The following diagrams show pinouts for the packages. For each pin, the diagrams show the default function. However, many signals may be multiplexed onto a single pin.