Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | Coldfire V2                                                 |

| Core Size                  | 32-Bit Single-Core                                          |

| Speed                      | 66MHz                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                           |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 56                                                          |

| Program Memory Size        | 256KB (256K x 8)                                            |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 32K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                   |

| Data Converters            | A/D 8x12b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 81-LBGA                                                     |

| Supplier Device Package    | 81-MAPBGA (10x10)                                           |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcf5212lcvm66j |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

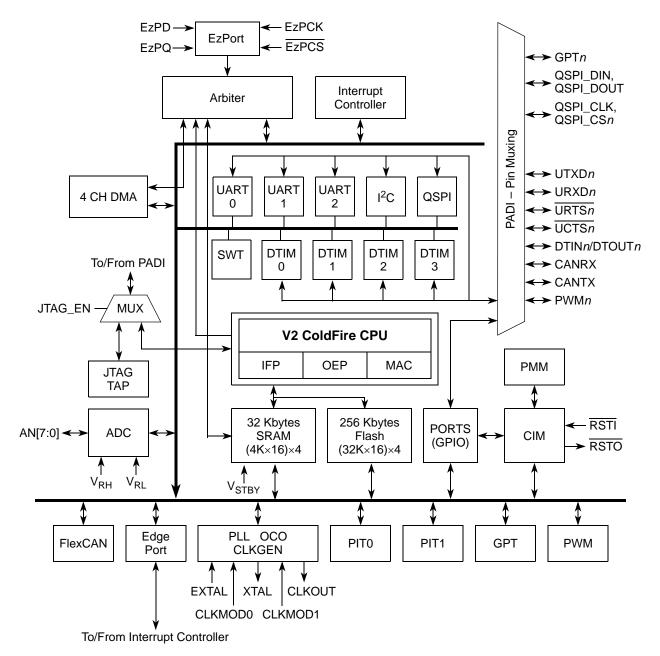

Figure 1. MCF5213 Block Diagram

# 1.1 Features

This document contains information on a new product under development. Freescale reserves the right to change or discontinue this product without notice. Specifications and information herein are subject to change without notice.

### **1.1.1 Feature Overview**

The MCF5213 family includes the following features:

- Version 2 ColdFire variable-length RISC processor core

- Static operation

- 32-bit address and data paths on-chip

- Up to 80 MHz processor core frequency

- Sixteen general-purpose, 32-bit data and address registers

- Implements ColdFire ISA\_A with extensions to support the user stack pointer register and four new instructions for improved bit processing (ISA\_A+)

- Multiply-Accumulate (MAC) unit with 32-bit accumulator to support  $16 \times 16 \rightarrow 32$  or  $32 \times 32 \rightarrow 32$  operations

- Illegal instruction decode that allows for 68-Kbyte emulation support

- System debug support

- Real-time trace for determining dynamic execution path

- Background debug mode (BDM) for in-circuit debugging (DEBUG\_B+)

- Real-time debug support, with six hardware breakpoints (4 PC, 1 address and 1 data) configurable into a 1- or 2-level trigger

- On-chip memories

- 32-Kbyte dual-ported SRAM on CPU internal bus, supporting core and DMA access with standby power supply support

- 256 Kbytes of interleaved flash memory supporting 2-1-1-1 accesses

- Power management

- Fully static operation with processor sleep and whole chip stop modes

- Rapid response to interrupts from the low-power sleep mode (wake-up feature)

- Clock enable/disable for each peripheral when not used

- FlexCAN 2.0B module

- Based on and includes all existing features of the Freescale TouCAN module

- Full implementation of the CAN protocol specification version 2.0B

- Standard data and remote frames (up to 109 bits long)

- Extended data and remote frames (up to 127 bits long)

- Zero to eight bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Flexible message buffers (MBs), totalling up to 16 message buffers of 0–8 byte data length each, configurable as Rx or Tx, all supporting standard and extended messages

- Unused MB space can be used as general purpose RAM space

- Listen-only mode capability

- Content-related addressing

- No read/write semaphores

- Three programmable mask registers: global for MBs 0-13, special for MB14, and special for MB15

- Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Three universal asynchronous/synchronous receiver transmitters (UARTs)

- 16-bit divider for clock generation

- Interrupt control logic with maskable interrupts

- DMA support

- Data formats can be 5, 6, 7 or 8 bits with even, odd, or no parity

- Up to two stop bits in 1/16 increments

- Programmable center or left aligned outputs on individual channels

- Four clock sources (A, B, SA, and SB) provide for a wide range of frequencies

- Emergency shutdown

- Two periodic interrupt timers (PITs)

- 16-bit counter

- Selectable as free running or count down

- Software watchdog timer

- 32-bit counter

- Low-power mode support

- Clock generation features

- One to 48 MHz crystal, 8 MHz on-chip relaxation oscillator, or external oscillator reference options

- Trimmed relaxation oscillator

- Two to 10 MHz reference frequency for normal PLL mode with a pre-divider programmable from 1 to 8

- System can be clocked from PLL or directly from crystal oscillator or relaxation oscillator

- Low power modes supported

- $2^n$  (n  $\le 0 \le 15$ ) low-power divider for extremely low frequency operation

- Interrupt controller

- Uniquely programmable vectors for all interrupt sources

- Fully programmable level and priority for all peripheral interrupt sources

- Seven external interrupt signals with fixed level and priority

- Unique vector number for each interrupt source

- Ability to mask any individual interrupt source or all interrupt sources (global mask-all)

- Support for hardware and software interrupt acknowledge (IACK) cycles

- Combinatorial path to provide wake-up from low-power modes

- DMA controller

- Four fully programmable channels

- Dual-address transfer support with 8-, 16-, and 32-bit data capability, along with support for 16-byte (4×32-bit) burst transfers

- Source/destination address pointers that can increment or remain constant

- 24-bit byte transfer counter per channel

- Auto-alignment transfers supported for efficient block movement

- Bursting and cycle steal support

- Software-programmable DMA requesters for the UARTs (3) and 32-bit timers (4)

- Reset

- Separate reset in and reset out signals

- Seven sources of reset:

- Power-on reset (POR)

- External

- Software

- Watchdog

- Loss of clock

- Loss of lock

- Low-voltage detection (LVD)

- Status flag indication of source of last reset

- Chip integration module (CIM)

### 1.1.7 FlexCAN

The FlexCAN module is a communication controller implementing version 2.0 of the CAN protocol parts A and B. The CAN protocol can be used as an industrial control serial data bus, meeting the specific requirements of reliable operation in a harsh EMI environment with high bandwidth. This instantiation of FlexCAN has 16 message buffers.

## 1.1.8 UARTs

The MCF5213 has three full-duplex UARTs that function independently. The three UARTs can be clocked by the system bus clock, eliminating the need for an external clock source. On smaller packages, the third UART is multiplexed with other digital I/O functions.

# 1.1.9 I<sup>2</sup>C Bus

The  $I^2C$  bus is a two-wire, bidirectional serial bus that provides a simple, efficient method of data exchange and minimizes the interconnection between devices. This bus is suitable for applications requiring occasional communications over a short distance between many devices.

### 1.1.10 QSPI

The queued serial peripheral interface (QSPI) provides a synchronous serial peripheral interface with queued transfer capability. It allows up to 16 transfers to be queued at once, minimizing the need for CPU intervention between transfers.

## 1.1.11 Fast ADC

The fast ADC consists of an eight-channel input select multiplexer and two independent sample and hold (S/H) circuits feeding separate 12-bit ADCs. The two separate converters store their results in accessible buffers for further processing.

The ADC can be configured to perform a single scan and halt, a scan when triggered, or a programmed scan sequence repeatedly until manually stopped.

The ADC can be configured for sequential or simultaneous conversion. When configured for sequential conversions, up to eight channels can be sampled and stored in any order specified by the channel list register. Both ADCs may be required during a scan, depending on the inputs to be sampled.

During a simultaneous conversion, both S/H circuits are used to capture two different channels at the same time. This configuration requires that a single channel may not be sampled by both S/H circuits simultaneously.

Optional interrupts can be generated at the end of the scan sequence if a channel is out of range (measures below the low threshold limit or above the high threshold limit set in the limit registers) or at several different zero crossing conditions.

# 1.1.12 DMA Timers (DTIM0–DTIM3)

There are four independent, DMA transfer capable 32-bit timers (DTIM0, DTIM1, DTIM2, and DTIM3) on the MCF5213. Each module incorporates a 32-bit timer with a separate register set for configuration and control. The timers can be configured to operate from the system clock or from an external clock source using one of the DTIN*n* signals. If the system clock is selected, it can be divided by 16 or 1. The input clock is further divided by a user-programmable 8-bit prescaler that clocks the actual timer counter register (TCR*n*). Each of these timers can be configured for input capture or reference (output) compare mode. Timer events may optionally cause interrupt requests or DMA transfers.

## 1.1.13 General Purpose Timer (GPT)

The general purpose timer (GPT) is a four-channel timer module consisting of a 16-bit programmable counter driven by a seven-stage programmable prescaler. Each of the four channels can be configured for input capture or output compare. Additionally, channel three, can be configured as a pulse accumulator.

A timer overflow function allows software to extend the timing capability of the system beyond the 16-bit range of the counter. The input capture and output compare functions allow simultaneous input waveform measurements and output waveform generation. The input capture function can capture the time of a selected transition edge. The output compare function can generate output waveforms and timer software delays. The 16-bit pulse accumulator can operate as a simple event counter or a gated time accumulator.

### 1.1.14 Periodic Interrupt Timers (PIT0 and PIT1)

The two periodic interrupt timers (PIT0 and PIT1) are 16-bit timers that provide interrupts at regular intervals with minimal processor intervention. Each timer can count down from the value written in its PIT modulus register or it can be a free-running down-counter.

### 1.1.15 Pulse-Width Modulation (PWM) Timers

The MCF5213 has an 8-channel, 8-bit PWM timer. Each channel has a programmable period and duty cycle as well as a dedicated counter. Each of the modulators can create independent continuous waveforms with software-selectable duty rates from 0% to 100%. The PWM outputs have programmable polarity, and can be programmed as left aligned outputs or center aligned outputs. For higher period and duty cycle resolution, each pair of adjacent channels ([7:6], [5:4], [3:2], and [1:0]) can be concatenated to form a single 16-bit channel. The module can, therefore, be configured to support 8/0, 6/1, 4/2, 2/3, or 0/4 8-/16-bit channels.

### 1.1.16 Software Watchdog Timer

The watchdog timer is a 32-bit timer that facilitates recovery from runaway code. The watchdog counter is a free-running down-counter that generates a reset on underflow. To prevent a reset, software must periodically restart the countdown.

# 1.1.17 Phase-Locked Loop (PLL)

The clock module contains a crystal oscillator, 8 MHz on-chip relaxation oscillator (OCO), phase-locked loop (PLL), reduced frequency divider (RFD), low-power divider status/control registers, and control logic. To improve noise immunity, the PLL, crystal oscillator, and relaxation oscillator have their own power supply inputs: VDDPLL and VSSPLL. All other circuits are powered by the normal supply pins, VDD and VSS.

## 1.1.18 Interrupt Controller (INTC)

The MCF5213 has a single interrupt controller that supports up to 63 interrupt sources. There are 56 programmable sources, 49 of which are assigned to unique peripheral interrupt requests. The remaining seven sources are unassigned and may be used for software interrupt requests.

## 1.1.19 DMA Controller

The direct memory access (DMA) controller provides an efficient way to move blocks of data with minimal processor intervention. It has four channels that allow byte, word, longword, or 16-byte burst line transfers. These transfers are triggered by software explicitly setting a DCR*n*[START] bit or by the occurrence of certain UART or DMA timer events.

### 1.1.20 Reset

The reset controller determines the source of reset, asserts the appropriate reset signals to the system, and keeps track of what caused the last reset. There are seven sources of reset:

- External reset input

- Power-on reset (POR)

- Watchdog timer

- Phase locked-loop (PLL) loss of lock

- PLL loss of clock

- Software

- Low-voltage detector (LVD)

Control of the LVD and its associated reset and interrupt are managed by the reset controller. Other registers provide status flags indicating the last source of reset and a control bit for software assertion of the  $\overline{\text{RSTO}}$  pin.

### 1.1.21 GPIO

Nearly all pins on the MCF5213 have general purpose I/O capability and are grouped into 8-bit ports. Some ports do not use all eight bits. Each port has registers that configure, monitor, and control the port pins.

### 1.1.22 Part Numbers and Packaging

This product is RoHS-compliant. Refer to the product page at freescale.com or contact your sales office for up-to-date RoHS information.

| Freescale Part<br>Number | Description                               | Speed  | Package   | Temperature   |

|--------------------------|-------------------------------------------|--------|-----------|---------------|

| MCF5211CAE66             | MCF5211 ColdFire Microcontroller          | 66 MHz | 64 LQFP   | -40 to +85 °C |

| MCF5211CEP66             | MCF5211 ColdFire Microcontroller, FlexCAN | 66 MHz | 64 QFN    | -40 to +85 °C |

| MCF5211LCEP66            | MCF5211 ColdFire Microcontroller          | 66 MHz | 64 QFN    | -40 to +85 °C |

| MCF5211LCVM66            | MCF5211 ColdFire Microcontroller          | 66 MHz | 81 MAPBGA | -40 to +85 °C |

| MCF5211LCVM80            | MCF5211 ColdFire Microcontroller          | 80 MHz | 81 MAPBGA | -40 to +85 °C |

| MCF5212CAE66             | MCF5212 ColdFire Microcontroller          | 66 MHz | 64 LQFP   | -40 to +85 °C |

| MCF5212LCVM66            | MCF5212 ColdFire Microcontroller          | 66 MHz | 81 MAPBGA | -40 to +85 °C |

| MCF5212LCVM80            | MCF5212 ColdFire Microcontroller          | 80 MHz | 81 MAPBGA | -40 to +85 °C |

| MCF5213CAF66             | MCF5213 ColdFire Microcontroller, FlexCAN | 66 MHz | 100 LQFP  | -40 to +85 °C |

| MCF5213CAF80             | MCF5213 ColdFire Microcontroller, FlexCAN | 80 MHz | 100 LQFP  | -40 to +85 °C |

| MCF5213LCVM66            | MCF5213 ColdFire Microcontroller, FlexCAN | 66 MHz | 81 MAPBGA | -40 to +85 °C |

| MCF5213LCVM80            | MCF5213 ColdFire Microcontroller, FlexCAN | 80 MHz | 81 MAPBGA | -40 to +85 °C |

#### Table 2. Orderable Part Number Summary

Figure 3 shows the pinout configuration for the 81 MAPBGA.

|   | 1               | 2        | 3               | 4               | 5               | 6               | 7                | 8                   | 9                |

|---|-----------------|----------|-----------------|-----------------|-----------------|-----------------|------------------|---------------------|------------------|

| A | V <sub>SS</sub> | UTXD1    | RSTI            | IRQ5            | IRQ3            | ALLPST          | TDO              | TMS                 | V <sub>SS</sub>  |

| В | URTS1           | URXD1    | RSTO            | IRQ6            | IRQ2            | TRST            | TDI              | V <sub>DD</sub> PLL | EXTAL            |

| С | UCTS0           | TEST     | UCTS1           | IRQ7            | IRQ4            | IRQ1            | TCLK             | V <sub>SS</sub> PLL | XTAL             |

| D | URXD0           | UTXD0    | URTS0           | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | PWM7             | GPT3                | GPT2             |

| E | SCL             | SDA      | V <sub>DD</sub>  | PWM5                | GPT1             |

| F | QSPI_CS3        | QSPI_CS2 | QSPI_DIN        | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | GPT0             | V <sub>STBY</sub>   | AN4              |

| G | QSPI_DOUT       | QSPI_CLK | RCON            | DTIN1           | CLKMOD0         | AN2             | AN3              | AN5                 | AN6              |

| Н | QSPI_CS0        | QSPI_CS1 | DTIN3           | DTIN0           | CLKMOD1         | AN1             | V <sub>SSA</sub> | V <sub>DDA</sub>    | AN7              |

| J | V <sub>SS</sub> | JTAG_EN  | DTIN2           | PWM3            | PWM1            | AN0             | V <sub>RL</sub>  | V <sub>RH</sub>     | V <sub>SSA</sub> |

Figure 3. 81 MAPBGA Pin Assignments

|  | 7 |  |

|--|---|--|

|  |   |  |

|  |   |  |

Freescale Semiconductor

MCF5213 ColdFire Microcontroller, Rev. 3

| Pin<br>Group           | Primary<br>Function | Secondary<br>Function | Tertiary<br>Function | Quaternary<br>Function | Drive<br>Strength /<br>Control <sup>1</sup> | Slew Rate /<br>Control <sup>1</sup> | Pull-up /<br>Pull-down <sup>2</sup> | Pin on<br>100 LQFP | Pin on 81<br>MAPBGA | Pin on 64<br>LQFP/QFN |

|------------------------|---------------------|-----------------------|----------------------|------------------------|---------------------------------------------|-------------------------------------|-------------------------------------|--------------------|---------------------|-----------------------|

| Interrupts             | IRQ7                | _                     |                      | GPIO                   | Low                                         | FAST                                | pull-up                             | 95                 | C4                  | 58                    |

|                        | IRQ6                | _                     |                      | GPIO                   | Low                                         | FAST                                | pull-up                             | 94                 | B4                  | —                     |

|                        | IRQ5                | _                     |                      | GPIO                   | Low                                         | FAST                                | pull-up                             | 91                 | A4                  | —                     |

|                        | IRQ4                | —                     | _                    | GPIO                   | Low                                         | FAST                                | pull-up                             | 90                 | C5                  | 57                    |

|                        | IRQ3                | —                     | _                    | GPIO                   | Low                                         | FAST                                | pull-up                             | 89                 | A5                  | —                     |

|                        | IRQ2                | —                     | _                    | GPIO                   | Low                                         | FAST                                | pull-up                             | 88                 | B5                  | —                     |

|                        | IRQ1                | SYNCA                 | PWM1                 | GPIO                   | High                                        | FAST                                | pull-up <sup>5</sup>                | 87                 | C6                  | 56                    |

| JTAG/BDM               | JTAG_EN             | —                     | _                    | —                      | N/A                                         | N/A                                 | pull-down                           | 26                 | J2                  | 17                    |

|                        | TCLK/<br>PSTCLK     | CLKOUT                | _                    | —                      | High                                        | FAST                                | pull-up <sup>6</sup>                | 64                 | C7                  | 44                    |

|                        | TDI/DSI             | —                     |                      | —                      | N/A                                         | N/A                                 | pull-up <sup>6</sup>                | 79                 | B7                  | 50                    |

|                        | TDO/DSO             | —                     | _                    | —                      | High                                        | FAST                                | —                                   | 80                 | A7                  | 51                    |

|                        | TMS<br>/BKPT        | _                     | _                    | —                      | N/A                                         | N/A                                 | pull-up <sup>6</sup>                | 76                 | A8                  | 49                    |

|                        | TRST<br>/DSCLK      | _                     | _                    | —                      | N/A                                         | N/A                                 | pull-up <sup>6</sup>                | 85                 | B6                  | 54                    |

| Mode                   | CLKMOD0             | —                     |                      | —                      | N/A                                         | N/A                                 | pull-down <sup>7</sup>              | 40                 | G5                  | 24                    |

| Selection <sup>7</sup> | CLKMOD1             | _                     | _                    | —                      | N/A                                         | N/A                                 | pull-down <sup>7</sup>              | 39                 | H5                  | —                     |

|                        | RCON/<br>EZPCS      | _                     | _                    | —                      | N/A                                         | N/A                                 | pull-up                             | 21                 | G3                  | 16                    |

| PWM                    | PWM7                | _                     | _                    | GPIO                   | PDSR[31]                                    | PSRR[31]                            | —                                   | 63                 | D7                  | —                     |

|                        | PWM5                | —                     | _                    | GPIO                   | PDSR[30]                                    | PSRR[30]                            | —                                   | 60                 | E8                  | —                     |

|                        | PWM3                | —                     | _                    | GPIO                   | PDSR[29]                                    | PSRR[29]                            | —                                   | 33                 | J4                  | —                     |

|                        | PWM1                | _                     |                      | GPIO                   | PDSR[28]                                    | PSRR[28]                            | —                                   | 38                 | J5                  | —                     |

### Table 3. Pin Functions by Primary and Alternate Purpose (continued)

17

| Pin<br>Group       | Primary<br>Function | Secondary<br>Function | Tertiary<br>Function | Quaternary<br>Function | Drive<br>Strength /<br>Control <sup>1</sup> | Slew Rate /<br>Control <sup>1</sup> | Pull-up /<br>Pull-down <sup>2</sup> | Pin on<br>100 LQFP | Pin on 81<br>MAPBGA | Pin on 64<br>LQFP/QFN |

|--------------------|---------------------|-----------------------|----------------------|------------------------|---------------------------------------------|-------------------------------------|-------------------------------------|--------------------|---------------------|-----------------------|

| QSPI               | QSPI_DIN/<br>EZPD   | CANRX <sup>4</sup>    | URXD1                | GPIO                   | PDSR[2]                                     | PSRR[2]                             |                                     | 16                 | F3                  | 12                    |

|                    | QSPI_DOUT/<br>EZPQ  | CANTX <sup>4</sup>    | UTXD1                | GPIO                   | PDSR[1]                                     | PSRR[1]                             | —                                   | 17                 | G1                  | 13                    |

|                    | QSPI_CLK/<br>EZPCK  | SCL                   | URTS1                | GPIO                   | PDSR[3]                                     | PSRR[3]                             | pull-up <sup>8</sup>                | 18                 | G2                  | 14                    |

|                    | QSPI_CS3            | SYNCA                 | SYNCB                | GPIO                   | PDSR[7]                                     | PSRR[7]                             | _                                   | 12                 | F1                  | —                     |

|                    | QSPI_CS2            | _                     | —                    | GPIO                   | PDSR[6]                                     | PSRR[6]                             | —                                   | 13                 | F2                  | —                     |

|                    | QSPI_CS1            | _                     | _                    | GPIO                   | PDSR[5]                                     | PSRR[5]                             | _                                   | 19                 | H2                  | —                     |

|                    | QSPI_CS0            | SDA                   | UCTS1                | GPIO                   | PDSR[4]                                     | PSRR[4]                             | pull-up <sup>8</sup>                | 20                 | H1                  | 15                    |

| Reset <sup>9</sup> | RSTI                | _                     | _                    | —                      | N/A                                         | N/A                                 | pull-up <sup>9</sup>                | 96                 | A3                  | 59                    |

|                    | RSTO                | _                     | —                    | —                      | high                                        | FAST                                | _                                   | 97                 | B3                  | 60                    |

| Test               | TEST                | _                     | —                    | —                      | N/A                                         | N/A                                 | pull-down                           | 5                  | C2                  | 3                     |

| Timers, 16-bit     | GPT3                | _                     | PWM7                 | GPIO                   | PDSR[23]                                    | PSRR[23]                            | pull-up <sup>10</sup>               | 62                 | D8                  | 43                    |

|                    | GPT2                | _                     | PWM5                 | GPIO                   | PDSR[22]                                    | PSRR[22]                            | pull-up <sup>10</sup>               | 61                 | D9                  | 42                    |

|                    | GPT1                | _                     | PWM3                 | GPIO                   | PDSR[21]                                    | PSRR[21]                            | pull-up <sup>10</sup>               | 59                 | E9                  | 41                    |

|                    | GPT0                | _                     | PWM1                 | GPIO                   | PDSR[20]                                    | PSRR[20]                            | pull-up <sup>10</sup>               | 58                 | F7                  | 40                    |

| Timers, 32-bit     | DTIN3               | DTOUT3                | PWM6                 | GPIO                   | PDSR[19]                                    | PSRR[19]                            | _                                   | 32                 | H3                  | 19                    |

|                    | DTIN2               | DTOUT2                | PWM4                 | GPIO                   | PDSR[18]                                    | PSRR[18]                            | _                                   | 31                 | JЗ                  | 18                    |

|                    | DTIN1               | DTOUT1                | PWM2                 | GPIO                   | PDSR[17]                                    | PSRR[17]                            | _                                   | 37                 | G4                  | 23                    |

|                    | DTIN0               | DTOUT0                | PWM0                 | GPIO                   | PDSR[16]                                    | PSRR[16]                            | _                                   | 36                 | H4                  | 22                    |

| UART 0             | UCTS0               | CANRX                 | _                    | GPIO                   | PDSR[11]                                    | PSRR[11]                            | _                                   | 6                  | C1                  | 4                     |

|                    | URTS0               | CANTX                 |                      | GPIO                   | PDSR[10]                                    | PSRR[10]                            | _                                   | 9                  | D3                  | 7                     |

|                    | URXD0               | _                     |                      | GPIO                   | PDSR[9]                                     | PSRR[9]                             | _                                   | 7                  | D1                  | 5                     |

|                    | UTXD0               | _                     | _                    | GPIO                   | PDSR[8]                                     | PSRR[8]                             |                                     | 8                  | D2                  | 6                     |

Table 3. Pin Functions by Primary and Alternate Purpose (continued)

MCF5213 Family Configurations

18

# 1.8 UART Module Signals

Table 11 describes the UART module signals.

| Table 11 | . UART | Module | Signals |

|----------|--------|--------|---------|

|----------|--------|--------|---------|

| Signal Name                    | Abbreviation | Function                                                                                                                                                                                                                                                          | I/O |

|--------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Transmit Serial Data<br>Output | UTXDn        | Transmitter serial data outputs for the UART modules. The output is held high (mark condition) when the transmitter is disabled, idle, or in the local loopback mode. Data is shifted out, LSB first, on this pin at the falling edge of the serial clock source. | 0   |

| Receive Serial Data<br>Input   | URXDn        | Receiver serial data inputs for the UART modules. Data is received on this pin LSB first. When the UART clock is stopped for power-down mode, any transition on this pin restarts the clock.                                                                      | I   |

| Clear-to-Send                  | UCTSn        | Indication to the UART modules that they can begin data transmission.                                                                                                                                                                                             | Ι   |

| Request-to-Send                | URTSn        | Automatic request-to-send outputs from the UART modules. This signal can also be configured to be asserted and negated as a function of the RxFIFO level.                                                                                                         | 0   |

# 1.9 DMA Timer Signals

Table 12 describes the signals of the four DMA timer modules.

#### Table 12. DMA Timer Signals

| Signal Name      | Abbreviation | Function                                        | I/O |

|------------------|--------------|-------------------------------------------------|-----|

| DMA Timer Input  | DTIN         | Event input to the DMA timer modules.           | Ι   |

| DMA Timer Output | DTOUT        | Programmable output from the DMA timer modules. | 0   |

# 1.10 ADC Signals

Table 13 describes the signals of the Analog-to-Digital Converter.

#### Table 13. ADC Signals

| Signal Name      | Abbreviation     | Function                                                            | I/O |

|------------------|------------------|---------------------------------------------------------------------|-----|

| Analog Inputs    | AN[7:0]          | Inputs to the analog-to-digital converter.                          | I   |

| Analog Reference | V <sub>RH</sub>  | Reference voltage high and low inputs.                              | I   |

|                  | V <sub>RL</sub>  |                                                                     | I   |

| Analog Supply    | V <sub>DDA</sub> | Isolate the ADC circuitry from power supply noise.                  |     |

|                  | V <sub>SSA</sub> |                                                                     |     |

| ADC Sync Inputs  | SYNCA /<br>SYNCB | These signals can initiate an analog-to-digital conversion process. | I   |

# 1.11 General Purpose Timer Signals

Table 14 describes the general purpose timer signals.

Table 14. GPT Signals

| Signal Name                           | Abbreviation | Function                                                    | I/O |

|---------------------------------------|--------------|-------------------------------------------------------------|-----|

| General Purpose Timer<br>Input/Output | GPT[3:0]     | Inputs to or outputs from the general purpose timer module. | I/O |

# 1.12 Pulse Width Modulator Signals

Table 15 describes the PWM signals.

| Signal Name         | Abbreviation | Function                                       | I/O |

|---------------------|--------------|------------------------------------------------|-----|

| PWM Output Channels | PWM[7:0]     | Pulse width modulated output for PWM channels. | 0   |

# 1.13 Debug Support Signals

These signals are used as the interface to the on-chip JTAG controller and the BDM logic.

| Signal Name                 | Abbreviation | Function                                                                                                                                                                                                                                                                                                                                                                                                  | I/O |

|-----------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| JTAG Enable                 | JTAG_EN      | Select between debug module and JTAG signals at reset.                                                                                                                                                                                                                                                                                                                                                    | I   |

| Test Reset                  | TRST         | This active-low signal is used to initialize the JTAG logic asynchronously.                                                                                                                                                                                                                                                                                                                               | I   |

| Test Clock                  | TCLK         | Used to synchronize the JTAG logic.                                                                                                                                                                                                                                                                                                                                                                       | I   |

| Test Mode Select            | TMS          | Used to sequence the JTAG state machine. TMS is sampled on the rising edge of TCLK.                                                                                                                                                                                                                                                                                                                       | I   |

| Test Data Input             | TDI          | Serial input for test instructions and data. TDI is sampled on the rising edge of TCLK.                                                                                                                                                                                                                                                                                                                   | I   |

| Test Data Output            | TDO          | Serial output for test instructions and data. TDO is tri-stateable and is actively driven in the shift-IR and shift-DR controller states. TDO changes on the falling edge of TCLK.                                                                                                                                                                                                                        | 0   |

| Development Serial<br>Clock | DSCLK        | Development Serial Clock - Internally synchronized input. (The logic<br>level on DSCLK is validated if it has the same value on two<br>consecutive rising bus clock edges.) Clocks the serial communication<br>port to the debug module during packet transfers. Maximum frequency<br>is PSTCLK/5. At the synchronized rising edge of DSCLK, the data<br>input on DSI is sampled and DSO changes state.   | I   |

| Breakpoint                  | ВКРТ         | Breakpoint - Input used to request a manual breakpoint. Assertion of BKPT puts the processor into a halted state after the current instruction completes. Halt status is reflected on processor status/debug data signals (PST[3:0] and PSTDDATA[7:0]) as the value 0xF. If CSR[BKD] is set (disabling normal BKPT functionality), asserting BKPT generates a debug interrupt exception in the processor. | I   |

Table 16. Debug Support Signals

| Signal Name                     | Abbreviation | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I/O |

|---------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Development Serial<br>Input     | DSI          | Development Serial Input - Internally synchronized input that provides data input for the serial communication port to the debug module, after the DSCLK has been seen as high (logic 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I   |

| Development Serial<br>Output    | DSO          | evelopment Serial Output - Provides serial output communication for<br>ebug module responses. DSO is registered internally. The output is<br>elayed from the validation of DSCLK high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| Debug Data                      | DDATA[3:0]   | Display captured processor data and breakpoint status. The CLKOUT signal can be used by the development system to know when to sample DDATA[3:0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0   |

| Processor Status Clock          | PSTCLK       | Processor Status Clock - Delayed version of the processor clock. Its rising edge appears in the center of valid PST and DDATA output. PSTCLK indicates when the development system should sample PST and DDATA values.<br>If real-time trace is not used, setting CSR[PCD] keeps PSTCLK, and PST and DDATA outputs from toggling without disabling triggers.<br>Non-quiescent operation can be reenabled by clearing CSR[PCD], although the external development systems must resynchronize with the PST and DDATA outputs.<br>PSTCLK starts clocking only when the first non-zero PST value (0xC, 0xD, or 0xF) occurs during system reset exception processing. | 0   |

| Processor Status<br>Outputs     | PST[3:0]     | Indicate core status. Debug mode timing is synchronous with the processor clock; status is unrelated to the current bus transfer. The CLKOUT signal can be used by the development system to know when to sample PST[3:0].                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0   |

| All Processor Status<br>Outputs | ALLPST       | Logical AND of PST[3:0]. The CLKOUT signal can be used by the development system to know when to sample ALLPST.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0   |

| Table 16 | . Debug | Support | Signals | (continued) |

|----------|---------|---------|---------|-------------|

|----------|---------|---------|---------|-------------|

# 1.14 EzPort Signal Descriptions

Table contains a list of EzPort external signals.

| Signal Name            | Abbreviation | Function                                                          | I/O |

|------------------------|--------------|-------------------------------------------------------------------|-----|

| EzPort Clock           | EZPCK        | Shift clock for EzPort transfers.                                 | Ι   |

| EzPort Chip Select     | EZPCS        | Chip select for signalling the start and end of serial transfers. | I   |

| EzPort Serial Data In  | EZPD         | EZPD is sampled on the rising edge of EZPCK.                      | I   |

| EzPort Serial Data Out | EZPQ         | EZPQ transitions on the falling edge of EZPCK.                    | 0   |

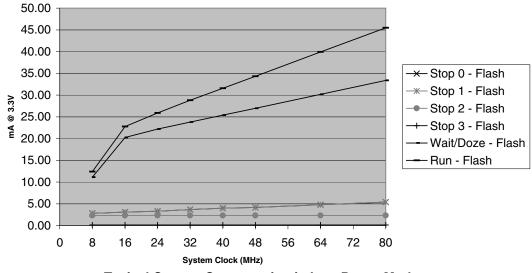

## 2.2 Current Consumption

| Mode                                 | 8MHz (Typ) <sup>3</sup> | 16MHz (Typ) <sup>2</sup> | 64MHz (Typ) <sup>2</sup> | 80MHz (Typ) <sup>2</sup> | Units |

|--------------------------------------|-------------------------|--------------------------|--------------------------|--------------------------|-------|

| Stop mode 3 (Stop 11) <sup>4</sup>   |                         | 0                        | .13                      |                          | mA    |

| Stop mode 2 (Stop 10) <sup>4</sup>   |                         | 2.29                     |                          |                          |       |

| Stop mode 1 (Stop 01) <sup>4,5</sup> | 2.80                    | 3.08                     | 4.76                     | 5.38                     |       |

| Stop mode 0 (Stop 00) <sup>4</sup>   | 2.80                    | 3.08                     | 4.76                     | 5.39                     |       |

| Wait / Doze                          | 11.12                   | 20.23                    | 30.17                    | 33.36                    |       |

| Run                                  | 12.40                   | 22.74                    | 39.92                    | 45.47                    |       |

#### Table 20. Current Consumption in Low-Power Mode<sup>1,2</sup>

<sup>1</sup> All values are measured with a 3.30 V power supply

<sup>2</sup> Refer to the Power Management chapter in the MCF5213 Reference Manual for more information on low-power modes.

<sup>3</sup> CLKOUT and all peripheral clocks except UART0 and CFM off before entering low power mode. CLKOUT is disabled. All code executed from flash memory. Code run from SRAM reduces power consumption further. Tests performed at room temperature.

<sup>4</sup> See the description of the Low-Power Control Register (LPCR) in the MCF5213 Reference Manual for more information on stop modes 0–3.

<sup>5</sup> Results are identical to STOP 00 for typical values because they only differ by CLKOUT power consumption. CLKOUT is already disabled in this instance prior to entering low power mode.

Typical Current Consumption in Low-Power Modes

|           | Characteristic                          | ;                       | Symbol           | Value             | Unit |

|-----------|-----------------------------------------|-------------------------|------------------|-------------------|------|

| 81 MAPBGA | Junction to ambient, natural convection | Single layer board (1s) | $\theta_{JA}$    | 61 <sup>1,2</sup> | °C/W |

|           | Junction to ambient, natural convection | Four layer board (2s2p) | $\theta_{JA}$    | 35 <sup>2,3</sup> | °C/W |

|           | Junction to ambient, (@200 ft/min)      | Single layer board (1s) | θ <sub>JMA</sub> | 50 <sup>2,3</sup> | °C/W |

|           | Junction to ambient, (@200 ft/min)      | Four layer board (2s2p) | $\theta_{JMA}$   | 31 <sup>2,3</sup> | °C/W |

|           | Junction to board                       | —                       | $\theta_{JB}$    | 20 <sup>4</sup>   | °C/W |

|           | Junction to case                        | —                       | θ <sub>JC</sub>  | 12 <sup>5</sup>   | °C/W |

|           | Junction to top of package              | Natural convection      | Ψ <sub>jt</sub>  | 2 <sup>6</sup>    | °C/W |

|           | Maximum operating junction temperature  | —                       | Тj               | 105               | °C   |

| 64 LQFP   | Junction to ambient, natural convection | Single layer board (1s) | $\theta_{JA}$    | 62 <sup>1,2</sup> | °C/W |

|           | Junction to ambient, natural convection | Four layer board (2s2p) | $\theta_{JA}$    | 43 <sup>1,3</sup> | °C/W |

|           | Junction to ambient (@200 ft/min)       | Single layer board (1s) | $\theta_{JMA}$   | 50 <sup>1,3</sup> | °C/W |

|           | Junction to ambient (@200 ft/min)       | Four layer board (2s2p) | $\theta_{JMA}$   | 36 <sup>1,3</sup> | °C/W |

|           | Junction to board                       | —                       | $\theta_{JB}$    | 26 <sup>4</sup>   | °C/W |

|           | Junction to case                        | —                       | $\theta^{JC}$    | 9 <sup>5</sup>    | °C/W |

|           | Junction to top of package              | Natural convection      | Ψ <sub>jt</sub>  | 2 <sup>6</sup>    | °C/W |

|           | Maximum operating junction temperature  | —                       | Тj               | 105               | °C   |

| 64 QFN    | Junction to ambient, natural convection | Single layer board (1s) | $\theta_{JA}$    | 68 <sup>1,2</sup> | °C/W |

|           | Junction to ambient, natural convection | Four layer board (2s2p) | $\theta_{JA}$    | 24 <sup>1,3</sup> | °C/W |

|           | Junction to ambient (@200 ft/min)       | Single layer board (1s) | $\theta_{JMA}$   | 55 <sup>1,3</sup> | °C/W |

|           | Junction to ambient (@200 ft/min)       | Four layer board (2s2p) | $\theta_{JMA}$   | 19 <sup>1,3</sup> | °C/W |

|           | Junction to board                       | —                       | $\theta_{JB}$    | 8 <sup>4</sup>    | °C/W |

|           | Junction to case (bottom)               | —                       | θ <sub>JC</sub>  | 0.6 <sup>5</sup>  | °C/W |

|           | Junction to top of package              | Natural convection      | Ψ <sub>jt</sub>  | 3 <sup>6</sup>    | °C/W |

|           | Maximum operating junction temperature  | —                       | Тj               | 105               | °C   |

#### Table 22. Thermal Characteristics (continued)

<sup>1</sup>  $\theta_{JA}$  and  $\Psi_{jt}$  parameters are simulated in conformance with EIA/JESD Standard 51-2 for natural convection. Freescale recommends the use of  $\theta_{JA}$  and power dissipation specifications in the system design to prevent device junction temperatures from exceeding the rated specification. System designers should be aware that device junction temperatures can be significantly influenced by board layout and surrounding devices. Conformance to the device junction temperature specification can be verified by physical measurement in the customer's system using the  $\Psi_{jt}$  parameter, the device power dissipation, and the method described in EIA/JESD Standard 51-2.

- <sup>2</sup> Per JEDEC JESD51-2 with the single-layer board (JESD51-3) horizontal.

- <sup>3</sup> Per JEDEC JESD51-6 with the board JESD51-7) horizontal.

- <sup>4</sup> Thermal resistance between the die and the printed circuit board in conformance with JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- <sup>5</sup> Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- <sup>6</sup> Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written in conformance with Psi-JT.

### 2.5 ESD Protection

| Characteristics                                                                             | Symbol              | Value  | Units |

|---------------------------------------------------------------------------------------------|---------------------|--------|-------|

| ESD target for Human Body Model                                                             | HBM                 | 2000   | V     |

| ESD target for Machine Model                                                                | MM                  | 200    | V     |

| HBM circuit description                                                                     | R <sub>series</sub> | 1500   | Ω     |

|                                                                                             | С                   | 100    | pF    |

| MM circuit description                                                                      | R <sub>series</sub> | 0      | Ω     |

|                                                                                             | С                   | 200    | pF    |

| Number of pulses per pin (HBM) <ul> <li>Positive pulses</li> <li>Negative pulses</li> </ul> |                     | 1      | _     |

| Number of pulses per pin (MM) <ul> <li>Positive pulses</li> <li>Negative pulses</li> </ul>  |                     | 3<br>3 | _     |

| Interval of pulses                                                                          | —                   | 1      | sec   |

### Table 25. ESD Protection Characteristics<sup>1, 2</sup>

<sup>1</sup> All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

<sup>2</sup> A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing is performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

# 2.6 DC Electrical Specifications

#### Table 26. DC Electrical Specifications <sup>1</sup>

| Characteristic                                                                               | Symbol              | Min                   | Max                 | Unit |

|----------------------------------------------------------------------------------------------|---------------------|-----------------------|---------------------|------|

| Supply voltage                                                                               | V <sub>DD</sub>     | 3.0                   | 3.6                 | V    |

| Standby voltage                                                                              | V <sub>STBY</sub>   | 3.0                   | 3.6                 | V    |

| Input high voltage                                                                           | V <sub>IH</sub>     | $0.7 \times V_{DD}$   | 4.0                 | V    |

| Input low voltage                                                                            | V <sub>IL</sub>     | $V_{SS} - 0.3$        | $0.35\times V_{DD}$ | V    |

| Input hysteresis                                                                             | V <sub>HYS</sub>    | $0.06 \times V_{DD}$  | _                   | mV   |

| Low-voltage detect trip voltage (V <sub>DD</sub> falling)                                    | V <sub>LVD</sub>    | 2.15                  | 2.3                 | V    |

| Low-voltage detect hysteresis (V <sub>DD</sub> rising)                                       | V <sub>LVDHYS</sub> | 60                    | 120                 | mV   |

| Input leakage current<br>V <sub>in</sub> = V <sub>DD</sub> or V <sub>SS</sub> , digital pins | l <sub>in</sub>     | -1.0                  | 1.0                 | μA   |

| Output high voltage (all input/output and all output pins) $I_{OH} = -2.0 \text{ mA}$        | V <sub>OH</sub>     | V <sub>DD</sub> – 0.5 | _                   | V    |

| Output low voltage (all input/output and all output pins) $I_{OL} = 2.0 mA$                  | V <sub>OL</sub>     | _                     | 0.5                 | V    |

**Electrical Characteristics**

| Characteristic                                                                                                      | Symbol           | Min                   | Max    | Unit |

|---------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|--------|------|

| Output high voltage (high drive)<br>I <sub>OH</sub> = -5 mA                                                         | V <sub>OH</sub>  | V <sub>DD</sub> – 0.5 | _      | V    |

| Output low voltage (high drive)<br>I <sub>OL</sub> = 5 mA                                                           | V <sub>OL</sub>  | —                     | 0.5    | V    |

| Output high voltage (low drive)<br>I <sub>OH</sub> = -2 mA                                                          | V <sub>OH</sub>  | V <sub>DD</sub> - 0.5 | _      | V    |

| Output low voltage (low drive)<br>I <sub>OL</sub> = 2 mA                                                            | V <sub>OL</sub>  | —                     | 0.5    | V    |

| Weak internal pull Up device current, tested at V <sub>IL</sub> Max. <sup>2</sup>                                   | I <sub>APU</sub> | -10                   | -130   | μA   |

| Input Capacitance <sup>3</sup> <ul> <li>All input-only pins</li> <li>All input/output (three-state) pins</li> </ul> | C <sub>in</sub>  | _                     | 7<br>7 | pF   |

### Table 26. DC Electrical Specifications (continued)<sup>1</sup>

<sup>1</sup> Refer to Table 27 for additional PLL specifications.

<sup>2</sup> Refer to Table 3 for pins having internal pull-up devices.

<sup>3</sup> This parameter is characterized before qualification rather than 100% tested.

# 2.7 Clock Source Electrical Specifications

#### Table 27. PLL Electrical Specifications

(V\_{DD} and V\_{DDPLL} = 2.7 to 3.6 V, V\_{SS} = V\_{SSPLL} = 0 V)

| Characteristic                                                                                       | Symbol                                           | Min                        | Max                                                  | Unit               |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------|------------------------------------------------------|--------------------|

| PLL reference frequency range<br>• Crystal reference<br>• External reference                         | f <sub>ref_crystal</sub><br>f <sub>ref_ext</sub> | 2<br>2                     | 10.0<br>10.0                                         | MHz                |

| System frequency <sup>1</sup> <ul> <li>External clock mode</li> <li>On-chip PLL frequency</li> </ul> | f <sub>sys</sub>                                 | 0<br>f <sub>ref</sub> / 32 | 66.67 or 80 <sup>2</sup><br>66.67 or 80 <sup>2</sup> | MHz                |

| Loss of reference frequency <sup>3, 5</sup>                                                          | f <sub>LOR</sub>                                 | 100                        | 1000                                                 | kHz                |

| Self clocked mode frequency <sup>4</sup>                                                             | f <sub>SCM</sub>                                 | 1                          | 5                                                    | MHz                |

| Crystal start-up time <sup>5, 6</sup>                                                                | t <sub>cst</sub>                                 | _                          | 10                                                   | ms                 |

| EXTAL input high voltage <ul> <li>External reference</li> </ul>                                      | V <sub>IHEXT</sub>                               | 2.0                        | V <sub>DD</sub>                                      | V                  |

| EXTAL input low voltage <ul> <li>External reference</li> </ul>                                       | V <sub>ILEXT</sub>                               | V <sub>SS</sub>            | 0.8                                                  | V                  |

| PLL lock time <sup>4,7</sup>                                                                         | t <sub>lpll</sub>                                | —                          | 500                                                  | μS                 |

| Duty cycle of reference <sup>4</sup>                                                                 | t <sub>dc</sub>                                  | 40                         | 60                                                   | % f <sub>ref</sub> |

# 2.10 I<sup>2</sup>C Input/Output Timing Specifications

Table 30 lists specifications for the  $I^2C$  input timing parameters shown in Figure 7.

| Num | Characteristic                                                             | Min                | Max | Units |

|-----|----------------------------------------------------------------------------|--------------------|-----|-------|

| 11  | Start condition hold time                                                  | $2 \times t_{CYC}$ | —   | ns    |

| 12  | Clock low period                                                           | $8 \times t_{CYC}$ | _   | ns    |

| 13  | SCL/SDA rise time ( $V_{IL} = 0.5 \text{ V}$ to $V_{IH} = 2.4 \text{ V}$ ) | _                  | 1   | ms    |

| 14  | Data hold time                                                             | 0                  | _   | ns    |

| 15  | SCL/SDA fall time ( $V_{IH} = 2.4 \text{ V}$ to $V_{IL} = 0.5 \text{ V}$ ) | _                  | 1   | ms    |

| 16  | Clock high time                                                            | $4 \times t_{CYC}$ | _   | ns    |

| 17  | Data setup time                                                            | 0                  | _   | ns    |

| 18  | Start condition setup time (for repeated start condition only)             | $2 \times t_{CYC}$ |     | ns    |

| 19  | Stop condition setup time                                                  | $2 \times t_{CYC}$ | —   | ns    |

Table 31 lists specifications for the  $I^2C$  output timing parameters shown in Figure 7.

Table 31. I<sup>2</sup>C Output Timing Specifications between I2C\_SCL and I2C\_SDA

| Num             | Characteristic                                                                  | Min                | Max | Units |

|-----------------|---------------------------------------------------------------------------------|--------------------|-----|-------|

| 11 <sup>1</sup> | Start condition hold time                                                       | $6 	imes t_{CYC}$  |     | ns    |

| 12 <sup>1</sup> | Clock low period                                                                | $10 	imes t_{CYC}$ |     | ns    |

| 13 <sup>2</sup> | I2C_SCL/I2C_SDA rise time $(V_{IL} = 0.5 \text{ V to } V_{IH} = 2.4 \text{ V})$ |                    | _   | μs    |

| 14 <sup>1</sup> | Data hold time                                                                  | $7 	imes t_{CYC}$  |     | ns    |

| 15 <sup>3</sup> | I2C_SCL/I2C_SDA fall time $(V_{IH} = 2.4 \text{ V to } V_{IL} = 0.5 \text{ V})$ |                    | 3   | ns    |

| 16 <sup>1</sup> | Clock high time                                                                 | $10 	imes t_{CYC}$ |     | ns    |

| 17 <sup>1</sup> | Data setup time                                                                 | $2 \times t_{CYC}$ | _   | ns    |

| 18 <sup>1</sup> | Start condition setup time (for repeated start condition only)                  | $20 	imes t_{CYC}$ | _   | ns    |

| 19 <sup>1</sup> | Stop condition setup time                                                       | $10 	imes t_{CYC}$ | _   | ns    |

<sup>1</sup> Output numbers depend on the value programmed into the IFDR; an IFDR programmed with the maximum frequency (IFDR = 0x20) results in minimum output timings as shown in Table 31. The I<sup>2</sup>C interface is designed to scale the actual data transition time to move it to the middle of the SCL low period. The actual position is affected by the prescale and division values programmed into the IFDR; however, the numbers given in Table 31 are minimum values.

<sup>2</sup> Because SCL and SDA are open-collector-type outputs, which the processor can only actively drive low, the time SCL or SDA take to reach a high level depends on external signal capacitance and pull-up resistor values.

<sup>3</sup> Specified at a nominal 50-pF load.

**Electrical Characteristics**

# 2.13 DMA Timers Timing Specifications

Table 33 lists timer module AC timings.

Table 33. Timer Module AC Timing Specifications

| Name | Characteristic <sup>1</sup>               | Min                | Max | Unit |

|------|-------------------------------------------|--------------------|-----|------|

| T1   | DTIN0 / DTIN1 / DTIN2 / DTIN3 cycle time  | $3 \times t_{CYC}$ | _   | ns   |

| T2   | DTIN0 / DTIN1 / DTIN2 / DTIN3 pulse width | $1 \times t_{CYC}$ |     | ns   |

<sup>1</sup> All timing references to CLKOUT are given to its rising edge.

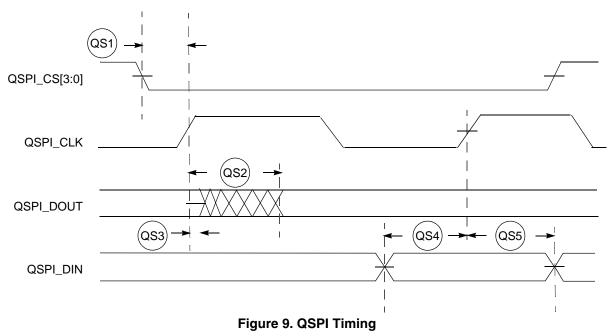

# 2.14 **QSPI Electrical Specifications**

Table 34 lists QSPI timings.

#### Table 34. QSPI Modules AC Timing Specifications

| Name | Characteristic                                   | Min | Max | Unit             |

|------|--------------------------------------------------|-----|-----|------------------|

| QS1  | QSPI_CS[3:0] to QSPI_CLK                         | 1   | 510 | t <sub>CYC</sub> |

| QS2  | QSPI_CLK high to QSPI_DOUT valid                 | _   | 10  | ns               |

| QS3  | QSPI_CLK high to QSPI_DOUT invalid (Output hold) | 2   | _   | ns               |

| QS4  | QSPI_DIN to QSPI_CLK (Input setup)               | 9   | _   | ns               |

| QS5  | QSPI_DIN to QSPI_CLK (Input hold)                | 9   |     | ns               |

The values in Table 34 correspond to Figure 9.

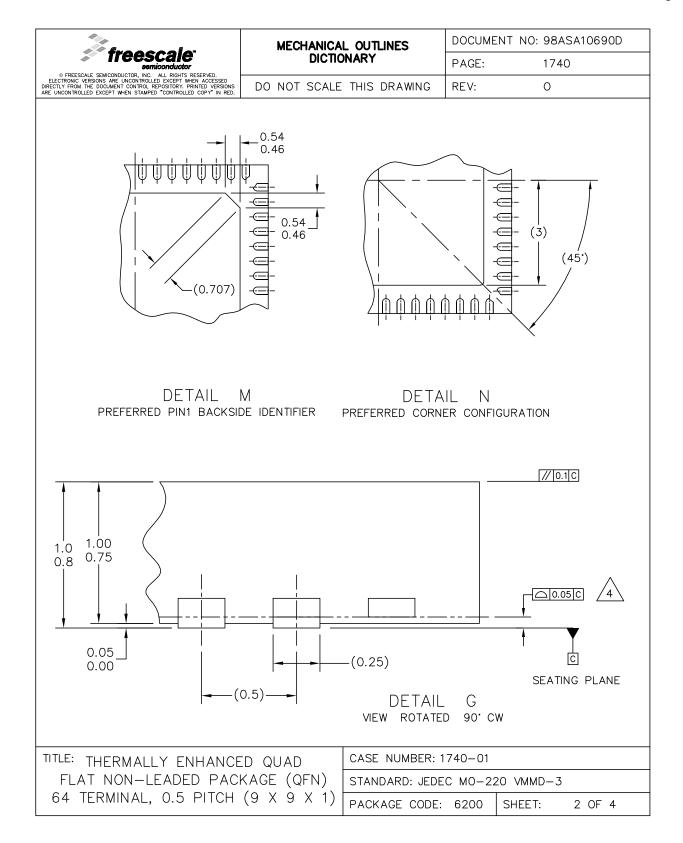

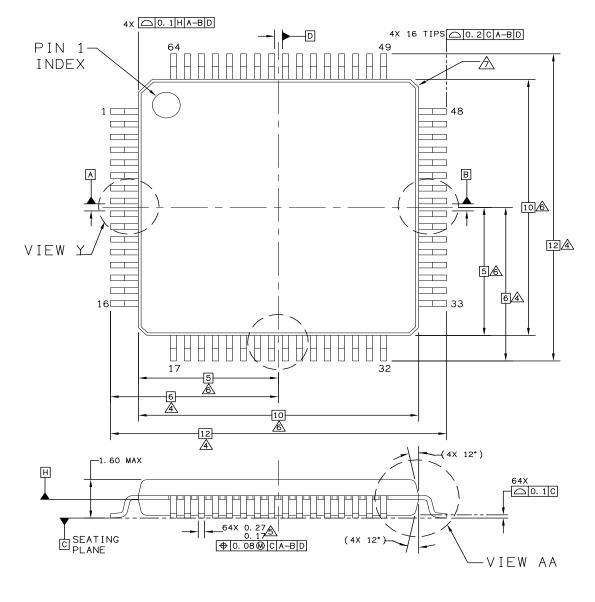

# 3 Mechanical Outline Drawings

This section describes the physical properties of the MCF5213 and its derivatives.

# 3.1 64-pin LQFP Package

| © FREESCALE SEMICONDUCTOR, INC. MECHANICA<br>All rights reserved. |                            | L OUTLINE   | PRINT VERSION NOT TO SCA |        |

|-------------------------------------------------------------------|----------------------------|-------------|--------------------------|--------|

| TITLE: 64LD LQFP,                                                 |                            | DOCUMENT NO | ): 98ASS23234₩           | REV: D |

| 10 X 10 X 1.4 P                                                   | CASE NUMBER: 840F-02       |             | 06 APR 2005              |        |

| 0.5 PITCH, CASE OU                                                | STANDARD: JEDEC MS-026 BCD |             |                          |        |

#### **Mechanical Outline Drawings**