Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | Coldfire V2                                                            |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 80MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                              |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                |

| Number of I/O              | 56                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 32K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                              |

| Data Converters            | A/D 8x12b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 81-LBGA                                                                |

| Supplier Device Package    | 81-MAPBGA (10x10)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcf5213lcvm80j |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **MCF5213 Family Configurations**

- Version 2 ColdFire variable-length RISC processor core

- Static operation

- 32-bit address and data paths on-chip

- Up to 80 MHz processor core frequency

- Sixteen general-purpose, 32-bit data and address registers

- Implements ColdFire ISA\_A with extensions to support the user stack pointer register and four new instructions for improved bit processing (ISA\_A+)

- Multiply-Accumulate (MAC) unit with 32-bit accumulator to support  $16 \times 16 \rightarrow 32$  or  $32 \times 32 \rightarrow 32$  operations

- Illegal instruction decode that allows for 68-Kbyte emulation support

- System debug support

- Real-time trace for determining dynamic execution path

- Background debug mode (BDM) for in-circuit debugging (DEBUG\_B+)

- Real-time debug support, with six hardware breakpoints (4 PC, 1 address and 1 data) configurable into a 1- or 2-level trigger

- On-chip memories

- 32-Kbyte dual-ported SRAM on CPU internal bus, supporting core and DMA access with standby power supply support

- 256 Kbytes of interleaved flash memory supporting 2-1-1-1 accesses

- Power management

- Fully static operation with processor sleep and whole chip stop modes

- Rapid response to interrupts from the low-power sleep mode (wake-up feature)

- Clock enable/disable for each peripheral when not used

- FlexCAN 2.0B module

- Based on and includes all existing features of the Freescale TouCAN module

- Full implementation of the CAN protocol specification version 2.0B

- Standard data and remote frames (up to 109 bits long)

- Extended data and remote frames (up to 127 bits long)

- Zero to eight bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Flexible message buffers (MBs), totalling up to 16 message buffers of 0–8 byte data length each, configurable as Rx or Tx, all supporting standard and extended messages

- Unused MB space can be used as general purpose RAM space

- Listen-only mode capability

- Content-related addressing

- No read/write semaphores

- Three programmable mask registers: global for MBs 0-13, special for MB14, and special for MB15

- Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Three universal asynchronous/synchronous receiver transmitters (UARTs)

- 16-bit divider for clock generation

- Interrupt control logic with maskable interrupts

- DMA support

- Data formats can be 5, 6, 7 or 8 bits with even, odd, or no parity

- Up to two stop bits in 1/16 increments

#### MCF5213 Family Configurations

- System configuration during reset

- Selects one of six clock modes

- Configures output pad drive strength

- Unique part identification number and part revision number

- General purpose I/O interface

- Up to 56 bits of general purpose I/O

- Bit manipulation supported via set/clear functions

- Programmable drive strengths

- Unused peripheral pins may be used as extra GPIO

- JTAG support for system level board testing

## 1.1.2 V2 Core Overview

The version 2 ColdFire processor core is comprised of two separate pipelines decoupled by an instruction buffer. The two-stage instruction fetch pipeline (IFP) is responsible for instruction-address generation and instruction fetch. The instruction buffer is a first-in-first-out (FIFO) buffer that holds prefetched instructions awaiting execution in the operand execution pipeline (OEP). The OEP includes two pipeline stages. The first stage decodes instructions and selects operands (DSOC); the second stage (AGEX) performs instruction execution and calculates operand effective addresses, if needed.

The V2 core implements the ColdFire instruction set architecture revision A+ with added support for a separate user stack pointer register and four new instructions to assist in bit processing. Additionally, the MCF5213 core includes the multiply-accumulate (MAC) unit for improved signal processing capabilities. The MAC implements a three-stage arithmetic pipeline, optimized for 16×16 bit operations, with support for one 32-bit accumulator. Supported operands include 16- and 32-bit signed and unsigned integers, signed fractional operands, and a complete set of instructions to process these data types. The MAC provides support for execution of DSP operations within the context of a single processor at a minimal hardware cost.

## 1.1.3 Integrated Debug Module

The ColdFire processor core debug interface is provided to support system debugging with low-cost debug and emulator development tools. Through a standard debug interface, access to debug information and real-time tracing capability is provided on 100-lead packages. This allows the processor and system to be debugged at full speed without the need for costly in-circuit emulators.

The on-chip breakpoint resources include a total of nine programmable 32-bit registers: an address and an address mask register, a data and a data mask register, four PC registers, and one PC mask register. These registers can be accessed through the dedicated debug serial communication channel or from the processor's supervisor mode programming model. The breakpoint registers can be configured to generate triggers by combining the address, data, and PC conditions in a variety of single- or dual-level definitions. The trigger event can be programmed to generate a processor halt or initiate a debug interrupt exception. The MCF5213 implements revision B+ of the ColdFire Debug Architecture.

The MCF5213's interrupt servicing options during emulator mode allow real-time critical interrupt service routines to be serviced while processing a debug interrupt event. This ensures the system continues to operate even during debugging.

To support program trace, the V2 debug module provides processor status (PST[3:0]) and debug data (DDATA[3:0]) ports. These buses and the PSTCLK output provide execution status, captured operand data, and branch target addresses defining processor activity at the CPU's clock rate. The MCF5213 includes a new debug signal, ALLPST. This signal is the logical AND of the processor status (PST[3:0]) signals and is useful for detecting when the processor is in a halted state (PST[3:0] = 1111).

The full debug/trace interface is available only on the 100-pin packages. However, every product features the dedicated debug serial communication channel (DSI, DSO, DSCLK) and the ALLPST signal.

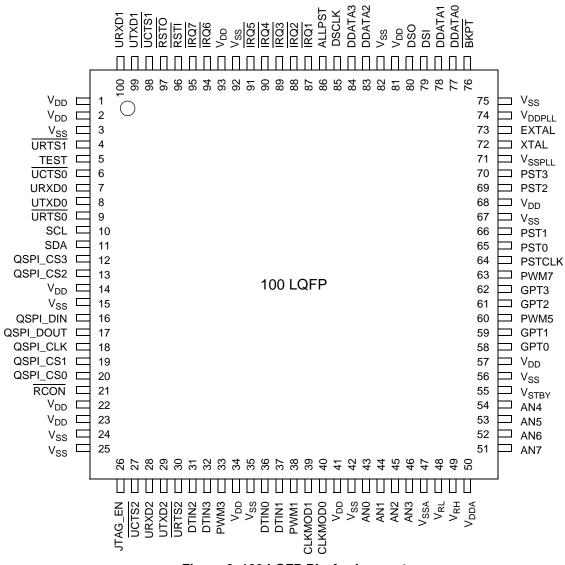

Figure 2 shows the pinout configuration for the 100 LQFP.

Figure 2. 100 LQFP Pin Assignments

| Pin<br>Group     | Primary<br>Function | Secondary<br>Function | Tertiary<br>Function | Quaternary<br>Function | Drive<br>Strength /<br>Control <sup>1</sup> | Slew Rate /<br>Control <sup>1</sup> | Pull-up /<br>Pull-down <sup>2</sup> | Pin on<br>100 LQFP | Pin on 81<br>MAPBGA | Pin on 64<br>LQFP/QFN |

|------------------|---------------------|-----------------------|----------------------|------------------------|---------------------------------------------|-------------------------------------|-------------------------------------|--------------------|---------------------|-----------------------|

| ADC              | AN7                 | —                     | _                    | GPIO                   | Low                                         | FAST                                | —                                   | 51                 | H9                  | 33                    |

|                  | AN6                 | —                     | _                    | GPIO                   | Low                                         | FAST                                | —                                   | 52                 | G9                  | 34                    |

|                  | AN5                 | —                     | _                    | GPIO                   | Low                                         | FAST                                | _                                   | 53                 | G8                  | 35                    |

|                  | AN4                 | _                     | _                    | GPIO                   | Low                                         | FAST                                |                                     | 54                 | F9                  | 36                    |

|                  | AN3                 | —                     | _                    | GPIO                   | Low                                         | FAST                                | _                                   | 46                 | G7                  | 28                    |

|                  | AN2                 | _                     | _                    | GPIO                   | Low                                         | FAST                                | —                                   | 45                 | G6                  | 27                    |

|                  | AN1                 | —                     | _                    | GPIO                   | Low                                         | FAST                                | —                                   | 44                 | H6                  | 26                    |

|                  | AN0                 | _                     | _                    | GPIO                   | Low                                         | FAST                                | —                                   | 43                 | J6                  | 25                    |

|                  | SYNCA <sup>3</sup>  | —                     | _                    | —                      | N/A                                         | N/A                                 | —                                   | _                  | _                   | —                     |

|                  | SYNCB <sup>3</sup>  | —                     | _                    | —                      | N/A                                         | N/A                                 | —                                   | _                  | -                   | —                     |

|                  | VDDA                | —                     | _                    | —                      | N/A                                         | N/A                                 | _                                   | 50                 | H8                  | 32                    |

|                  | VSSA                | _                     | _                    | —                      | N/A                                         | N/A                                 | —                                   | 47                 | H7, J9              | 29                    |

|                  | VRH                 | —                     | _                    | —                      | N/A                                         | N/A                                 | —                                   | 49                 | J8                  | 31                    |

|                  | VRL                 | —                     | _                    | —                      | N/A                                         | N/A                                 | _                                   | 48                 | J7                  | 30                    |

| Clock            | EXTAL               | _                     | _                    | —                      | N/A                                         | N/A                                 | —                                   | 73                 | B9                  | 47                    |

| Generation       | XTAL                | —                     | _                    | —                      | N/A                                         | N/A                                 | —                                   | 72                 | C9                  | 46                    |

|                  | VDDPLL              | _                     | _                    | —                      | N/A                                         | N/A                                 | _                                   | 74                 | B8                  | 48                    |

|                  | VSSPLL              | —                     | _                    | —                      | N/A                                         | N/A                                 | —                                   | 71                 | C8                  | 45                    |

| Debug Data       | ALLPST              | —                     | _                    | —                      | High                                        | FAST                                | —                                   | 86                 | A6                  | 55                    |

|                  | DDATA[3:0]          | —                     | _                    | GPIO                   | High                                        | FAST                                |                                     | 84,83,78,77        |                     | —                     |

|                  | PST[3:0]            | —                     | _                    | GPIO                   | High                                        | FAST                                |                                     | 70,69,66,65        | _                   | —                     |

| I <sup>2</sup> C | SCL                 | CANTX <sup>4</sup>    | UTXD2                | GPIO                   | PDSR[0]                                     | PSRR[0]                             | pull-up <sup>5</sup>                | 10                 | E1                  | 8                     |

|                  | SDA                 | CANRX <sup>3</sup>    | URXD2                | GPIO                   | PDSR[0]                                     | PSRR[0]                             | pull-up <sup>5</sup>                | 11                 | E2                  | 9                     |

## Table 3. Pin Functions by Primary and Alternate Purpose

MCF5213 Family Configurations

16

|  | 1 |  |

|--|---|--|

|  |   |  |

|  |   |  |

Freescale Semiconductor

MCF5213 ColdFire Microcontroller, Rev. 3

| Pin<br>Group           | Primary<br>Function | Secondary<br>Function | Tertiary<br>Function | Quaternary<br>Function | Drive<br>Strength /<br>Control <sup>1</sup> | Slew Rate /<br>Control <sup>1</sup> | Pull-up /<br>Pull-down <sup>2</sup> | Pin on<br>100 LQFP | Pin on 81<br>MAPBGA | Pin on 64<br>LQFP/QFN |

|------------------------|---------------------|-----------------------|----------------------|------------------------|---------------------------------------------|-------------------------------------|-------------------------------------|--------------------|---------------------|-----------------------|

| Interrupts             | IRQ7                | _                     |                      | GPIO                   | Low                                         | FAST                                | pull-up                             | 95                 | C4                  | 58                    |

|                        | IRQ6                | _                     |                      | GPIO                   | Low                                         | FAST                                | pull-up                             | 94                 | B4                  | —                     |

|                        | IRQ5                | _                     |                      | GPIO                   | Low                                         | FAST                                | pull-up                             | 91                 | A4                  | —                     |

|                        | IRQ4                | —                     | _                    | GPIO                   | Low                                         | FAST                                | pull-up                             | 90                 | C5                  | 57                    |

|                        | IRQ3                | —                     | _                    | GPIO                   | Low                                         | FAST                                | pull-up                             | 89                 | A5                  | —                     |

|                        | IRQ2                | —                     | _                    | GPIO                   | Low                                         | FAST                                | pull-up                             | 88                 | B5                  | —                     |

|                        | IRQ1                | SYNCA                 | PWM1                 | GPIO                   | High                                        | FAST                                | pull-up <sup>5</sup>                | 87                 | C6                  | 56                    |

| JTAG/BDM               | JTAG_EN             | —                     | _                    | —                      | N/A                                         | N/A                                 | pull-down                           | 26                 | J2                  | 17                    |

|                        | TCLK/<br>PSTCLK     | CLKOUT                | _                    | —                      | High                                        | FAST                                | pull-up <sup>6</sup>                | 64                 | C7                  | 44                    |

|                        | TDI/DSI             | —                     |                      | —                      | N/A                                         | N/A                                 | pull-up <sup>6</sup>                | 79                 | B7                  | 50                    |

|                        | TDO/DSO             | —                     | _                    | —                      | High                                        | FAST                                | —                                   | 80                 | A7                  | 51                    |

|                        | TMS<br>/BKPT        | _                     | _                    | —                      | N/A                                         | N/A                                 | pull-up <sup>6</sup>                | 76                 | A8                  | 49                    |

|                        | TRST<br>/DSCLK      | _                     | _                    | —                      | N/A                                         | N/A                                 | pull-up <sup>6</sup>                | 85                 | B6                  | 54                    |

| Mode                   | CLKMOD0             | —                     |                      | —                      | N/A                                         | N/A                                 | pull-down <sup>7</sup>              | 40                 | G5                  | 24                    |

| Selection <sup>7</sup> | CLKMOD1             | _                     | _                    | —                      | N/A                                         | N/A                                 | pull-down <sup>7</sup>              | 39                 | H5                  | —                     |

|                        | RCON/<br>EZPCS      | —                     | _                    | —                      | N/A                                         | N/A                                 | pull-up                             | 21                 | G3                  | 16                    |

| PWM                    | PWM7                | _                     | _                    | GPIO                   | PDSR[31]                                    | PSRR[31]                            | —                                   | 63                 | D7                  | —                     |

|                        | PWM5                | —                     | _                    | GPIO                   | PDSR[30]                                    | PSRR[30]                            | —                                   | 60                 | E8                  | —                     |

|                        | PWM3                | —                     | _                    | GPIO                   | PDSR[29]                                    | PSRR[29]                            | —                                   | 33                 | J4                  | —                     |

|                        | PWM1                | _                     |                      | GPIO                   | PDSR[28]                                    | PSRR[28]                            | —                                   | 38                 | J5                  | —                     |

## Table 3. Pin Functions by Primary and Alternate Purpose (continued)

17

| Pin<br>Group | Primary<br>Function   | Secondary<br>Function | Tertiary<br>Function | Quaternary<br>Function | Drive<br>Strength /<br>Control <sup>1</sup> | Slew Rate /<br>Control <sup>1</sup> | Pull-up /<br>Pull-down <sup>2</sup> | Pin on<br>100 LQFP                      | Pin on 81<br>MAPBGA      | Pin on 64<br>LQFP/QFN |

|--------------|-----------------------|-----------------------|----------------------|------------------------|---------------------------------------------|-------------------------------------|-------------------------------------|-----------------------------------------|--------------------------|-----------------------|

| UART 1       | UCTS1                 | SYNCA                 | URXD2                | GPIO                   | PDSR[15]                                    | PSRR[15]                            | —                                   | 98                                      | C3                       | 61                    |

|              | URTS1                 | SYNCB                 | UTXD2                | GPIO                   | PDSR[14]                                    | PSRR[14]                            | —                                   | 4                                       | B1                       | 2                     |

|              | URXD1                 | —                     | _                    | GPIO                   | PDSR[13]                                    | PSRR[13]                            |                                     | 100                                     | B2                       | 63                    |

|              | UTXD1                 | —                     | _                    | GPIO                   | PDSR[12]                                    | PSRR[12]                            |                                     | 99                                      | A2                       | 62                    |

| UART 2       | UCTS2                 | —                     |                      | GPIO                   | PDSR[27]                                    | PSRR[27]                            | —                                   | 27                                      | —                        | —                     |

|              | URTS2                 | —                     | _                    | GPIO                   | PDSR[26]                                    | PSRR[26]                            | —                                   | 30                                      |                          | —                     |

|              | URXD2                 | —                     |                      | GPIO                   | PDSR[25]                                    | PSRR[25]                            | _                                   | 28                                      | —                        | —                     |

|              | UTXD2                 | —                     | —                    | GPIO                   | PDSR[24]                                    | PSRR[24]                            | —                                   | 29                                      | —                        | —                     |

| FlexCAN      | CANRX <sup>4,11</sup> |                       |                      |                        | N/A                                         | N/A                                 | —                                   | —                                       | —                        | —                     |

|              | CANTX <sup>4,11</sup> |                       |                      |                        | N/A                                         | N/A                                 |                                     | —                                       | —                        | —                     |

| VSTBY        | VSTBY                 | —                     | _                    | —                      | N/A                                         | N/A                                 | —                                   | 55                                      | F8                       | 37                    |

| VDD          | VDD                   | _                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | 1,2,14,22,<br>23,34,41,<br>57,68,81,93  | D5,E3–E7,<br>F5          | 1,10,20,39,5<br>2     |

| VSS          | VSS                   |                       |                      | _                      | N/A                                         | N/A                                 | _                                   | 3,15,24,25,3<br>5,42,56,<br>67,75,82,92 | A1,A9,D4,D<br>6,F4,F6,J1 | 11,21,38,<br>53,64    |

### Table 3. Pin Functions by Primary and Alternate Purpose (continued)

<sup>1</sup> The PDSR and PSSR registers are described in the General Purpose I/O chapter. All programmable signals default to 2 mA drive and FAST slew rate in <sup>2</sup> All signals have a pull-up in GPIO mode.

<sup>3</sup> These signals are multiplexed on other pins.

<sup>4</sup> The signals are multiplexed on other pins.

<sup>4</sup> The multiplexed CANTX and CANRX signals are not available on the MCF5211 or MCF5212.

<sup>5</sup> For primary and GPIO functions only.

<sup>6</sup> Only when JTAG mode is enabled.

<sup>7</sup> CLKMOD0 and CLKMOD1 have internal pull-down resistors; however, the use of external resistors is very strongly recommended.

<sup>8</sup> For secondary and GPIO functions only.

<sup>9</sup> RSTI has an internal pull-up resistor; however, the use of an external resistor is very strongly recommended.

<sup>10</sup> For GPIO function. Primary Function has pull-up control within the GPT module.

<sup>11</sup> CANTX and CANRX are secondary functions only.

**MCF5213 Family Configurations**

## 1.2 Reset Signals

Table 4 describes signals used to reset the chip or as a reset indication.

**Table 4. Reset Signals**

| Signal Name | Abbreviation | Function                                                                                                                                          | I/O |

|-------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Reset In    |              | Primary reset input to the device. Asserting $\overline{\text{RSTI}}$ for at least 8 CPU clock cycles immediately resets the CPU and peripherals. | I   |

| Reset Out   | RSTO         | Driven low for 1024 CPU clocks after the reset source has deasserted.                                                                             | 0   |

# 1.3 PLL and Clock Signals

Table 5 describes signals used to support the on-chip clock generation circuitry.

### Table 5. PLL and Clock Signals

| Signal Name       | Abbreviation | Function                                                                                                     | I/O |

|-------------------|--------------|--------------------------------------------------------------------------------------------------------------|-----|

| External Clock In |              | Crystal oscillator or external clock input except when the on-chip relaxation oscillator is used.            | Ι   |

| Crystal           |              | Crystal oscillator output except when CLKMOD1=1, then sampled as part of the clock mode selection mechanism. | 0   |

| Clock Out         | CLKOUT       | This output signal reflects the internal system clock.                                                       | 0   |

## 1.4 Mode Selection

Table 6 describes signals used in mode selection; Table 7 describes the particular clocking modes.

Table 6. Mode Selection Signals

| Signal Name          | Abbreviation | Function                                                                                                                                                                                                                                                            | I/O |

|----------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Clock Mode Selection | CLKMOD[1:0]  | Selects the clock boot mode.                                                                                                                                                                                                                                        | Ι   |

| Reset Configuration  |              | The Serial Flash Programming mode is entered by asserting the $\overline{\text{RCON}}$ pin (with the TEST pin negated) as the chip comes out of reset. During this mode, the EzPort has access to the flash memory which can be programmed from an external device. |     |

| Test                 | TEST         | Reserved for factory testing only and in normal modes of operation should be connected to VSS to prevent unintentional activation of test functions.                                                                                                                | Ι   |

### Table 7. Clocking Modes

| CLKMOD[1:0] | XTAL | Configure the clock mode.                               |

|-------------|------|---------------------------------------------------------|

| 00          | 0    | PLL disabled, clock driven by external oscillator       |

| 00          | 1    | PLL disabled, clock driven by on-chip oscillator        |

| 01          | N/A  | PLL disabled, clock driven by crystal                   |

| 10          | 0    | PLL in normal mode, clock driven by external oscillator |

| 10          | 1    | PLL in normal mode, clock driven by on-chip oscillator  |

| 11          | N/A  | PLL in normal mode, clock driven by crystal             |

## 1.5 External Interrupt Signals

Table 8 describes the external interrupt signals.

**Table 8. External Interrupt Signals**

| Signal Name         | Abbreviation | Function                    | I/O |

|---------------------|--------------|-----------------------------|-----|

| External Interrupts | IRQ[7:1]     | External interrupt sources. | I   |

# 1.6 Queued Serial Peripheral Interface (QSPI)

Table 9 describes the QSPI signals.

| Table 9. Queueo | Serial Peri | pheral Interface  | (QSPI) Signals |

|-----------------|-------------|-------------------|----------------|

|                 |             | priorai interiado |                |

| Signal Name                            | Abbreviation | Function                                                                                                             | I/O |

|----------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------|-----|

| QSPI Synchronous<br>Serial Output      | QSPI_DOUT    | Provides the serial data from the QSPI and can be programmed to be driven on the rising or falling edge of QSPI_CLK. | 0   |

| QSPI Synchronous<br>Serial Data Input  | QSPI_DIN     | Provides the serial data to the QSPI and can be programmed to be sampled on the rising or falling edge of QSPI_CLK.  | I   |

| QSPI Serial Clock                      | QSPI_CLK     | Provides the serial clock from the QSPI. The polarity and phase of QSPI_CLK are programmable.                        | 0   |

| Synchronous Peripheral<br>Chip Selects | QSPI_CS[3:0] | QSPI peripheral chip select; can be programmed to be active high or low.                                             | 0   |

# 1.7 I<sup>2</sup>C I/O Signals

Table 10 describes the I<sup>2</sup>C serial interface module signals.

## Table 10. I<sup>2</sup>C I/O Signals

| Signal Name  | Abbreviation | Function                                                                                                                                                                                                | I/O |

|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Serial Clock |              | Open-drain clock signal for the for the $I^2C$ interface. When the bus is In master mode, this clock is driven by the $I^2C$ module; when the bus is in slave mode, this clock becomes the clock input. | I/O |

| Serial Data  | SDA          | Open-drain signal that serves as the data input/output for the I <sup>2</sup> C interface.                                                                                                              | I/O |

| Characteristic                                                                                                                                                                                                                                                                                                                                                                      | Symbol            | Typical <sup>1</sup><br>Active<br>(SRAM) | Typical <sup>1</sup><br>Active<br>(Flash) | Peak <sup>2</sup>                                        | Unit           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------|-------------------------------------------|----------------------------------------------------------|----------------|

| 1 MHz core & I/O                                                                                                                                                                                                                                                                                                                                                                    | I <sub>DD</sub>   | —                                        | 3.48                                      | —                                                        | mA             |

| 8 MHz core & I/O                                                                                                                                                                                                                                                                                                                                                                    |                   | 7.28                                     | 13.37                                     | 19.02                                                    |                |

| 16 MHz core & I/O                                                                                                                                                                                                                                                                                                                                                                   |                   | 12.08                                    | 25.08                                     | 35.66                                                    |                |

| 64 MHz core & I/O                                                                                                                                                                                                                                                                                                                                                                   |                   | 40.14                                    | 54.62                                     | 85.01                                                    |                |

| 80 MHz core & I/O                                                                                                                                                                                                                                                                                                                                                                   |                   | 49.2                                     | 64.09                                     | 100.03                                                   |                |

| $\label{eq:RAM} \begin{array}{l} \text{RAM standby supply current} \\ \bullet  \text{Normal operation: } V_{\text{DD}} > V_{\text{STBY}} - 0.3 \text{ V} \\ \bullet  \text{Transient condition: } V_{\text{STBY}} - 0.3 \text{ V} > V_{\text{DD}} > V_{\text{SS}} + 0.5 \text{ V} \\ \bullet  \text{Standby operation: } V_{\text{DD}} < V_{\text{SS}} + 0.5 \text{ V} \end{array}$ | I <sub>STBY</sub> | N/<br>N/<br>N/                           | A <sup>3</sup>                            | N/A <sup>3</sup><br>N/A <sup>3</sup><br>N/A <sup>3</sup> | μA<br>mA<br>μA |

| Analog supply current <ul> <li>Normal operation</li> <li>Low-power stop</li> </ul>                                                                                                                                                                                                                                                                                                  | I <sub>DDA</sub>  | —                                        |                                           | 16<br>50                                                 | mA<br>μA       |

### Table 21. Typical Active Current Consumption Specifications

<sup>1</sup> Tested at room temperature with CPU polling a status register. All clocks were off except the UART and CFM (when running from flash memory).

<sup>2</sup> Peak current measured with all modules active, and default drive strength with matching load.

<sup>3</sup> Due to the errata "Non-functional RAM Standby Supply" in the MCF5213 Device Errata, V<sub>STBY</sub> should be connected directly to V<sub>DD</sub> and cannot be used for RAM standby operation.

## 2.3 Thermal Characteristics

Table 22 lists thermal resistance values.

### Table 22. Thermal Characteristics

|          | Characteristic                          |                         | Symbol          | Value             | Unit |

|----------|-----------------------------------------|-------------------------|-----------------|-------------------|------|

| 100 LQFP | Junction to ambient, natural convection | Single layer board (1s) | $\theta_{JA}$   | 53 <sup>1,2</sup> | °C/W |

|          | Junction to ambient, natural convection | Four layer board (2s2p) | $\theta_{JA}$   | 39 <sup>1,3</sup> | °C/W |

|          | Junction to ambient, (@200 ft/min)      | Single layer board (1s) | $\theta_{JMA}$  | 42 <sup>1,3</sup> | °C/W |

|          | Junction to ambient, (@200 ft/min)      | Four layer board (2s2p) | $\theta_{JMA}$  | 33 <sup>1,3</sup> | °C/W |

|          | Junction to board                       | _                       | $\theta_{JB}$   | 25 <sup>4</sup>   | °C/W |

|          | Junction to case                        | _                       | $\theta^{PC}$   | 9 <sup>5</sup>    | °C/W |

|          | Junction to top of package              | Natural convection      | Ψ <sub>jt</sub> | 2 <sup>6</sup>    | °C/W |

|          | Maximum operating junction temperature  | —                       | Тj              | 105               | °C   |

|           | Characteristic                          |                         | Symbol           | Value             | Unit |

|-----------|-----------------------------------------|-------------------------|------------------|-------------------|------|

| 81 MAPBGA | Junction to ambient, natural convection | Single layer board (1s) | $\theta_{JA}$    | 61 <sup>1,2</sup> | °C/W |

|           | Junction to ambient, natural convection | Four layer board (2s2p) | $\theta_{JA}$    | 35 <sup>2,3</sup> | °C/W |

|           | Junction to ambient, (@200 ft/min)      | Single layer board (1s) | θ <sub>JMA</sub> | 50 <sup>2,3</sup> | °C/W |

|           | Junction to ambient, (@200 ft/min)      | Four layer board (2s2p) | $\theta_{JMA}$   | 31 <sup>2,3</sup> | °C/W |

|           | Junction to board                       | —                       | $\theta_{JB}$    | 20 <sup>4</sup>   | °C/W |

|           | Junction to case                        | —                       | θ <sub>JC</sub>  | 12 <sup>5</sup>   | °C/W |

|           | Junction to top of package              | Natural convection      | Ψ <sub>jt</sub>  | 2 <sup>6</sup>    | °C/W |

|           | Maximum operating junction temperature  | —                       | Тj               | 105               | °C   |

| 64 LQFP   | Junction to ambient, natural convection | Single layer board (1s) | $\theta_{JA}$    | 62 <sup>1,2</sup> | °C/W |

|           | Junction to ambient, natural convection | Four layer board (2s2p) | $\theta_{JA}$    | 43 <sup>1,3</sup> | °C/W |

|           | Junction to ambient (@200 ft/min)       | Single layer board (1s) | $\theta_{JMA}$   | 50 <sup>1,3</sup> | °C/W |

|           | Junction to ambient (@200 ft/min)       | Four layer board (2s2p) | $\theta_{JMA}$   | 36 <sup>1,3</sup> | °C/W |

|           | Junction to board                       | —                       | $\theta_{JB}$    | 26 <sup>4</sup>   | °C/W |

|           | Junction to case                        | —                       | $\theta^{JC}$    | 9 <sup>5</sup>    | °C/W |

|           | Junction to top of package              | Natural convection      | Ψ <sub>jt</sub>  | 2 <sup>6</sup>    | °C/W |

|           | Maximum operating junction temperature  | —                       | Тj               | 105               | °C   |

| 64 QFN    | Junction to ambient, natural convection | Single layer board (1s) | $\theta_{JA}$    | 68 <sup>1,2</sup> | °C/W |

|           | Junction to ambient, natural convection | Four layer board (2s2p) | $\theta_{JA}$    | 24 <sup>1,3</sup> | °C/W |

|           | Junction to ambient (@200 ft/min)       | Single layer board (1s) | $\theta_{JMA}$   | 55 <sup>1,3</sup> | °C/W |

|           | Junction to ambient (@200 ft/min)       | Four layer board (2s2p) | $\theta_{JMA}$   | 19 <sup>1,3</sup> | °C/W |

|           | Junction to board                       | —                       | $\theta_{JB}$    | 8 <sup>4</sup>    | °C/W |

|           | Junction to case (bottom)               | —                       | θ <sub>JC</sub>  | 0.6 <sup>5</sup>  | °C/W |

|           | Junction to top of package              | Natural convection      | Ψ <sub>jt</sub>  | 3 <sup>6</sup>    | °C/W |

|           | Maximum operating junction temperature  | —                       | Тj               | 105               | °C   |

### Table 22. Thermal Characteristics (continued)

<sup>1</sup>  $\theta_{JA}$  and  $\Psi_{jt}$  parameters are simulated in conformance with EIA/JESD Standard 51-2 for natural convection. Freescale recommends the use of  $\theta_{JA}$  and power dissipation specifications in the system design to prevent device junction temperatures from exceeding the rated specification. System designers should be aware that device junction temperatures can be significantly influenced by board layout and surrounding devices. Conformance to the device junction temperature specification can be verified by physical measurement in the customer's system using the  $\Psi_{jt}$  parameter, the device power dissipation, and the method described in EIA/JESD Standard 51-2.

- <sup>2</sup> Per JEDEC JESD51-2 with the single-layer board (JESD51-3) horizontal.

- <sup>3</sup> Per JEDEC JESD51-6 with the board JESD51-7) horizontal.

- <sup>4</sup> Thermal resistance between the die and the printed circuit board in conformance with JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- <sup>5</sup> Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- <sup>6</sup> Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written in conformance with Psi-JT.

Τ<sub>A</sub>

The average chip-junction temperature (T<sub>.</sub>) in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \Theta_{JMA})$$

(1)

Where:

= ambient temperature, °C

= package thermal resistance, junction-to-ambient, °C/W  $\Theta_{JA}$

$\mathsf{P}_\mathsf{D}$  $= P_{INT} + P_{I/O}$

= chip internal power,  $I_{DD} \times V_{DD}$ , watts PINT

= power dissipation on input and output pins - user determined, watts P<sub>I/O</sub>

For most applications  $P_{I/O} < P_{INT}$  and can be ignored. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_{\rm D} = K \div (T_{\rm J} + 273^{\circ}C)$$

(2)

Solving equations 1 and 2 for K gives:

$$K = P_D \times (T_A + 273 \text{ °C}) + \Theta_{JMA} \times P_D^2 (3)$$

where K is a constant pertaining to the particular part. K can be determined from equation (3) by measuring P<sub>D</sub> (at equilibrium) for a known T<sub>A</sub>. Using this value of K, the values of P<sub>D</sub> and T<sub>J</sub> can be obtained by solving equations (1) and (2) iteratively for any value of T<sub>A</sub>.

#### **Flash Memory Characteristics** 2.4

The flash memory characteristics are shown in Table 23 and Table 24.

### Table 23. SGFM Flash Program and Erase Characteristics $(V_{DDE} = 2.7 \text{ to } 3.6 \text{ V})$

| Parameter                                 | Symbol                | Min  | Тур | Max                      | l |

|-------------------------------------------|-----------------------|------|-----|--------------------------|---|

| System clock (read only)                  | f <sub>sys(R)</sub>   | 0    | —   | 66.67 or 80 <sup>1</sup> | 1 |

| System clock (program/erase) <sup>2</sup> | f <sub>svs(P/E)</sub> | 0.15 | _   | 66.67 or 80 <sup>1</sup> | ľ |

t<sub>sys(P/E)</sub>

Depending on packaging; see Table 2.

2 Refer to the flash memory section for more information

#### Table 24. SGFM Flash Module Life Characteristics

$(V_{DDF} = 2.7 \text{ to } 3.6 \text{ V})$

| Parameter                                                                     | Symbol    | Value               | Unit   |

|-------------------------------------------------------------------------------|-----------|---------------------|--------|

| Maximum number of guaranteed program/erase cycles <sup>1</sup> before failure | P/E       | 10,000 <sup>2</sup> | Cycles |

| Data retention at average operating temperature of 85°C                       | Retention | 10                  | Years  |

<sup>1</sup> A program/erase cycle is defined as switching the bits from  $1 \rightarrow 0 \rightarrow 1$ .

<sup>2</sup> Reprogramming of a flash memory array block prior to erase is not required.

Unit MHz

MHz

| Characteristic                                                                                                      | Symbol           | Min                   | Max    | Unit |

|---------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|--------|------|

| Output high voltage (high drive)<br>I <sub>OH</sub> = -5 mA                                                         | V <sub>OH</sub>  | V <sub>DD</sub> – 0.5 | _      | V    |

| Output low voltage (high drive)<br>I <sub>OL</sub> = 5 mA                                                           | V <sub>OL</sub>  | _                     | 0.5    | V    |

| Output high voltage (low drive)<br>I <sub>OH</sub> = -2 mA                                                          | V <sub>OH</sub>  | V <sub>DD</sub> - 0.5 | _      | V    |

| Output low voltage (low drive)<br>I <sub>OL</sub> = 2 mA                                                            | V <sub>OL</sub>  | —                     | 0.5    | V    |

| Weak internal pull Up device current, tested at V <sub>IL</sub> Max. <sup>2</sup>                                   | I <sub>APU</sub> | -10                   | -130   | μA   |

| Input Capacitance <sup>3</sup> <ul> <li>All input-only pins</li> <li>All input/output (three-state) pins</li> </ul> | C <sub>in</sub>  | _                     | 7<br>7 | pF   |

## Table 26. DC Electrical Specifications (continued)<sup>1</sup>

<sup>1</sup> Refer to Table 27 for additional PLL specifications.

<sup>2</sup> Refer to Table 3 for pins having internal pull-up devices.

<sup>3</sup> This parameter is characterized before qualification rather than 100% tested.

# 2.7 Clock Source Electrical Specifications

### Table 27. PLL Electrical Specifications

(V\_{DD} and V\_{DDPLL} = 2.7 to 3.6 V, V\_{SS} = V\_{SSPLL} = 0 V)

| Characteristic                                                                                       | Symbol                                           | Min                        | Max                                                  | Unit               |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------|------------------------------------------------------|--------------------|

| PLL reference frequency range<br>• Crystal reference<br>• External reference                         | f <sub>ref_crystal</sub><br>f <sub>ref_ext</sub> | 2<br>2                     | 10.0<br>10.0                                         | MHz                |

| System frequency <sup>1</sup> <ul> <li>External clock mode</li> <li>On-chip PLL frequency</li> </ul> | f <sub>sys</sub>                                 | 0<br>f <sub>ref</sub> / 32 | 66.67 or 80 <sup>2</sup><br>66.67 or 80 <sup>2</sup> | MHz                |

| Loss of reference frequency <sup>3, 5</sup>                                                          | f <sub>LOR</sub>                                 | 100                        | 1000                                                 | kHz                |

| Self clocked mode frequency <sup>4</sup>                                                             | f <sub>SCM</sub>                                 | 1                          | 5                                                    | MHz                |

| Crystal start-up time <sup>5, 6</sup>                                                                | t <sub>cst</sub>                                 | _                          | 10                                                   | ms                 |

| EXTAL input high voltage <ul> <li>External reference</li> </ul>                                      | V <sub>IHEXT</sub>                               | 2.0                        | V <sub>DD</sub>                                      | V                  |

| EXTAL input low voltage <ul> <li>External reference</li> </ul>                                       | V <sub>ILEXT</sub>                               | V <sub>SS</sub>            | 0.8                                                  | V                  |

| PLL lock time <sup>4,7</sup>                                                                         | t <sub>lpll</sub>                                | —                          | 500                                                  | μS                 |

| Duty cycle of reference <sup>4</sup>                                                                 | t <sub>dc</sub>                                  | 40                         | 60                                                   | % f <sub>ref</sub> |

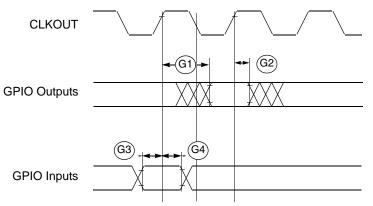

### Figure 5. GPIO Timing

# 2.9 Reset Timing

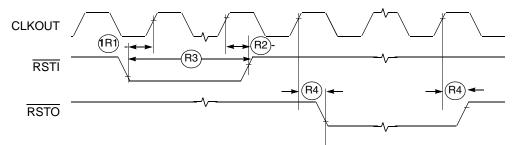

### Table 29. Reset and Configuration Override Timing

| (V <sub>DD</sub> = 2.7 to 3.6 | V, V <sub>SS</sub> = 0 V, T | $_{\Lambda} = T_{L} \text{ to } T_{H})^{1}$ |

|-------------------------------|-----------------------------|---------------------------------------------|

|                               | / 00 /                      |                                             |

| NUM | Characteristic                     | Symbol             | Min | Мах | Unit             |

|-----|------------------------------------|--------------------|-----|-----|------------------|

| R1  | RSTI input valid to CLKOUT High    | t <sub>RVCH</sub>  | 9   | _   | ns               |

| R2  | CLKOUT High to RSTI Input invalid  | t <sub>CHRI</sub>  | 1.5 | _   | ns               |

| R3  | RSTI input valid time <sup>2</sup> | t <sub>RIVT</sub>  | 5   | _   | t <sub>CYC</sub> |

| R4  | CLKOUT High to RSTO Valid          | t <sub>CHROV</sub> | —   | 10  | ns               |

<sup>1</sup> All AC timing is shown with respect to 50%  $V_{DD}$  levels unless otherwise noted.

<sup>2</sup> During low power STOP, the synchronizers for the RSTI input are bypassed and RSTI is asserted asynchronously to the system. Thus, RSTI must be held a minimum of 100 ns.

Figure 6. RSTI and Configuration Override Timing

NP

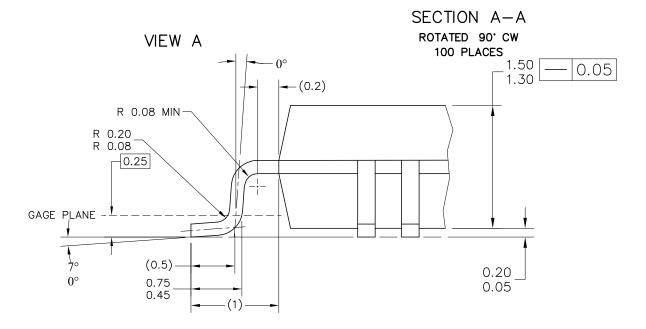

**Mechanical Outline Drawings**

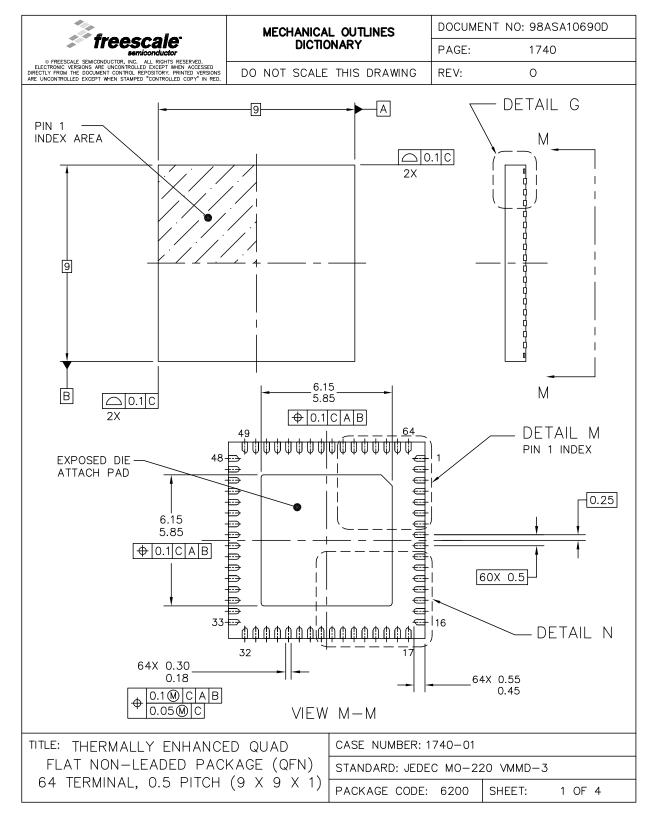

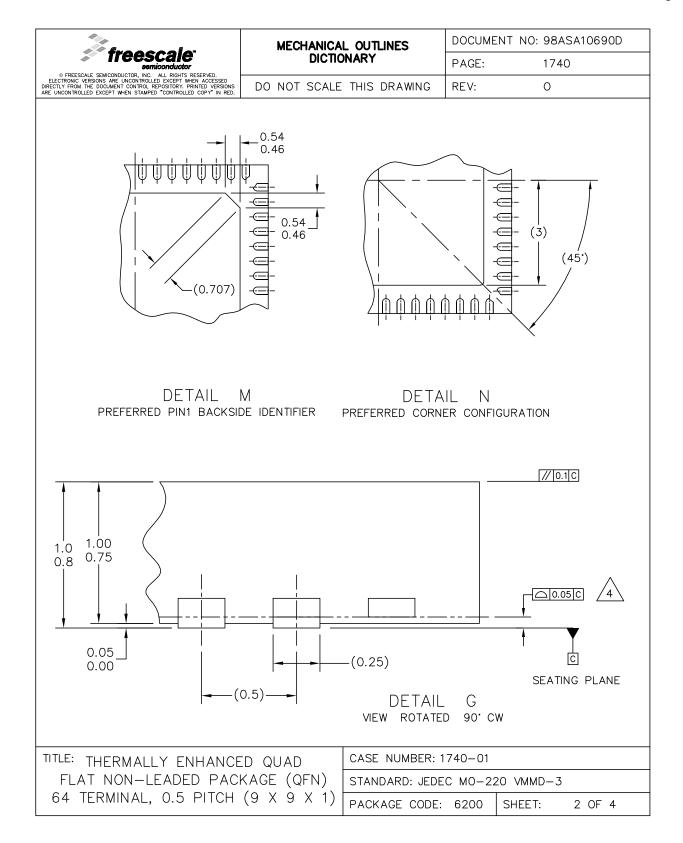

# 3.2 64 QFN Package

#### **Mechanical Outline Drawings**

### **Mechanical Outline Drawings**

|                                                                                                                                                                                                                                                         |                                                                                  |               | DOCUMENT NO: 98ASA10690D |            |           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------|--------------------------|------------|-----------|

|                                                                                                                                                                                                                                                         | REVISION HISTORY                                                                 |               | PAGE: 1740               |            |           |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.<br>ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL, REPOSITORY, PRINTED VERSIONS<br>ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED. |                                                                                  |               | REV:                     | 0          |           |

| LTR ORIGINATOR                                                                                                                                                                                                                                          | REVIS                                                                            | SIONS         |                          | DRAFTER    | DATE      |

| O ERIC TRIPLETT RELEASED FO                                                                                                                                                                                                                             | R PRODUCTION                                                                     | PRODUCTION    |                          | TAYLOR LIU | 27JUL2005 |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               |                          |            |           |

|                                                                                                                                                                                                                                                         |                                                                                  |               | 740 01                   |            |           |

|                                                                                                                                                                                                                                                         | THERMALLY ENHANCED QUADCase Number: 174T NON-LEADED PACKAGE (QFN)STANDARD: JEDEC |               |                          |            |           |

| 64 TERMINAL, 0.5 PITCH                                                                                                                                                                                                                                  | (9 X 9 X 1)                                                                      | PACKAGE CODE: |                          | SHEET:     | 4 OF 4    |

NOTES:

- 1. ALL DIMENSIONS IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- /3. MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

5. PARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.

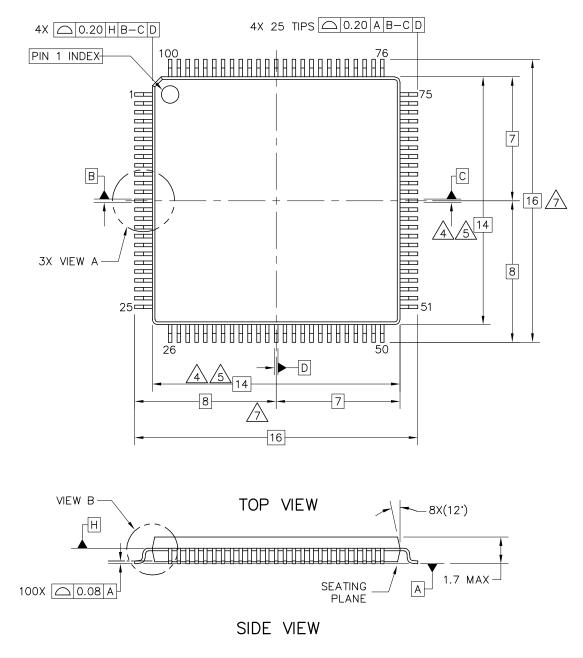

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. |                           | MECHANICA    | L OUTLINE            | PRINT VERSION NO | T TO SCALE  |

|---------------------------------------------------------|---------------------------|--------------|----------------------|------------------|-------------|

|                                                         | TITLE: PBGA, LOW PROFILE, |              | DOCUMENT NO          | ): 98ASA10670D   | REV: O      |

|                                                         | 81 I/O, 10 X 10 PKG,      |              | CASE NUMBER: 1662-01 |                  | 04 FEB 2005 |

|                                                         | 1 MM PITCH (M             | STANDARD: NO | DN-JEDEC             |                  |             |

**Mechanical Outline Drawings**

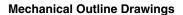

# 3.4 100-pin LQFP Package

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE       |              | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------|--------------------------|--------------|----------------------------|-------------|

| пте:<br>100 LEAD LQFP<br>14 X 14, 0.5 PITCH, 1.4 THICK  | DOCUMENT NO: 98ASS23308W |              | REV: G                     |             |

|                                                         | L THICK                  | CASE NUMBER  | 2: 983–03                  | 07 APR 2005 |

|                                                         | THOR                     | STANDARD: NO | N-JEDEC                    |             |

**Mechanical Outline Drawings**

VIEW B

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.  | MECHANICAL OUTLINE |                          | PRINT VERSION NOT TO SCALE |             |

|----------------------------------------------------------|--------------------|--------------------------|----------------------------|-------------|

| TITLE:<br>100 LEAD LQFP<br>14 X 14, 0.5 PITCH, 1.4 THICK |                    | DOCUMENT NO: 98ASS23308W |                            | REV: G      |

|                                                          | - THICK            | CASE NUMBER              | 8: 983–03                  | 07 APR 2005 |

|                                                          |                    | STANDARD: NO             | DN-JEDEC                   |             |

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: MCF5213EC Rev. 3 05/2007 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.