Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detuils                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | Н8/300Н                                                                        |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20MHz                                                                          |

| Connectivity               | I²C, SCI                                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                             |

| Number of I/O              | 45                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                      |

| Data Converters            | A/D 8x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-LQFP                                                                        |

| Supplier Device Package    | 64-LFQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f3684gfpv |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 1. The  $\overline{\text{NMI}}$  pin is reserved for the E7 or E8, and cannot be used.

- 2. Pins P85, P86, and P87 cannot be used. In order to use these pins, additional hardware must be provided on the user board.

- 3. Area H'D000 to H'DFFF is used by the E7 or E8, and is not available to the user.

- 4. Area H'F780 to H'FB7F must on no account be accessed.

- 5. When the E7 or E8 is used, address breaks can be set as either available to the user or for use by the E7 or E8. If address breaks are set as being used by the E7 or E8, the address break control registers must not be accessed.

- 6. When the E7 or E8 is used,  $\overline{\text{NMI}}$  is an input/output pin (open-drain in output mode), P85 and P87 are input pins, and P86 is an output pin.

- 7. Use channel 1 of the SCI3 (P21/RXD, P22/TXD) in on-board programming mode by boot mode.

Related Manuals: The latest versions of all related manuals are available from our web site. Please ensure you have the latest versions of all documents you require. http://www.renesas.com/

#### H8/3687 Group manuals:

| Document Title                 | Document No. |

|--------------------------------|--------------|

| H8/3687 Group Hardware Manual  | This manual  |

| H8/300H Series Software Manual | REJ09B0213   |

#### User's manuals for development tools:

| Document Title                                                                                      | Document No. |

|-----------------------------------------------------------------------------------------------------|--------------|

| H8S, H8/300 Series C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual               | REJ10B0058   |

| Microcomputer Development Environment System H8S, H8/300 Series<br>Simulator/Debugger User's Manual | ADE-702-282  |

| H8S, H8/300 Series High-Performance Embedded Workshop 3, Tutorial                                   | REJ10B0024   |

| H8S, H8/300 Series High-Performance Embedded Workshop 3, User's Manual                              | REJ10B0026   |

# Contents

| Secti | on 1                   | Overview1                                          |  |  |  |  |  |  |

|-------|------------------------|----------------------------------------------------|--|--|--|--|--|--|

| 1.1   | Features1              |                                                    |  |  |  |  |  |  |

| 1.2   | Internal Block Diagram |                                                    |  |  |  |  |  |  |

| 1.3   | Pin A                  | rrangement                                         |  |  |  |  |  |  |

| 1.4   | Pin Fu                 | inctions7                                          |  |  |  |  |  |  |

|       |                        |                                                    |  |  |  |  |  |  |

| Secti | on 2                   | CPU11                                              |  |  |  |  |  |  |

| 2.1   | Addre                  | ess Space and Memory Map 12                        |  |  |  |  |  |  |

| 2.2   | Regist                 | ter Configuration15                                |  |  |  |  |  |  |

|       | 2.2.1                  | General Registers                                  |  |  |  |  |  |  |

|       | 2.2.2                  | Program Counter (PC)                               |  |  |  |  |  |  |

|       | 2.2.3                  | Condition-Code Register (CCR)                      |  |  |  |  |  |  |

| 2.3   | Data F                 | Formats19                                          |  |  |  |  |  |  |

|       | 2.3.1                  | General Register Data Formats                      |  |  |  |  |  |  |

|       | 2.3.2                  | Memory Data Formats                                |  |  |  |  |  |  |

| 2.4   | Instru                 | ction Set                                          |  |  |  |  |  |  |

|       | 2.4.1                  | Table of Instructions Classified by Function    22 |  |  |  |  |  |  |

|       | 2.4.2                  | Basic Instruction Formats                          |  |  |  |  |  |  |

| 2.5   | Addre                  | ssing Modes and Effective Address Calculation      |  |  |  |  |  |  |

|       | 2.5.1                  | Addressing Modes                                   |  |  |  |  |  |  |

|       | 2.5.2                  | Effective Address Calculation                      |  |  |  |  |  |  |

| 2.6   | Basic                  | Bus Cycle                                          |  |  |  |  |  |  |

|       | 2.6.1                  | Access to On-Chip Memory (RAM, ROM)                |  |  |  |  |  |  |

|       | 2.6.2                  | On-Chip Peripheral Modules                         |  |  |  |  |  |  |

| 2.7   | CPU S                  | States                                             |  |  |  |  |  |  |

| 2.8   | Usage                  | Notes                                              |  |  |  |  |  |  |

|       | 2.8.1                  | Notes on Data Access to Empty Areas                |  |  |  |  |  |  |

|       | 2.8.2                  | EEPMOV Instruction                                 |  |  |  |  |  |  |

|       | 2.8.3                  | Bit-Manipulation Instruction                       |  |  |  |  |  |  |

| ~ .   |                        |                                                    |  |  |  |  |  |  |

| Secti |                        | Exception Handling                                 |  |  |  |  |  |  |

| 3.1   | -                      | tion Sources and Vector Address                    |  |  |  |  |  |  |

| 3.2   | U                      | ter Descriptions                                   |  |  |  |  |  |  |

|       | 3.2.1                  | Interrupt Edge Select Register 1 (IEGR1) 50        |  |  |  |  |  |  |

|       | 3.2.2                  | Interrupt Edge Select Register 2 (IEGR2)           |  |  |  |  |  |  |

|       | 3.2.3                  | Interrupt Enable Register 1 (IENR1)                |  |  |  |  |  |  |

|       | 3.2.4                  | Interrupt Enable Register 2 (IENR2)                |  |  |  |  |  |  |

# RENESAS

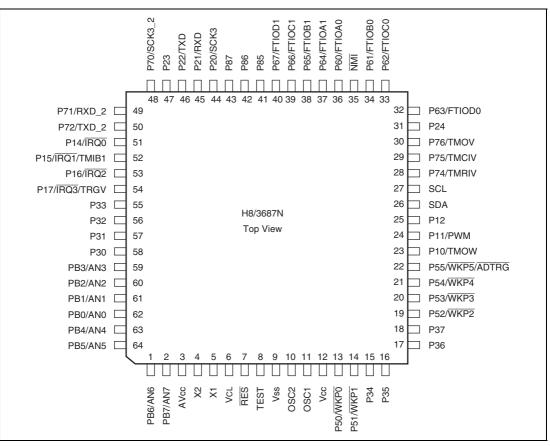

Figure 1.4 Pin Arrangement of H8/3687N (EEPROM Stacked Version) (FP-64E)

|                                            |                     | Pin No.<br>FP-64E | _                         |                                                                                                                                            |

|--------------------------------------------|---------------------|-------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Туре                                       | Symbol              | FP-64A            | I/O                       | Functions                                                                                                                                  |

| Timer V                                    | TMOV                | 30                | Output                    | This is an output pin for waveforms generated by the output compare function.                                                              |

|                                            | TMCIV               | 29                | Input                     | External event input pin.                                                                                                                  |

|                                            | TMRIV               | 28                | Input                     | Counter reset input pin.                                                                                                                   |

|                                            | TRGV                | 54                | Input                     | Counter start trigger input pin.                                                                                                           |

| Timer Z                                    | FTIOA0              | 36                | I/O                       | Output compare output/input capture input/external clock input pin                                                                         |

|                                            | FTIOB0              | 34                | I/O                       | Output compare output/input capture input/PWM output pin                                                                                   |

|                                            | FTIOC0              | 33                | I/O                       | Output compare output/input capture<br>input/PWM sync output pin (at a reset,<br>complementary PWM mode)                                   |

|                                            | FTIOD0              | 32                | I/O                       | Output compare output/input capture input/PWM output pin                                                                                   |

|                                            | FTIOA1              | 37                | I/O                       | Output compare output/input capture<br>input/PWM output pin (at a reset,<br>complementary PWM mode)                                        |

|                                            | FTIOB1 to<br>FTIOD1 | 38 to 40          | I/O                       | Output compare output/input capture input/PWM output pin                                                                                   |

| 14-bit PWM                                 | PWM                 | 24                | Output                    | 14-bit PWM square wave output pin                                                                                                          |

| I <sup>2</sup> C bus<br>interface<br>(IIC) | SDA*1               | 26                | I/O                       | IIC data I/O pin. Can directly drive a bus by NMOS open-drain output. When using this pin, external pull-up resistance is required.        |

|                                            | SCL*1               | 27                | I/O<br>(EEPROM:<br>Input) | IIC clock I/O pin. Can directly drive a bus by<br>NMOS open-drain output. When using this pin,<br>external pull-up resistance is required. |

| Serial com-<br>munication                  | TXD,<br>TXD_2       | 46, 50            | Output                    | Transmit data output pin                                                                                                                   |

| interface<br>(SCI)                         | RXD,<br>RXD_2       | 45, 49            | Input                     | Receive data input pin                                                                                                                     |

|                                            | SCK3,<br>SCK3_2     | 44, 48            | I/O                       | Clock I/O pin                                                                                                                              |

| A/D<br>converter                           | AN7 to AN0          | 1, 2,<br>59 to 64 | Input                     | Analog input pin                                                                                                                           |

|                                            | ADTRG               | 22                | Input                     | A/D converter trigger input pin.                                                                                                           |

# Section 7 ROM

The features of the 56-kbyte or 32-kbyte flash memories built into the flash memory (F-ZTAT) version are summarized below.

- Programming/erase methods

- The flash memory is programmed 128 bytes at a time. Erase is performed in single-block units. The flash memory is configured as follows: 1 kbyte × 4 blocks, 28 kbytes × 1 block, 16 kbytes × 1 block, and 8 kbytes × 1 block for H8/3687F and 1 kbyte × 4 blocks and 28 kbytes × 1 block for H8/3684F. To erase the entire flash memory, each block must be erased in turn.

- Reprogramming capability

- The flash memory can be reprogrammed up to 1,000 times.

- On-board programming

- On-board programming/erasing can be done in boot mode, in which the boot program built into the chip is started to erase or program of the entire flash memory. In normal user program mode, individual blocks can be erased or programmed.

- Programmer mode

- Flash memory can be programmed/erased in programmer mode using a PROM programmer, as well as in on-board programming mode.

- Automatic bit rate adjustment

- For data transfer in boot mode, this LSI's bit rate can be automatically adjusted to match the transfer bit rate of the host.

- Programming/erasing protection

- Sets software protection against flash memory programming/erasing.

- Power-down mode

- Operation of the power supply circuit can be partly halted in subactive mode. As a result, flash memory can be read with low power consumption.

# 7.1 Block Configuration

Figure 7.1 shows the block configuration of flash memory. The thick lines indicate erasing units, the narrow lines indicate programming units, and the values are addresses. The 56-kbyte flash memory is divided into 1 kbyte  $\times$  4 blocks, 28 kbytes  $\times$  1 block, 16 kbytes  $\times$  1 block, and 8 kbytes  $\times$  1 block. The 32-kbyte flash memory is divided into 1 kbyte  $\times$  4 blocks and 28 kbytes  $\times$  1 blocks. Erasing is performed in these units. Programming is performed in 128-byte units starting from an address with lower eight bits H'00 or H'80.

## P62/FTIOC0 pin

| Register      | TOER | TFCR            | TPMR  | TIORC0          | PCR6  |                            |

|---------------|------|-----------------|-------|-----------------|-------|----------------------------|

| Bit Name      | EC0  | CMD1 to<br>CMD0 | PWMC0 | IOC2 to<br>IOC0 | PCR62 | Pin Function               |

| Setting Value | 1    | 00              | 0     | 000 or<br>1XX   | 0     | P62 input/FTIOC0 input pin |

|               |      |                 |       |                 | 1     | P62 output pin             |

|               | 0    | 00              | 0     | 001 or<br>01X   | Х     | FTIOC0 output pin          |

|               |      |                 | 1     | XXX             | _     |                            |

|               |      | Other than 00   | Х     | XXX             | _     |                            |

Legend: X: Don't care.

### P61/FTIOB0 pin

| Register      | TOER | TFCR            | TPMR  | TIORA0          | PCR6  |                            |

|---------------|------|-----------------|-------|-----------------|-------|----------------------------|

| Bit Name      | EB0  | CMD1 to<br>CMD0 | PWMB0 | IOB2 to<br>IOB0 | PCR61 | Pin Function               |

| Setting Value | 1    | 00              | 0     | 000 or<br>1XX   | 0     | P61 input/FTIOB0 input pin |

|               |      |                 |       |                 | 1     | P61 output pin             |

|               | 0    | 00              | 0     | 001 or<br>01X   | Х     | FTIOB0 output pin          |

|               |      |                 | 1     | XXX             | _     |                            |

|               |      | Other than 00   | Х     | XXX             |       |                            |

Legend: X: Don't care.

# 9.7.3 Pin Functions

The correspondence between the register specification and the port functions is shown below.

### P87 pin

| Register      | PCR8  |                |

|---------------|-------|----------------|

| Bit Name      | PCR87 | Pin Function   |

| Setting Value | 0     | P87 input pin  |

|               | 1     | P87 output pin |

#### P86 pin

| Register      | PCR8  |                |  |

|---------------|-------|----------------|--|

| Bit Name      | PCR86 | Pin Function   |  |

| Setting Value | 0     | P86 input pin  |  |

|               | 1     | P86 output pin |  |

### P85 pin

| Register      | PCR8  |                |

|---------------|-------|----------------|

| Bit Name      | PCR85 | Pin Function   |

| Setting Value | 0     | P85 input pin  |

|               | 1     | P85 output pin |

#### 10.3.3 Hour Data Register (RHRDR)

RHRDR counts the BCD-coded hour value on the carry generated once per hour by RMINDR. The setting range is either decimal 00 to 11 or 00 to 23 by the selection of the 12/24 bit in RTCCR1.

|     |          | Initial |     |                                                                                                                                                                                                                                       |

|-----|----------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                                                                                                                                                           |

| 7   | BSY      | —       | R   | RTC busy                                                                                                                                                                                                                              |

|     |          |         |     | This bit is set to 1 when the RTC is updating (operating) the values of second, minute, hour, and day-of-week data registers. When this bit is 0, the values of second, minute, hour, and day-of-week data registers must be adopted. |

| 6   | —        | 0       | _   | Reserved                                                                                                                                                                                                                              |

|     |          |         |     | This bit is always read as 0.                                                                                                                                                                                                         |

| 5   | HR11     |         | R/W | Counting ten's position of hours                                                                                                                                                                                                      |

| 4   | HR10     | _       | R/W | Counts on 0 to 2 for ten's position of hours.                                                                                                                                                                                         |

| 3   | HR03     |         | R/W | Counting one's position of hours                                                                                                                                                                                                      |

| 2   | HR02     | —       | R/W | Counts on 0 to 9 once per hour. When a carry is                                                                                                                                                                                       |

| 1   | HR01     | _       | R/W | generated, 1 is added to the ten's position.                                                                                                                                                                                          |

| 0   | HR00     | —       | R/W |                                                                                                                                                                                                                                       |

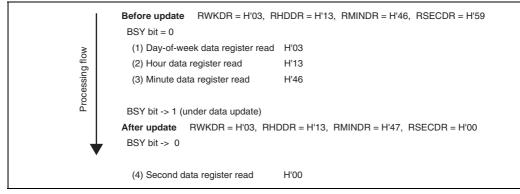

#### 10.4.3 Data Reading Procedure

When the seconds, minutes, hours, or day-of-week datum is updated while time data is being read, the data obtained may not be correct, and so the time data must be read again. Figure 10.4 shows an example in which correct data is not obtained. In this example, since only RSECDR is read after data update, about 1-minute inconsistency occurs.

To avoid reading in this timing, the following processing must be performed.

- 1. Check the setting of the BSY bit, and when the BSY bit changes from 1 to 0, read from the second, minute, hour, and day-of-week registers. When about 62.5 ms is passed after the BSY bit is set to 1, the registers are updated, and the BSY bit is cleared to 0.

- 2. Making use of interrupts, read from the second, minute, hour, and day-of week registers after the IRRTA flag in IRR1 is set to 1 and the BSY bit is confirmed to be 0.

- 3. Read from the second, minute, hour, and day-of week registers twice in a row, and if there is no change in the read data, the read data is used.

Figure 10.4 Example: Reading of Inaccurate Time Data

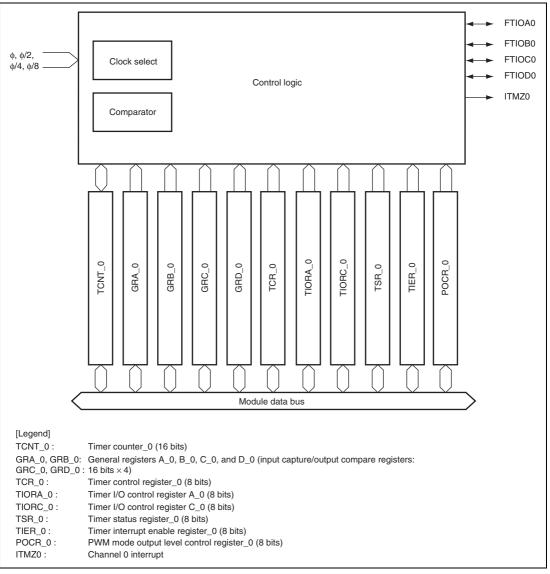

Figure 13.2 Timer Z (Channel 0) Block Diagram

RENESAS

#### 14.2.1 Timer Control/Status Register WD (TCSRWD)

TCSRWD performs the TCSRWD and TCWD write control. TCSRWD also controls the watchdog timer operation and indicates the operating state. TCSRWD must be rewritten by using the MOV instruction. The bit manipulation instruction cannot be used to change the setting value.

| 5.4 |          | Initial | -   |                                                                                                                       |

|-----|----------|---------|-----|-----------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                                           |

| 7   | B6WI     | 1       | R/W | Bit 6 Write Inhibit                                                                                                   |

|     |          |         |     | The TCWE bit can be written only when the write value of the B6WI bit is 0.                                           |

|     |          |         |     | This bit is always read as 1.                                                                                         |

| 6   | TCWE     | 0       | R/W | Timer Counter WD Write Enable                                                                                         |

|     |          |         |     | TCWD can be written when the TCWE bit is set to 1.                                                                    |

|     |          |         |     | When writing data to this bit, the value for bit 7 must be 0.                                                         |

| 5   | B4WI     | 1       | R/W | Bit 4 Write Inhibit                                                                                                   |

|     |          |         |     | The TCSRWE bit can be written only when the write value of the B4WI bit is 0. This bit is always read as 1.           |

| 4   | TCSRWE   | 0       | R/W | Timer Control/Status Register WD Write Enable                                                                         |

|     |          |         |     | The WDON and WRST bits can be written when the<br>TCSRWE bit is set to 1.                                             |

|     |          |         |     | When writing data to this bit, the value for bit 5 must be 0.                                                         |

| 3   | B2WI     | 1       | R/W | Bit 2 Write Inhibit                                                                                                   |

|     |          |         |     | This bit can be written to the WDON bit only when the write value of the B2WI bit is 0.                               |

|     |          |         |     | This bit is always read as 1.                                                                                         |

| 2   | WDON     | 0       | R/W | Watchdog Timer On                                                                                                     |

|     |          |         |     | TCWD starts counting up when WDON is set to 1 and<br>halts when WDON is cleared to 0.                                 |

|     |          |         |     | [Setting condition]                                                                                                   |

|     |          |         |     | When 1 is written to the WDON bit while writing 0 to the B2WI bit when the TCSRWE bit=1                               |

|     |          |         |     | [Clearing conditions]                                                                                                 |

|     |          |         |     | Reset by RES pin                                                                                                      |

|     |          |         |     | • When 0 is written to the WDON bit while writing 0 to                                                                |

|     |          |         |     | the B2WI when the TCSRWE bit=1                                                                                        |

| 1   | B0WI     | 1       | R/W | Bit 0 Write Inhibit                                                                                                   |

|     |          |         |     | This bit can be written to the WRST bit only when the write value of the B0WI bit is 0. This bit is always read as 1. |

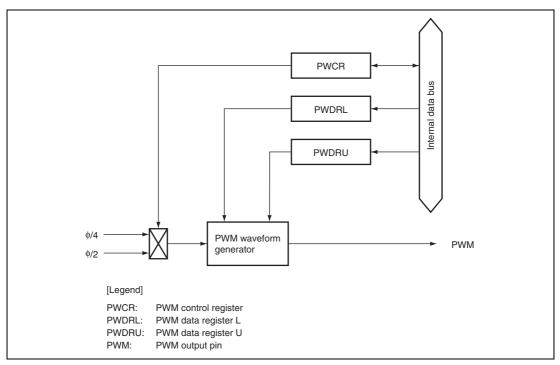

# Section 15 14-Bit PWM

The 14-bit PWM is a pulse division type PWM that can be used for electronic tuner control, etc. Figure 15.1 shows a block diagram of the 14-bit PWM.

## 15.1 Features

Choice of two conversion periods

A conversion period of  $32768/\phi$  with a minimum modulation width of  $2/\phi$ , or a conversion period of  $16384/\phi$  with a minimum modulation width of  $1/\phi$ , can be selected.

• Pulse division method for less ripple

Figure 15.1 Block Diagram of 14-Bit PWM

# Section 16 Serial Communication Interface 3 (SCI3)

This LSI includes a serial communication interface 3 (SCI3), which has independent two channels. The SCI3 can handle both asynchronous and clocked synchronous serial communication. In asynchronous mode, serial data communication can be carried out using standard asynchronous communication chips such as a Universal Asynchronous Receiver/Transmitter (UART) or an Asynchronous Communication Interface Adapter (ACIA). A function is also provided for serial communication between processors (multiprocessor communication function).

Table 16.1 shows the SCI3 channel configuration and figure 16.1 shows a block diagram of the SCI3. Since pin functions are identical for each of the two channels (SCI3 and SCI3\_2), separate explanations are not given in this section.

# 16.1 Features

- Choice of asynchronous or clocked synchronous serial communication mode

- Full-duplex communication capability

The transmitter and receiver are mutually independent, enabling transmission and reception to be executed simultaneously.

Double-buffering is used in both the transmitter and the receiver, enabling continuous transmission and continuous reception of serial data.

- On-chip baud rate generator allows any bit rate to be selected

- External clock or on-chip baud rate generator can be selected as a transfer clock source.

- Six interrupt sources

Transmit-end, transmit-data-empty, receive-data-full, overrun error, framing error, and parity error.

Asynchronous mode

- Data length: 7 or 8 bits

- Stop bit length: 1 or 2 bits

- Parity: Even, odd, or none

- Receive error detection: Parity, overrun, and framing errors

- Break detection: Break can be detected by reading the RxD pin level directly in the case of a framing error

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                 |

|-----|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CKS1     | 0                | R/W | Clock Select 0 and 1                                                                                                                                                                                                                        |

| 0   | CKS0     | 0                | R/W | These bits select the clock source for the baud rate generator.                                                                                                                                                                             |

|     |          |                  |     | 00:                                                                                                                                                                                                                                         |

|     |          |                  |     | 01:                                                                                                                                                                                                                                         |

|     |          |                  |     | 10:                                                                                                                                                                                                                                         |

|     |          |                  |     | 11: φ/64 clock (n = 3)                                                                                                                                                                                                                      |

|     |          |                  |     | For the relationship between the bit rate register setting<br>and the baud rate, see section 16.3.8, Bit Rate Register<br>(BRR). n is the decimal representation of the value of n in<br>BRR (see section 16.3.8, Bit Rate Register (BRR)). |

#### 16.3.6 Serial Control Register 3 (SCR3)

SCR3 is a register that enables or disables SCI3 transfer operations and interrupt requests, and is also used to select the transfer clock source. For details on interrupt requests, refer to section 16.7, Interrupts.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                            |

|-----|----------|------------------|-----|------------------------------------------------------------------------|

| 7   | TIE      | 0                | R/W | Transmit Interrupt Enable                                              |

|     |          |                  |     | When this bit is set to 1, the TXI interrupt request is enabled.       |

| 6   | RIE      | 0                | R/W | Receive Interrupt Enable                                               |

|     |          |                  |     | When this bit is set to 1, RXI and ERI interrupt requests are enabled. |

| 5   | TE       | 0                | R/W | Transmit Enable                                                        |

|     |          |                  |     | When this bit s set to 1, transmission is enabled.                     |

| 4   | RE       | 0                | R/W | Receive Enable                                                         |

|     |          |                  |     | When this bit is set to 1, reception is enabled.                       |

# **19.4** Operation

### **19.4.1 EEPROM Interface**

The HD64N3687G has a multi-chip structure with two internal chips of the HD64F3687G (F-ZTAT<sup>TM</sup> version) and 512-byte EEPROM. The HD6483687G has a multi-chip structure with two internal chips of the HD6433687G (mask-ROM version) and 512-byte EEPROM.

The EEPROM interface is the  $I^2C$  bus interface. This  $I^2C$  bus is open to the outside, so the communication with the external devices connected to the  $I^2C$  bus can be made.

#### 19.4.2 Bus Format and Timing

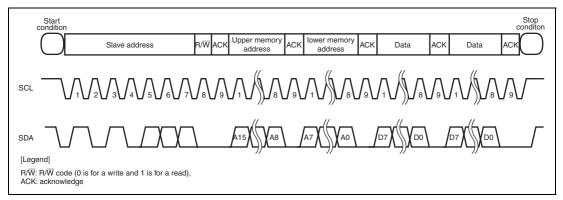

The I<sup>2</sup>C bus format and the I<sup>2</sup>C bus timing follow section 17.4.1, I<sup>2</sup>C Bus Format. The bus formats specific for the EEPROM are the following two.

- 1. The EEPROM address is configured of two bytes, the write data is transferred in the order of upper address and lower address from each MSB side.

- 2. The write data is transmitted from the MSB side.

The bus format and bus timing of the EEPROM are shown in figure 19.2.

Figure 19.2 EEPROM Bus Format and Bus Timing

### **19.4.3** Start Condition

A high-to-low transition of the SDA input with the SCL input high is needed to generate the start condition for starting read, write operation.

|                           |                 |                                                                                        |                                                                        |                       | Value | es                   |      |       |

|---------------------------|-----------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------|-------|----------------------|------|-------|

| ltem                      | Symbol          | Applicable Pins                                                                        | Test Condition                                                         | Min                   | Тур   | Max                  | Unit | Notes |

| Input low<br>voltage      | V <sub>IL</sub> | RES, NMI,<br>WKP0 to WKP5,<br>IRQ0 to IRQ3,<br>ADTRG, TMIB1,<br>TMRIV,                 | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$                               | -0.3                  | _     | $V_{cc} \times 0.2$  | V    |       |

|                           |                 | TMCIV, FTIOA0<br>to FTIOD0,<br>FTIOA1 to<br>FTIOD1, SCK3,<br>SCK3_2, TRGV              |                                                                        | -0.3                  | _     | $V_{cc} \times 0.1$  | —    |       |

|                           |                 | RXD, RXD_2,<br>SCL, SDA,<br>P10 to P12,<br>P14 to P17,<br>P20 to P24,<br>P30 to P37,   | $V_{cc}$ = 4.0 to 5.5 V                                                | -0.3                  | _     | V <sub>cc</sub> ×0.3 | V    | _     |

|                           |                 | P50 to P57,<br>P60 to P67,.<br>P70 to P72,<br>P74 to P76,<br>P85 to P87,<br>PB0 to PB7 |                                                                        | -0.3                  | _     | V <sub>cc</sub> ×0.2 | _    |       |

|                           |                 | OSC1                                                                                   | $V_{cc}$ = 4.0 to 5.5 V                                                | -0.3                  | _     | 0.5                  | ۷    | -     |

|                           |                 |                                                                                        |                                                                        | -0.3                  | _     | 0.3                  |      |       |

| Output<br>high<br>voltage | V <sub>oh</sub> | P10 to P12,<br>P14 to P17,<br>P20 to P24,<br>P30 to P37,                               | V <sub>cc</sub> = 4.0 to 5.5 V<br>-I <sub>OH</sub> = 1.5 mA            | V <sub>cc</sub> – 1.0 | _     | _                    | V    |       |

|                           |                 | P50 to P55,<br>P60 to P67,<br>P70 to P72,<br>P74 to P76,<br>P85 to P87                 | -l <sub>oH</sub> = 0.1 mA                                              | V <sub>cc</sub> – 0.5 | _     | _                    | _    |       |

|                           |                 | P56, P57                                                                               | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$<br>$-I_{OH} = 0.1 \text{ mA}$ | V <sub>cc</sub> – 2.5 | _     | _                    | V    | _     |

|                           |                 |                                                                                        | V <sub>cc</sub> =2.7 to 4.0 V<br>-I <sub>OH</sub> = 0.1 mA             | $V_{cc} - 2.0$        |       | _                    | _    |       |

RENESAS

### 23.3.4 A/D Converter Characteristics

#### Table 23.16 A/D Converter Characteristics

$V_{\rm cc}$  = 2.7 to 5.5 V,  $V_{\rm ss}$  = 0.0 V,  $T_{\rm a}$  = –20 to +75°C, unless otherwise indicated.

|                                   |                     | Applicable    | Test                               |                          | Val      | ues                    |                       | Reference<br>Figure                  |  |

|-----------------------------------|---------------------|---------------|------------------------------------|--------------------------|----------|------------------------|-----------------------|--------------------------------------|--|

| Item                              | Symbol              | Pins          | Condition                          | Min                      | Тур      | Max                    | Unit                  |                                      |  |

| Analog power supply voltage       | $AV_{cc}$           | $AV_{cc}$     |                                    | 3.3                      | $V_{cc}$ | 5.5                    | V                     | *1                                   |  |

| Analog input voltage              | $AV_{IN}$           | AN0 to<br>AN7 |                                    | V <sub>ss</sub> –<br>0.3 | _        | AV <sub>cc</sub> + 0.3 | V                     |                                      |  |

| Analog power supply               | $AI_{OPE}$          | $AV_{cc}$     | $AV_{cc} = 5.0 V$                  | _                        | —        | 2.0                    | mA                    |                                      |  |

| current                           |                     |               | f <sub>osc</sub> =<br>20 MHz       |                          |          |                        |                       |                                      |  |

|                                   | AI <sub>stop1</sub> | $AV_{cc}$     |                                    | _                        | 50       | _                      | μA                    | * <sup>2</sup><br>Reference<br>value |  |

|                                   | $AI_{_{STOP2}}$     | $AV_{cc}$     |                                    | —                        | —        | 5.0                    | μA                    | *3                                   |  |

| Analog input<br>capacitance       | C <sub>AIN</sub>    | AN0 to<br>AN7 |                                    | _                        | _        | 30.0                   | pF                    |                                      |  |

| Allowable signal source impedance | $R_{_{\text{AIN}}}$ | AN0 to<br>AN7 |                                    | —                        | —        | 5.0                    | kΩ                    |                                      |  |

| Resolution (data length)          |                     |               |                                    | 10                       | 10       | 10                     | bit                   |                                      |  |

| Conversion time (single mode)     |                     |               | AV <sub>cc</sub> = 3.3 to<br>5.5 V | 134                      | —        | _                      | $t_{_{\mathrm{cyc}}}$ |                                      |  |

| Nonlinearity error                |                     |               | -                                  | _                        | _        | ±7.5                   | LSB                   | _                                    |  |

| Offset error                      |                     |               | -                                  | _                        | _        | ±7.5                   | LSB                   | _                                    |  |

| Full-scale error                  |                     |               | _                                  | _                        | _        | ±7.5                   | LSB                   | _                                    |  |

| Quantization error                |                     |               | _                                  | —                        | —        | ±0.5                   | LSB                   | _                                    |  |

| Absolute accuracy                 |                     |               | -                                  | _                        | —        | ±8.0                   | LSB                   | —                                    |  |

| Conversion time (single mode)     |                     |               | AV <sub>cc</sub> = 4.0 to<br>5.5 V | 70                       | _        | —                      | $t_{_{\mathrm{cyc}}}$ |                                      |  |

| Nonlinearity error                |                     |               | _                                  | —                        | —        | ±7.5                   | LSB                   | _                                    |  |

| Offset error                      |                     |               | _                                  | —                        | —        | ±7.5                   | LSB                   | _                                    |  |

| Full-scale error                  |                     |               | _                                  | _                        | —        | ±7.5                   | LSB                   | _                                    |  |

| Quantization error                |                     |               | _                                  | _                        | —        | ±0.5                   | LSB                   | _                                    |  |

| Absolute accuracy                 |                     |               | _                                  | _                        | _        | ±8.0                   | LSB                   | _                                    |  |

## 2. Arithmetic Instructions

|          |                   |              | Addressing Mode and<br>Instruction Length (bytes) |    |      |           |             |     |          |        | ) |                                                                      |   |     |       |       |     | No. of<br>States <sup>*1</sup> |        |          |

|----------|-------------------|--------------|---------------------------------------------------|----|------|-----------|-------------|-----|----------|--------|---|----------------------------------------------------------------------|---|-----|-------|-------|-----|--------------------------------|--------|----------|

| Mnemonic |                   | Operand Size | #xx                                               | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | @ @ aa |   | Operation                                                            |   | Con | ditic | on Co | ode | с                              | Normal | Advanced |

| ADD      | ADD.B #xx:8, Rd   | В            | 2                                                 |    |      |           |             |     |          |        |   | $Rd8+#xx:8 \rightarrow Rd8$                                          | _ | \$  | \$    | 1     | \$  | \$                             |        | 2        |

|          | ADD.B Rs, Rd      | В            |                                                   | 2  |      |           |             |     |          |        |   | $Rd8+Rs8 \rightarrow Rd8$                                            | - | \$  | \$    | 1     | \$  | \$                             | 2      | 2        |

|          | ADD.W #xx:16, Rd  | W            | 4                                                 |    |      |           |             |     |          |        |   | Rd16+#xx:16 $\rightarrow$ Rd16                                       | - | (1) | \$    | 1     | \$  | \$                             | 4      | 4        |

|          | ADD.W Rs, Rd      | W            |                                                   | 2  |      |           |             |     |          |        |   | Rd16+Rs16 $\rightarrow$ Rd16                                         | - | (1) | \$    | \$    | \$  | \$                             | 2      | 2        |

|          | ADD.L #xx:32, ERd | L            | 6                                                 |    |      |           |             |     |          |        |   | ERd32+#xx:32 →<br>ERd32                                              | - | (2) | \$    | \$    | \$  | \$                             | e      | 6        |

|          | ADD.L ERs, ERd    | L            |                                                   | 2  |      |           |             |     |          |        |   | ERd32+ERs32 →<br>ERd32                                               | - | (2) | \$    | \$    | \$  | \$                             | 2      | 2        |

| ADDX     | ADDX.B #xx:8, Rd  | В            | 2                                                 |    |      |           |             |     |          |        |   | $Rd8+#xx:8 + C \rightarrow Rd8$                                      | - | \$  | \$    | (3)   | \$  | Ĵ                              | 2      | 2        |

|          | ADDX.B Rs, Rd     | В            |                                                   | 2  |      |           |             |     |          |        |   | Rd8+Rs8 +C → Rd8                                                     | - | 1   | 1     | (3)   | 1   | 1                              | 2      | 2        |

| ADDS     | ADDS.L #1, ERd    | L            |                                                   | 2  |      |           |             |     |          |        |   | ERd32+1 $\rightarrow$ ERd32                                          | - |     | _     | _     | _   |                                | 2      | 2        |

|          | ADDS.L #2, ERd    | L            |                                                   | 2  |      |           |             |     |          |        |   | $ERd32+2 \rightarrow ERd32$                                          | _ | -   | -     | —     | _   | -                              | - 2    |          |

|          | ADDS.L #4, ERd    | L            |                                                   | 2  |      |           |             |     |          |        |   | ERd32+4 $\rightarrow$ ERd32                                          | - | -   | -     | -     | _   | -                              | - 2    |          |

| INC      | INC.B Rd          | В            |                                                   | 2  |      |           |             |     |          |        |   | $Rd8+1 \rightarrow Rd8$                                              | - | -   | \$    | \$    | \$  | —                              | 2      | 2        |

|          | INC.W #1, Rd      | W            |                                                   | 2  |      |           |             |     |          |        |   | Rd16+1 $\rightarrow$ Rd16                                            | — | -   | \$    | \$    | \$  | —                              | 2      | 2        |

|          | INC.W #2, Rd      | W            |                                                   | 2  |      |           |             |     |          |        |   | $Rd16+2 \rightarrow Rd16 \qquad \uparrow \uparrow \uparrow \uparrow$ |   | \$  | —     | 2     | 2   |                                |        |          |

|          | INC.L #1, ERd     | L            |                                                   | 2  |      |           |             |     |          |        |   | ERd32+1 $\rightarrow$ ERd32 $  \updownarrow$ $\updownarrow$          |   | \$  | —     | 2     | 2   |                                |        |          |

|          | INC.L #2, ERd     | L            |                                                   | 2  |      |           |             |     |          |        |   | $ERd32+2 \rightarrow ERd32$                                          | — | -   | \$    | \$    | \$  | —                              | 2      | 2        |

| DAA      | DAA Rd            | В            |                                                   | 2  |      |           |             |     |          |        |   | Rd8 decimal adjust $\rightarrow$ Rd8                                 | - | *   | \$    | \$    | *   | -                              | 2      | 2        |

| SUB      | SUB.B Rs, Rd      | В            |                                                   | 2  |      |           |             |     |          |        |   | $Rd8-Rs8 \rightarrow Rd8$                                            | — | \$  | \$    | \$    | \$  | \$                             | 2      | 2        |

|          | SUB.W #xx:16, Rd  | W            | 4                                                 |    |      |           |             |     |          |        |   | Rd16–#xx:16 $\rightarrow$ Rd16                                       | - | (1) | \$    | \$    | \$  | \$                             | 4      | 4        |

|          | SUB.W Rs, Rd      | W            |                                                   | 2  |      |           |             |     |          |        |   | Rd16–Rs16 $\rightarrow$ Rd16                                         |   | (1) | \$    | \$    | \$  | \$                             | 2      | 2        |

|          | SUB.L #xx:32, ERd | L            | 6                                                 |    |      |           |             |     |          |        |   | ERd32–#xx:32 $\rightarrow$ ERd32                                     |   | (2) | \$    | \$    | \$  | \$                             | e      | 6        |

|          | SUB.L ERs, ERd    | L            |                                                   | 2  |      |           |             |     |          |        |   | ERd32–ERs32 $\rightarrow$ ERd32                                      | — | (2) | \$    | \$    | \$  | \$                             | 2      | 2        |

| SUBX     | SUBX.B #xx:8, Rd  | В            | 2                                                 |    |      |           |             |     |          |        |   | Rd8–#xx:8–C $\rightarrow$ Rd8                                        | - | \$  | \$    | (3)   | \$  | \$                             | 2      | 2        |

|          | SUBX.B Rs, Rd     | В            |                                                   | 2  |      |           |             |     |          |        |   | Rd8–Rs8–C $\rightarrow$ Rd8                                          | — | \$  | \$    | (3)   | \$  | \$                             | 2      | 2        |

| SUBS     | SUBS.L #1, ERd    | L            |                                                   | 2  |      |           |             |     |          |        |   | ERd32–1 $\rightarrow$ ERd32                                          | - | -   | -     | -     | —   | -                              | 2      | 2        |

|          | SUBS.L #2, ERd    | L            |                                                   | 2  |      |           |             |     |          |        |   | $ERd32-2 \rightarrow ERd32$                                          |   | -   | -     | -     | —   | -                              | 2      | 2        |

|          | SUBS.L #4, ERd    | L            |                                                   | 2  |      |           |             |     |          |        |   | $ERd32-4 \rightarrow ERd32$                                          | - | -   | -     | -     | —   | -                              | 2      | 2        |

| DEC      | DEC.B Rd          | В            |                                                   | 2  |      |           |             |     |          |        |   | Rd8–1 $\rightarrow$ Rd8                                              | — | -   | \$    | \$    | \$  | -                              | 2      | 2        |

|          | DEC.W #1, Rd      | W            |                                                   | 2  |      |           |             |     |          |        |   | Rd16−1 → Rd16                                                        | - | -   | \$    | \$    | \$  | -                              | 2      | 2        |

|          | DEC.W #2, Rd      | W            |                                                   | 2  |      |           |             |     |          |        |   | Rd16–2 $\rightarrow$ Rd16                                            | — | -   | \$    | \$    | \$  | —                              | 2      | 2        |

# Main Revisions and Additions in this Edition

| Item                                                                                                  | Page    | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface                                                                                               | vi, vii | <ul> <li>Notes:</li> <li>When using the on-chip emulator (E7, E8) for H8/3687<br/>program development and debugging, the following restrictions<br/>must be noted.</li> <li>1. The NMI pin is reserved for the E7 or E8, and cannot be<br/>used.</li> <li>3. Area H'D000 to H'DFFF is used by the E7 or E8, and is not<br/>available to the user.</li> <li>5. When the E7 or E8 is used, address breaks can be set as<br/>either available to the user or for use by the E7 or E8. If<br/>address breaks are set as being used by the E7 or E8, the<br/>address break control registers must not be accessed.</li> <li>6. When the E7 or E8 is used, NMI is an input/output pin<br/>(open-drain in output mode), P85 and P87 are input pins,<br/>and P86 is an output pin.</li> <li>7. Use channel 1 of the SCI3 (P21/RXD, P22/TXD) in on-<br/>board programming mode by boot mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Section 1 Overview<br>Figure 1.2 Internal Block<br>Diagram of H8/3687N<br>(EEPROM Stacked<br>Version) | 4       | AD converter<br>PORA.VD<br>Port B<br>NWV Edu<br>AVcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Section 5 Clock Pulse<br>Generators<br>Figure 5.3 Typical<br>Connection to Crystal<br>Resonator       | 70      | $\begin{array}{c} OSC_1 \\ \hline \\ OSC_2 \\ \hline \\ OSC_2 \\ \hline \\ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 5.5 Typical<br>Connection to Ceramic<br>Resonator                                              | 71      | $\begin{array}{c} C_{1} \\ \hline \\ C_{2} \\ C_{2} \\ \hline \\ C_{2} \\ \hline \\ C_{2} \\ C_{2} \\ \hline \\ C_{2} \\ C_{$ |

| tem Page Revision (See Manual for Details)                                                      |             |                       |                 |                                        |                                          |                     |  |  |  |

|-------------------------------------------------------------------------------------------------|-------------|-----------------------|-----------------|----------------------------------------|------------------------------------------|---------------------|--|--|--|

| Section 20 Power-On<br>Reset and Low-Voltage<br>Detection Circuits<br>(Optional)                | 362         |                       |                 | o<br>∔                                 | 2<br>Wo                                  |                     |  |  |  |

| Figure 20.1 Block<br>Diagram of Power-On<br>Reset Circuit and Low-<br>Voltage Detection Circuit |             |                       |                 | CRES                                   |                                          |                     |  |  |  |

| Section 23 Electrical<br>Characteristics                                                        | 394,<br>395 |                       |                 | Applicable                             |                                          | Values              |  |  |  |

| Table 23.2 DC                                                                                   | 395         | Item                  | Symbol          | ••                                     | Test Condition                           | Min                 |  |  |  |

| Characteristics (1)                                                                             |             | Input high<br>voltage | $V_{\rm IH}$    | PB0 to PB7                             | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | $V_{cc} \times 0.7$ |  |  |  |

|                                                                                                 |             |                       |                 |                                        |                                          | $V_{cc} \times 0.8$ |  |  |  |

|                                                                                                 |             | Input low<br>voltage  | V <sub>IL</sub> | RXD, RXD2,<br>SCL, SDA,<br>P10 to P12, | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | -0.3                |  |  |  |

|                                                                                                 |             |                       |                 | :<br>P85 to P87,<br>PB0 to PB7         |                                          | -0.3                |  |  |  |

|                                                                                                 | 398         | Mode                  |                 | RES Pin                                | Internal Stat                            | <u> </u>            |  |  |  |

|                                                                                                 | 390         | Active mod            | e 1             | V <sub>cc</sub>                        | Operates                                 |                     |  |  |  |

|                                                                                                 |             | Active mod            | e 2             |                                        | Operates<br>(¢OSC/64)                    |                     |  |  |  |

|                                                                                                 |             | Sleep mod             | e 1             | V <sub>cc</sub>                        | Only timers o                            | perate              |  |  |  |

|                                                                                                 |             | Sleep mod             | e 2             |                                        | Only timers operate<br>(¢OSC/64)         |                     |  |  |  |