Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | H8/300H                                                                       |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20MHz                                                                         |

| Connectivity               | I²C, SCI                                                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                            |

| Number of I/O              | 45                                                                            |

| Program Memory Size        | 56KB (56K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-QFP                                                                        |

| Supplier Device Package    | -                                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f3687gdv |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

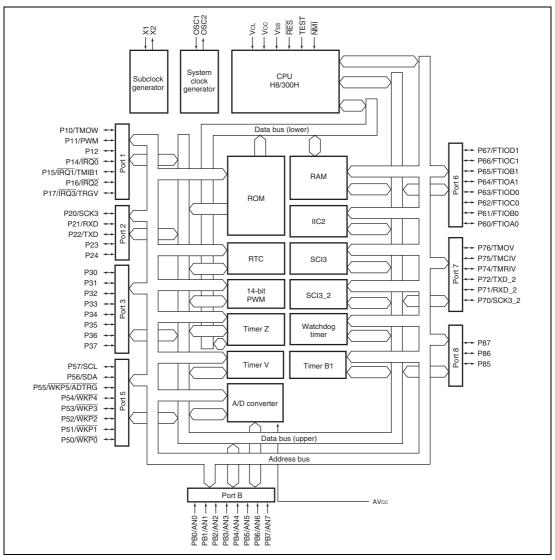

## 1.2 Internal Block Diagram

Figure 1.1 Internal Block Diagram of H8/3687 Group of F-ZTAT<sup>™</sup> and Mask-ROM Versions

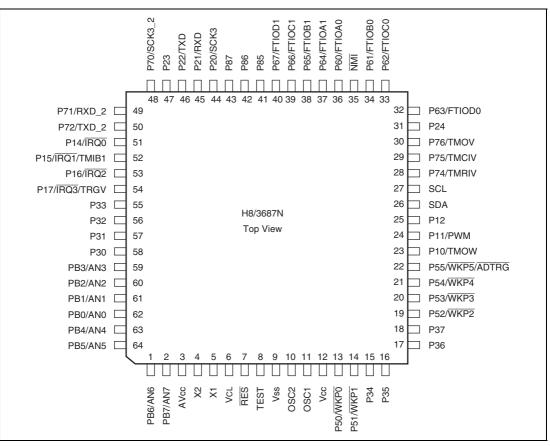

Figure 1.4 Pin Arrangement of H8/3687N (EEPROM Stacked Version) (FP-64E)

#### 2.3.2 Memory Data Formats

Figure 2.6 shows the data formats in memory. The H8/300H CPU can access word data and longword data in memory, however word or longword data must begin at an even address. If an attempt is made to access word or longword data at an odd address, an address error does not occur, however the least significant bit of the address is regarded as 0, so access begins the preceding address. This also applies to instruction fetches.

When ER7 (SP) is used as an address register to access the stack area, the operand size should be word or longword.

| Data Type     | Address                                                        | Data Format   |

|---------------|----------------------------------------------------------------|---------------|

|               | 7                                                              | 0             |

| 1-bit data    | Address L 7                                                    | 6 5 4 3 2 1 0 |

| Byte data     | Address L MSI                                                  | B LSB         |

| Word data     | Address 2M MSR<br>Address 2M+1                                 | B LSB         |

| Longword data | Address 2N MSI<br>Address 2N+1<br>Address 2N+2<br>Address 2N+3 | B LSB         |

|               |                                                                |               |

Figure 2.6 Memory Data Formats

| Instructio   | on Size*                                             | Function                                                                                                                                                                                                                                                                                                        |

|--------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD<br>SUB   | B/W/L                                                | $Rd \pm Rs \rightarrow Rd$ , $Rd \pm \#IMM \rightarrow Rd$<br>Performs addition or subtraction on data in two general registers, or on<br>immediate data and data in a general register (immediate byte data<br>cannot be subtracted from byte data in a general register. Use the<br>SUBX or ADD instruction.) |

| ADDX<br>SUBX | В                                                    | $\begin{array}{ll} Rd \pm Rs \pm C \rightarrow Rd, & Rd \pm \#IMM \pm C \rightarrow Rd \\ Performs \ addition \ or \ subtraction \ with \ carry \ on \ byte \ data \ in \ two \ general \\ registers, \ or \ on \ immediate \ data \ and \ data \ in \ a \ general \ register. \end{array}$                     |

| INC<br>DEC   | B/W/L                                                | $Rd \pm 1 \rightarrow Rd$ , $Rd \pm 2 \rightarrow Rd$<br>Increments or decrements a general register by 1 or 2. (Byte operands<br>can be incremented or decremented by 1 only.)                                                                                                                                 |

| ADDS<br>SUBS | L                                                    | $\begin{array}{ll} Rd\pm 1 \rightarrow Rd, & Rd\pm 2 \rightarrow Rd, & Rd\pm 4 \rightarrow Rd \\ \mbox{Adds or subtracts the value 1, 2, or 4 to or from data in a 32-bit register.} \end{array}$                                                                                                               |

| DAA<br>DAS   | В                                                    | Rd (decimal adjust) $\rightarrow$ Rd<br>Decimal-adjusts an addition or subtraction result in a general register by<br>referring to the CCR to produce 4-bit BCD data.                                                                                                                                           |

| MULXU        | B/W                                                  | $\begin{array}{l} \text{Rd}\times\text{Rs}\rightarrow\text{Rd}\\ \text{Performs unsigned multiplication on data in two general registers: either}\\ 8 \text{ bits}\times8 \text{ bits}\rightarrow16 \text{ bits or } 16 \text{ bits}\times16 \text{ bits}\rightarrow32 \text{ bits.} \end{array}$               |

| MULXS        | B/W                                                  | $\begin{array}{l} Rd\timesRs\toRd\\ Performs \text{ signed multiplication on data in two general registers: either 8}\\ bits\times8 \ bits\to16 \ bits \ or \ 16 \ bits\times16 \ bits\to32 \ bits. \end{array}$                                                                                                |

| DIVXU        | B/W                                                  | Rd $\div$ Rs $\rightarrow$ Rd<br>Performs unsigned division on data in two general registers: either 16<br>bits $\div$ 8 bits $\rightarrow$ 8-bit quotient and 8-bit remainder or 32 bits $\div$ 16 bits $\rightarrow$<br>16-bit quotient and 16-bit remainder.                                                 |

| Note: *      | efers to the op<br>B: Byte<br>W: Word<br>L: Longword | perand size.                                                                                                                                                                                                                                                                                                    |

## Table 2.3 Arithmetic Operations Instructions (1)

### 9.4.2 Port Control Register 5 (PCR5)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                |

|-----|----------|------------------|-----|--------------------------------------------------------------------------------------------|

| 7   | PCR57    | 0                | W   | When each of the port 5 pins P57 to P50 functions as a                                     |

| 6   | PCR56    | 0                | W   | general I/O port, setting a PCR5 bit to 1 makes the                                        |

| 5   | PCR55    | 0                | W   | corresponding pin an output port, while clearing the bit to 0 makes the pin an input port. |

| 4   | PCR54    | 0                | W   | Note: The PCR57 and PCR56 bits should not be set to 1                                      |

| 3   | PCR53    | 0                | W   | in the H8/3687N.                                                                           |

| 2   | PCR52    | 0                | W   |                                                                                            |

| 1   | PCR51    | 0                | W   |                                                                                            |

| 0   | PCR50    | 0                | W   |                                                                                            |

PCR5 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 5.

### 9.4.3 Port Data Register 5 (PDR5)

PDR5 is a general I/O port data register of port 5.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                          |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------|

| 7   | P57      | 0                | R/W | Stores output data for port 5 pins.                                                                                  |

| 6   | P56      | 0                | R/W | If PDR5 is read while PCR5 bits are set to 1, the value                                                              |

| 5   | P55      | 0                | R/W | stored in PDR5 are read. If PDR5 is read while PCR5 bits are cleared to 0, the pin states are read regardless of the |

| 4   | P54      | 0                | R/W | value stored in PDR5.                                                                                                |

| 3   | P53      | 0                | R/W | Note: The P57 and P56 bits should not be set to 1 in the                                                             |

| 2   | P52      | 0                | R/W | H8/3687N.                                                                                                            |

| 1   | P51      | 0                | R/W |                                                                                                                      |

| 0   | P50      | 0                | R/W |                                                                                                                      |

## P64/FTIOA1 pin

| Register      | TOER | TFCR            | TIORA1          | PCR6  |                            |

|---------------|------|-----------------|-----------------|-------|----------------------------|

| Bit Name      | EB1  | CMD1 to<br>CMD0 | IOA2 to<br>IOA0 | PCR64 | Pin Function               |

| Setting Value | 1    | XX              | 000 or          | 0     | P64 input/FTIOA1 input pin |

|               |      |                 | 1XX             | 1     | P64 output pin             |

|               | 0    | 00              | 001 or<br>01X   | Х     | FTIOA1 output pin          |

Legend: X: Don't care.

### P63/FTIOD0 pin

| Register      | TOER | TFCR            | TPMR  | TIORC0          | PCR6  |                            |

|---------------|------|-----------------|-------|-----------------|-------|----------------------------|

| Bit Name      | ED0  | CMD1 to<br>CMD0 | PWMD0 | IOD2 to<br>IOD0 | PCR63 | Pin Function               |

| Setting Value | 1    | 00              | 0     | 000 or<br>1XX   | 0     | P63 input/FTIOD0 input pin |

|               |      |                 |       |                 | 1     | P63 output pin             |

|               | 0    | 00              | 0     | 001 or<br>01X   | Х     | FTIOD0 output pin          |

|               |      |                 | 1     | XXX             | _     |                            |

|               |      | Other than 00   | Х     | XXX             | _     |                            |

Legend: X: Don't care.

# Section 12 Timer V

Timer V is an 8-bit timer based on an 8-bit counter. Timer V counts external events. Comparematch signals with two registers can also be used to reset the counter, request an interrupt, or output a pulse signal with an arbitrary duty cycle. Counting can be initiated by a trigger input at the TRGV pin, enabling pulse output control to be synchronized to the trigger, with an arbitrary delay from the trigger input. Figure 12.1 shows a block diagram of timer V.

## 12.1 Features

- Choice of seven clock signals is available.

Choice of six internal clock sources (φ/128, φ/64, φ/32, φ/16, φ/8, φ/4) or an external clock.

- Counter can be cleared by compare match A or B, or by an external reset signal. If the count stop function is selected, the counter can be halted when cleared.

- Timer output is controlled by two independent compare match signals, enabling pulse output with an arbitrary duty cycle, PWM output, and other applications.

- Three interrupt sources: compare match A, compare match B, timer overflow

- Counting can be initiated by trigger input at the TRGV pin. The rising edge, falling edge, or both edges of the TRGV input can be selected.

### 12.3.4 Timer Control/Status Register V (TCSRV)

TCSRV indicates the status flag and controls outputs by using a compare match.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                  |  |  |  |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------------|--|--|--|

| 7   | CMFB     | 0                | R/W | Compare Match Flag B                                                                         |  |  |  |

|     |          |                  |     | Setting condition:                                                                           |  |  |  |

|     |          |                  |     | When the TCNTV value matches the TCORB value                                                 |  |  |  |

|     |          |                  |     | Clearing condition:                                                                          |  |  |  |

|     |          |                  |     | After reading CMFB = 1, cleared by writing 0 to CMFB                                         |  |  |  |

| 6   | CMFA     | 0                | R/W | Compare Match Flag A                                                                         |  |  |  |

|     |          |                  |     | Setting condition:                                                                           |  |  |  |

|     |          |                  |     | When the TCNTV value matches the TCORA value                                                 |  |  |  |

|     |          |                  |     | Clearing condition:                                                                          |  |  |  |

|     |          |                  |     | After reading $CMFA = 1$ , cleared by writing 0 to $CMFA$                                    |  |  |  |

| 5   | OVF      | 0                | R/W | Timer Overflow Flag                                                                          |  |  |  |

|     |          |                  |     | Setting condition:                                                                           |  |  |  |

|     |          |                  |     | When TCNTV overflows from H'FF to H'00                                                       |  |  |  |

|     |          |                  |     | Clearing condition:                                                                          |  |  |  |

|     |          |                  |     | After reading OVF = 1, cleared by writing 0 to OVF                                           |  |  |  |

| 4   | —        | 1                | —   | Reserved                                                                                     |  |  |  |

|     |          |                  |     | This bit is always read as 1.                                                                |  |  |  |

| 3   | OS3      | 0                | R/W | Output Select 3 and 2                                                                        |  |  |  |

| 2   | OS2      | 0                | R/W | These bits select an output method for the TMOV pin by the compare match of TCORB and TCNTV. |  |  |  |

|     |          |                  |     | 00: No change                                                                                |  |  |  |

|     |          |                  |     | 01: 0 output                                                                                 |  |  |  |

|     |          |                  |     | 10: 1 output                                                                                 |  |  |  |

|     |          |                  |     | 11: Output toggles                                                                           |  |  |  |

| 1   | OS1      | 0                | R/W | Output Select 1 and 0                                                                        |  |  |  |

| 0   | OS0      | 0                | R/W | These bits select an output method for the TMOV pin by the compare match of TCORA and TCNTV. |  |  |  |

|     |          |                  |     | 00: No change                                                                                |  |  |  |

|     |          |                  |     | 01: 0 output                                                                                 |  |  |  |

|     |          |                  |     | 10: 1 output                                                                                 |  |  |  |

|     |          |                  |     | 11: Output toggles                                                                           |  |  |  |

### 13.4.7 Complementary PWM Mode

Three PWM waveforms for non-overlapped normal and counter phases are output by combining channels 0 and 1.

In complementary PWM mode, the FTIOB0 to FTIOD0 and FTIOA1 to FTIOD1 pins become PWM-output pins automatically. TCNT\_0 and TCNT\_1 perform an increment or decrement operation. Tables 13.6 and 13.7 show the output pins and register settings in complementary PWM mode, respectively.

Figure 13.29 shows the example of complementary PWM mode setting procedure.

| Channel | Pin Name | Input/Output | Pin Function                                                               |

|---------|----------|--------------|----------------------------------------------------------------------------|

| 0       | FTIOC0   | Output       | Toggle output in synchronous with PWM cycle                                |

| 0       | FTIOB0   | Output       | PWM output 1                                                               |

| 0       | FTIOD0   | Output       | PWM output 1 (counter-phase waveform non-<br>overlapped with PWM output 1) |

| 1       | FTIOA1   | Output       | PWM output 2                                                               |

| 1       | FTIOC1   | Output       | PWM output 2 (counter-phase waveform non-<br>overlapped with PWM output 2) |

| 1       | FTIOB1   | Output       | PWM output 3                                                               |

| 1       | FTIOD1   | Output       | PWM output 3 (counter-phase waveform non-<br>overlapped with PWM output 3) |

Table 13.6

Output Pins in Complementary PWM Mode

#### Table 13.7 Register Settings in Complementary PWM Mode

| Register | Description                                                                                    |

|----------|------------------------------------------------------------------------------------------------|

| TCNT_0   | Initial setting of non-overlapped periods (non-overlapped periods are differences with TCNT_1) |

| TCNT_1   | Initial setting of H'0000                                                                      |

| GRA_0    | Sets (upper limit value – 1) of TCNT_0                                                         |

| GRB_0    | Set a changing point of the PWM waveform output from pins FTIOB0 and FTIOD0.                   |

| GRA_1    | Set a changing point of the PWM waveform output from pins FTIOA1 and FTIOC1.                   |

| GRB_1    | Set a changing point of the PWM waveform output from pins FTIOB1 and FTIOD1.                   |

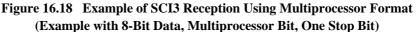

#### 16.8.4 Receive Data Sampling Timing and Reception Margin in Asynchronous Mode

In asynchronous mode, the SCI3 operates on a basic clock with a frequency of 16 times the transfer rate. In reception, the SCI3 samples the falling edge of the start bit using the basic clock, and performs internal synchronization. Receive data is latched internally at the rising edge of the 8th pulse of the basic clock as shown in figure 16.19. Thus, the reception margin in asynchronous mode is given by formula (1) below.

$$M = \left\{ (0.5 - \frac{1}{2N}) - \frac{D - 0.5}{N} - (L - 0.5) F \right\} \times 100(\%)$$

... Formula (1)

Legend N : Ratio of bit rate to clock (N = 16)

- D : Clock duty (D = 0.5 to 1.0)

- L : Frame length (L = 9 to 12)

- F : Absolute value of clock rate deviation

Assuming values of F (absolute value of clock rate deviation) = 0 and D (clock duty) = 0.5 in formula (1), the reception margin can be given by the formula.

$M = \{0.5 - 1/(2 \times 16)\} \times 100 \text{ [\%]} = 46.875\%$

However, this is only the computed value, and a margin of 20% to 30% should be allowed for in system design.

Figure 16.19 Receive Data Sampling Timing in Asynchronous Mode

# Section 17 I<sup>2</sup>C Bus Interface 2 (IIC2)

The I<sup>2</sup>C bus interface 2 conforms to and provides a subset of the Philips I<sup>2</sup>C bus (inter-IC bus) interface functions. The register configuration that controls the I<sup>2</sup>C bus differs partly from the Philips configuration, however.

Figure 17.1 shows a block diagram of the I<sup>2</sup>C bus interface 2.

Figure 17.2 shows an example of I/O pin connections to external circuits.

## 17.1 Features

- Selection of I<sup>2</sup>C format or clocked synchronous serial format

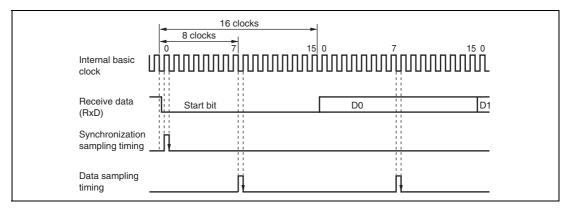

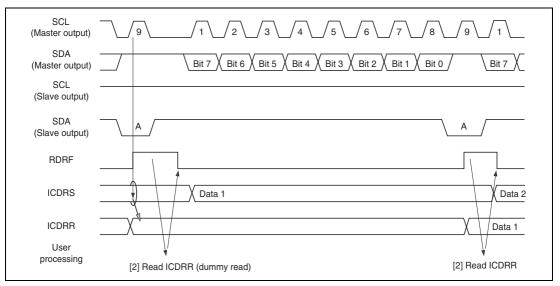

- Continuous transmission/reception

Since the shift register, transmit data register, and receive data register are independent from each other, the continuous transmission/reception can be performed.

I<sup>2</sup>C bus format

- Start and stop conditions generated automatically in master mode

- Selection of acknowledge output levels when receiving

- Automatic loading of acknowledge bit when transmitting

- Bit synchronization/wait function

In master mode, the state of SCL is monitored per bit, and the timing is synchronized automatically.

If transmission/reception is not yet possible, set the SCL to low until preparations are completed.

• Six interrupt sources

Transmit data empty (including slave-address match), transmit end, receive data full (including slave-address match), arbitration lost, NACK detection, and stop condition detection

• Direct bus drive

Two pins, SCL and SDA pins, function as NMOS open-drain outputs when the bus drive function is selected.

Clocked synchronous format

• Four interrupt sources

Transmit-data-empty, transmit-end, receive-data-full, and overrun error

- 3. Read ICDRR every time RDRF is set. If 8th receive clock pulse falls while RDRF is 1, SCL is fixed low until ICDRR is read. The change of the acknowledge before reading ICDRR, to be returned to the master device, is reflected to the next transmit frame.

- 4. The last byte data is read by reading ICDRR.

Figure 17.11 Slave Receive Mode Operation Timing (1)

# Section 20 Power-On Reset and Low-Voltage Detection Circuits (Optional)

This LSI can include a power-on reset circuit and low-voltage detection circuit as optional circuits.

The low-voltage detection circuit consists of two circuits: LVDI (interrupt by low voltage detect) and LVDR (reset by low voltage detect) circuits.

This circuit is used to prevent abnormal operation (runaway execution) from occurring due to the power supply voltage fall and to recreate the state before the power supply voltage fall when the power supply voltage rises again.

Even if the power supply voltage falls, the unstable state when the power supply voltage falls below the guaranteed operating voltage can be removed by entering standby mode when exceeding the guaranteed operating voltage and during normal operation. Thus, system stability can be improved. If the power supply voltage falls more, the reset state is automatically entered. If the power supply voltage rises again, the reset state is held for a specified period, then active mode is automatically entered.

Figure 20.1 is a block diagram of the power-on reset circuit and the low-voltage detection circuit.

## 20.1 Features

• Power-on reset circuit

Uses an external capacitor to generate an internal reset signal when power is first supplied.

• Low-voltage detection circuit

LVDR: Monitors the power-supply voltage, and generates an internal reset signal when the voltage falls below a specified value.

LVDI: Monitors the power-supply voltage, and generates an interrupt when the voltage falls below or rises above respective specified values.

Two pairs of detection levels for reset generation voltage are available: when only the LVDR circuit is used, or when the LVDI and LVDR circuits are both used.

```

LVI0000A_000020030300

```

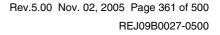

# Section 21 Power Supply Circuit

This LSI incorporates an internal power supply step-down circuit. Use of this circuit enables the internal power supply to be fixed at a constant level of approximately 3.0 V, independently of the voltage of the power supply connected to the external  $V_{cc}$  pin. As a result, the current consumed when an external power supply is used at 3.0 V or above can be held down to virtually the same low level as when used at approximately 3.0 V. If the external power supply is 3.0 V or below, the internal voltage will be practically the same as the external voltage. It is, of course, also possible to use the same level of external power supply voltage and internal power supply voltage without using the internal power supply step-down circuit.

## 21.1 When Using Internal Power Supply Step-Down Circuit

Connect the external power supply to the  $V_{cc}$  pin, and connect a capacitance of approximately 0.1  $\mu$ F between  $V_{cc}$  and  $V_{ss}$ , as shown in figure 21.1. The internal step-down circuit is made effective simply by adding this external circuit. In the external circuit interface, the external power supply voltage connected to  $V_{cc}$  and the GND potential connected to  $V_{ss}$  are the reference levels. For example, for port input/output levels, the  $V_{cc}$  level is the reference for the high level, and the  $V_{ss}$  level is that for the low level. The A/D converter analog power supply is not affected by the internal step-down circuit.

Figure 21.1 Power Supply Connection when Internal Step-Down Circuit is Used

| Register                         | Abbre-<br>viation | Bit No | Address                | Module<br>Name    | Data<br>Bus<br>Width | Access<br>State |

|----------------------------------|-------------------|--------|------------------------|-------------------|----------------------|-----------------|

| Timer control/status register WD | TCSRW<br>D        | 8      | H'FFC0                 | WDT* <sup>2</sup> | 8                    | 2               |

| Timer counter WD                 | TCWD              | 8      | H'FFC1                 | WDT* <sup>2</sup> | 8                    | 2               |

| Timer mode register WD           | TMWD              | 8      | H'FFC2                 | WDT* <sup>2</sup> | 8                    | 2               |

|                                  | _                 |        | H'FFC3                 | WDT* <sup>2</sup> | _                    | _               |

| _                                | _                 | -      | H'FFC4<br>to<br>H'FFC7 | _                 |                      | _               |

| Address break control register   | ABRKCR            | 8      | H'FFC8                 | Address<br>break  | 8                    | 2               |

| Address break status register    | ABRKSR            | 8      | H'FFC9                 | Address<br>break  | 8                    | 2               |

| Break address register H         | BARH              | 8      | H'FFCA                 | Address<br>break  | 8                    | 2               |

| Break address register L         | BARL              | 8      | H'FFCB                 | Address<br>break  | 8                    | 2               |

| Break data register H            | BDRH              | 8      | H'FFCC                 | Address<br>break  | 8                    | 2               |

| Break data register L            | BDRL              | 8      | H'FFCD                 | Address<br>break  | 8                    | 2               |

| Port pull-up control register 1  | PUCR1             | 8      | H'FFD0                 | I/O port          | 8                    | 2               |

| Port pull-up control register 5  | PUCR5             | 8      | H'FFD1                 | I/O port          | 8                    | 2               |

| _                                | _                 | _      | H'FFD2,<br>H'FFD3      | I/O port          | _                    | _               |

| Port data register 1             | PDR1              | 8      | H'FFD4                 | I/O port          | 8                    | 2               |

| Port data register 2             | PDR2              | 8      | H'FFD5                 | I/O port          | 8                    | 2               |

| Port data register 3             | PDR3              | 8      | H'FFD6                 | I/O port          | 8                    | 2               |

|                                  | _                 | _      | H'FFD7                 | I/O port          |                      | _               |

| Port data register 5             | PDR5              | 8      | H'FFD8                 | I/O port          | 8                    | 2               |

| Port data register 6             | PDR6              | 8      | H'FFD9                 | I/O port          | 8                    | 2               |

| Port data register 7             | PDR7              | 8      | H'FFDA                 | I/O port          | 8                    | 2               |

| Port data register 8             | PDR8              | 8      | H'FFDB                 | I/O port          | 8                    | 2               |

|                                  |                   | —      | H'FFDC                 | I/O port          | —                    |                 |

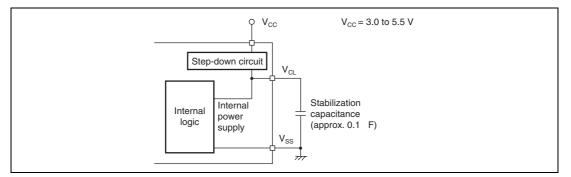

Figure 23.2 RES Low Width Timing

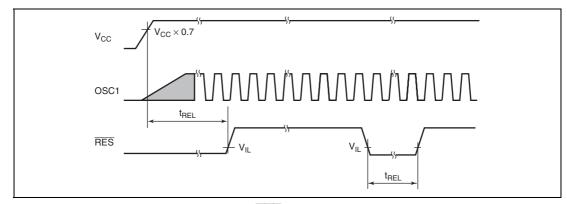

Figure 23.3 Input Timing

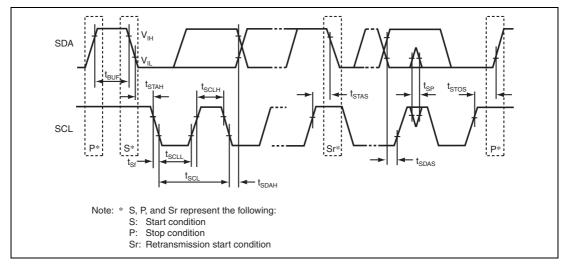

Figure 23.4 I<sup>2</sup>C Bus Interface Input/Output Timing

| Instruction | Mnemonic          | Instruction<br>Fetch<br>I | Branch<br>Addr. Read<br>J | Stack<br>Operation<br>K | Byte Data<br>Access<br>L | Word Data<br>Access<br>M | Internal<br>Operation<br>N |

|-------------|-------------------|---------------------------|---------------------------|-------------------------|--------------------------|--------------------------|----------------------------|

| SUBX        | SUBX #xx:8, Rd    | 1                         |                           |                         |                          |                          |                            |

|             | SUBX. Rs, Rd      | 1                         |                           |                         |                          |                          |                            |

| TRAPA       | TRAPA #xx:2       | 2                         | 1                         | 2                       |                          |                          | 4                          |

| XOR         | XOR.B #xx:8, Rd   | 1                         |                           |                         |                          |                          |                            |

|             | XOR.B Rs, Rd      | 1                         |                           |                         |                          |                          |                            |

|             | XOR.W #xx:16, Rd  | 2                         |                           |                         |                          |                          |                            |

|             | XOR.W Rs, Rd      | 1                         |                           |                         |                          |                          |                            |

|             | XOR.L #xx:32, ERd | 3                         |                           |                         |                          |                          |                            |

|             | XOR.L ERs, ERd    | 2                         |                           |                         |                          |                          |                            |

| XORC        | XORC #xx:8, CCR   | 1                         |                           |                         |                          |                          |                            |

Notes: 1. n: Specified value in R4L and R4. The source and destination operands are accessed n+1 times respectively.

2. Cannot be used in this LSI.

## Renesas 16-Bit Single-Chip Microcomputer Hardware Manual H8/3687 Group

| Publication Date: | 1st Edition, Jul, 2001              |

|-------------------|-------------------------------------|

|                   | Rev.5.00, Nov. 02, 2005             |

| Published by:     | Sales Strategic Planning Div.       |

|                   | Renesas Technology Corp.            |

| Edited by:        | Customer Support Department         |

|                   | Global Strategic Communication Div. |

|                   | Renesas Solutions Corp.             |

|                   |                                     |