Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | H8/300H                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20MHz                                                                           |

| Connectivity               | I²C, SCI                                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 45                                                                              |

| Program Memory Size        | 56KB (56K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LFQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f3687gfpiv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Bit manipulation for two registers assigned to the same address

#### Example 1: Bit manipulation for the timer load register and timer counter

#### (Applicable for timer B1 in the H8/3687 Group.)

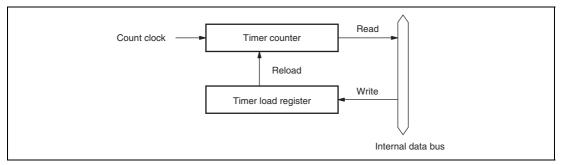

Figure 2.13 shows an example of a timer in which two timer registers are assigned to the same address. When a bit-manipulation instruction accesses the timer load register and timer counter of a reloadable timer, since these two registers share the same address, the following operations takes place.

- 1. Data is read in byte units.

- 2. The CPU sets or resets the bit to be manipulated with the bit-manipulation instruction.

- 3. The written data is written again in byte units to the timer load register.

The timer is counting, so the value read is not necessarily the same as the value in the timer load register. As a result, bits other than the intended bit in the timer counter may be modified and the modified value may be written to the timer load register.

Figure 2.13 Example of Timer Configuration with Two Registers Allocated to Same Address

#### Example 2: The BSET instruction is executed for port 5.

P57 and P56 are input pins, with a low-level signal input at P57 and a high-level signal input at P56. P55 to P50 are output pins and output low-level signals. An example to output a high-level signal at P50 with a BSET instruction is shown below.

When an address break is set in the data read cycle or data write cycle, the data bus used will depend on the combination of the byte/word access and address. Table 4.1 shows the access and data bus used. When an I/O register space with an 8-bit data bus width is accessed in word size, a byte access is generated twice. For details on data widths of each register, see section 22.1, Register Addresses (Address Order).

|                                         | Word         | Access       | Byte Access  |               |  |  |

|-----------------------------------------|--------------|--------------|--------------|---------------|--|--|

|                                         | Even Address | Odd Address  | Even Address | s Odd Address |  |  |

| ROM space                               | Upper 8 bits | Lower 8 bits | Upper 8 bits | Upper 8 bits  |  |  |

| RAM space                               | Upper 8 bits | Lower 8 bits | Upper 8 bits | Upper 8 bits  |  |  |

| I/O register with 8-bit data bus width  | Upper 8 bits | Upper 8 bits | Upper 8 bits | Upper 8 bits  |  |  |

| I/O register with 16-bit data bus width | Upper 8 bits | Lower 8 bits | _            |               |  |  |

#### Table 4.1 Access and Data Bus Used

#### 4.1.2 Address Break Status Register (ABRKSR)

ABRKSR consists of the address break interrupt flag and the address break interrupt enable bit.

|            |      | Value | R/W | Description                                                        |

|------------|------|-------|-----|--------------------------------------------------------------------|

| 7 Δ        | ABIF | -     |     |                                                                    |

| <i>'</i> 7 |      | 0     | R/W | Address Break Interrupt Flag                                       |

|            |      |       |     | [Setting condition]                                                |

|            |      |       |     | When the condition set in ABRKCR is satisfied                      |

|            |      |       |     | [Clearing condition]                                               |

|            |      |       |     | When 0 is written after ABIF=1 is read                             |

| 6 A        | ABIE | 0     | R/W | Address Break Interrupt Enable                                     |

|            |      |       |     | When this bit is 1, an address break interrupt request is enabled. |

| 5 to 0 –   |      | All 1 | _   | Reserved                                                           |

|            |      |       |     | These bits are always read as 1.                                   |

#### 4.1.3 Break Address Registers (BARH, BARL)

BARH and BARL are 16-bit read/write registers that set the address for generating an address break interrupt. When setting the address break condition to the instruction execution cycle, set the first byte address of the instruction. The initial value of this register is H'FFFF.

#### 7.2.3 Erase Block Register 1 (EBR1)

EBR1 specifies the flash memory erase area block. EBR1 is initialized to H'00 when the SWE bit in FLMCR1 is 0. Do not set more than one bit at a time, as this will cause all the bits in EBR1 to be automatically cleared to 0.

|     |          | Initial |     |                                                                          |

|-----|----------|---------|-----|--------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                              |

| 7   | —        | 0       |     | Reserved                                                                 |

|     |          |         |     | This bit is always read as 0.                                            |

| 6   | EB6      | 0       | R/W | When this bit is set to 1, 8 bytes of H'C000 to H'DFFF will be erased.   |

| 5   | EB5      | 0       | R/W | When this bit is set to 1, 16 bytes of H'8000 to H'BFFF will be erased.  |

| 4   | EB4      | 0       | R/W | When this bit is set to 1, 28 kbytes of H'1000 to H'7FFF will be erased. |

| 3   | EB3      | 0       | R/W | When this bit is set to 1, 1 kbyte of H'0C00 to H'0FFF will be erased.   |

| 2   | EB2      | 0       | R/W | When this bit is set to 1, 1 kbyte of H'0800 to H'0BFF will be erased.   |

| 1   | EB1      | 0       | R/W | When this bit is set to 1, 1 kbyte of H'0400 to H'07FF will be erased.   |

| 0   | EB0      | 0       | R/W | When this bit is set to 1, 1 kbyte of H'0000 to H'03FF will be erased.   |

|     |          |         |     |                                                                          |

- 5. For a dummy write to a verify address, write 1-byte data H'FF to an address whose lower two bits are B'00. Verify data can be read in longwords from the address to which a dummy write was performed.

- 6. If the read data is not erased successfully, set erase mode again, and repeat the erase/erase-verify sequence as before. The maximum number of repetitions of the erase/erase-verify sequence is 100.

## 7.4.3 Interrupt Handling when Programming/Erasing Flash Memory

All interrupts, including the NMI interrupt, are disabled while flash memory is being programmed or erased, or while the boot program is executing, for the following three reasons:

- 1. Interrupt during programming/erasing may cause a violation of the programming or erasing algorithm, with the result that normal operation cannot be assured.

- 2. If interrupt exception handling starts before the vector address is written or during programming/erasing, a correct vector cannot be fetched and the CPU malfunctions.

- 3. If an interrupt occurs during boot program execution, normal boot mode sequence cannot be carried out.

# 9.4.1 Port Mode Register 5 (PMR5)

PMR5 switches the functions of pins in port 5.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                            |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------|

|     |          |                  | -   |                                                                                                                        |

| 7   | POF57    | 0                | R/W | When the bit is set to 1, the corresponding pin is cut off                                                             |

| 6   | POF56    | 0                | R/W | by PMOS and it functions as the NMOS open-drain<br>output. When cleared to 0, the pin functions as the CMOS<br>output. |

| 5   | WKP5     | 0                | R/W | This bit selects the function of pin P55/WKP5/ADTRG.                                                                   |

|     |          |                  |     | 0: General I/O port                                                                                                    |

|     |          |                  |     | 1: WKP5/ADTRG input pin                                                                                                |

| 4   | WKP4     | 0                | R/W | This bit selects the function of pin P54/WKP4.                                                                         |

|     |          |                  |     | 0: General I/O port                                                                                                    |

|     |          |                  |     | 1: WKP4 input pin                                                                                                      |

| 3   | WKP3     | 0                | R/W | This bit selects the function of pin P53/WKP3.                                                                         |

|     |          |                  |     | 0: General I/O port                                                                                                    |

|     |          |                  |     | 1: WKP3 input pin                                                                                                      |

| 2   | WKP2     | 0                | R/W | This bit selects the function of pin P52/WKP2.                                                                         |

|     |          |                  |     | 0: General I/O port                                                                                                    |

|     |          |                  |     | 1: WKP2 input pin                                                                                                      |

| 1   | WKP1     | 0                | R/W | This bit selects the function of pin P51/WKP1.                                                                         |

|     |          |                  |     | 0: General I/O port                                                                                                    |

|     |          |                  |     | 1: WKP1 input pin                                                                                                      |

| 0   | WKP0     | 0                | R/W | This bit selects the function of pin P50/WKP0.                                                                         |

|     |          |                  |     | 0: General I/O port                                                                                                    |

|     |          |                  |     | 1: WKP0 input pin                                                                                                      |

|     |          |                  |     |                                                                                                                        |

| φ                    |   |   |     | - |

|----------------------|---|---|-----|---|

| TCNTV                | Ν | X | N+1 | - |

| TCORA or<br>TCORB    | Ν |   |     |   |

| Compare match signal |   |   |     |   |

| CMFA or<br>CMFB      |   |   |     | - |

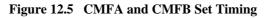

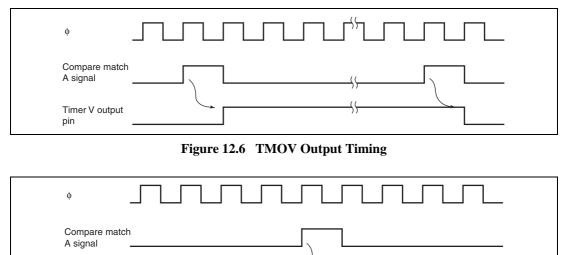

Figure 12.7 Clear Timing by Compare Match

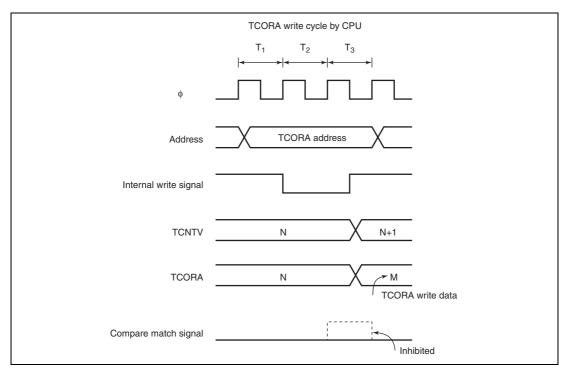

Figure 12.12 Contention between TCORA Write and Compare Match

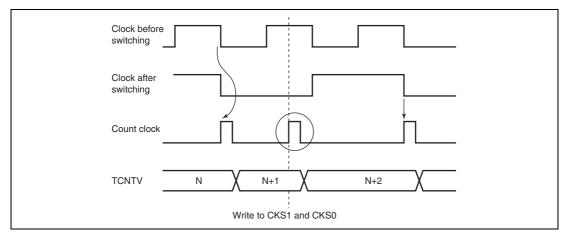

Figure 12.13 Internal Clock Switching and TCNTV Operation

# 13.3.8 General Registers A, B, C, and D (GRA, GRB, GRC, and GRD)

GR are 16-bit registers. Timer Z has eight general registers (GR), four for each channel. The GR registers are dual function 16-bit readable/writable registers, functioning as either output compare or input capture registers. Functions can be switched by TIORA and TIORC.

The values in GR and TCNT are constantly compared with each other when the GR registers are used as output compare registers. When the both values match, the IMFA to IMFD flags in TSR are set to 1. Compare match outputs can be selected by TIORA and TIORC.

When the GR registers are used as input capture registers, the TCNT value is stored after detecting external signals. At this point, IMFA to IMFD flags in the corresponding TSR are set to 1. Detection edges for input capture signals can be selected by TIORA and TIORC.

When PWM mode, complementary PWM mode, or reset synchronous PWM mode is selected, the values in TIORA and TIORC are ignored. Upon reset, the GR registers are set as output compare registers (no output) and initialized to H'FFFF. The GR registers cannot be accessed in 8-bit units; they must always be accessed as a 16-bit unit.

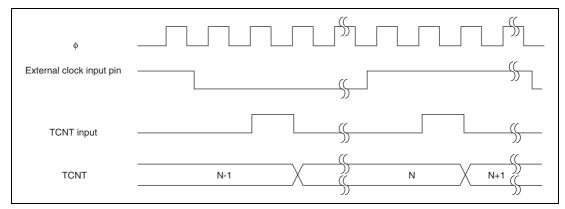

B. External clock operation

An external clock input pin (TCLK) can be selected by bits TPSC2 to TPSC0 in TCR, and a detection edge can be selected by bits CKEG1 and CKEG0. To detect an external clock, the rising edge, falling edge, or both edges can be selected. The pulse width of the external clock needs two or more system clocks. Note that an external clock does not operate correctly with the lower pulse width.

Figure 13.11 illustrates the detection timing of the rising and falling edges.

Figure 13.11 Count Timing at External Clock Operation (Both Edges Detected)

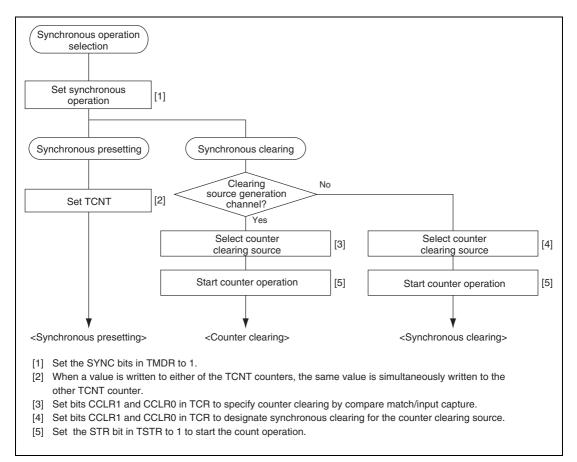

### 13.4.4 Synchronous Operation

In synchronous operation, the values in a number of TCNT counters can be rewritten simultaneously (synchronous presetting). Also, a number of TCNT counters can be cleared simultaneously by making the appropriate setting in TCR (synchronous clearing). Synchronous operation enables GR to be increased with respect to a single time base.

Figure 13.19 shows an example of the synchronous operation setting procedure.

Figure 13.19 Example of Synchronous Operation Setting Procedure

RENESAS

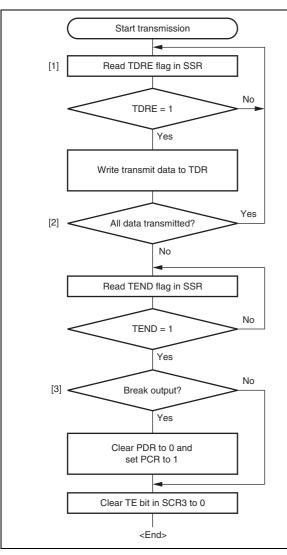

- [1] Read SSR and check that the TDRE flag is set to 1, then write transmit data to TDR. When data is written to TDR, the TDRE flag is automatically cleared to 0.

- [2] To continue serial transmission, read 1 from the TDRE flag to confirm that writing is possible, then write data to TDR. When data is written to TDR, the TDRE flag is automaticaly cleared to 0.

- [3] To output a break in serial transmission, after setting PCR to 1 and PDR to 0, clear TxD in PMR1 to 0, then clear the TE bit in SCR3 to 0.

Figure 16.6 Sample Serial Transmission Data Flowchart (Asynchronous Mode)

# 17.3.5 I<sup>2</sup>C Bus Status Register (ICSR)

ICSR performs confirmation of interrupt request flags and status.

| -   | 54.11    | Initial | -   | <b>-</b>                                                                                                              |

|-----|----------|---------|-----|-----------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                                           |

| 7   | TDRE     | 0       | R/W | Transmit Data Register Empty                                                                                          |

|     |          |         |     | [Setting conditions]                                                                                                  |

|     |          |         |     | <ul> <li>When data is transferred from ICDRT to ICDRS and<br/>ICDRT becomes empty</li> </ul>                          |

|     |          |         |     | When TRS is set                                                                                                       |

|     |          |         |     | <ul> <li>When a start condition (including re-transfer) has<br/>been issued</li> </ul>                                |

|     |          |         |     | When transmit mode is entered from receive mode in<br>slave mode                                                      |

|     |          |         |     | [Clearing conditions]                                                                                                 |

|     |          |         |     | • When 0 is written in TDRE after reading TDRE = 1                                                                    |

|     |          |         |     | When data is written to ICDRT with an instruction                                                                     |

| 6   | TEND     | 0       | R/W | Transmit End                                                                                                          |

|     |          |         |     | [Setting conditions]                                                                                                  |

|     |          |         |     | <ul> <li>When the ninth clock of SCL rises with the I<sup>2</sup>C bus<br/>format while the TDRE flag is 1</li> </ul> |

|     |          |         |     | When the final bit of transmit frame is sent with the<br>clock synchronous serial format                              |

|     |          |         |     | [Clearing conditions]                                                                                                 |

|     |          |         |     | • When 0 is written in TEND after reading TEND = 1                                                                    |

|     |          |         |     | When data is written to ICDRT with an instruction                                                                     |

| 5   | RDRF     | 0       | R/W | Receive Data Register Full                                                                                            |

|     |          |         |     | [Setting condition]                                                                                                   |

|     |          |         |     | <ul> <li>When a receive data is transferred from ICDRS to<br/>ICDRR</li> </ul>                                        |

|     |          |         |     | [Clearing conditions]                                                                                                 |

|     |          |         |     | • When 0 is written in RDRF after reading RDRF = 1                                                                    |

|     |          |         |     | When ICDRR is read with an instruction                                                                                |

| Bit | Bit Name | Initial<br>Value | R/W | Description                   |                  |  |  |  |

|-----|----------|------------------|-----|-------------------------------|------------------|--|--|--|

| 2   | CH2      | 0                | R/W | Channel Select 2 to 0         |                  |  |  |  |

| 1   | CH1      | 0                | R/W | Select analog input channels. |                  |  |  |  |

| 0   | CH0      | 0                | R/W | When SCAN = 0                 | When SCAN = 1    |  |  |  |

|     |          |                  |     | 000: AN0                      | 000: AN0         |  |  |  |

|     |          |                  |     | 001: AN1                      | 001: AN0 and AN1 |  |  |  |

|     |          |                  |     | 010: AN2                      | 010: AN0 to AN2  |  |  |  |

|     |          |                  |     | 011: AN3                      | 011: AN0 to AN3  |  |  |  |

|     |          |                  |     | 100: AN4                      | 100: AN4         |  |  |  |

|     |          |                  |     | 101: AN5                      | 101: AN4 and AN5 |  |  |  |

|     |          |                  |     | 110: AN6                      | 110: AN4 to AN6  |  |  |  |

|     |          |                  |     | 111: AN7                      | 111: AN4 to AN7  |  |  |  |

# 18.3.3 A/D Control Register (ADCR)

ADCR enables A/D conversion started by an external trigger signal.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                          |

|--------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | TRGE     | 0                | R/W | Trigger Enable                                                                                                                                                       |

|        |          |                  |     | A/D conversion is started at the falling edge and the rising edge of the external trigger signal (ADTRG) when this bit is set to 1.                                  |

|        |          |                  |     | The selection between the falling edge and rising edge of the external trigger pin (ADTRG) conforms to the WPEG5 bit in the interrupt edge select register 2 (IEGR2) |

| 6 to 1 | _        | All 1            | _   | Reserved                                                                                                                                                             |

|        |          |                  |     | These bits are always read as 1.                                                                                                                                     |

| 0      | _        | 0                | R/W | Reserved                                                                                                                                                             |

|        |          |                  |     | Do not set this bit to 1, though the bit is readable/writable.                                                                                                       |

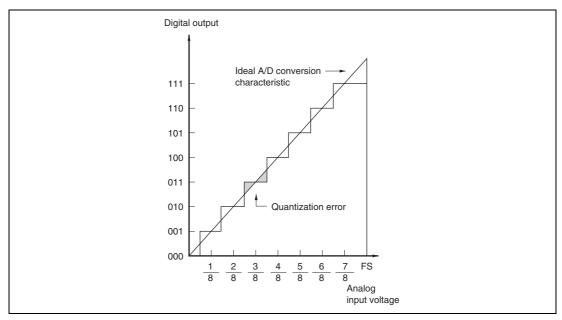

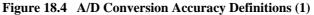

Figure 18.5 A/D Conversion Accuracy Definitions (2)

| Register<br>Name | Reset       | Active | Sleep | Subactive   | Subsleep    | Standby     | Module            |

|------------------|-------------|--------|-------|-------------|-------------|-------------|-------------------|

| TCORA            | Initialized |        | _     | Initialized | Initialized | Initialized | Timer V           |

| TCORB            | Initialized |        | —     | Initialized | Initialized | Initialized | _                 |

| TCNTV            | Initialized |        | _     | Initialized | Initialized | Initialized | _                 |

| TCRV1            | Initialized | —      | _     | Initialized | Initialized | Initialized | _                 |

| SMR              | Initialized | —      | _     | Initialized | Initialized | Initialized | SCI3              |

| BRR              | Initialized | —      | _     | Initialized | Initialized | Initialized | _                 |

| SCR3             | Initialized | —      | _     | Initialized | Initialized | Initialized | _                 |

| TDR              | Initialized | —      | _     | Initialized | Initialized | Initialized | _                 |

| SSR              | Initialized | _      | _     | Initialized | Initialized | Initialized | _                 |

| RDR              | Initialized |        | _     | Initialized | Initialized | Initialized | _                 |

| ADDRA            | Initialized |        | —     | Initialized | Initialized | Initialized | A/D converter     |

| ADDRB            | Initialized | _      | _     | Initialized | Initialized | Initialized | _                 |

| ADDRC            | Initialized | —      | _     | Initialized | Initialized | Initialized | _                 |

| ADDRD            | Initialized | —      | _     | Initialized | Initialized | Initialized | _                 |

| ADCSR            | Initialized | _      | _     | Initialized | Initialized | Initialized | _                 |

| ADCR             | Initialized |        | _     | Initialized | Initialized | Initialized | _                 |

| PWDRL            | Initialized | —      | _     | _           |             |             | 14bit PWM         |

| PWDRU            | Initialized | _      | _     | _           |             |             | _                 |

| PWCR             | Initialized | _      | _     | _           |             |             | _                 |

| TCSRWD           | Initialized | —      | —     | —           | —           | _           | WDT* <sup>2</sup> |

| TCWD             | Initialized | _      | _     |             | _           | _           | _                 |

| TMWD             | Initialized | —      | —     | —           | —           | _           | _                 |

| ABRKCR           | Initialized | —      | —     | —           |             | —           | Address break     |

| ABRKSR           | Initialized | —      | —     | —           | —           | _           | _                 |

| BARH             | Initialized |        | _     | _           |             | _           | _                 |

| BARL             | Initialized | —      | —     | —           |             | —           | _                 |

| BDRH             | Initialized | —      | —     | —           | —           | _           | _                 |

| BDRL             | Initialized | —      | —     | —           | —           | _           | _                 |

| PUCR1            | Initialized | _      | _     | _           | _           | _           | I/O port          |

| PUCR5            | Initialized | _      | _     | _           | _           | _           | _                 |

| PDR1             | Initialized | _      | _     | _           |             |             | _                 |

|                         |                  | Applicable                                                                                                                                                                            |                                                       |                 | Value | s   | <br>Unit                                | Reference<br>Figure |

|-------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|-------|-----|-----------------------------------------|---------------------|

| ltem                    | Symbol           | Pins                                                                                                                                                                                  | Test Condition                                        | Min             | Тур   | Max |                                         |                     |

| RES pin low width       | t <sub>rel</sub> | RES                                                                                                                                                                                   | At power-on and in<br>modes other than<br>those below | t <sub>rc</sub> | _     | —   | ms                                      | Figure 23.2         |

|                         |                  |                                                                                                                                                                                       | In active mode and sleep mode operation               | 200             |       | _   | ns                                      | _                   |

| Input pin high<br>width | t <sub>iH</sub>  | NMI, TMIB1,<br>IRQ0 to<br>IRQ3,<br>WKP0 to<br>WKP5,<br>TMCIV,<br>TMRIV,<br>TRGV,<br>ADTRG,<br>FTIOA0 to<br>FTIOD0,<br>FTIOA1 to<br>FTIOD1                                             |                                                       | 2               | _     | _   | t <sub>cyc</sub><br>t <sub>subcyc</sub> | Figure 23.3         |

| Input pin low<br>width  | t,L              | NMI, TMIB1,         IRQ0 to         IRQ3,         WKP0 to         WKP5,         TMCIV,         TMRIV,         TRGV,         ADTRG,         FTIOA0 to         FTIOA1 to         FTIOD1 |                                                       | 2               | _     | _   | t <sub>cyc</sub><br>t <sub>subcyc</sub> | _                   |

Notes: 1. When an external clock is input, the minimum system clock oscillation frequency is 1.0 MHz.

2. Determined by MA2, MA1, MA0, SA1, and SA0 of system control register 2 (SYSCR2).

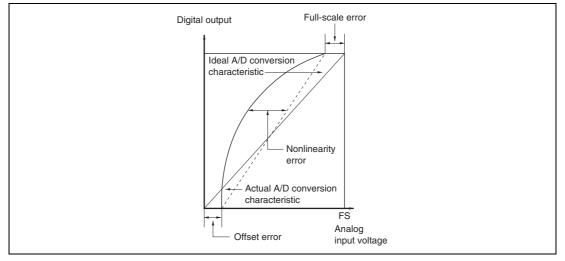

Figure B.5 Port 2 Block Diagram (P11)

# H8/3687Group Hardware Manual

Renesas Electronics Corporation 1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan

REJ09B0027-0500