#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             |                                                                                 |

| Core Size                  |                                                                                 |

| Speed                      |                                                                                 |

| Connectivity               | -                                                                               |

| Peripherals                | -                                                                               |

| Number of I/O              | -                                                                               |

| Program Memory Size        | -                                                                               |

| Program Memory Type        | -                                                                               |

| EEPROM Size                | -                                                                               |

| RAM Size                   | -                                                                               |

| Voltage - Supply (Vcc/Vdd) |                                                                                 |

| Data Converters            |                                                                                 |

| Oscillator Type            |                                                                                 |

| Operating Temperature      |                                                                                 |

| Mounting Type              | -                                                                               |

| Package / Case             | -                                                                               |

| Supplier Device Package    | -                                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f3687gfzkv |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### On-chip memory

|                                             |                            |          |                     | Model                                                                         |           |          |         |

|---------------------------------------------|----------------------------|----------|---------------------|-------------------------------------------------------------------------------|-----------|----------|---------|

| Product Clas                                | ssification                |          | Standard<br>Version | On-Chip Power-<br>On Reset and<br>Low-Voltage<br>Detecting Circuit<br>Version | ROM       | RAM      | Remarks |

| Flash memor                                 | -                          | H8/3687F | HD64F3687           | HD64F3687G                                                                    | 56 kbytes | 4 kbytes |         |

| (F-ZTAT <sup>™</sup> ve                     | rsion)                     | H8/3684F | HD64F3684           | HD64F3684G                                                                    | 32 kbytes | 4 kbytes |         |

| Mask-ROM v                                  | ersion                     | H8/3687  | HD6433687           | HD6433687G                                                                    | 56 kbytes | 3 kbytes |         |

|                                             |                            | H8/3686  | HD6433686           | HD6433686G                                                                    | 48 kbytes | 3 kbytes |         |

|                                             |                            | H8/3685  | HD6433685           | HD6433685G                                                                    | 40 kbytes | 3 kbytes |         |

|                                             |                            | H8/3684  | HD6433684           | HD6433684G                                                                    | 32 kbytes | 3 kbytes |         |

|                                             |                            | H8/3683  | HD6433683           | HD6433683G                                                                    | 24 kbytes | 3 kbytes |         |

|                                             |                            |          | HD6433682           | HD6433682G                                                                    | 16 kbytes | 3 kbytes |         |

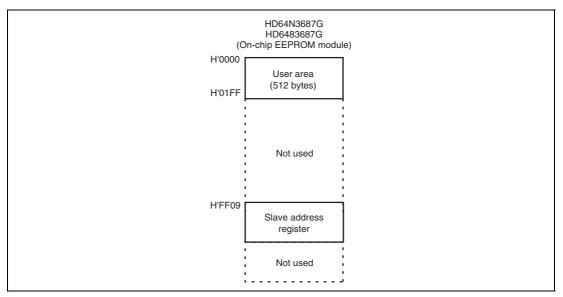

| EEPROM<br>stacked<br>version<br>(512 bytes) | Flash<br>memory<br>version | H8/3687N | —                   | HD64N3687G                                                                    | 56 kbytes | 4 kbytes |         |

|                                             | Mask-ROM version           | -        | _                   | HD6483687G                                                                    | 56 kbytes | 3 kbytes |         |

- General I/O ports

- I/O pins: 45 I/O pins (43 I/O pins for H8/3687N), including 8 large current ports (I $_{oL}$  = 20 mA, @V $_{oL}$  = 1.5 V)

- Input-only pins: 8 input pins (also used for analog input)

- EEPROM interface (only for H8/3687N)

- I<sup>2</sup>C bus interface (conforms to the I<sup>2</sup>C bus interface format that is advocated by Philips Electronics)

- Supports various power-down states

Note: F-ZTAT<sup>™</sup> is a trademark of Renesas Technology Corp.

Compact package

| Package | Code   | Body Size        | Pin Pitch |  |  |  |  |

|---------|--------|------------------|-----------|--|--|--|--|

| LQFP-64 | FP-64E | 10.0	imes10.0 mm | 0.5 mm    |  |  |  |  |

| QFP-64  | FP-64A | 14.0	imes14.0 mm | 0.8 mm    |  |  |  |  |

|         |        |                  |           |  |  |  |  |

Only LQFP-64 (FP-64E) for H8/3687N package

Figure 2.1 Memory Map (3)

# 2.5 Addressing Modes and Effective Address Calculation

The following describes the H8/300H CPU. In this LSI, the upper eight bits are ignored in the generated 24-bit address, so the effective address is 16 bits.

# 2.5.1 Addressing Modes

The H8/300H CPU supports the eight addressing modes listed in table 2.10. Each instruction uses a subset of these addressing modes. Addressing modes that can be used differ depending on the instruction. For details, refer to appendix A.4, Combinations of Instructions and Addressing Modes.

Arithmetic and logic instructions can use the register direct and immediate modes. Data transfer instructions can use all addressing modes except program-counter relative and memory indirect. Bit-manipulation instructions use register direct, register indirect, or the absolute addressing mode (@aa:8) to specify an operand, and register direct (BSET, BCLR, BNOT, and BTST instructions) or immediate (3-bit) addressing mode to specify a bit number in the operand.

| No. | Addressing Mode                                                               | Symbol                  |

|-----|-------------------------------------------------------------------------------|-------------------------|

| 1   | Register direct                                                               | Rn                      |

| 2   | Register indirect                                                             | @ERn                    |

| 3   | Register indirect with displacement                                           | @(d:16,ERn)/@(d:24,ERn) |

| 4   | Register indirect with post-increment<br>Register indirect with pre-decrement | @ERn+<br>@-ERn          |

| 5   | Absolute address                                                              | @aa:8/@aa:16/@aa:24     |

| 6   | Immediate                                                                     | #xx:8/#xx:16/#xx:32     |

| 7   | Program-counter relative                                                      | @(d:8,PC)/@(d:16,PC)    |

| 8   | Memory indirect                                                               | @ @ aa:8                |

#### Table 2.10 Addressing Modes

# Register Direct—Rn

The register field of the instruction specifies an 8-, 16-, or 32-bit general register containing the operand. R0H to R7H and R0L to R7L can be specified as 8-bit registers. R0 to R7 and E0 to E7 can be specified as 16-bit registers. ER0 to ER7 can be specified as 32-bit registers.

### 3.2.4 Interrupt Enable Register 2 (IENR2)

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                  |

|--------|----------|------------------|-----|--------------------------------------------------------------------------------------------------------------|

| 7, 6   | _        | All 0            | _   | Reserved                                                                                                     |

|        |          |                  |     | These bits are always read as 0.                                                                             |

| 5      | IENTB1   | 0                | R/W | Timer B1 Interrupt Enable<br>When this bit is set to 1, timer B1 overflow interrupt<br>requests are enabled. |

| 4 to 0 |          | All 1            | _   | Reserved                                                                                                     |

|        |          |                  |     | These bits are always read as 1.                                                                             |

IENR2 enables, timer B1 overflow interrupts.

When disabling interrupts by clearing bits in an interrupt enable register, or when clearing bits in an interrupt flag register, always do so while interrupts are masked (I = 1). If the above clear operations are performed while I = 0, and as a result a conflict arises between the clear instruction and an interrupt request, exception handling for the interrupt will be executed after the clear instruction has been executed.

# 3.2.5 Interrupt Flag Register 1 (IRR1)

IRR1 is a status flag register for direct transition interrupts, RTC interrupts, and  $\overline{IRQ3}$  to  $\overline{IRQ0}$  interrupt requests.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                       |

|-----|----------|------------------|-----|---------------------------------------------------------------------------------------------------|

| 7   | IRRDT    | 0                | R/W | Direct Transfer Interrupt Request Flag                                                            |

|     |          |                  |     | [Setting condition]                                                                               |

|     |          |                  |     | When a direct transfer is made by executing a SLEEP instruction while DTON in SYSCR2 is set to 1. |

|     |          |                  |     | [Clearing condition]                                                                              |

|     |          |                  |     | When IRRDT is cleared by writing 0                                                                |

| 6   | IRRTA    | 0                | R/W | RTC Interrupt Request Flag                                                                        |

|     |          |                  |     | [Setting condition]                                                                               |

|     |          |                  |     | When the RTC counter value overflows                                                              |

|     |          |                  |     | [Clearing condition]                                                                              |

|     |          |                  |     | When IRRTA is cleared by writing 0                                                                |

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                                 |

|------|----------|------------------|-----|---------------------------------------------------------------------------------------------|

| 5, 4 |          | All 1            | _   | Reserved                                                                                    |

|      |          |                  |     | These bits are always read as 1.                                                            |

| 3    | IRRI3    | 0                | R/W | IRQ3 Interrupt Request Flag                                                                 |

|      |          |                  |     | [Setting condition]                                                                         |

|      |          |                  |     | When IRQ3 pin is designated for interrupt input and the designated signal edge is detected. |

|      |          |                  |     | [Clearing condition]                                                                        |

|      |          |                  |     | When IRRI3 is cleared by writing 0                                                          |

| 2    | IRRI2    | 0                | R/W | IRQ2 Interrupt Request Flag                                                                 |

|      |          |                  |     | [Setting condition]                                                                         |

|      |          |                  |     | When IRQ2 pin is designated for interrupt input and the designated signal edge is detected. |

|      |          |                  |     | [Clearing condition]                                                                        |

|      |          |                  |     | When IRRI2 is cleared by writing 0                                                          |

| 1    | IRRI1    | 0                | R/W | IRQ1 Interrupt Request Flag                                                                 |

|      |          |                  |     | [Setting condition]                                                                         |

|      |          |                  |     | When IRQ1 pin is designated for interrupt input and the designated signal edge is detected. |

|      |          |                  |     | [Clearing condition]                                                                        |

|      |          |                  |     | When IRRI1 is cleared by writing 0                                                          |

| 0    | IRRI0    | 0                | R/W | IRQ0 Interrupt Request Flag                                                                 |

|      |          |                  |     | [Setting condition]                                                                         |

|      |          |                  |     | When IRQ0 pin is designated for interrupt input and the designated signal edge is detected. |

|      |          |                  |     | [Clearing condition]                                                                        |

|      |          |                  |     | When IRRI0 is cleared by writing 0                                                          |

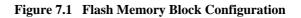

| Г          | H'0000    | H'0001 | H'0002 | ← Programming unit: 128 bytes → | H'007F      |

|------------|-----------|--------|--------|---------------------------------|-------------|

| Erase unit | H'0080    | H'0081 | H'0082 |                                 | H'00FF      |

| 1 kbyte    |           |        |        | 1<br>1<br>1                     | 1           |

|            |           |        |        | <br>                            | <br> <br>   |

|            | H'0380    | H'0381 | H'0382 | 1<br> <br>                      | H'03FF      |

|            | H'0400    | H'0401 | H'0402 | ← Programming unit: 128 bytes → | H'047F      |

| Erase unit | H'0480    | H'0481 | H'0481 | 1<br>1<br>1<br>1                | H'04FF      |

| 1 kbyte    |           |        |        |                                 |             |

| -          |           |        |        | 1<br>1<br>1                     | 1           |

| ŀ          | H'0780    | H'0781 | H'0782 | 1<br>1<br>T                     | H'07FF      |

| ŀ          | H'0800    | H'0801 | H'0802 | ← Programming unit: 128 bytes → | H'087F      |

| Erase unit | H'0880    | H'0881 | H'0882 | I<br>I<br>I                     | H'08FF      |

| 1 kbyte    |           |        |        |                                 | -<br>-<br>  |

| ŀ          | H'0B80    | H'0B81 | H'0B82 |                                 | H'0BFF      |

| ŀ          | H'0C00    | H'0C01 | H'0C02 | ← Programming unit: 128 bytes → | H'0C7F      |

| Erase unit | H'0C80    | H'0C81 | H'0C82 |                                 | H'0CFF      |

| 1 kbyte    |           |        |        | 1                               | 1           |

|            |           |        |        |                                 |             |

|            | H'0F80    | H'0F81 | H'0F82 | <br> <br>                       | H'0FFF      |

|            | H'1000    | H'1001 | H'1002 | ← Programming unit: 128 bytes → | H'107F      |

| Erase unit | H'1080    | H'1081 | H'1082 |                                 | H'10FF      |

| 28 kbytes  |           |        |        |                                 |             |

|            |           |        |        | <br> <br>                       |             |

| ŀ          | 1.1125.00 |        |        | I<br>I                          | 1           |

| ŀ          | H'7F80    | H'7F81 | H'7F82 | - Programming with 100 butes    | H'7FFF      |

| Erase unit | H'8000    | H'8001 | H'8002 | ← Programming unit: 128 bytes → | H'807F      |

|            | H'8080    | H'8081 | H'8082 | <br> <br>                       | H'80FF      |

| 16 kbytes  |           |        |        | -<br> <br> <br>                 | <br> <br>   |

|            |           |        |        | 1                               | 1<br>1<br>1 |

| ŀ          | H'BF80    | H'BF81 | H'BF82 | 1<br>1<br>1                     | H'BFFF      |

| ŀ          | H'C000    | H'C001 | H'C002 | ← Programming unit: 128 bytes → | H'C07F      |

| Erase unit | H'C080    | H'C081 | H'C082 |                                 | H'COFF      |

| 8 kbytes   |           |        |        |                                 | 1           |

| ·          |           |        |        | -<br> <br> <br>                 | 1<br>1<br>1 |

|            |           |        |        | 1<br>1<br>1                     | 1           |

| E F        | HDF80     | H'DF81 | H'DF82 | <br> <br>                       | H'DFFF      |

RENESAS

# 7.2.4 Flash Memory Power Control Register (FLPWCR)

FLPWCR enables or disables a transition to the flash memory power-down mode when the LSI switches to subactive mode. There are two modes: mode in which operation of the power supply circuit of flash memory is partly halted in power-down mode and flash memory can be read, and mode in which even if a transition is made to subactive mode, operation of the power supply circuit of flash memory is retained and flash memory can be read.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                |

|--------|----------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | PDWND    | 0                | R/W | Power-Down Disable                                                                                                                                                                                                                         |

|        |          |                  |     | When this bit is 0 and a transition is made to subactive<br>mode, the flash memory enters the power-down mode.<br>When this bit is 1, the flash memory remains in the<br>normal mode even after a transition is made to subactive<br>mode. |

| 6 to 0 | _        | All 0            | _   | Reserved                                                                                                                                                                                                                                   |

|        |          |                  |     | These bits are always read as 0.                                                                                                                                                                                                           |

### 7.2.5 Flash Memory Enable Register (FENR)

Bit 7 (FLSHE) in FENR enables or disables the CPU access to the flash memory control registers, FLMCR1, FLMCR2, EBR1, and FLPWCR.

|        |          | Initial |     |                                                                                                                                                              |

|--------|----------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit    | Bit Name | Value   | R/W | Description                                                                                                                                                  |

| 7      | FLSHE    | 0       | R/W | Flash Memory Control Register Enable                                                                                                                         |

|        |          |         |     | Flash memory control registers can be accessed when<br>this bit is set to 1. Flash memory control registers cannot<br>be accessed when this bit is set to 0. |

| 6 to 0 |          | All 0   | _   | Reserved                                                                                                                                                     |

|        |          |         |     | These bits are always read as 0.                                                                                                                             |

# 10.5 Interrupt Source

There are five kinds of RTC interrupts: week interrupts, day interrupts, hour interrupts, minute interrupts, and second interrupts.

When using an interrupt, initiate the RTC last after other registers are set. Do not set multiple interrupt enable bits in RTCCR2 simultaneously to 1.

When an interrupt request of the RTC occurs, the IRRTA flag in IRR1 is set to 1. When clearing the flag, write 0.

| Interrupt Name            | Interrupt Source                                                      | Interrupt Enable Bit |

|---------------------------|-----------------------------------------------------------------------|----------------------|

| Overflow interrupt        | Occurs when the free running counter is overflown.                    | FOIE                 |

| Week periodic interrupt   | Occurs every week when the day-of-week date register value becomes 0. | WKIE                 |

| Day periodic interrupt    | Occurs every day when the day-of-week date register is counted.       | DYIE                 |

| Hour periodic interrupt   | Occurs every hour when the hour date register is counted.             | HRIE                 |

| Minute periodic interrupt | Occurs every minute when the minute date register is counted.         | MNIE                 |

| Second periodic interrupt | Occurs every second when the second date register is counted.         | SCIE                 |

#### Table 10.2 Interrupt Source

# 11.2 Input/Output Pin

Table 11.1 shows the timer B1 pin configuration.

### Table 11.1 Pin Configuration

| Name                 | Abbreviation | I/O   | Function            |

|----------------------|--------------|-------|---------------------|

| Timer B1 event input | TMIB1        | Input | Event input to TCB1 |

# **11.3** Register Descriptions

The timer B1 has the following registers.

- Timer mode register B1 (TMB1)

- Timer counter B1 (TCB1)

- Timer load register B1 (TLB1)

# 13.3.8 General Registers A, B, C, and D (GRA, GRB, GRC, and GRD)

GR are 16-bit registers. Timer Z has eight general registers (GR), four for each channel. The GR registers are dual function 16-bit readable/writable registers, functioning as either output compare or input capture registers. Functions can be switched by TIORA and TIORC.

The values in GR and TCNT are constantly compared with each other when the GR registers are used as output compare registers. When the both values match, the IMFA to IMFD flags in TSR are set to 1. Compare match outputs can be selected by TIORA and TIORC.

When the GR registers are used as input capture registers, the TCNT value is stored after detecting external signals. At this point, IMFA to IMFD flags in the corresponding TSR are set to 1. Detection edges for input capture signals can be selected by TIORA and TIORC.

When PWM mode, complementary PWM mode, or reset synchronous PWM mode is selected, the values in TIORA and TIORC are ignored. Upon reset, the GR registers are set as output compare registers (no output) and initialized to H'FFFF. The GR registers cannot be accessed in 8-bit units; they must always be accessed as a 16-bit unit.

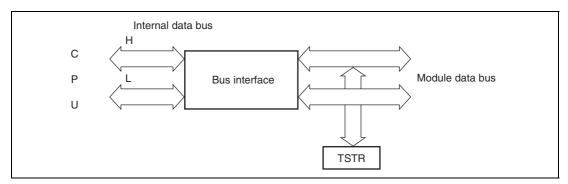

2. 8-bit register

Registers other than TCNT and GR are 8-bit registers that are connected internally with the CPU in an 8-bit width. Figure 13.6 shows an example of accessing the 8-bit registers.

Figure 13.6 Accessing Operation of 8-Bit Register (between CPU and TSTR (8 bits))

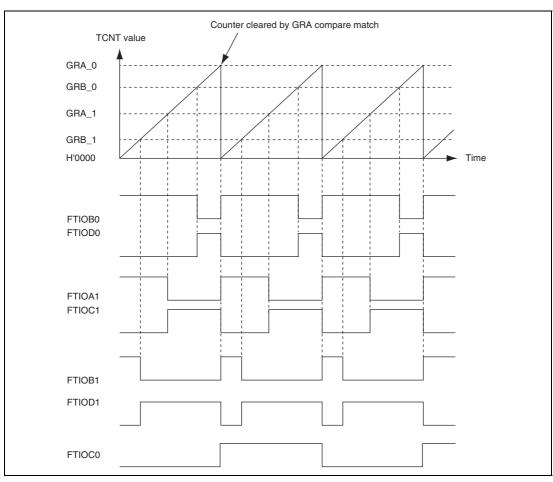

#### 13.4.6 Reset Synchronous PWM Mode

Three normal- and counter-phase PWM waveforms are output by combining channels 0 and 1 that one of changing points of waveforms will be common.

In reset synchronous PWM mode, the FTIOB0 to FTIOD0 and FTIOA1 to FTIOD1 pins become PWM-output pins automatically. TCNT\_0 performs an increment operation. Tables 13.4 and 13.5 show the PWM-output pins used and the register settings, respectively.

Figure 13.26 shows the example of reset synchronous PWM mode setting procedure.

| Channel | Pin Name | Input/Output | Pin Function                                          |

|---------|----------|--------------|-------------------------------------------------------|

| 0       | FTIOC0   | Output       | Toggle output in synchronous with PWM cycle           |

| 0       | FTIOB0   | Output       | PWM output 1                                          |

| 0       | FTIOD0   | Output       | PWM output 1 (counter-phase waveform of PWM output 1) |

| 1       | FTIOA1   | Output       | PWM output 2                                          |

| 1       | FTIOC1   | Output       | PWM output 2 (counter-phase waveform of PWM output 2) |

| 1       | FTIOB1   | Output       | PWM output 3                                          |

| 1       | FTIOD1   | Output       | PWM output 3 (counter-phase waveform of PWM output 3) |

Table 13.4

Output Pins in Reset Synchronous PWM Mode

#### Table 13.5 Register Settings in Reset Synchronous PWM Mode

| Register | Description                                                                  |

|----------|------------------------------------------------------------------------------|

| TCNT_0   | Initial setting of H'0000                                                    |

| TCNT_1   | Not used (independently operates)                                            |

| GRA_0    | Sets counter cycle of TCNT_0                                                 |

| GRB_0    | Set a changing point of the PWM waveform output from pins FTIOB0 and FTIOD0. |

| GRA_1    | Set a changing point of the PWM waveform output from pins FTIOA1 and FTIOC1. |

| GRB_1    | Set a changing point of the PWM waveform output from pins FTIOB1 and FTIOD1. |

Figure 13.28 Example of Reset Synchronous PWM Mode Operation (OLS0 = OLS1 = 0)

In reset synchronous PWM mode, TCNT\_0 and TCNT\_1 perform increment and independent operations, respectively. However, GRA\_1 and GRB\_1 are separated from TCNT\_1. When a compare match occurs between TCNT\_0 and GRA\_0, a counter is cleared and an increment operation is restarted from H'0000.

The PWM pin outputs 0 or 1 whenever a compare match between GRB\_0, GRA\_1, GRB\_1 and TCNT\_0 or counter clearing occur.

For details on operations when reset synchronous PWM mode and buffer operation are simultaneously set, refer to section 13.4.8, Buffer Operation.

To change duty cycles while a waveform with a duty cycle of 0% or 100% is being output, make sure the following procedure.

- To change duty cycles while a 0%-duty cycle waveform is being output, write to GR while H'0000 ≤ TCNT\_1 < previous GR value

- To change duty cycles while a 100%-duty cycle waveform is being output, write to GR while previous GR value< TCNT\_0 ≤ GRA\_0</li>

Note that changing from a 0%-duty cycle waveform to a 100%-duty cycle waveform and vice versa is not possible.

- Buffer operation is used and TPSC2 = TPSC1 = TPSC0 = 0

Write H'0000 or a value equal to or more than the GRA\_0 value to the buffer register.

- To output a 0%-duty cycle waveform, write a value equal to or more than the GRA\_0 value to the buffer register

- To output a 100%-duty cycle waveform, write H'0000 to the buffer register For details on buffer operation, see section 13.4.8, Buffer Operation.

- c. Buffer operation is not used and other than TPSC2 = TPSC1 = TPSC0 = 0

Write a value which satisfies GRA\_0 + 1 < GR < H'FFFF to GR directly at the timing shown below.</li>

- To output a 0%-duty cycle waveform, write the value while H'0000 ≤ TCNT\_1 < previous GR value

- To output a 100%-duty cycle waveform, write the value while previous GR value< TCNT\_0  $\leq$  GRA\_0

To change duty cycles while a waveform with a duty cycle of 0% and 100% is being output, the following procedure must be followed.

- To change duty cycles while a 0%-duty cycle waveform is being output, write to GR while H'0000 ≤ TCNT\_1 < previous GR value

- To change duty cycles while a 100%-duty cycle waveform is being output, write to GR while previous GR value< TCNT\_0 ≤ GRA\_0</li>

Note that changing from a 0%-duty cycle waveform to a 100%-duty cycle waveform and vice versa is not possible.

- d. Buffer operation is used and other than TPSC2 = TPSC1 = TPSC0 = 0 Write a value which satisfies  $GRA_0 + 1 < GR < H$ 'FFFF to the buffer register. A waveform with a duty cycle of 0% can be output. However, a waveform with a duty cycle of 100% cannot be output using the buffer operation. Also, the buffer operation cannot be used to change duty cycles while a waveform with a duty cycle of 100% is being output. For details on buffer operation, see section 13.4.8, Buffer Operation.

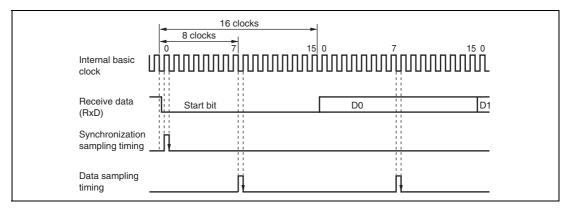

#### 16.8.4 Receive Data Sampling Timing and Reception Margin in Asynchronous Mode

In asynchronous mode, the SCI3 operates on a basic clock with a frequency of 16 times the transfer rate. In reception, the SCI3 samples the falling edge of the start bit using the basic clock, and performs internal synchronization. Receive data is latched internally at the rising edge of the 8th pulse of the basic clock as shown in figure 16.19. Thus, the reception margin in asynchronous mode is given by formula (1) below.

$$M = \left\{ (0.5 - \frac{1}{2N}) - \frac{D - 0.5}{N} - (L - 0.5) F \right\} \times 100(\%)$$

... Formula (1)

Legend N : Ratio of bit rate to clock (N = 16)

- D : Clock duty (D = 0.5 to 1.0)

- L : Frame length (L = 9 to 12)

- F : Absolute value of clock rate deviation

Assuming values of F (absolute value of clock rate deviation) = 0 and D (clock duty) = 0.5 in formula (1), the reception margin can be given by the formula.

$M = \{0.5 - 1/(2 \times 16)\} \times 100 \text{ [\%]} = 46.875\%$

However, this is only the computed value, and a margin of 20% to 30% should be allowed for in system design.

Figure 16.19 Receive Data Sampling Timing in Asynchronous Mode

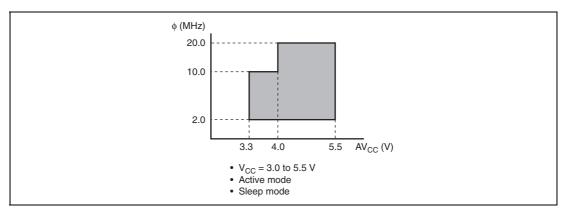

#### Analog Power Supply Voltage and A/D Converter Accuracy Guarantee Range

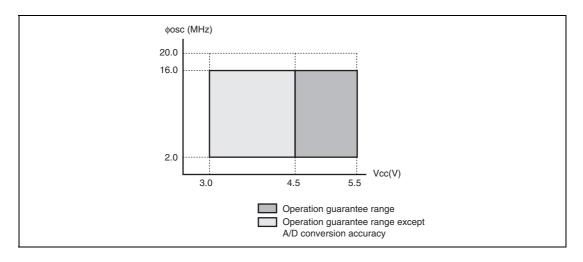

Range of Power Supply Voltage and Oscillation Frequency when Low-Voltage Detection Circuit is Used

|         |                                                            |        |                |     | Value | S   |       |

|---------|------------------------------------------------------------|--------|----------------|-----|-------|-----|-------|

| Item    |                                                            | Symbol | Test Condition | Min | Тур   | Max | Unit  |

| Erasing | Wait time after SWE bit setting*1                          | x      |                | 1   | _     | _   | μs    |

|         | Wait time after ESU bit setting*1                          | У      |                | 100 | _     | _   | μs    |

|         | Wait time after E bit setting* <sup>1</sup> * <sup>6</sup> | z      |                | 10  | —     | 100 | ms    |

|         | Wait time after E bit clear*1                              | α      |                | 10  | _     | _   | μs    |

|         | Wait time after ESU bit clear*1                            | β      |                | 10  | —     | _   | μs    |

|         | Wait time after EV bit setting* <sup>1</sup>               | γ      |                | 20  | —     | —   | μs    |

|         | Wait time after<br>dummy write*1                           | ε      |                | 2   | —     | —   | μs    |

|         | Wait time after EV bit clear*1                             | η      |                | 4   | _     | _   | μs    |

|         | Wait time after SWE bit clear*1                            | θ      |                | 100 | —     | —   | μs    |

|         | Maximum erase count *1*6*7                                 | Ν      |                | _   | _     | 120 | Times |

Notes: 1. Make the time settings in accordance with the program/erase algorithms.

- 2. The programming time for 128 bytes. (Indicates the total time for which the P bit in flash memory control register 1 (FLMCR1) is set. The program-verify time is not included.)

- 3. The time required to erase one block. (Indicates the time for which the E bit in flash memory control register 1 (FLMCR1) is set. The erase-verify time is not included.)

- 4. Programming time maximum value ( $t_P(max.)$ ) = wait time after P bit setting (z) × maximum programming count (N)

- 5. Set the maximum programming count (N) according to the actual set values of z1, z2, and z3, so that it does not exceed the programming time maximum value ( $t_p(max.)$ ). The wait time after P bit setting (z1, z2) should be changed as follows according to the value of the programming count (n).

Programming count (n)

$1 \leq n \leq 6 \qquad \qquad z1 = 30 \ \mu s$

$$7 \le n \le 1000$$

$z2 = 200 \ \mu s$

- 6. Erase time maximum value (t<sub>E</sub>(max.)) = wait time after E bit setting (z)  $\times$  maximum erase count (N)

- 7. Set the maximum erase count (N) according to the actual set value of (z), so that it does not exceed the erase time maximum value ( $t_e(max.)$ ).

|                           |                 |                                                                                        |                                                                        |                       | Value | es                   |      |       |

|---------------------------|-----------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------|-------|----------------------|------|-------|

| ltem                      | Symbol          | Applicable Pins                                                                        | Test Condition                                                         | Min                   | Тур   | Max                  | Unit | Notes |

| Input low<br>voltage      | V <sub>IL</sub> | RES, NMI,<br>WKP0 to WKP5,<br>IRQ0 to IRQ3,<br>ADTRG, TMIB1,<br>TMRIV,                 | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$                               | -0.3                  | _     | $V_{cc} \times 0.2$  | V    |       |

|                           |                 | TMCIV, FTIOA0<br>to FTIOD0,<br>FTIOA1 to<br>FTIOD1, SCK3,<br>SCK3_2, TRGV              |                                                                        | -0.3                  | _     | $V_{cc} \times 0.1$  | —    |       |

|                           |                 | RXD, RXD_2,<br>SCL, SDA,<br>P10 to P12,<br>P14 to P17,<br>P20 to P24,<br>P30 to P37,   | $V_{cc}$ = 4.0 to 5.5 V                                                | -0.3                  | _     | V <sub>cc</sub> ×0.3 | V    | _     |

|                           |                 | P50 to P57,<br>P60 to P67,.<br>P70 to P72,<br>P74 to P76,<br>P85 to P87,<br>PB0 to PB7 |                                                                        | -0.3                  | _     | V <sub>cc</sub> ×0.2 | _    |       |

|                           |                 | OSC1                                                                                   | $V_{\rm cc}$ = 4.0 to 5.5 V                                            | -0.3                  | _     | 0.5                  | ۷    | -     |

|                           |                 |                                                                                        |                                                                        | -0.3                  | _     | 0.3                  |      |       |

| Output<br>high<br>voltage | V <sub>oh</sub> | P10 to P12,<br>P14 to P17,<br>P20 to P24,<br>P30 to P37,                               | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$<br>$-I_{OH} = 1.5 \text{ mA}$ | V <sub>cc</sub> – 1.0 | _     | _                    | V    |       |

|                           |                 | P50 to P55,<br>P60 to P67,<br>P70 to P72,<br>P74 to P76,<br>P85 to P87                 | -l <sub>oH</sub> = 0.1 mA                                              | V <sub>cc</sub> – 0.5 | _     | _                    | _    |       |

|                           |                 | P56, P57                                                                               | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$<br>$-I_{OH} = 0.1 \text{ mA}$ | V <sub>cc</sub> – 2.5 | _     | _                    | V    | _     |

|                           |                 |                                                                                        | $V_{cc}$ =2.7 to 4.0 V<br>- $I_{OH}$ = 0.1 mA                          | V <sub>cc</sub> - 2.0 | _     | _                    | _    |       |

RENESAS

|          |                         |                     | Addressing Mode and<br>Instruction Length (bytes) |    |      |           |             |      |          |       |   |                                                                                       |                            |          |                |                |   |   | No<br>Stat | . of<br>es <sup>*1</sup> |  |

|----------|-------------------------|---------------------|---------------------------------------------------|----|------|-----------|-------------|------|----------|-------|---|---------------------------------------------------------------------------------------|----------------------------|----------|----------------|----------------|---|---|------------|--------------------------|--|

| Mnemonic |                         | <b>Operand Size</b> | #xx                                               | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @ aa | @(d, PC) | @ @aa | 1 | Operation                                                                             | 1                          | Con<br>H | ditio          | n Co           | v | с | Normal     | Advanced                 |  |

| MOV      | MOV.W Rs, @-ERd         | w                   |                                                   |    |      |           | 2           |      |          |       |   | $ \begin{array}{l} ERd32-2 \rightarrow ERd32 \\ Rs16 \rightarrow @ ERd \end{array} $  | -                          | -        | ≎              | \$             | 0 | - | 6          | 5                        |  |

|          | MOV.W Rs, @aa:16        | W                   |                                                   |    |      |           |             | 4    |          |       |   | $Rs16 \rightarrow @aa:16$                                                             | -                          | -        | ≎              | €              | 0 | _ | 6          | 6                        |  |

|          | MOV.W Rs, @aa:24        | W                   |                                                   |    |      |           |             | 6    |          |       |   | Rs16 $\rightarrow$ @aa:24                                                             | -                          | —        | $\updownarrow$ | $\uparrow$     | 0 | _ | 8          | 3                        |  |

| Í        | MOV.L #xx:32, Rd        | L                   | 6                                                 |    |      |           |             |      |          |       |   | $#xx:32 \rightarrow Rd32$                                                             | -                          | —        | \$             | \$             | 0 | _ | 6          | 6                        |  |

|          | MOV.L ERs, ERd          | L                   |                                                   | 2  |      |           |             |      |          |       |   | $ERs32 \rightarrow ERd32$                                                             | -                          | -        | \$             | \$             | 0 | _ | 2          | 2                        |  |

| Í        | MOV.L @ERs, ERd         | L                   |                                                   |    | 4    |           |             |      |          |       |   | @ERs $\rightarrow$ ERd32                                                              | -                          | _        | €              | \$             | 0 | _ | 8          | 3                        |  |

| Í        | MOV.L @(d:16, ERs), ERd | L                   |                                                   |    |      | 6         |             |      |          |       |   | @(d:16, ERs) → ERd32                                                                  | -                          | _        | \$             | \$             | 0 | _ | 1          | 0                        |  |

|          | MOV.L @(d:24, ERs), ERd | L                   |                                                   |    |      | 10        |             |      |          |       |   | $@(d:24, ERs) \rightarrow ERd32$                                                      | -                          | -        | \$             | \$             | 0 | _ | 1          | 14<br>10                 |  |

|          | MOV.L @ERs+, ERd        | L                   |                                                   |    |      |           | 4           |      |          |       |   | @ERs → ERd32<br>ERs32+4 → ERs32                                                       | -                          | -        | \$             | \$             | 0 | - | 1          |                          |  |

|          | MOV.L @aa:16, ERd       | L                   |                                                   |    |      |           |             | 6    |          |       |   | @aa:16 $\rightarrow$ ERd32                                                            | -                          | -        | €              | €              | 0 | _ | 1          | 0                        |  |

|          | MOV.L @aa:24, ERd       | L                   |                                                   |    |      |           |             | 8    |          |       |   | @aa:24 $\rightarrow$ ERd32                                                            | -                          | -        | €              | €              | 0 | _ | 12         |                          |  |

|          | MOV.L ERs, @ERd         | L                   |                                                   |    | 4    |           |             |      |          |       |   | $ERs32 \rightarrow @ERd$                                                              | -                          | -        | €              | €              | 0 | _ | 8          | 3                        |  |

|          | MOV.L ERs, @(d:16, ERd) | L                   |                                                   |    |      | 6         |             |      |          |       |   | ERs32 $\rightarrow$ @(d:16, ERd)                                                      | -                          | -        | €              | €              | 0 | _ | 1          | 0                        |  |

|          | MOV.L ERs, @(d:24, ERd) | L                   |                                                   |    |      | 10        |             |      |          |       |   | ERs32 $\rightarrow$ @(d:24, ERd)                                                      | -                          | _        | €              | \$             | 0 | _ | 1          | 4                        |  |

|          | MOV.L ERs, @-ERd        | L                   |                                                   |    |      |           | 4           |      |          |       |   | $ \begin{array}{l} ERd32-4 \rightarrow ERd32 \\ ERs32 \rightarrow @ ERd \end{array} $ | -                          | —        | \$             | \$             | 0 | - | 1          | 0                        |  |

|          | MOV.L ERs, @aa:16       | L                   |                                                   |    |      |           |             | 6    |          |       |   | ERs32 $\rightarrow$ @aa:16                                                            | -                          | -        | ↕              | $\updownarrow$ | 0 | _ | 1          | 0                        |  |

|          | MOV.L ERs, @aa:24       | L                   |                                                   |    |      |           |             | 8    |          |       |   | $ERs32 \rightarrow @aa:24$                                                            | -                          | -        | ↕              | $\updownarrow$ | 0 | — | 1          | 2                        |  |

| POP      | POP.W Rn                | W                   |                                                   |    |      |           |             |      |          |       | 2 | $\begin{array}{l} @ SP \to Rn16 \\ SP+2 \to SP \end{array}$                           | -                          | —        | \$             | \$             | 0 | — | 6          | 6                        |  |

|          | POP.L ERn               | L                   |                                                   |    |      |           |             |      |          |       | 4 | $\begin{array}{l} @ SP \to ERn32 \\ SP+4 \to SP \end{array}$                          | -                          | —        | \$             | \$             | 0 | - | 1          | 0                        |  |

| PUSH     | PUSH.W Rn               | W                   |                                                   |    |      |           |             |      |          |       | 2 | $\begin{array}{l} SP-2 \rightarrow SP \\ Rn16 \rightarrow @ SP \end{array}$           | -                          | -        | \$             | \$             | 0 | - | 6          | 6                        |  |

|          | PUSH.L ERn              | L                   |                                                   |    |      |           |             |      |          |       | 4 | $SP-4 \rightarrow SP$<br>ERn32 $\rightarrow @SP$                                      | -                          | -        | \$             | \$             | 0 | - | 1          | 0                        |  |

| MOVFPE   | MOVFPE @aa:16, Rd       | В                   |                                                   |    |      |           |             | 4    |          |       |   | Cannot be used in this LSI                                                            | Cannot be used in this LSI |          |                |                |   |   |            |                          |  |

| MOVTPE   | MOVTPE Rs, @aa:16       | В                   |                                                   |    |      |           |             | 4    |          |       |   | Cannot be used in this LSI                                                            | Cannot be used in this LSI |          |                |                |   |   |            |                          |  |

Figure B.23 Port B Block Diagram (PB7 to PB0)