#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | Н8/300Н                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SCI                                                        |

| Peripherals                | PWM, WDT                                                                     |

| Number of I/O              | 45                                                                           |

| Program Memory Size        | 56КВ (56К × 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 4K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-BQFP                                                                      |

| Supplier Device Package    | 64-QFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f3687hv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 13.59 | When Compare Match and Bit Manipulation Instruction to TOCR<br>Occur at the Same Timing | 250 |

|--------------|-----------------------------------------------------------------------------------------|-----|

| Section 14   | Watchdog Timer                                                                          |     |

|              | Block Diagram of Watchdog Timer                                                         |     |

|              | Watchdog Timer Operation Example                                                        |     |

| Section 15   | 14-Bit PWM                                                                              |     |

|              | Block Diagram of 14-Bit PWM                                                             |     |

| -            | Waveform Output by 14-Bit PWM                                                           |     |

| Section 16   | Serial Communication Interface 3 (SCI3)                                                 |     |

| Figure 16.1  | Block Diagram of SCI3                                                                   | 261 |

| Figure 16.2  | Data Format in Asynchronous Communication                                               | 276 |

| Figure 16.3  | Relationship between Output Clock and Transfer Data Phase                               |     |

| -            | (Asynchronous Mode) (Example with 8-Bit Data, Parity, Two Stop Bits)                    | 276 |

| Figure 16.4  | Sample SCI3 Initialization Flowchart                                                    | 277 |

| Figure 16.5  | Example of SCI3 Transmission in Asynchronous Mode                                       |     |

|              | (8-Bit Data, Parity, One Stop Bit)                                                      | 278 |

| Figure 16.6  | Sample Serial Transmission Data Flowchart (Asynchronous Mode)                           | 279 |

| Figure 16.7  | Example of SCI3 Reception in Asynchronous Mode                                          |     |

| -            | (8-Bit Data, Parity, One Stop Bit)                                                      | 280 |

| Figure 16.8  | Sample Serial Reception Data Flowchart (Asynchronous Mode) (1)                          | 282 |

| Figure 16.8  | Sample Serial Reception Data Flowchart (Asynchronous Mode) (2)                          | 283 |

| Figure 16.9  | Data Format in Clocked Synchronous Communication                                        |     |

| Figure 16.10 | Example of SCI3 Transmission in Clocked Synchronous Mode                                |     |

| Figure 16.11 | Sample Serial Transmission Flowchart (Clocked Synchronous Mode)                         | 287 |

| Figure 16.12 | Example of SCI3 Reception in Clocked Synchronous Mode                                   | 288 |

| Figure 16.13 | Sample Serial Reception Flowchart (Clocked Synchronous Mode)                            |     |

| Figure 16.14 | Sample Flowchart of Simultaneous Serial Transmit and Receive Operations                 |     |

|              | (Clocked Synchronous Mode)                                                              | 291 |

| Figure 16.15 | Example of Inter-Processor Communication Using Multiprocessor Format                    |     |

|              | (Transmission of Data H'AA to Receiving Station A)                                      | 293 |

| Figure 16.16 | Sample Multiprocessor Serial Transmission Flowchart                                     | 294 |

| Figure 16.17 | Sample Multiprocessor Serial Reception Flowchart (1)                                    | 296 |

| Figure 16.17 | Sample Multiprocessor Serial Reception Flowchart (2)                                    | 297 |

| Figure 16.18 | Example of SCI3 Reception Using Multiprocessor Format                                   |     |

|              | (Example with 8-Bit Data, Multiprocessor Bit, One Stop Bit)                             | 298 |

| Figure 16.19 | Receive Data Sampling Timing in Asynchronous Mode                                       | 301 |

|              | I <sup>2</sup> C Bus Interface 2 (IIC2)                                                 |     |

| Figure 17.1  | Block Diagram of I <sup>2</sup> C Bus Interface 2                                       | 304 |

# RENESAS

# Section 1 Overview

### 1.1 Features

- High-speed H8/300H central processing unit with an internal 16-bit architecture

- Upward-compatible with H8/300 CPU on an object level

- Sixteen 16-bit general registers

- 62 basic instructions

- Various peripheral functions

- RTC (can be used as a free running counter)

- Timer B1 (8-bit timer)

- Timer V (8-bit timer)

- Timer Z (16-bit timer)

- 14-bit PWM

- Watchdog timer

- SCI (Asynchronous or clocked synchronous serial communication interface) × 2 channels

- I<sup>2</sup>C Bus Interface (conforms to the I<sup>2</sup>C bus interface format that is advocated by Philips Electronics)

- 10-bit A/D converter

| Instructio   | on Size*                                             | Function                                                                                                                                                                                                                                                                                                        |  |  |  |

|--------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ADD<br>SUB   | B/W/L                                                | $Rd \pm Rs \rightarrow Rd$ , $Rd \pm \#IMM \rightarrow Rd$<br>Performs addition or subtraction on data in two general registers, or on<br>immediate data and data in a general register (immediate byte data<br>cannot be subtracted from byte data in a general register. Use the<br>SUBX or ADD instruction.) |  |  |  |

| ADDX<br>SUBX | В                                                    | $\begin{array}{l} Rd\pm Rs\pm C\rightarrow Rd,  Rd\pm \#IMM\pm C\rightarrow Rd\\ Performs addition or subtraction with carry on byte data in two general registers, or on immediate data and data in a general register. \end{array}$                                                                           |  |  |  |

| INC<br>DEC   | B/W/L                                                | $Rd \pm 1 \rightarrow Rd$ , $Rd \pm 2 \rightarrow Rd$<br>Increments or decrements a general register by 1 or 2. (Byte operands<br>can be incremented or decremented by 1 only.)                                                                                                                                 |  |  |  |

| ADDS<br>SUBS | L                                                    | $\begin{array}{ll} Rd\pm 1 \rightarrow Rd, & Rd\pm 2 \rightarrow Rd, & Rd\pm 4 \rightarrow Rd \\ \mbox{Adds or subtracts the value 1, 2, or 4 to or from data in a 32-bit register.} \end{array}$                                                                                                               |  |  |  |

| DAA<br>DAS   | В                                                    | Rd (decimal adjust) $\rightarrow$ Rd<br>Decimal-adjusts an addition or subtraction result in a general register by<br>referring to the CCR to produce 4-bit BCD data.                                                                                                                                           |  |  |  |

| MULXU        | B/W                                                  | $\begin{array}{l} \text{Rd}\times\text{Rs}\rightarrow\text{Rd}\\ \text{Performs unsigned multiplication on data in two general registers: either}\\ 8 \text{ bits}\times8 \text{ bits}\rightarrow16 \text{ bits or } 16 \text{ bits}\times16 \text{ bits}\rightarrow32 \text{ bits.} \end{array}$               |  |  |  |

| MULXS        | B/W                                                  | $\begin{array}{l} Rd\timesRs\toRd\\ Performs \text{ signed multiplication on data in two general registers: either 8}\\ bits\times8 \ bits\to16 \ bits \ or \ 16 \ bits\times16 \ bits\to32 \ bits. \end{array}$                                                                                                |  |  |  |

| DIVXU        | B/W                                                  | Rd $\div$ Rs $\rightarrow$ Rd<br>Performs unsigned division on data in two general registers: either 16<br>bits $\div$ 8 bits $\rightarrow$ 8-bit quotient and 8-bit remainder or 32 bits $\div$ 16 bits $\rightarrow$<br>16-bit quotient and 16-bit remainder.                                                 |  |  |  |

| Note: *      | efers to the op<br>B: Byte<br>W: Word<br>L: Longword | perand size.                                                                                                                                                                                                                                                                                                    |  |  |  |

# Table 2.3 Arithmetic Operations Instructions (1)

| Instructio | on Size*      | Function                                                                                                                                                                              |

|------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AND        | B/W/L         | $Rd \wedge Rs \rightarrow Rd$ , $Rd \wedge \#IMM \rightarrow Rd$<br>Performs a logical AND operation on a general register and another<br>general register or immediate data.         |

| OR         | B/W/L         | $Rd \lor Rs \rightarrow Rd$ , $Rd \lor \#IMM \rightarrow Rd$<br>Performs a logical OR operation on a general register and another<br>general register or immediate data.              |

| XOR        | B/W/L         | $Rd \oplus Rs \rightarrow Rd$ , $Rd \oplus #IMM \rightarrow Rd$<br>Performs a logical exclusive OR operation on a general register and<br>another general register or immediate data. |

| NOT        | B/W/L         | ¬ (Rd) → (Rd)<br>Takes the one's complement (logical complement) of general register contents.                                                                                        |

| Note: *    | Refers to the | operand size.                                                                                                                                                                         |

|            | B: Byte       |                                                                                                                                                                                       |

|            | W: Word       |                                                                                                                                                                                       |

|            | L: Longword   |                                                                                                                                                                                       |

#### Table 2.4 Logic Operations Instructions

#### Table 2.5Shift Instructions

| Instructio     | on Size*                    | Function                                                                                  |  |  |  |

|----------------|-----------------------------|-------------------------------------------------------------------------------------------|--|--|--|

| SHAL<br>SHAR   | B/W/L                       | Rd (shift) $\rightarrow$ Rd Performs an arithmetic shift on general register contents.    |  |  |  |

| SHLL<br>SHLR   | B/W/L                       | Rd (shift) $\rightarrow$ Rd<br>Performs a logical shift on general register contents.     |  |  |  |

| ROTL<br>ROTR   | B/W/L                       | Rd (rotate) $\rightarrow$ Rd<br>Rotates general register contents.                        |  |  |  |

| ROTXL<br>ROTXR | B/W/L                       | Rd (rotate) $\rightarrow$ Rd<br>Rotates general register contents through the carry flag. |  |  |  |

| Note: *        | Refers to the operand size. |                                                                                           |  |  |  |

B: Byte

W: Word

L: Longword

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                     |

|-----|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------|

| 3   | IWPF3    | 0                | R/W | WKP3 Interrupt Request Flag                                                                                     |

|     |          |                  |     | [Setting condition]                                                                                             |

|     |          |                  |     | When $\overline{\text{WKP3}}$ pin is designated for interrupt input and the designated signal edge is detected. |

|     |          |                  |     | [Clearing condition]                                                                                            |

|     |          |                  |     | When IWPF3 is cleared by writing 0.                                                                             |

| 2   | IWPF2    | 0                | R/W | WKP2 Interrupt Request Flag                                                                                     |

|     |          |                  |     | [Setting condition]                                                                                             |

|     |          |                  |     | When $\overline{\text{WKP2}}$ pin is designated for interrupt input and the designated signal edge is detected. |

|     |          |                  |     | [Clearing condition]                                                                                            |

|     |          |                  |     | When IWPF2 is cleared by writing 0.                                                                             |

| 1   | IWPF1    | 0                | R/W | WKP1 Interrupt Request Flag                                                                                     |

|     |          |                  |     | [Setting condition]                                                                                             |

|     |          |                  |     | When $\overline{WKP1}$ pin is designated for interrupt input and the designated signal edge is detected.        |

|     |          |                  |     | [Clearing condition]                                                                                            |

|     |          |                  |     | When IWPF1 is cleared by writing 0.                                                                             |

| 0   | IWPF0    | 0                | R/W | WKP0 Interrupt Request Flag                                                                                     |

|     |          |                  |     | [Setting condition]                                                                                             |

|     |          |                  |     | When $\overline{\text{WKP0}}$ pin is designated for interrupt input and the designated signal edge is detected. |

|     |          |                  |     | [Clearing condition]                                                                                            |

|     |          |                  |     | When IWPF0 is cleared by writing 0.                                                                             |

# 3.3 Reset Exception Handling

When the  $\overline{\text{RES}}$  pin goes low, all processing halts and this LSI enters the reset. The internal state of the CPU and the registers of the on-chip peripheral modules are initialized by the reset. To ensure that this LSI is reset at power-up, hold the  $\overline{\text{RES}}$  pin low until the clock pulse generator output stabilizes. To reset the chip during operation, hold the  $\overline{\text{RES}}$  pin low for at least 10 system clock cycles. When the  $\overline{\text{RES}}$  pin goes high after being held low for the necessary time, this LSI starts reset exception handling. The reset exception handling sequence is shown in figure 3.1. However, for the reset exception handling sequence of the product with on-chip power-on reset circuit, refer to section 20, Power-On Reset and Low-Voltage Detection Circuits (Optional).

The reset exception handling sequence is as follows:

- 1. Set the I bit in the condition code register (CCR) to 1.

- 2. The CPU generates a reset exception handling vector address (from H'0000 to H'0001), the data in that address is sent to the program counter (PC) as the start address, and program execution starts from that address.

# 3.4 Interrupt Exception Handling

### 3.4.1 External Interrupts

As the external interrupts, there are NMI, IRQ3 to IRQ0, and WKP5 to WKP0 interrupts.

### **NMI Interrupt**

NMI interrupt is requested by input signal edge to pin  $\overline{\text{NMI}}$ . This interrupt is detected by either rising edge sensing or falling edge sensing, depending on the setting of bit NMIEG in IEGR1. NMI is the highest-priority interrupt, and can always be accepted without depending on the I bit value in CCR.

## **IRQ3 to IRQ0 Interrupts**

IRQ3 to IRQ0 interrupts are requested by input signals to pins  $\overline{\text{IRQ3}}$  to  $\overline{\text{IRQ0}}$ . These four interrupts are given different vector addresses, and are detected individually by either rising edge sensing or falling edge sensing, depending on the settings of bits IEG3 to IEG0 in IEGR1. When pins  $\overline{\text{IRQ3}}$  to  $\overline{\text{IRQ0}}$  are designated for interrupt input in PMR1 and the designated signal edge is input, the corresponding bit in IRR1 is set to 1, requesting the CPU of an interrupt. These interrupts can be masked by setting bits IEN3 to IEN0 in IENR1.

#### 6.1.4 Module Standby Control Register 2 (MSTCR2)

MSTCR2 allows the on-chip peripheral modules to enter a standby state in module units.

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                           |

|------|----------|------------------|-----|-------------------------------------------------------|

| 7    | MSTS3_2  | 0                | R/W | SCI3_2 Module Standby                                 |

|      |          |                  |     | SCI3_2 enters standby mode when this bit is set to1   |

| 6, 5 | _        | All 0            | _   | Reserved                                              |

|      |          |                  |     | These bits are always read as 0.                      |

| 4    | MSTTB1   | 0                | R/W | Timer B1 Module Standby                               |

|      |          |                  |     | Timer B1 enters standby mode when this bit is set to1 |

| 3, 2 | _        | All 0            |     | Reserved                                              |

|      |          |                  |     | These bits are always read as 0.                      |

| 1    | MSTTZ    | 0                | R/W | Timer Z Module Standby                                |

|      |          |                  |     | Timer Z enters standby mode when this bit is set to1  |

| 0    | MSTPWM   | 0                | R/W | PWM Module Standby                                    |

|      |          |                  |     | PWM enters standby mode when this bit is set to1      |

### 6.2 Mode Transitions and States of LSI

Figure 6.1 shows the possible transitions among these operating modes. A transition is made from the program execution state to the program halt state by executing a SLEEP instruction. Interrupts allow for returning from the program halt state to the program execution state. A direct transition between active mode and subactive mode, which are both program execution states, can be made without halting the program. The operating frequency can also be changed in the same modes by making a transition directly from active mode to active mode, and from subactive mode to subactive mode. RES input enables transitions from a mode to the reset state. Table 6.2 shows the transition conditions of each mode after the SLEEP instruction is executed and a mode to return by an interrupt. Table 6.3 shows the internal states of the LSI in each mode.

# 7.2 **Register Descriptions**

The flash memory has the following registers.

- Flash memory control register 1 (FLMCR1)

- Flash memory control register 2 (FLMCR2)

- Erase block register 1 (EBR1)

- Flash memory power control register (FLPWCR)

- Flash memory enable register (FENR)

#### 7.2.1 Flash Memory Control Register 1 (FLMCR1)

FLMCR1 is a register that makes the flash memory change to program mode, program-verify mode, erase mode, or erase-verify mode. For details on register setting, refer to section 7.4, Flash Memory Programming/Erasing.

| 7       -       0       -       Reserved<br>This bit is always read as 0.         6       SWE       0       R/W       Software Write Enable<br>When this bit is set to 1, flash memory<br>programming/erasing is enabled. When this bit is<br>to 0, other FLMCR1 register bits and all EBR1 bits<br>be set.         5       ESU       0       R/W       Erase Setup<br>When this bit is set to 1, the flash memory change<br>erase setup state. When it is cleared to 0, the era<br>setup state is cancelled. Set this bit to 1 before se<br>E bit to 1 in FLMCR1.         4       PSU       0       R/W       Program Setup<br>When this bit is set to 1, the flash memory change<br>program setup state. When it is cleared to 0, the<br>setup state is cancelled. Set this bit to 1 before se<br>E bit to 1 in FLMCR1.         3       EV       0       R/W       Erase-Verify<br>When this bit is set to 1, the flash memory change<br>erase-verify mode. When it is cleared to 0, erase-<br>erase-verify mode. When it is cleared to 0, erase-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |          | Initial |     |                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This bit is always read as 0.         6       SWE       0       R/W       Software Write Enable         When this bit is set to 1, flash memory<br>programming/erasing is enabled. When this bit is<br>to 0, other FLMCR1 register bits and all EBR1 bits<br>be set.         5       ESU       0       R/W       Erase Setup<br>When this bit is set to 1, the flash memory change<br>erase setup state. When it is cleared to 0, the era<br>setup state is cancelled. Set this bit to 1 before set<br>E bit to 1 in FLMCR1.         4       PSU       0       R/W       Program Setup<br>When this bit is set to 1, the flash memory change<br>program setup state. When it is cleared to 0, the<br>setup state is cancelled. Set this bit to 1 before set<br>to 1 in FLMCR1.         4       PSU       0       R/W       Program Setup<br>When this bit is set to 1, the flash memory change<br>program setup state. When it is cleared to 0, the<br>setup state is cancelled. Set this bit to 1 before set<br>the P bit in FLMCR1.         3       EV       0       R/W       Erase-Verify<br>When this bit is set to 1, the flash memory change<br>erase-verify mode. When it is cleared to 0, erase-<br>erase-verify mode. When it is cleared to 0, erase-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit | Bit Name | Value   | R/W | Description                                                                                                                                                                                           |

| 6       SWE       0       R/W       Software Write Enable         When this bit is set to 1, flash memory programming/erasing is enabled. When this bit is to 0, other FLMCR1 register bits and all EBR1 bits be set.         5       ESU       0       R/W       Erase Setup         When this bit is set to 1, the flash memory change erase setup state. When it is cleared to 0, the era setup state is cancelled. Set this bit to 1 before set E bit to 1 in FLMCR1.         4       PSU       0       R/W       Program Setup         When this bit is set to 1, the flash memory change erase setup state. When it is cleared to 0, the era setup state is cancelled. Set this bit to 1 before set to 1 in FLMCR1.         4       PSU       0       R/W       Program Setup         When this bit is set to 1, the flash memory change program setup state. When it is cleared to 0, the setup state is cancelled. Set this bit to 1 before set the P bit in FLMCR1.         3       EV       0       R/W       Erase-Verify         When this bit is set to 1, the flash memory change erase-verify mode. When it is cleared to 0, erase-verify mode                                                                                                                                                                                                                                                                                                                                                                 | 7   | _        | 0       | _   | Reserved                                                                                                                                                                                              |

| When this bit is set to 1, flash memory<br>programming/erasing is enabled. When this bit is<br>to 0, other FLMCR1 register bits and all EBR1 bits<br>be set.5ESU0R/WErase Setup<br>When this bit is set to 1, the flash memory change<br>erase setup state. When it is cleared to 0, the era<br>setup state is cancelled. Set this bit to 1 before se<br>E bit to 1 in FLMCR1.4PSU0R/WProgram Setup<br>When this bit is set to 1, the flash memory change<br>erase setup state. When it is cleared to 0, the era<br>setup state is cancelled. Set this bit to 1 before se<br>E bit to 1 in FLMCR1.3EV0R/WProgram Setup<br>setup state is cancelled. Set this bit to 1 before se<br>the P bit in FLMCR1.3EV0R/WErase-Verify<br>When this bit is set to 1, the flash memory change<br>erase-verify mode. When it is cleared to 0, erase-<br>verify mode. When it is cleared to 0, erase-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |          |         |     | This bit is always read as 0.                                                                                                                                                                         |

| programming/erasing is enabled. When this bit is<br>to 0, other FLMCR1 register bits and all EBR1 bits<br>be set.5ESU0R/WErase Setup<br>When this bit is set to 1, the flash memory change<br>erase setup state. When it is cleared to 0, the era<br>setup state is cancelled. Set this bit to 1 before se<br>E bit to 1 in FLMCR1.4PSU0R/WProgram Setup<br>When this bit is set to 1, the flash memory change<br>program setup state. When it is cleared to 0, the<br>setup state is cancelled. Set this bit to 1 before se<br>the P bit in FLMCR1.3EV0R/WErase-Verify<br>When this bit is set to 1, the flash memory change<br>erase-verify mode. When it is cleared to 0, erase-<br>verify mode. When it is cleared to 0, erase-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6   | SWE      | 0       | R/W | Software Write Enable                                                                                                                                                                                 |

| When this bit is set to 1, the flash memory change erase setup state. When it is cleared to 0, the erase setup state is cancelled. Set this bit to 1 before set E bit to 1 in FLMCR1.         4       PSU       0       R/W       Program Setup When this bit is set to 1, the flash memory change program setup state. When it is cleared to 0, the setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before setup setup state is cancelled. Set this bit to 1 before setup setup setup setup state is cancelled. Set this bit to 1 before setup setu |     |          |         |     | programming/erasing is enabled. When this bit is cleared to 0, other FLMCR1 register bits and all EBR1 bits cannot                                                                                    |

| erase setup state. When it is cleared to 0, the erase setup state is cancelled. Set this bit to 1 before set E bit to 1 in FLMCR1.         4       PSU       0       R/W       Program Setup Men this bit is set to 1, the flash memory change program setup state. When it is cleared to 0, the setup state is cancelled. Set this bit to 1 before set the P bit in FLMCR1.         3       EV       0       R/W       Erase-Verify When this bit is set to 1, the flash memory change erase-verify mode. When it is cleared to 0, erase-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5   | ESU      | 0       | R/W | Erase Setup                                                                                                                                                                                           |

| When this bit is set to 1, the flash memory change program setup state. When it is cleared to 0, the setup state is cancelled. Set this bit to 1 before set the P bit in FLMCR1.         3       EV       0       R/W       Erase-Verify When this bit is set to 1, the flash memory change erase-verify mode. When it is cleared to 0, erase-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |          |         |     | When this bit is set to 1, the flash memory changes to the erase setup state. When it is cleared to 0, the erase setup state is cancelled. Set this bit to 1 before setting the E bit to 1 in FLMCR1. |

| program setup state. When it is cleared to 0, the setup state is cancelled. Set this bit to 1 before setup state is cancelled. Set this bit to 1 before set the P bit in FLMCR1.         3       EV       0       R/W       Erase-Verify         When this bit is set to 1, the flash memory change erase-verify mode. When it is cleared to 0, erase-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4   | PSU      | 0       | R/W | Program Setup                                                                                                                                                                                         |

| When this bit is set to 1, the flash memory change<br>erase-verify mode. When it is cleared to 0, erase-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |          |         |     | When this bit is set to 1, the flash memory changes to the program setup state. When it is cleared to 0, the program setup state is cancelled. Set this bit to 1 before setting the P bit in FLMCR1.  |

| erase-verify mode. When it is cleared to 0, erase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3   | EV       | 0       | R/W | Erase-Verify                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |          |         |     | When this bit is set to 1, the flash memory changes to erase-verify mode. When it is cleared to 0, erase-verify mode is cancelled.                                                                    |

### 9.2.4 Pin Functions

The correspondence between the register specification and the port functions is shown below.

#### P24 pin

| Register      | PCR2  |                |  |

|---------------|-------|----------------|--|

| Bit Name      | PCR24 | Pin Function   |  |

| Setting Value | 0     | P24 input pin  |  |

|               | 1     | P24 output pin |  |

### P23 pin

| Register      | PCR2  |                |  |

|---------------|-------|----------------|--|

| Bit Name      | PCR23 | Pin Function   |  |

| Setting Value | 0     | P23 input pin  |  |

|               | 1     | P23 output pin |  |

#### P22/TXD pin

|           | PCR2                 |                 |  |

|-----------|----------------------|-----------------|--|

| TXD PCR22 |                      | Pin Function    |  |

| 0         | 0                    | P22 input pin   |  |

|           | 1                    | P22 output pin  |  |

| 1         | Х                    | TXD output pin  |  |

|           | <b>TXD</b><br>0<br>1 | 0 <u>0</u><br>1 |  |

Legend: X: Don't care.

#### P21/RXD pin

| SCR3     | PCR2 |                |  |

|----------|------|----------------|--|

| RE PCR21 |      | Pin Function   |  |

| 0        | 0    | P21 input pin  |  |

|          | 1    | P21 output pin |  |

| 1        | Х    | RXD input pin  |  |

|          | RE   | RE PCR21       |  |

Legend: X: Don't care.

# Section 10 Realtime Clock (RTC)

The realtime clock (RTC) is a timer used to count time ranging from a second to a week. Figure 10.1 shows the block diagram of the RTC.

## 10.1 Features

- Counts seconds, minutes, hours, and day-of-week

- Start/stop function

- Reset function

- Readable/writable counter of seconds, minutes, hours, and day-of-week with BCD codes

- Periodic (seconds, minutes, hours, days, and weeks) interrupts

- 8-bit free running counter

- Selection of clock source

When the counter is incremented or decremented, the IMFA flag of channel 0 is set to 1, and when the register is underflowed, the UDF flag of channel 0 is set to 1. After buffer operation has been designated for BR, BR is transferred to GR when the counter is incremented by compare match A0 or when TCNT\_1 is underflowed. If the  $\phi$  or  $\phi/2$  clock is selected by TPSC2 to TPSC0 bits, the OVF flag is not set to 1 at the timing that the counter value changes from H'FFFF to H'0000. If the  $\phi/4$  or  $\phi/8$  clock is selected by TPSC2 to TPSC0 bits, the OVF flag is set to 1.

- 3. Setting GR Value in Complementary PWM Mode: To set the general register (GR) or modify GR during operation in complementary PWM mode, refer to the following notes.

- A. Initial value

- a. When other than TPSC2 = TPSC1 = TPSC0 = 0, the GRA\_0 value must be equal to H'FFFC or less. When TPSC2 = TPSC1 = TPSC0 = 0, the GRA\_0 value can be set to H'FFFF or less.

- b. H'0000 to T 1 (T: Initial value of TCNT0) must not be set for the initial value.

- c.  $GRA_0 (T 1)$  or more must not be set for the initial value.

- d. When using buffer operation, the same values must be set in the buffer registers and corresponding general registers.

- B. Modifying the setting value

- a. Writing to GR directly must be performed while the TCNT\_1 and TCNT\_0 values should satisfy the following expression:  $H'0000 \le TCNT_1 < previous GR value, and previous GR value < TCNT_0 \le GRA_0$ . Otherwise, a waveform is not output correctly. For details on outputting a waveform with a duty cycle of 0% and 100%, see C., Outputting a waveform with a duty cycle of 0% and 100%.

- b. Do not write the following values to GR directly. When writing the values, a waveform is not output correctly.

H'0000  $\leq$  GR  $\leq$  T – 1 and GRA\_0 – (T – 1)  $\leq$  GR < GRA\_0 when TPSC2 = TPSC1 = TPSC0 = 0

$H'0000 < GR \le T-1$  and  $GRA_0 - (T-1) \le GR < GRA_0 + 1$  when TPSC2 = TPSC1 = TPSC0 = 0

- c. Do not change settings of GRA\_0 during operation.

- C. Outputting a waveform with a duty cycle of 0% and 100%

- a. Buffer operation is not used and TPSC2 = TPSC1 = TPSC0 = 0

Write H'0000 or a value equal to or more than the GRA\_0 value to GR directly at the timing shown below.

- To output a 0%-duty cycle waveform, write a value equal to or more than the GRA\_0 value while H'0000 ≤ TCNT\_1 < previous GR value

- To output a 100%-duty cycle waveform, write H'0000 while previous GR value< TCNT\_0  $\leq$  GRA\_0

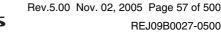

5. Contention between GR Read and Input Capture: If an input capture signal is generated in the T<sub>1</sub> state of a GR read cycle, the data that is read will be transferred before input capture transfer. Figure 13.56 shows the timing in this case.

Figure 13.56 Contention between GR Read and Input Capture

## 17.3.4 I<sup>2</sup>C Bus Interrupt Enable Register (ICIER)

ICIER enables or disables interrupt sources and acknowledge bits, sets acknowledge bits to be transferred, and confirms acknowledge bits to be received.

| Bit | Bit Name | Initial<br>Value | R/W  | Description                                                                                                                                                                                                                                                                                                                         |

|-----|----------|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TIE      | 0                | R/W  | Transmit Interrupt Enable                                                                                                                                                                                                                                                                                                           |

| ,   |          | 0                | 1000 | When the TDRE bit in ICSR is set to 1, this bit enables or disables the transmit data empty interrupt (TXI).                                                                                                                                                                                                                        |

|     |          |                  |      | 0: Transmit data empty interrupt request (TXI) is disabled.                                                                                                                                                                                                                                                                         |

|     |          |                  |      | 1: Transmit data empty interrupt request (TXI) is enabled.                                                                                                                                                                                                                                                                          |

| 6   | TEIE     | 0                | R/W  | Transmit End Interrupt Enable                                                                                                                                                                                                                                                                                                       |

|     |          |                  |      | This bit enables or disables the transmit end interrupt<br>(TEI) at the rising of the ninth clock while the TDRE bit in<br>ICSR is 1. TEI can be canceled by clearing the TEND bit<br>or the TEIE bit to 0.                                                                                                                         |

|     |          |                  |      | 0: Transmit end interrupt request (TEI) is disabled.                                                                                                                                                                                                                                                                                |

|     |          |                  |      | 1: Transmit end interrupt request (TEI) is enabled.                                                                                                                                                                                                                                                                                 |

| 5   | RIE      | 0                | R/W  | Receive Interrupt Enable                                                                                                                                                                                                                                                                                                            |

|     |          |                  |      | This bit enables or disables the receive data full interrupt<br>request (RXI) and the overrun error interrupt request<br>(ERI) with the clocked synchronous format, when a<br>receive data is transferred from ICDRS to ICDRR and the<br>RDRF bit in ICSR is set to 1. RXI can be canceled by<br>clearing the RDRF or RIE bit to 0. |

|     |          |                  |      | <ol> <li>Receive data full interrupt request (RXI) and overrun<br/>error interrupt request (ERI) with the clocked<br/>synchronous format are disabled.</li> </ol>                                                                                                                                                                   |

|     |          |                  |      | <ol> <li>Receive data full interrupt request (RXI) and overrun<br/>error interrupt request (ERI) with the clocked<br/>synchronous format are enabled.</li> </ol>                                                                                                                                                                    |

| 4   | NAKIE    | 0                | R/W  | NACK Receive Interrupt Enable                                                                                                                                                                                                                                                                                                       |

|     |          |                  |      | This bit enables or disables the NACK receive interrupt<br>request (NAKI) and the overrun error (setting of the OVE<br>bit in ICSR) interrupt request (ERI) with the clocked<br>synchronous format, when the NACKF and AL bits in<br>ICSR are set to 1. NAKI can be canceled by clearing the<br>NACKF, OVE, or NAKIE bit to 0.      |

|     |          |                  |      | 0: NACK receive interrupt request (NAKI) is disabled.                                                                                                                                                                                                                                                                               |

|     |          |                  |      | 1: NACK receive interrupt request (NAKI) is enabled.                                                                                                                                                                                                                                                                                |

|     |          |                  |      |                                                                                                                                                                                                                                                                                                                                     |

| D:4 |          | Initial | D // A/ | Description                                                                                                                                                                                           |

|-----|----------|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W     | Description                                                                                                                                                                                           |

| 4   | NACKF    | 0       | R/W     | No Acknowledge Detection Flag                                                                                                                                                                         |

|     |          |         |         | [Setting condition]                                                                                                                                                                                   |

|     |          |         |         | <ul> <li>When no acknowledge is detected from the receive<br/>device in transmission while the ACKE bit in ICIER is<br/>1</li> </ul>                                                                  |

|     |          |         |         | [Clearing condition]                                                                                                                                                                                  |

|     |          |         |         | • When 0 is written in NACKF after reading NACKF = 1                                                                                                                                                  |

| 3   | STOP     | 0       | R/W     | Stop Condition Detection Flag                                                                                                                                                                         |

|     |          |         |         | [Setting Conditions]                                                                                                                                                                                  |

|     |          |         |         | In master mode, when a stop condition is detected     after frame transfer                                                                                                                            |

|     |          |         |         | • In slave mode, when a stop condition is detected after<br>the general call address or the first byte slave<br>address, next to detection of start condition, accords<br>with the address set in SAR |

|     |          |         |         | [Clearing Condition]                                                                                                                                                                                  |

|     |          |         |         | • When 0 is written in STOP after reading STOP = 1                                                                                                                                                    |

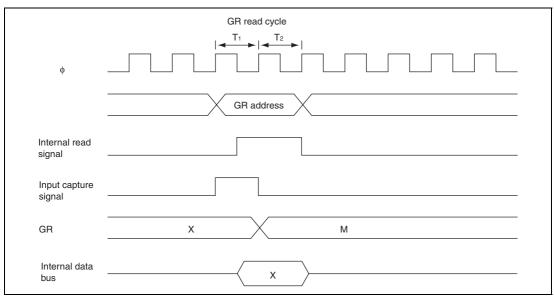

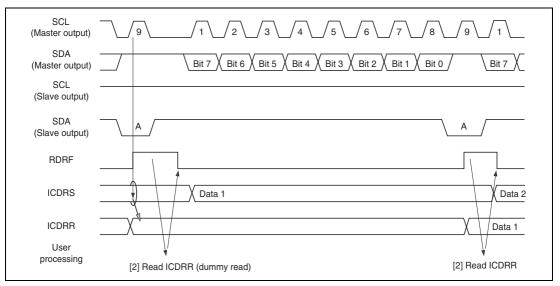

Figure 17.7 Master Receive Mode Operation Timing (1)

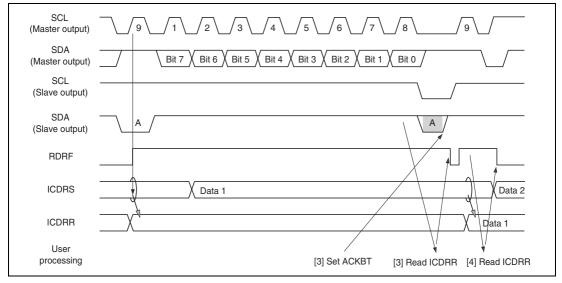

- 3. Read ICDRR every time RDRF is set. If 8th receive clock pulse falls while RDRF is 1, SCL is fixed low until ICDRR is read. The change of the acknowledge before reading ICDRR, to be returned to the master device, is reflected to the next transmit frame.

- 4. The last byte data is read by reading ICDRR.

Figure 17.11 Slave Receive Mode Operation Timing (1)

# 18.2 Input/Output Pins

Table 18.1 summarizes the input pins used by the A/D converter. The 8 analog input pins are divided into two groups; analog input pins 0 to 3 (AN0 to AN3) comprising group 0, analog input pins 4 to 7 (AN4 to AN7) comprising group 1. The AVcc pin is the power supply pin for the analog block in the A/D converter.

| Pin Name                       | Abbreviation     | I/O   | Function                                           |

|--------------------------------|------------------|-------|----------------------------------------------------|

| Analog power supply pin        | AV <sub>cc</sub> | Input | Analog block power supply                          |

| Analog input pin 0             | AN0              | Input | Group 0 analog input                               |

| Analog input pin 1             | AN1              | Input | _                                                  |

| Analog input pin 2             | AN2              | Input | _                                                  |

| Analog input pin 3             | AN3              | Input | _                                                  |

| Analog input pin 4             | AN4              | Input | Group 1 analog input                               |

| Analog input pin 5             | AN5              | Input | _                                                  |

| Analog input pin 6             | AN6              | Input | _                                                  |

| Analog input pin 7             | AN7              | Input | _                                                  |

| A/D external trigger input pin | ADTRG            | Input | External trigger input for starting A/D conversion |

#### Table 18.1 Pin Configuration

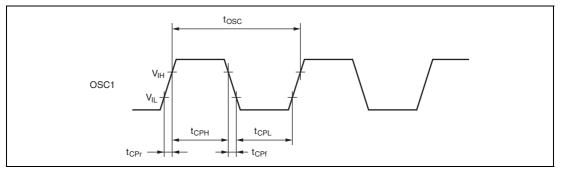

### 23.3.3 AC Characteristics

#### Table 23.13 AC Characteristics

$V_{\rm cc}$  = 2.7 to 5.5 V,  $V_{\rm ss}$  = 0.0 V,  $T_{\rm a}$  = –20 to +75°C, unless otherwise indicated.

|                                                          |                     | Applicable    |                                          |      | Value  |      | Reference                               |             |

|----------------------------------------------------------|---------------------|---------------|------------------------------------------|------|--------|------|-----------------------------------------|-------------|

| Item                                                     | Symbol              | Pins          | Test Condition                           | Min  | Тур    | Max  | Unit                                    | Figure      |

| System clock oscillation                                 | f <sub>osc</sub>    | OSC1,<br>OSC2 | $V_{cc} = 4.0 \text{ to } 5.5 \text{ V}$ | 2.0  | —      | 20.0 | MHz                                     | *1          |

| frequency                                                |                     |               |                                          | 2.0  |        | 10.0 |                                         |             |

| System clock (                                           | t <sub>cyc</sub>    |               |                                          | 1    | —      | 64   | t <sub>osc</sub>                        | *2          |

| cycle time                                               |                     |               |                                          | _    | —      | 12.8 | μs                                      |             |

| Subclock<br>oscillation<br>frequency                     | f <sub>w</sub>      | X1, X2        |                                          | _    | 32.768 | _    | kHz                                     |             |

| Watch clock $(\phi_w)$ cycle time                        | t <sub>w</sub>      | X1, X2        |                                          | —    | 30.5   | _    | μs                                      |             |

| Subclock ( $\phi_{SUB}$ ) cycle time                     | t <sub>subcyc</sub> |               |                                          | 2    | _      | 8    | t <sub>w</sub>                          | *2          |

| Instruction cycle time                                   |                     |               |                                          | 2    | _      | _    | t <sub>cyc</sub><br>t <sub>subcyc</sub> |             |

| Oscillation<br>stabilization time<br>(crystal resonator) | t <sub>rc</sub>     | OSC1,<br>OSC2 |                                          | _    | _      | 10.0 | ms                                      |             |

| Oscillation<br>stabilization time<br>(ceramic resonator) | t <sub>rc</sub>     | OSC1,<br>OSC2 |                                          | _    | _      | 5.0  | ms                                      |             |

| Oscillation stabilization time                           | t <sub>rcx</sub>    | X1, X2        |                                          | —    | —      | 2.0  | S                                       |             |

| External clock                                           | t <sub>CPH</sub>    | OSC1          | $V_{cc}$ = 4.0 to 5.5 V                  | 20.0 |        | —    | ns                                      | Figure 23.1 |

| high width                                               |                     |               |                                          | 40.0 |        | —    | _                                       |             |

| External clock                                           | t <sub>CPL</sub>    | OSC1          | $V_{cc}$ = 4.0 to 5.5 V                  | 20.0 | —      | —    | ns                                      | -           |

| low width                                                |                     |               |                                          | 40.0 | —      | _    | _                                       |             |

| External clock                                           | t <sub>CPr</sub>    | OSC1          | $V_{\rm cc}$ = 4.0 to 5.5 V              |      |        | 10.0 | ns                                      | -           |

| rise time                                                |                     |               |                                          | _    |        | 15.0 | _                                       | _           |

| External clock                                           | t <sub>CPf</sub>    | OSC1          | $V_{\rm cc}$ = 4.0 to 5.5 V              | _    |        | 10.0 | ns                                      |             |

| fall time                                                |                     |               |                                          | —    | —      | 15.0 |                                         |             |

### 23.3.8 Power-On Reset Circuit Characteristics (Optional)

#### Table 23.20 Power-On Reset Circuit Characteristics

$V_{ss} = 0.0 \text{ V}, T_a = -20 \text{ to } +75^{\circ}\text{C}$ , unless otherwise indicated.

|                                                   |                  | Test      | _   |     |     |      |

|---------------------------------------------------|------------------|-----------|-----|-----|-----|------|

| Item                                              | Symbol           | Condition | Min | Тур | Max | Unit |

| Pull-up resistance of $\overline{\text{RES}}$ pin | R <sub>RES</sub> |           | 100 | 150 | _   | kΩ   |

| Power-on reset start voltage*                     | $V_{por}$        |           | _   | —   | 100 | mV   |

Note: \* The power-supply voltage (Vcc) must fall below Vpor = 100 mV and then rise after charge of the RES pin is removed completely. In order to remove charge of the RES pin, it is recommended that the diode be placed in the Vcc side. If the power-supply voltage (Vcc) rises from the point over 100 mV, a power-on reset may not occur.

# 23.4 Operation Timing

Figure 23.1 System Clock Input Timing

|          |                    |              |     | Addressing Mode and<br>Instruction Length (bytes) |      |           |             |     |          |        |   |                                                       |   |     |       |      |     | No.<br>Stat | . of<br>es*1 |          |

|----------|--------------------|--------------|-----|---------------------------------------------------|------|-----------|-------------|-----|----------|--------|---|-------------------------------------------------------|---|-----|-------|------|-----|-------------|--------------|----------|

| Mnemonic |                    | Operand Size | ×   |                                                   | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | @ @ aa |   | Operation                                             |   | Con | ditio | n Co | ode |             | Normal       | Advanced |

|          |                    | ŏ            | XX# | Rn                                                | 0    | 0         | Ö           | 0   | 0        | 0      | Ι |                                                       | Т | н   | N     | z    | v   | с           | Ň            | Ad       |

| BLD      | BLD #xx:3, @ERd    | В            |     |                                                   | 4    |           |             |     |          |        |   | (#xx:3 of @ERd) $\rightarrow$ C                       | — | —   | -     | -    | -   | \$          | 6            | 6        |

|          | BLD #xx:3, @aa:8   | В            |     |                                                   |      |           |             | 4   |          |        |   | (#xx:3 of @aa:8) $\rightarrow$ C                      | — | —   | —     | -    | -   | 1           | 6            | 6        |

| BILD     | BILD #xx:3, Rd     | В            |     | 2                                                 |      |           |             |     |          |        |   | $\neg$ (#xx:3 of Rd8) $\rightarrow$ C                 | — | —   | —     | -    | -   | 1           | 2            | 2        |

|          | BILD #xx:3, @ERd   | В            |     |                                                   | 4    |           |             |     |          |        |   | $\neg$ (#xx:3 of @ERd) $\rightarrow$ C                | — | —   | —     | -    | —   | $\uparrow$  | 6            | 6        |