Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                       |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 33MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI, SmartCard                                         |

| Peripherals                | DMA, POR, PWM, WDT                                                             |

| Number of I/O              | 96                                                                             |

| Program Memory Size        | -                                                                              |

| Program Memory Type        | ROMIess                                                                        |

| EEPROM Size                | <u>.</u>                                                                       |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b; D/A 6x8b                                                           |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 144-LQFP                                                                       |

| Supplier Device Package    | 144-LQFP (20x20)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/d12373rvfq33v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com )

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

(1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

Rev.7.00 Mar. 18, 2009 page ii of lxvi REJ09B0109-0700

| Item                                                                                          | Page | Revision (See Manual for Details)   |

|-----------------------------------------------------------------------------------------------|------|-------------------------------------|

| 26.4.3 Bus Timing                                                                             | 1074 | Figure amended                      |

| Figure 26.11 Basic<br>Bus Timing: Three-<br>State Access (CS<br>Assertion Period<br>Extended) |      | EDACK2, EDACK3                      |

| Figure 26.14 DRAM<br>Access Timing: Two-<br>State Access                                      | 1077 | Figure amended                      |

| Figure 26.15 DRAM<br>Access Timing: Two-<br>State Access, One<br>Wait                         | 1078 | Figure amended       EDACK2, EDACK3 |

| Figure 26.16 DRAM<br>Access Timing: Two-<br>State Burst Access                                | 1079 | Figure amended                      |

| Figure 26.17 DRAM<br>Access Timing: Three-<br>State Access (RAST =<br>1)                      | 1080 | Figure amended                      |

| Figure 26.18 DRAM<br>Access Timing: Three-<br>State Burst Access                              | 1081 | Figure amended                      |

| 26.4.4 DMAC and EXDMAC Timing                                                                 | 1088 | Figure amended                      |

| Figure 26.28 DMAC<br>and EXDMAC Single<br>Address Transfer<br>Timing: Two-State<br>Access     |      | EDACK2, EDACK3                      |

| Figure 26.29 DMAC<br>and EXDMAC Single<br>Address Transfer                                    | 1089 | Figure amended                      |

| Timing: Three-State<br>Access                                                                 |      | EDACK2, EDACK3                      |

Rev.7.00 Mar. 18, 2009 page xxi of lxvi REJ09B0109-0700

# 4.7 Stack Status after Exception Handling

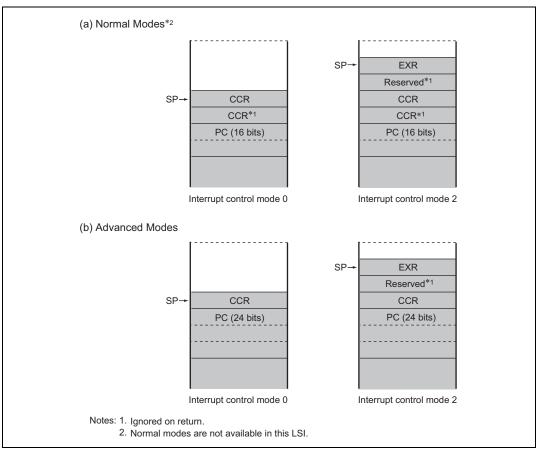

Figure 4.3 shows the stack after completion of trap instruction exception handling and interrupt exception handling.

Figure 4.3 Stack Status after Exception Handling

# 6.12 Bus Arbitration

This LSI has a bus arbiter that arbitrates bus mastership operations (bus arbitration).

There are four bus masters—the CPU, DTC, DMAC, and EXDMAC<sup>\*</sup>—that perform read/write operations when they have possession of the bus. Each bus master requests the bus by means of a bus request signal. The bus arbiter determines priorities at the prescribed timing, and permits use of the bus by means of a bus request acknowledge signal. The selected bus master then takes possession of the bus and begins its operation.

Note: \* The EXDMAC is not supported by the H8S/2375, H8S/2375R, H8S/2373, and H8S/2373R.

### 6.12.1 Operation

The bus arbiter detects the bus masters' bus request signals, and if the bus is requested, sends a bus request acknowledge signal to the bus master. If there are bus requests from more than one bus master, the bus request acknowledge signal is sent to the one with the highest priority. When a bus master receives the bus request acknowledge signal, it takes possession of the bus until that signal is canceled.

The order of priority of the bus mastership is as follows:

(High) EXDMAC\* > DMAC > DTC > CPU (Low)

An internal bus access by internal bus masters except the EXDMAC<sup>\*</sup> and external bus release, a refresh when the CBRM bit is 0, and an external bus access by the EXDMAC<sup>\*</sup> can be executed in parallel.

If an external bus release request, a refresh request, and an external access by an internal bus master occur simultaneously, the order of priority is as follows:

(High) Refresh > EXDMAC<sup>\*</sup> > External bus release (Low)

(High) External bus release > External access by internal bus master except EXDMAC\* (Low)

As a refresh when the CBRM bit in REFCR is cleared to 0 and an external access other than to DRAM space by an internal bus master can be executed simultaneously, there is no relative order of priority for these two operations.

Note: \* The EXDMAC is not supported by the H8S/2375, H8S/2375R, H8S/2373, and H8S/2373R.

#### 9.7.4 Software Activation

An example is shown in which the DTC is used to transfer a block of 128 bytes of data by means of software activation. The transfer source address is H'1000 and the destination address is H'2000. The vector number is H'60, so the vector address is H'04C0.

- Set MRA to incrementing source address (SM1 = 1, SM0 = 0), incrementing destination address (DM1 = 1, DM0 = 0), block transfer mode (MD1 = 1, MD0 = 0), and byte size (Sz = 0). The DTS bit can have any value. Set MRB for one block transfer by one interrupt (CHNE = 0). Set the transfer source address (H'1000) in SAR, the destination address (H'2000) in DAR, and 128 (H'8080) in CRA. Set 1 (H'0001) in CRB.

- 2. Set the start address of the register information at the DTC vector address (H'04C0).

- 3. Check that the SWDTE bit in DTVECR is 0. Check that there is currently no transfer activated by software.

- 4. Write 1 to the SWDTE bit and the vector number (H'60) to DTVECR. The write data is H'E0.

- 5. Read DTVECR again and check that it is set to the vector number (H'60). If it is not, this indicates that the write failed. This is presumably because an interrupt occurred between steps 3 and 4 and led to a different software activation. To activate this transfer, go back to step 3.

- 6. If the write was successful, the DTC is activated and a block of 128 bytes of data is transferred.

- 7. After the transfer, an SWDTEND interrupt occurs. The interrupt handling routine should clear the SWDTE bit to 0 and perform other wrap-up processing.

## 9.8 Usage Notes

### 9.8.1 Module Stop Mode Setting

DTC operation can be disabled or enabled using the module stop control register. The initial setting is for DTC operation to be enabled. Register access is disabled by setting module stop mode. Module stop mode cannot be set while the DTC is activated. For details, refer to section 24, Power-Down Modes.

### 9.8.2 On-Chip RAM

The MRA, MRB, SAR, DAR, CRA, and CRB registers are all located in on-chip RAM. When the DTC is used, the RAME bit in SYSCR must not be cleared to 0.

# 10.2 Port 2

Port 2 is an 8-bit I/O port that also has other functions. The port 2 has the following registers.

- Port 2 data direction register (P2DDR)

- Port 2 data register (P2DR)

- Port 2 register (PORT2)

### 10.2.1 Port 2 Data Direction Register (P2DDR)

The individual bits of P2DDR specify input or output for the pins of port 2.

P2DDR cannot be read; if it is, an undefined value will be read.

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                             |

|-----|----------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------|

| 7   | P27DDR   | 0             | W   | When a pin function is specified to a general                                                                           |

| 6   | P26DDR   | 0             | W   | <ul> <li>purpose I/O, setting this bit to 1 makes the</li> <li>corresponding port 1 pin an output pin, while</li> </ul> |

| 5   | P25DDR   | 0             | W   | clearing this bit to 0 makes the pin an input pin.                                                                      |

| 4   | P24DDR   | 0             | W   | _                                                                                                                       |

| 3   | P23DDR   | 0             | W   |                                                                                                                         |

| 2   | P22DDR   | 0             | W   |                                                                                                                         |

| 1   | P21DDR   | 0             | W   | _                                                                                                                       |

| 0   | P20DDR   | 0             | W   | —                                                                                                                       |

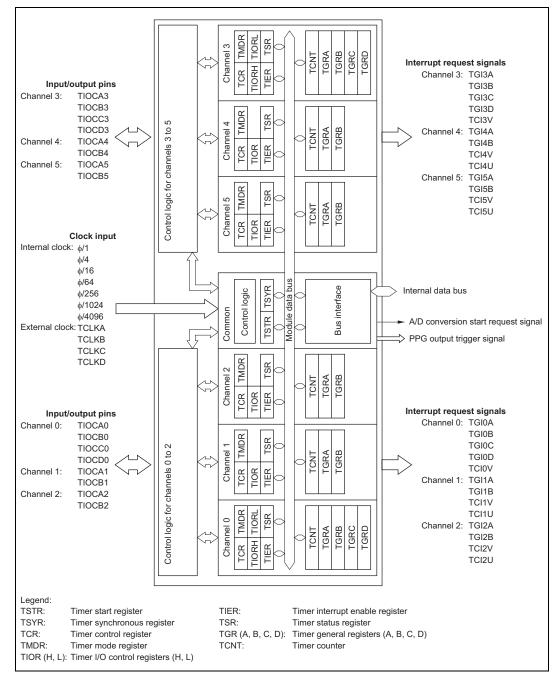

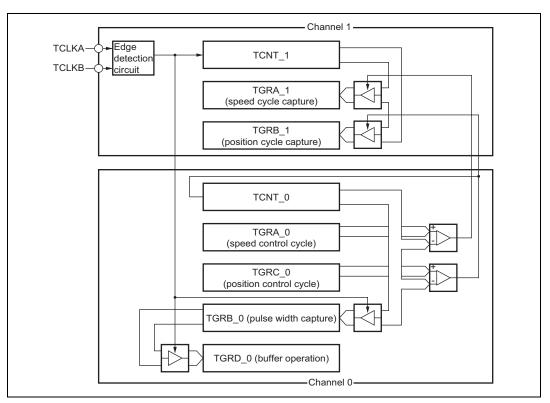

Figure 11.1 Block Diagram of TPU

Rev.7.00 Mar. 18, 2009 page 548 of 1136 REJ09B0109-0700

| Table | 11.13 | TIORL | 0 |

|-------|-------|-------|---|

|-------|-------|-------|---|

|               |               |               |               | Description                         |                                               |  |  |  |  |

|---------------|---------------|---------------|---------------|-------------------------------------|-----------------------------------------------|--|--|--|--|

| Bit 7<br>IOD3 | Bit 6<br>IOD2 | Bit 5<br>IOD1 | Bit 4<br>IOD0 | TGRD_0<br>Function                  | TIOCD0 Pin Function                           |  |  |  |  |

| 0             | 0             | 0             | 0             | Output                              | Output disabled                               |  |  |  |  |

|               |               |               | 1             | compare<br>register <sup>*2</sup>   | Initial output is 0 output                    |  |  |  |  |

|               |               |               |               | register                            | 0 output at compare match                     |  |  |  |  |

|               |               | 1             | 0             | _                                   | Initial output is 0 output                    |  |  |  |  |

|               |               |               |               |                                     | 1 output at compare match                     |  |  |  |  |

|               |               |               | 1             | _                                   | Initial output is 0 output                    |  |  |  |  |

|               |               |               |               |                                     | Toggle output at compare match                |  |  |  |  |

|               | 1             | 0             | 0             | Output disabled                     |                                               |  |  |  |  |

|               |               |               | 1             |                                     | Initial output is 1 output                    |  |  |  |  |

|               |               |               |               |                                     | 0 output at compare match                     |  |  |  |  |

|               |               | 1             | 0             |                                     | Initial output is 1 output                    |  |  |  |  |

|               |               |               |               |                                     | 1 output at compare match                     |  |  |  |  |

|               |               |               | 1             | _                                   | Initial output is 1 output                    |  |  |  |  |

|               |               |               |               |                                     | Toggle output at compare match                |  |  |  |  |

| 1             | 0             | 0             | 0             | Input                               | Capture input source is TIOCD0 pin            |  |  |  |  |

|               |               |               |               | capture<br>– register <sup>*2</sup> | Input capture at rising edge                  |  |  |  |  |

|               |               |               | 1             |                                     | Capture input source is TIOCD0 pin            |  |  |  |  |

|               |               |               |               |                                     | Input capture at falling edge                 |  |  |  |  |

| 1 ×           |               |               |               |                                     | Capture input source is TIOCD0 pin            |  |  |  |  |

|               |               |               |               |                                     | Input capture at both edges                   |  |  |  |  |

|               | 1             | х             | ×             |                                     | Capture input source is channel 1/count clock |  |  |  |  |

|               |               |               |               |                                     | Input capture at TCNT_1 count-up/count-down*1 |  |  |  |  |

Legend: x: Don't care

Notes: 1. When bits TPSC2 to TPSC0 in TCR\_1 are set to B'000 and  $\phi/1$  is used as the TCNT\_1 count clock, this setting is invalid and input capture is not generated.

2. When the BFB bit in TMDR\_0 is set to 1 and TGRD\_0 is used as a buffer register, this setting is invalid and input capture/output compare is not generated.

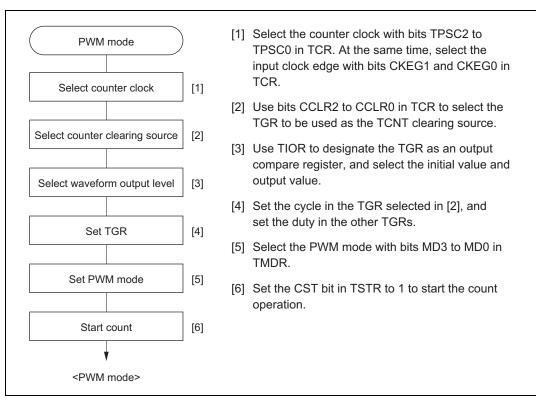

**Example of PWM Mode Setting Procedure:** Figure 11.20 shows an example of the PWM mode setting procedure.

Figure 11.20 Example of PWM Mode Setting Procedure

**Examples of PWM Mode Operation:** Figure 11.21 shows an example of PWM mode 1 operation.

In this example, TGRA compare match is set as the TCNT clearing source, 0 is set for the TGRA initial output value and output value, and 1 is set as the TGRB output value.

In this case, the value set in TGRA is used as the cycle, and the values set in TGRB registers as the duty cycle.

Figure 11.29 Phase Counting Mode Application Example

### **11.5** Interrupt Sources

There are three kinds of TPU interrupt source: TGR input capture/compare match, TCNT overflow, and TCNT underflow. Each interrupt source has its own status flag and enable/disable bit, allowing generation of interrupt request signals to be enabled or disabled individually.

When an interrupt request is generated, the corresponding status flag in TSR is set to 1. If the corresponding enable/disable bit in TIER is set to 1 at this time, an interrupt is requested. The interrupt request is cleared by clearing the status flag to 0.

Relative channel priorities can be changed by the interrupt controller, but the priority order within a channel is fixed. For details, see section 5, Interrupt Controller.

Table 11.36 lists the TPU interrupt sources.

# Renesas

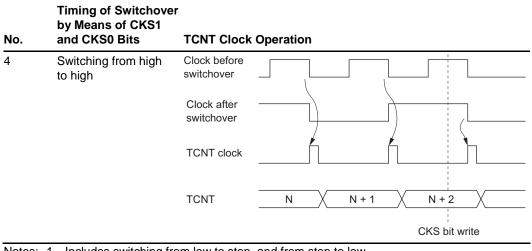

- Notes: 1. Includes switching from low to stop, and from stop to low.

- 2. Includes switching from stop to high.

- 3. Includes switching from high to stop.

- 4. Generated on the assumption that the switchover is a falling edge; TCNT is incremented.

#### 13.8.6 Mode Setting with Cascaded Connection

If 16-bit counter mode and compare match count mode are specified at the same time, input clocks for TCNT\_0 and TCNT\_1 are not generated, and the counter stops. Do not specify 16-bit counter and compare match count modes simultaneously.

#### 13.8.7 Interrupts in Module Stop Mode

If module stop mode is entered when an interrupt has been requested, it will not be possible to clear the CPU interrupt source or the DTC and DMAC activation source. Interrupts should therefore be disabled before entering module stop mode.

## Renesas

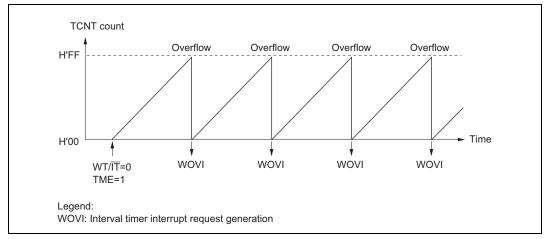

Figure 14.3 Operation in Interval Timer Mode

## 14.5 Interrupt Source

During interval timer mode operation, an overflow generates an interval timer interrupt (WOVI). The interval timer interrupt is requested whenever the OVF flag is set to 1 in TCSR. OVF must be cleared to 0 in the interrupt handling routine.

#### Table 14.2WDT Interrupt Source

| Name | Interrupt Source | Interrupt Flag | DTC Activation |

|------|------------------|----------------|----------------|

| WOVI | TCNT overflow    | OVF            | Impossible     |

### 14.6 Usage Notes

#### 14.6.1 Notes on Register Access

The watchdog timer's TCNT, TCSR, and RSTCSR registers differ from other registers in being more difficult to write to. The procedures for writing to and reading these registers are given below.

#### Writing to TCNT, TCSR, and RSTCSR

TCNT and TCSR must be written to by a word transfer instruction. They cannot be written to by a byte transfer instruction.

#### 21.1.2 Mode Comparison

The comparison table of programming and erasing related items about boot mode, user program mode, user boot mode, and PROM mode is shown in table 21.1.

| <b>Table 21.1</b> | <b>Comparison of Programming Modes</b> |

|-------------------|----------------------------------------|

|-------------------|----------------------------------------|

|                                        | Boot mode                       | User program<br>mode         | User boot mode                  | PROM mode                 |

|----------------------------------------|---------------------------------|------------------------------|---------------------------------|---------------------------|

| Programming/<br>erasing<br>environment | On-board<br>programming         | On-board<br>programming      | On-board<br>programming         | Off-board programming     |

| Programming/<br>erasing enable<br>MAT  | User MAT<br>User boot MAT       | User MAT                     | User MAT                        | User MAT<br>User boot MAT |

| All erasure                            | ○ (Automatic)                   | 0                            | 0                               | ○ (Automatic)             |

| Block division<br>erasure              | O <sup>*1</sup>                 | 0                            | 0                               | ×                         |

| Program data<br>transfer               | From host via SCI               | From optional device via RAM | From optional device via RAM    | Via programmer            |

| Reset initiation<br>MAT                | Embedded progran<br>storage MAT | n User MAT                   | User boot MAT*2                 |                           |

| Transition to user mode                | Changing mode setting and reset | Changing FLSHE bit           | Changing mode setting and reset | _                         |

Notes: 1. All-erasure is performed. After that, the specified block can be erased.

Firstly, the reset vector is fetched from the embedded program storage MAT. After the flash memory related registers are checked, the reset vector is fetched from the user boot MAT.

- The user boot MAT can be programmed or erased only in boot mode and PROM mode.

- The user MAT and user boot MAT are erased in boot mode. Then, the user MAT and user boot MAT can be programmed by means of the command method. However, the contents of the MAT cannot be read until this state.

Only user boot MAT is programmed and the user MAT is programmed in user boot mode or only user MAT is programmed because user boot mode is not used.

• The boot operation of the optional interface can be performed by the mode pin setting different from user program mode in user boot mode.

# Renesas

# Section 25 List of Registers

The address list gives information on the on-chip I/O register addresses, how the register bits are configured, and the register states in each operating mode. The information is given as shown below.

- 1. Register addresses (address order)

- Registers are listed from the lower allocation addresses.

- Reserved addresses are indicated by in the register name column. Do not access to reserved addresses.

- For the addresses of 16 or 32 bits, the MSB-side address is described.

- Registers are classified by functional modules.

- The access size is indicated.

- 2. Register bits

- Bit configurations of the registers are described in the same order as the register addresses.

- Reserved bits are indicated by in the bit name column.

- For the registers of 16 or 32 bits, the MSB is described first.

- 3. Register states in each operating mode

- Register states are described in the same order as the register addresses.

- The register states described here are for the basic operating modes. If there is a specific reset for an on-chip peripheral module, refer to the section on that on-chip peripheral module.

## 25.1 Register Addresses (Address Order)

The data bus width indicates the numbers of bits by which the register is accessed.

The number of access states indicates the number of states based on the specified reference clock.

#### Section 25 List of Registers

| Register<br>Abbreviation | Reset       | High-<br>Speed | Clock<br>Division | Sleep | Module<br>Stop | All Module<br>Clock Stop |   | Hardware<br>Standby | Module |

|--------------------------|-------------|----------------|-------------------|-------|----------------|--------------------------|---|---------------------|--------|

| EBR1                     | Initialized | _              |                   | _     |                | _                        | _ | Initialized         | FLASH  |

| EBR2                     | Initialized |                |                   | _     | _              |                          |   | Initialized         | -      |

| FVACR <sup>*2</sup>      | Initialized |                |                   | _     | _              |                          |   | Initialized         | -      |

| FVADRR*2                 | Initialized | _              | _                 | _     | _              | _                        | _ | Initialized         | -      |

| FVADRE*2                 | Initialized | _              | _                 | _     | _              | _                        | _ | Initialized         | -      |

| FVADRH*2                 | Initialized | _              | _                 |       | _              |                          | _ | Initialized         | -      |

| FVADRL*2                 | Initialized | _              | _                 | _     | _              | _                        | _ | Initialized         | -      |

| TCR_0                    | Initialized | _              | _                 | _     | _              | _                        | _ | Initialized         | TPU_0  |

| TMDR_0                   | Initialized | _              | _                 |       | _              | _                        | _ | Initialized         | -      |

| TIORH_0                  | Initialized | _              | _                 | _     | _              | _                        | _ | Initialized         | -      |

| TIORL_0                  | Initialized |                |                   | _     | _              |                          |   | Initialized         | -      |

| TIER_0                   | Initialized |                |                   | _     | _              |                          |   | Initialized         | -      |

| TSR_0                    | Initialized | _              | _                 | _     | _              | _                        | _ | Initialized         | -      |

| TCNT_0                   | Initialized |                |                   | _     | _              |                          |   | Initialized         | -      |

| TGRA_0                   | Initialized |                |                   | _     | _              |                          |   | Initialized         | -      |

| TGRB_0                   | Initialized | _              | _                 | _     | _              | _                        | _ | Initialized         | -      |

| TGRC_0                   | Initialized | _              | _                 | _     | _              | _                        | _ | Initialized         | -      |

| TGRD_0                   | Initialized | _              | _                 |       | _              | _                        | _ | Initialized         | -      |

| TCR_1                    | Initialized | _              | _                 |       | _              |                          | _ | Initialized         | TPU_1  |

| TMDR_1                   | Initialized | _              | _                 | _     | _              | _                        | _ | Initialized         | -      |

| TIOR_1                   | Initialized |                |                   | _     | _              |                          |   | Initialized         | -      |

| TIER_1                   | Initialized | _              | _                 | _     | _              | _                        | _ | Initialized         | -      |

| TSR_1                    | Initialized |                |                   | _     | _              |                          |   | Initialized         | -      |

| TCNT_1                   | Initialized |                |                   | _     | _              |                          |   | Initialized         | -      |

| TGRA_1                   | Initialized | _              | _                 | _     | _              | _                        | _ | Initialized         | -      |

| TGRB_1                   | Initialized |                |                   | _     | _              |                          |   | Initialized         | -      |

| TCR_2                    | Initialized | _              | _                 | _     | _              | _                        | _ | Initialized         | TPU_2  |

| TMDR_2                   | Initialized |                | _                 |       | _              | _                        |   | Initialized         | -      |

| TIOR_2                   | Initialized | _              |                   |       | _              | _                        |   | Initialized         | _      |

| TIER_2                   | Initialized | _              | _                 | _     | _              | _                        | _ | Initialized         | -      |

| TSR_2                    | Initialized | _              | _                 | _     | _              | _                        | _ | Initialized         | _      |

#### 26.2.2 DC Characteristics

#### Table 26.15 DC Characteristics

$\begin{array}{ll} \mbox{Conditions:} & V_{CC} = 3.0 \mbox{ V to } 3.6 \mbox{ V, } AV_{CC} = 3.0 \mbox{ V to } 3.6 \mbox{ V, } V_{ref} = 3.0 \mbox{ V to } AV_{CC}, \\ & V_{SS} = AV_{SS} = 0 \mbox{ V}^{*1}, \mbox{ } T_a = -20^{\circ}\mbox{C to } +75^{\circ}\mbox{C (regular specifications)}, \\ & T_a = -40^{\circ}\mbox{C to } +85^{\circ}\mbox{C (wide-range specifications)} \end{array}$

| Item                  |                                                                                                                    | Symbol          | Min.                       | Тур. | Max.                       | Unit | Test<br>Conditions        |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------|------|----------------------------|------|---------------------------|

| Schmitt               | Port 1, port 2,                                                                                                    | VT <sup>-</sup> | $V_{CC} \times 0.2$        |      | _                          | V    | _                         |

|                       | P50 to P53 <sup>*2</sup> ,<br>port 6 <sup>*2</sup> , port 8 <sup>*2</sup> ,                                        | $VT^+$          | _                          |      | $V_{CC} \times 0.7$        | V    | _                         |

| voltage               | PA4 to PA7 <sup>*2</sup> ,<br>PF1 <sup>*2</sup> , PF2 <sup>*2</sup> ,<br>PH2 <sup>*2</sup> , PH3 <sup>*2</sup>     | $VT^+ - VT^-$   | $V_{CC} \times 0.07$       |      |                            | V    | -                         |

| Input high<br>voltage | STBY,<br>MD2 to MD0                                                                                                | V <sub>IH</sub> | $V_{CC} \times 0.9$        |      | V <sub>CC</sub> +0.3       | V    |                           |

|                       | RES, NMI, EMLE                                                                                                     | -               | $V_{CC} \times 0.9$        |      | V <sub>CC</sub> +0.3       | V    | -                         |

|                       | EXTAL                                                                                                              | -               | $V_{\text{CC}} \times 0.7$ | _    | V <sub>CC</sub> +0.3       | V    | -                         |

|                       | Port 3,<br>P50 to P53 <sup>*3</sup> ,<br>ports 6 <sup>*3</sup> and 8 <sup>*3</sup> ,<br>ports A to H <sup>*3</sup> | -               | 2.2                        | _    | V <sub>CC</sub> +0.3       | V    | -                         |

|                       | Port 4, Port 9                                                                                                     | -               | 2.2                        |      | AV <sub>CC</sub> +0.3      | V    | -                         |

| Input low<br>voltage  | RES, STBY,<br>MD2 to MD0,<br>EMLE                                                                                  | V <sub>IL</sub> | -0.3                       | _    | $V_{CC} 	imes 0.1$         | V    |                           |

|                       | NMI, EXTAL                                                                                                         | -               | -0.3                       |      | $V_{\text{CC}} \times 0.2$ | V    | -                         |

|                       | Ports 3 to $6^{*3}$ ,<br>Port $8^{*3}$ ,<br>ports A to $H^{*3}$ ,<br>port 9                                        | -               | -0.3                       | _    | $V_{CC} 	imes 0.2$         | V    | -                         |

|                       | All output pins                                                                                                    | V <sub>OH</sub> | $V_{CC}$ –0.5              |      | _                          | V    | $I_{OH}=-200~\mu A$       |

| voltage               |                                                                                                                    |                 | V <sub>cc</sub> -1.0       |      |                            | V    | $I_{OH} = -1 \text{ mA}$  |

| Output low            | All output pins                                                                                                    | V <sub>OL</sub> |                            | —    | 0.4                        | V    | $I_{OL} = 1.6 \text{ mA}$ |

| voltage               | P32 to P35*4                                                                                                       | -               |                            |      | 0.5                        | V    | $I_{OL} = 8.0 \text{ mA}$ |

Notes: 1. When the A/D and D/A converters are not used, the AV<sub>CC</sub>, V<sub>ref</sub>, and AV<sub>SS</sub> pins should not be open. Connect the AV<sub>CC</sub> and V<sub>ref</sub> pins to V<sub>CC</sub>, and the AV<sub>SS</sub> pin to V<sub>SS</sub>.

2. When used as  $\overline{IRQ0}$  to  $\overline{IRQ15}$ .

3. When used as other than  $\overline{\text{IRQ0}}$  to  $\overline{\text{IRQ15}}$ .

4. When used as SCL0, SCL1, SDA0, and SDA1.

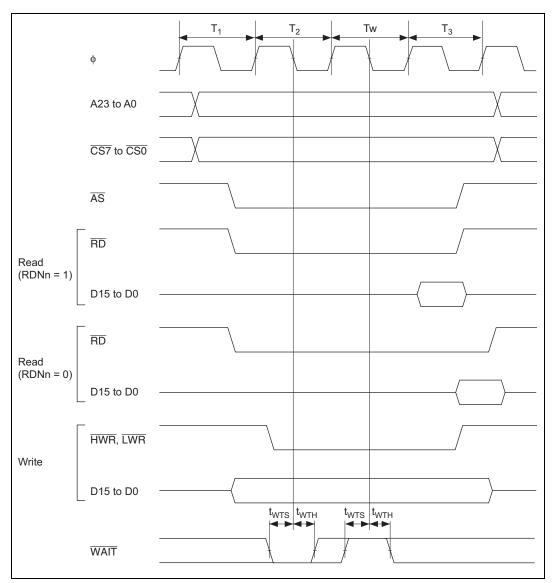

#### Table 26.34Bus Timing (2)

$\begin{array}{ll} \mbox{Conditions:} & V_{CC} = 3.0 \mbox{ V to } 3.6 \mbox{ V}, \mbox{AV}_{CC} = 3.0 \mbox{ V to } 3.6 \mbox{ V}, \mbox{V}_{ref} = 3.0 \mbox{ V to } AV_{CC}, \mbox{V}_{SS} = AV_{SS} = \\ & 0 \mbox{ V}, \mbox{$\phi$} = 8 \mbox{ MHz to } 34 \mbox{ MHz}, \mbox{$T_a$} = -20^{\circ}\mbox{C to } +75^{\circ}\mbox{C} \mbox{ (regular specifications)}, \\ & T_a = -40^{\circ}\mbox{C to } +85^{\circ}\mbox{C} \mbox{ (wide-range specifications)} \end{array}$

| Item                       | Symbol             | Min.                             | Max. | Unit | Test Conditions |

|----------------------------|--------------------|----------------------------------|------|------|-----------------|

| WR delay time 1            | t <sub>WRD1</sub>  |                                  | 15   | ns   | Figures 26.7 to |

| WR delay time 2            | t <sub>WRD2</sub>  |                                  | 15   | ns   | 26.20           |

| WR pulse width 1           | t <sub>wsw1</sub>  | $1.0\times t_{cyc}{-}13$         | _    | ns   | _               |

| WR pulse width 2           | t <sub>WSW2</sub>  | $1.5 \times t_{\text{cyc}}{-}13$ | _    | ns   |                 |

| Write data delay time      | t <sub>WDD</sub>   |                                  | 23   | ns   | —               |

| Write data setup time 1    | t <sub>WDS1</sub>  | $0.5 \times t_{\text{cyc}}{-}15$ | _    | ns   |                 |

| Write data setup time 2    | t <sub>WDS2</sub>  | $1.0\times t_{cyc}{-}15$         | _    | ns   | _               |

| Write data setup time 3    | t <sub>WDS3</sub>  | $1.5 	imes t_{cyc}$ -15          | _    | ns   |                 |

| Write data hold time 1     | t <sub>WDH1</sub>  | $0.5 \times t_{\text{cyc}}{-}13$ | _    | ns   |                 |

| Write data hold time 2     | t <sub>WDH2</sub>  | $1.0 \times t_{\text{cyc}}{-}13$ | _    | ns   |                 |

| Write data hold time 3     | t <sub>WDH3</sub>  | $1.5 \times t_{\text{cyc}}{-}13$ | _    | ns   |                 |

| Write command setup time 1 | t <sub>WCS1</sub>  | $0.5 \times t_{\text{cyc}}{-}10$ | _    | ns   |                 |

| Write command setup time 2 | t <sub>WCS2</sub>  | $1.0 \times t_{\text{cyc}}{-}10$ | _    | ns   |                 |

| Write command hold time 1  | t <sub>WCH1</sub>  | $0.5 \times t_{\text{cyc}}{-}10$ | _    | ns   |                 |

| Write command hold time 2  | t <sub>WCH2</sub>  | $1.0 \times t_{\text{cyc}}{-}10$ | _    | ns   |                 |

| Read command setup time 1  | t <sub>RCS1</sub>  | $1.5 \times t_{\text{cyc}}{-}10$ | _    | ns   |                 |

| Read command setup time 2  | t <sub>RCS2</sub>  | $2.0\times t_{cyc}{-}10$         | _    | ns   | _               |

| Read command hold time     | t <sub>RCH</sub>   | $0.5 \times t_{\text{cyc}}{-}10$ | _    | ns   | _               |

| CAS delay time 1           | t <sub>CASD1</sub> |                                  | 15   | ns   |                 |

| CAS delay time 2           | t <sub>CASD2</sub> | —                                | 15   | ns   |                 |

| CAS setup time 1           | t <sub>CSR1</sub>  | $0.5 \times t_{\text{cyc}}{-}10$ | _    | ns   |                 |

| CAS setup time 2           | t <sub>CSR2</sub>  | $1.5 \times t_{\text{cyc}}{-}10$ | _    | ns   | —               |

| CAS pulse width 1          | t <sub>CASW1</sub> | $1.0 \times t_{cyc}{-}20$        | _    | ns   |                 |

| CAS pulse width 2          | t <sub>CASW2</sub> | $1.5 \times t_{\text{cyc}}{-}20$ | _    | ns   |                 |

| CAS precharge time 1       | t <sub>CPW1</sub>  | $1.0\times t_{cyc}{-}20$         | _    | ns   |                 |

| CAS precharge time 2       | t <sub>CPW2</sub>  | $1.5 \times t_{\text{cyc}}{-}20$ | _    | ns   | —               |

| OE delay time 1            | t <sub>OED1</sub>  | _                                | 15   | ns   |                 |

| OE delay time 2            | t <sub>OED2</sub>  | —                                | 15   | ns   | —               |

| Precharge time 1           | t <sub>PCH1</sub>  | $1.0 \times t_{\text{cyc}}{-}20$ | _    | ns   | —               |

| Precharge time 2           | t <sub>PCH2</sub>  | $1.5 \times t_{cyc}{-}20$        |      | ns   |                 |

Rev.7.00 Mar. 18, 2009 page 1058 of 1136 REJ09B0109-0700

Figure 26.9 Basic Bus Timing: Three-State Access, One Wait

| Instruction                                  | 1           | 2                           | 3                                   | 4                        | 5                      | 6      | 7 | 8 | 9 |

|----------------------------------------------|-------------|-----------------------------|-------------------------------------|--------------------------|------------------------|--------|---|---|---|

| SLEEP                                        | R:W<br>NEXT | Internal<br>operation:<br>M |                                     |                          |                        |        |   |   |   |

| STC CCR,Rd                                   | R:W<br>NEXT |                             |                                     |                          |                        |        |   |   |   |

| STC EXR,Rd                                   | R:W<br>NEXT |                             |                                     |                          |                        |        |   |   |   |

| STC<br>CCR,@ERd                              | R:W 2nd     | R:W<br>NEXT                 | W:W EA                              |                          |                        |        |   |   |   |

| STC<br>EXR,@ERd                              | R:W 2nd     | R:W<br>NEXT                 | W:W EA                              |                          |                        |        |   |   |   |

| STC CCR,<br>@(d:16,ERd)                      | R:W 2nd     | R:W 3rd                     | R:W<br>NEXT                         | W:W EA                   |                        |        |   |   |   |

| STC EXR,<br>@(d:16,ERd)                      | R:W 2nd     | R:W 3rd                     | R:W<br>NEXT                         | W:W EA                   |                        |        |   |   |   |

| STC CCR,<br>@(d:32,ERd)                      | R:W 2nd     | R:W 3rd                     | R:W 4th                             | R:W 5th                  | R:W<br>NEXT            | W:W EA |   |   |   |

| STC EXR,<br>@(d:32,ERd)                      | R:W 2nd     | R:W 3rd                     | R:W 4th                             | R:W 5th                  | R:W<br>NEXT            | W:W EA |   |   |   |

| STC CCR,<br>@-ERd                            | R:W 2nd     | R:W<br>NEXT                 | 1 state of<br>internal<br>operation | W:W EA                   |                        |        |   |   |   |

| STC EXR,<br>@-ERd                            | R:W 2nd     | R:W<br>NEXT                 | 1 state of<br>internal<br>operation | W:W EA                   |                        |        |   |   |   |

| STC<br>CCR,@aa:16                            | R:W 2nd     | R:W 3rd                     | R:W<br>NEXT                         | W:W EA                   |                        |        |   |   |   |

| STC<br>EXR,@aa:16                            | R:W 2nd     | R:W 3rd                     | R:W<br>NEXT                         | W:W EA                   |                        |        |   |   |   |

| STC<br>CCR,@aa:32                            | R:W 2nd     | R:W 3rd                     | R:W 4th                             | R:W<br>NEXT              | W:W EA                 |        |   |   |   |

| STC<br>EXR,@aa:32                            | R:W 2nd     | R:W 3rd                     | R:W 4th                             | R:W<br>NEXT              | W:W EA                 |        |   |   |   |

| STM.L (ERn-<br>ERn+1),<br>@-SP <sup>*8</sup> | R:W 2nd     | R:W<br>NEXT                 | 1 state of<br>internal<br>operation | W:W:M<br>Stack (H)<br>*2 | W:W<br>Stack (L)       |        |   |   |   |

| STM.L (ERn-<br>ERn+2),<br>@-SP <sup>*8</sup> | R:W 2nd     | R:W<br>NEXT                 | 1 state of<br>internal<br>operation | W:W:M<br>Stack (H)<br>*2 | W:W<br>Stack (L)<br>*2 |        |   |   |   |

Index

| SSIER 119, 983, 99             | 95, 1008 |

|--------------------------------|----------|

| SSR 703, 984, 99               | 97, 1009 |

| SYSCR                          | 01, 1012 |

| TCNT 656, 985, 99              | 97, 1009 |

| TCORA 656, 990, 100            | )4, 1015 |

| TCORB 656, 990, 100            | )4, 1015 |

| TCR 552, 657, 984, 9           | 90, 997, |

|                                | 5, 1016  |

| TCSR 679, 990, 100             |          |

| TDR 694, 984, 99               |          |

| TGR 573, 581, 592, 9           | 85, 991, |

|                                |          |

| TIER 576, 985, 99              |          |

| TIOR 558, 984, 99              |          |

| TMDR 557, 984, 99              |          |

| TSR                            |          |

| TSTR 581, 991, 100             |          |

| TSYR                           |          |

| WTCR 144, 985, 99              |          |

| Reset                          |          |

| RTCNT                          |          |

| Serial Communication Interface |          |

| Acknowledge                    |          |

| 0                              |          |

| Asynchronous Mode          | 723 |

|----------------------------|-----|

| Bit rate                   | 711 |

| Break                      |     |

| Clocked Synchronous Mode   | 740 |

| Framing error              | 730 |

| General Call Address       |     |

| IrDA Operation             | 759 |

| Mark State                 |     |

| Overrun error              | 730 |

| Parity error               | 730 |

| Slave address              |     |

| Start condition            |     |

| Stop condition             |     |

| Transfer Rate              | 776 |

| Stack Pointer (SP)         | 44  |

| Synchronous DRAM Interface |     |

| Trace Bit                  | 45  |

| TRAPA                      | 64  |

| TRAPA instruction          |     |

| Watchdog Timer (WDT)       | 677 |

| Interval Timer Mode        |     |

| Overflow                   |     |

| Write Data Buffer          |     |