Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                      |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 34MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI, SmartCard                                        |

| Peripherals                | DMA, POR, PWM, WDT                                                            |

| Number of I/O              | 96                                                                            |

| Program Memory Size        | 256KB (256K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | <u>.</u>                                                                      |

| RAM Size                   | 16K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b; D/A 6x8b                                                          |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 144-LQFP                                                                      |

| Supplier Device Package    | 144-LQFP (20x20)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2370vfq34v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 5.3.5 IRQ Status Register (ISR)

| Bit                                                                                | Bit Name                                                                                                                                                             | Initial Value                                                                               | R/W                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15<br>14<br>13<br>12<br>11<br>10<br>9<br>8<br>7<br>6<br>5<br>4<br>3<br>2<br>1<br>0 | IRQ15F<br>IRQ14F<br>IRQ13F<br>IRQ12F<br>IRQ11F<br>IRQ10F<br>IRQ9F<br>IRQ9F<br>IRQ8F<br>IRQ7F<br>IRQ6F<br>IRQ5F<br>IRQ4F<br>IRQ4F<br>IRQ3F<br>IRQ2F<br>IRQ1F<br>IRQ0F | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | R/(W)*<br>R/(W)*<br>R/(W)*<br>R/(W)*<br>R/(W)*<br>R/(W)*<br>R/(W)*<br>R/(W)*<br>R/(W)*<br>R/(W)*<br>R/(W)*<br>R/(W)*<br>R/(W)*<br>R/(W)*<br>R/(W)* | <ul> <li>[Setting condition]</li> <li>When the interrupt source selected by ISCR occurs</li> <li>[Clearing conditions]</li> <li>Cleared by reading IRQnF flag when IRQnF = 1, then writing 0 to IRQnF flag</li> <li>When interrupt exception handling is executed when low-level detection is set and IRQn input is high</li> <li>When IRQn interrupt exception handling is executed when falling, rising, or both-edge detection is set</li> <li>When the DTC is activated by an IRQn interrupt, and the DISEL bit in MRB of the DTC is cleared to 0</li> </ul> |

|                                                                                    |                                                                                                                                                                      |                                                                                             |                                                                                                                                                    | (n = 15 to 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

ISR is an IRQ15 to IRQ0 interrupt request flag register.

Note: \* Only 0 can be written, to clear the flag.

|                     | Origin of           |                  | Vector<br>Address <sup>*1</sup> |                  |          |                   |                    |

|---------------------|---------------------|------------------|---------------------------------|------------------|----------|-------------------|--------------------|

| Interrupt<br>Source | Interrupt<br>Source | Vector<br>Number | Advanced<br>Mode                | IPR              | Priority | DTC<br>Activation | DMAC<br>Activation |

| SCI_0               | ERI0                | 88               | H'0160                          | IPRI2 to IPRI0   | High     | _                 |                    |

|                     | RXI0                | 89               | H'0164                          | _                | 1        | 0                 | 0                  |

|                     | TXI0                | 90               | H'0168                          | _                |          | 0                 | 0                  |

|                     | TEI0                | 91               | H'016C                          | _                |          | _                 | _                  |

| SCI_1               | ERI1                | 92               | H'0170                          | IPRJ14 to IPRJ12 | -        | _                 | _                  |

|                     | RXI1                | 93               | H'0174                          | _                |          | 0                 | 0                  |

|                     | TXI1                | 94               | H'0178                          | _                |          | 0                 | 0                  |

|                     | TEI1                | 95               | H'017C                          | _                |          | _                 | _                  |

| SCI_2               | ERI2                | 96               | H'0180                          | IPRJ10 to IPRJ8  | -        |                   |                    |

|                     | RXI2                | 97               | H'0184                          | _                |          | 0                 | _                  |

|                     | TXI2                | 98               | H'0188                          | _                |          | 0                 |                    |

|                     | TEI2                | 99               | H'018C                          | _                |          |                   |                    |

| SCI_3               | ERI3                | 100              | H'0190                          | IPRJ6 to IPRJ4   | -        | _                 |                    |

|                     | RXI3                | 101              | H'0194                          | _                |          | 0                 | _                  |

|                     | TXI3                | 102              | H'0198                          | _                |          | 0                 | _                  |

|                     | TEI3                | 103              | H'019C                          | _                |          | _                 | _                  |

| SCI_4               | ERI4                | 104              | H'01A0                          | IPRJ2 to IPRJ0   | -        | _                 | _                  |

|                     | RXI4                | 105              | H'01A4                          | _                |          | 0                 | _                  |

|                     | TXI4                | 106              | H'01A8                          | _                |          | 0                 | _                  |

|                     | TEI4                | 107              | H'01AC                          | _                |          | _                 | _                  |

|                     | Reserved for        | 108              | H'01B0                          | IPRK14 to IPRK12 | -        | _                 | _                  |

|                     | system use          | 109              | H'01B4                          | _                |          | _                 | _                  |

|                     |                     | 110              | H'01B8                          | _                |          | _                 | _                  |

|                     |                     | 111              | H'01BC                          | _                |          | _                 | _                  |

|                     |                     | 112              | H'01C0                          | IPRK10 to IPRK8  | -        | _                 |                    |

|                     |                     | 113              | H'01C4                          | _                |          | _                 | _                  |

|                     |                     | 114              | H'01C8                          | _                |          | _                 |                    |

|                     |                     | 115              | H'01CC                          | _                | Low      | _                 | _                  |

| Bit | Bit Name | Initial Value | R/W | Description                                            |

|-----|----------|---------------|-----|--------------------------------------------------------|

| 2   | MXC2     | 0             | R/W | 011: 11-bit shift                                      |

| 1   | MXC1     | 0             | R/W | • When 8-bit access space is designated:               |

| 0   | MXC0     | 0             | R/W | Row address bits A23 to A11 used for<br>comparison     |

|     |          |               |     | When 16-bit access space is designated:                |

|     |          |               |     | Row address bits A23 to A12 used for<br>comparison     |

|     |          |               |     | Synchronous DRAM interface                             |

|     |          |               |     | 100: 8-bit shift                                       |

|     |          |               |     | • When 8-bit access space is designated:               |

|     |          |               |     | Row address bits A23 to A8 used for<br>comparison      |

|     |          |               |     | • When 16-bit access space is designated:              |

|     |          |               |     | Row address bits A23 to A9 used for<br>comparison      |

|     |          |               |     | The precharge-sel is A15 to A9 of the column address.  |

|     |          |               |     | 101: 9-bit shift                                       |

|     |          |               |     | • When 8-bit access space is designated:               |

|     |          |               |     | Row address bits A23 to A9 used for<br>comparison      |

|     |          |               |     | When 16-bit access space is designated:                |

|     |          |               |     | Row address bits A23 to A10 used for<br>comparison     |

|     |          |               |     | The precharge-sel is A15 to A10 of the column address. |

|     |          |               |     | 110: 10-bit shift                                      |

|     |          |               |     | • When 8-bit access space is designated:               |

|     |          |               |     | Row address bits A23 to A10 used for<br>comparison     |

|     |          |               |     | • When 16-bit access space is designated:              |

|     |          |               |     | Row address bits A23 to A11 used for<br>comparison     |

|     |          |               |     | The precharge-sel is A15 to A11 of the column address. |

### Rev.7.00 Mar. 18, 2009 page 162 of 1136 REJ09B0109-0700

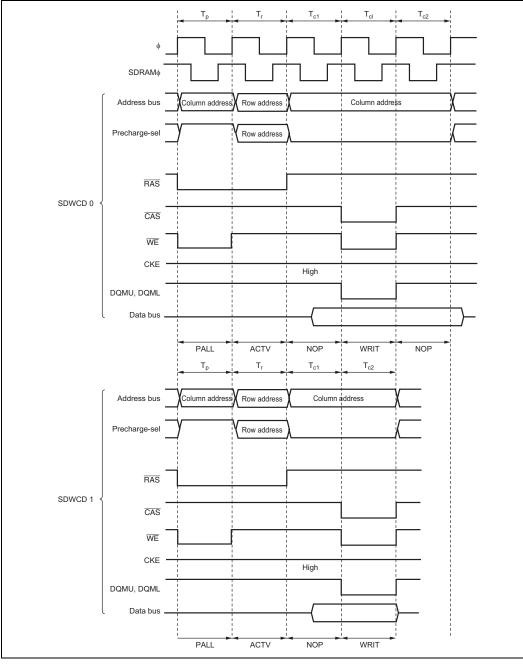

Figure 6.5 CAS Latency Control Cycle Disable Timing during Continuous Synchronous DRAM Space Write Access (for CAS Latency 2)

Rev.7.00 Mar. 18, 2009 page 166 of 1136 REJ09B0109-0700

### 6.6.12 Refresh Control

This LSI is provided with a DRAM refresh control function. CAS-before-RAS (CBR) refreshing is used. In addition, self-refreshing can be executed when the chip enters the software standby state.

Refresh control is enabled when any area is designated as DRAM space in accordance with the setting of bits RMTS2 to RMTS0 in DRAMCR.

**CAS-before-RAS (CBR) Refreshing:** To select CBR refreshing, set the RFSHE bit to 1 in REFCR.

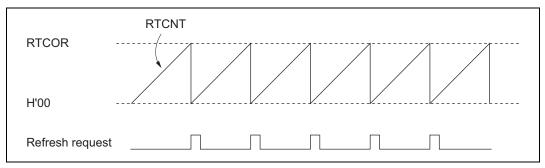

With CBR refreshing, RTCNT counts up using the input clock selected by bits RTCK2 to RTCK0 in REFCR, and when the count matches the value set in RTCOR (compare match), refresh control is performed. At the same time, RTCNT is reset and starts counting up again from H'00. Refreshing is thus repeated at fixed intervals determined by RTCOR and bits RTCK2 to RTCK0. Set a value in RTCOR and bits RTCK2 to RTCK0 that will meet the refreshing interval specification for the DRAM used.

When bits RTCK2 to RTCK0 in REFCR are set, RTCNT starts counting up. RTCNT and RTCOR settings should therefore be completed before setting bits RTCK2 to RTCK0. RTCNT operation is shown in figure 6.34, compare match timing in figure 6.35, and CBR refresh timing in figure 6.36.

When the CBRM bit in REFCR is cleared to 0, access to external space other than DRAM space is performed in parallel during the CBR refresh period.

Figure 6.34 RTCNT Operation

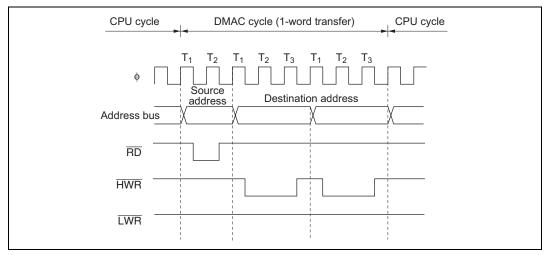

### 7.5.8 Basic Bus Cycles

An example of the basic DMAC bus cycle timing is shown in figure 7.17. In this example, wordsize transfer is performed from 16-bit, 2-state access space to 8-bit, 3-state access space. When the bus is transferred from the CPU to the DMAC, a source address read and destination address write are performed. The bus is not released in response to another bus request, etc., between these read and write operations. As like CPU cycles, DMA cycles conform to the bus controller settings.

The address is not output to the external address bus in an access to on-chip memory or an internal I/O register.

Figure 7.17 Example of DMA Transfer Bus Timing

## 10.2 Port 2

Port 2 is an 8-bit I/O port that also has other functions. The port 2 has the following registers.

- Port 2 data direction register (P2DDR)

- Port 2 data register (P2DR)

- Port 2 register (PORT2)

### 10.2.1 Port 2 Data Direction Register (P2DDR)

The individual bits of P2DDR specify input or output for the pins of port 2.

P2DDR cannot be read; if it is, an undefined value will be read.

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                             |

|-----|----------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------|

| 7   | P27DDR   | 0             | W   | When a pin function is specified to a general                                                                           |

| 6   | P26DDR   | 0             | W   | <ul> <li>purpose I/O, setting this bit to 1 makes the</li> <li>corresponding port 1 pin an output pin, while</li> </ul> |

| 5   | P25DDR   | 0             | W   | clearing this bit to 0 makes the pin an input pin.                                                                      |

| 4   | P24DDR   | 0             | W   | _                                                                                                                       |

| 3   | P23DDR   | 0             | W   |                                                                                                                         |

| 2   | P22DDR   | 0             | W   |                                                                                                                         |

| 1   | P21DDR   | 0             | W   | _                                                                                                                       |

| 0   | P20DDR   | 0             | W   | —                                                                                                                       |

- Timer interrupt enable register\_3 (TIER\_3)

- Timer status register\_3 (TSR\_3)

- Timer counter\_3 (TCNT\_3)

- Timer general register A\_3 (TGRA\_3)

- Timer general register B\_3 (TGRB\_3)

- Timer general register C\_3 (TGRC\_3)

- Timer general register D\_3 (TGRD\_3)

- Timer control register\_4 (TCR\_4)

- Timer mode register\_4 (TMDR\_4)

- Timer I/O control register \_4 (TIOR\_4)

- Timer interrupt enable register\_4 (TIER\_4)

- Timer status register\_4 (TSR\_4)

- Timer counter\_4 (TCNT\_4)

- Timer general register A\_4 (TGRA\_4)

- Timer general register B\_4 (TGRB\_4)

- Timer control register\_5 (TCR\_5)

- Timer mode register\_5 (TMDR\_5)

- Timer I/O control register\_5 (TIOR\_5)

- Timer interrupt enable register\_5 (TIER\_5)

- Timer status register\_5 (TSR\_5)

- Timer counter\_5 (TCNT\_5)

- Timer general register A\_5 (TGRA\_5)

- Timer general register B\_5 (TGRB\_5)

#### **Common Registers**

- Timer start register (TSTR)

- Timer synchronous register (TSYR)

| Channel | Timer General Register | Buffer Register |

|---------|------------------------|-----------------|

| 0       | TGRA_0                 | TGRC_0          |

|         | TGRB_0                 | TGRD_0          |

| 3       | TGRA_3                 | TGRC_3          |

|         | TGRB_3                 | TGRD_3          |

#### Table 11.28 Register Combinations in Buffer Operation

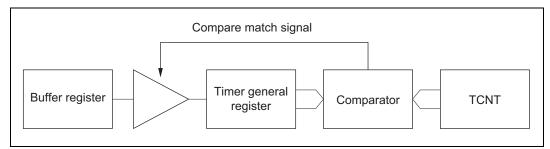

• When TGR is an output compare register

When a compare match occurs, the value in the buffer register for the corresponding channel is transferred to the timer general register.

This operation is illustrated in figure 11.12.

Figure 11.12 Compare Match Buffer Operation

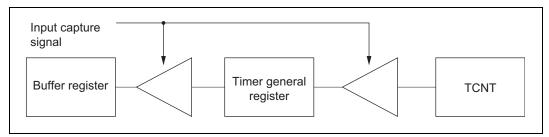

• When TGR is an input capture register

When input capture occurs, the value in TCNT is transferred to TGR and the value previously held in the timer general register is transferred to the buffer register.

This operation is illustrated in figure 11.13.

Figure 11.13 Input Capture Buffer Operation

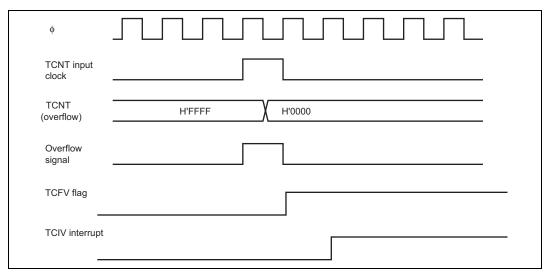

**TCFV Flag/TCFU Flag Setting Timing:** Figure 11.40 shows the timing for setting of the TCFV flag in TSR by overflow occurrence, and the TCIV interrupt request signal timing.

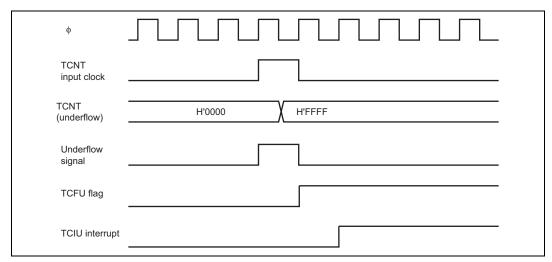

Figure 11.41 shows the timing for setting of the TCFU flag in TSR by underflow occurrence, and the TCIU interrupt request signal timing.

Figure 11.40 TCIV Interrupt Setting Timing

- 1. Set up the TPU channel to be used as the output trigger channel so that TGRA and TGRB are output compare registers. Set the trigger period in TGRB and the non-overlap margin in TGRA, and set the counter to be cleared by compare match B. Set the TGIEA bit in TIER to 1 to enable the TGIA interrupt.

- 2. Write H'FF in P1DDR and NDERH, and set the G3CMS1, G3CMS0, G2CMS1, and G2CMS0 bits in PCR to select compare match in the TPU channel set up in the previous step to be the output trigger. Set the G3NOV and G2NOV bits in PMR to 1 to select non-overlapping output. Write output data H'95 in NDRH.

- 3. The timer counter in the TPU channel starts. When a compare match with TGRB occurs, outputs change from 1 to 0. When a compare match with TGRA occurs, outputs change from 0 to 1 (the change from 0 to 1 is delayed by the value set in TGRA). The TGIA interrupt handling routine writes the next output data (H'65) in NDRH.

- Four-phase complementary non-overlapping pulse output can be obtained subsequently by writing H'59, H'56, H'95... at successive TGIA interrupts. If the DTC or DMAC is set for activation by the TGIA interrupt, pulse output can be obtained without imposing a load on the CPU.

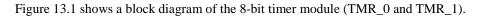

Figure 13.1 Block Diagram of 8-Bit Timer Module

Rev.7.00 Mar. 18, 2009 page 654 of 1136 REJ09B0109-0700

|     | <ul> <li>DACR01 (Available only for the H8S/2377, H8S/2377R, H8S/2378 0.18µm F-ZTAT Group,<br/>and H8S/2378R 0.18µm F-ZTAT Group)</li> </ul> |               |     |                                                                                                                                                                                                                |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit | Bit Name                                                                                                                                     | Initial Value | R/W | Description                                                                                                                                                                                                    |  |  |

| 7   | DAOE1                                                                                                                                        | 0             | R/W | D/A Output Enable 1                                                                                                                                                                                            |  |  |

|     |                                                                                                                                              |               |     | Controls D/A conversion and analog output.                                                                                                                                                                     |  |  |

|     |                                                                                                                                              |               |     | 0: Analog output (DA1) is disabled                                                                                                                                                                             |  |  |

|     |                                                                                                                                              |               |     | 1: Channel 1 D/A conversion is enabled; analog output<br>(DA1) is enabled                                                                                                                                      |  |  |

| 6   | DAOE0                                                                                                                                        | 0             | R/W | D/A Output Enable 0                                                                                                                                                                                            |  |  |

|     |                                                                                                                                              |               |     | Controls D/A conversion and analog output.                                                                                                                                                                     |  |  |

|     |                                                                                                                                              |               |     | 0: Analog output (DA0) is disabled                                                                                                                                                                             |  |  |

|     |                                                                                                                                              |               |     | 1: Channel 0 D/A conversion is enabled; analog output (DA0) is enabled                                                                                                                                         |  |  |

| 5   | DAE                                                                                                                                          | 0             | R/W | D/A Enable                                                                                                                                                                                                     |  |  |

|     |                                                                                                                                              |               |     | Used together with the DAOE0 and DAOE1 bits to control D/A conversion. When the DAE bit is cleared to 0, channel 0 and 1 D/A conversions are controlled independently. When the DAE bit is set to 1, channel 0 |  |  |

and 1 D/A conversions are controlled together. Output of conversion results is always controlled independently by the DAOE0 and DAOE1 bits. For

These bits are always read as 1 and cannot be modified.

#### Table 18.2 Control of D/A Conversion

All 1

4 to —

0

| Bit 5<br>DAE | Bit 7<br>DAOE1 | Bit 6<br>DAOE0 | Description                                                        |

|--------------|----------------|----------------|--------------------------------------------------------------------|

| 0            | 0              | 0              | D/A conversion disabled                                            |

|              |                | 1              | Channel 0 D/A conversion enabled, channel1 D/A conversion disabled |

|              | 1              | 0              | Channel 1 D/A conversion enabled, channel0 D/A conversion disabled |

|              |                | 1              | Channel 0 and 1 D/A conversions enabled                            |

| 1            | 0              | 0              | D/A conversion disabled                                            |

|              |                | 1              | Channel 0 and 1 D/A conversions enabled                            |

|              | 1              | 0              | _                                                                  |

|              |                | 1              | _                                                                  |

details, see table 18.2.

Reserved

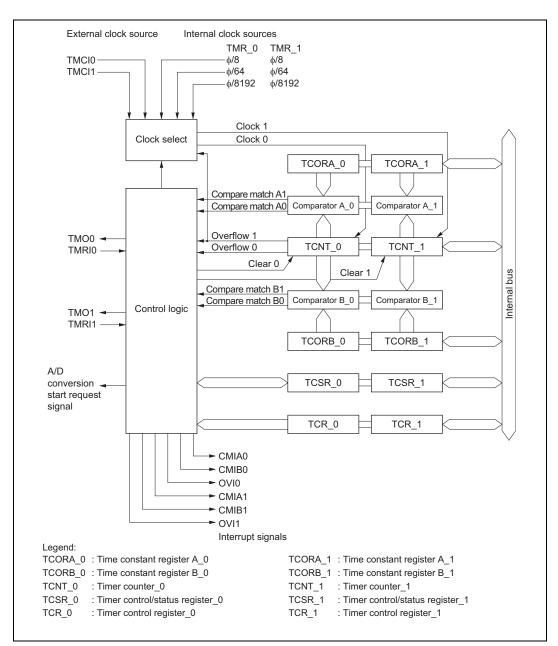

### Figure 20.7 Program/Program-Verify Flowchart

|                                                | Stora          | ble/Exec            | utable Area                             | Selected MAT |                     |                                     |  |

|------------------------------------------------|----------------|---------------------|-----------------------------------------|--------------|---------------------|-------------------------------------|--|

| ltem                                           | On-chip<br>RAM | User<br>Boot<br>MAT | External<br>Space<br>(Expanded<br>Mode) | User<br>MAT  | User<br>Boot<br>MAT | Embedded<br>Program<br>Storage Area |  |

| Operation for Settings<br>of Program Parameter | 0              | ×                   | 0                                       | 0            |                     |                                     |  |

| Execution of<br>Programming                    | 0              | ×                   | ×                                       | 0            |                     |                                     |  |

| Determination of<br>Program Result             | 0              | ×                   | 0                                       | 0            |                     |                                     |  |

| Operation for Program<br>Error                 | 0              | ×*2                 | 0                                       | 0            |                     |                                     |  |

| Operation for FKEY<br>Clear                    | 0              | ×                   | 0                                       | 0            |                     |                                     |  |

| Switching MATs by FMATS                        | 0              | ×                   | ×                                       |              | 0                   |                                     |  |

Notes: 1. Transferring the data to the on-chip RAM enables this area to be used.

2. Switching FMATS by a program in the on-chip RAM enables this area to be used.

#### (d) Clock Mode Selection

The boot program will set the specified clock mode. The program will return the selected clockmode information after this setting has been made.

The clock-mode selection command should be sent after the device-selection commands.

| Command H'11 Size Mode SUM | Command | H'11 | Size | Mode | SUM | ] |

|----------------------------|---------|------|------|------|-----|---|

|----------------------------|---------|------|------|------|-----|---|

- Command, H'11, (one byte): Selection of clock mode

- Size (one byte): Amount of data that represents the modes

- Mode (one byte): A clock mode returned in reply to the supported clock mode inquiry.

- SUM (one byte): Checksum

H'06

Response

• Response, H'06, (one byte): Response to the clock mode selection command ACK will be returned when the clock mode matches.

Error Response H'91 ERROR

- Error response, H'91, (one byte): Error response to the clock mode selection command

- ERROR, (one byte): Error code

H'11: Checksum error

H'22: Clock mode error, that is, the clock mode does not match.

Even if the clock mode numbers are H'00 and H'01 by a clock mode inquiry, the clock mode must be selected using these respective values.

| Command H'58 | Size | Block number | SUM |

|--------------|------|--------------|-----|

|--------------|------|--------------|-----|

- Command, H'58, (one byte): Erasure

- Size, (one byte): The number of bytes that represents the block number This is fixed to 1.

- Block number (one byte): H'FF Stop code for erasure

- SUM (one byte): Checksum

Response H'06

• Response, H'06, (one byte): Response to end of erasure (ACK) When erasure is to be performed after the block number H'FF has been sent, the procedure should be executed from the erasure selection command.

### (11) Memory read

The boot program will return the data in the specified address.

| Command | H'52    | Size | Area | Read address |     |  |

|---------|---------|------|------|--------------|-----|--|

|         | Read si | ze   |      |              | SUM |  |

- Command: H'52 (1 byte): Memory read

- Size (1 byte): Amount of data that represents the area, read address, and read size (fixed at 9)

- Area (1 byte)

H'00: User boot MAT

H'01: User MAT

An address error occurs when the area setting is incorrect.

- Read address (4 bytes): Start address to be read from

- Read size (4 bytes): Size of data to be read

- SUM (1 byte): Checksum

| Response | H'52 | Read si | ze |  |  |  |  |

|----------|------|---------|----|--|--|--|--|

|          | Data |         |    |  |  |  |  |

|          | SUM  |         |    |  |  |  |  |

- Response: H'52 (1 byte): Response to memory read

- Read size (4 bytes): Size of data to be read

- Data (n bytes): Data for the read size from the read address

- SUM (1 byte): Checksum

# Renesas

| Port Name | MCU O <sub>l</sub><br>Mode | perating      | Reset        | Hardware<br>Standby<br>Mode | Software<br>Standby Mode                     | Bus Release<br>State   | Program<br>Execution<br>State Sleep<br>Mode |

|-----------|----------------------------|---------------|--------------|-----------------------------|----------------------------------------------|------------------------|---------------------------------------------|

| Port E    | 1, 2, 4                    | 8-bit<br>bus  | т            | Т                           | keep                                         | keep                   | I/O port                                    |

|           |                            | 16-bit<br>bus | т            | т                           | Т                                            | Т                      | D7 to D0                                    |

|           | 3, 5 <sup>*2</sup> ,<br>7  | 8-bit<br>bus  | Т            | Т                           | keep                                         | keep                   | I/O port                                    |

|           |                            | 16-bit        | Т            | Т                           | [Data bus]                                   | [Data bus]             | [Data bus]                                  |

|           |                            | bus           |              |                             | т                                            | т                      | D7 to D0                                    |

|           |                            |               |              |                             | [Other than the above]                       | [Other than the above] | [Other than the above]                      |

|           |                            |               |              |                             | keep                                         | keep                   | I/O port                                    |

| PF7/ø     | 1, 2, 4                    |               | Clock output | Т                           | [Clock output]                               | [Clock output]         | [Clock output]                              |

|           | 3, 5 <sup>*2</sup> , 7     | ,             | Т            | -                           | н                                            | Clock output           | Clock output                                |

|           |                            |               |              |                             | [Other than the above]                       | [Other than the above] | [Other than the above]                      |

|           |                            |               |              |                             | keep                                         | keep                   | Input port                                  |

| PF6/AS    | 1, 2, 4                    |               | Н            | Т                           | $[OPE = 0, \\ \overline{AS} \text{ output}]$ | [AS output]            | [AS output]                                 |

|           |                            |               |              |                             | T                                            | Т                      | ĀS                                          |

|           | 3, 5 <sup>*2</sup> , 7     | 7             | т            | -                           | [OPE = 1,                                    | [Other than the above] | [Other than the above]                      |

|           |                            |               |              |                             | AS output]                                   | keep                   | I/O port                                    |

|           |                            |               |              |                             | Н                                            |                        |                                             |

|           |                            |               |              |                             | [Other than the above]                       |                        |                                             |

|           |                            |               |              |                             | keep                                         |                        |                                             |

| Instruction   | 1           | 2                                   | 3                                   | 4           | 5           | 6 | 7 | 8 | 9 |

|---------------|-------------|-------------------------------------|-------------------------------------|-------------|-------------|---|---|---|---|

| OR.L ERs,ERd  | R:W 2nd     | R:W<br>NEXT                         |                                     |             |             |   |   |   |   |

| ORC #xx:8,CCR | R:W<br>NEXT |                                     |                                     |             |             |   |   |   |   |

| ORC #xx:8,EXR | R:W 2nd     | R:W<br>NEXT                         |                                     |             |             |   |   |   |   |

| POP.W Rn      | R:W<br>NEXT | 1 State of<br>internal<br>operation | R:W EA                              |             |             |   |   |   |   |

| POP.L ERn     | R:W 2nd     | R:W<br>NEXT                         | 1 State of<br>internal<br>operation | R:W:M<br>EA | R:W<br>EA+2 |   |   |   |   |

| PUSH.W Rn     | R:W<br>NEXT | 1 State of<br>internal<br>operation | W:W EA                              |             |             |   |   |   |   |

| PUSH.L ERn    | R:W 2nd     | R:W<br>NEXT                         | 1 State of<br>internal<br>operation | W:W:M<br>EA | W:W<br>EA+2 |   |   |   |   |

| ROTL.B Rd     | R:W<br>NEXT |                                     |                                     |             |             |   |   |   |   |

| ROTL.B #2,Rd  | R:W<br>NEXT |                                     |                                     |             |             |   |   |   |   |

| ROTL.W Rd     | R:W<br>NEXT |                                     |                                     |             |             |   |   |   |   |

| ROTL.W #2,Rd  | R:W<br>NEXT |                                     |                                     |             |             |   |   |   |   |

| ROTL.L ERd    | R:W<br>NEXT |                                     |                                     |             |             |   |   |   |   |

| ROTL.L #2,ERd | R:W<br>NEXT |                                     |                                     |             |             |   |   |   |   |

| ROTR.B Rd     | R:W<br>NEXT |                                     |                                     |             |             |   |   |   |   |

| ROTR.B #2,Rd  | R:W<br>NEXT |                                     |                                     |             |             |   |   |   |   |

| ROTR.W Rd     | R:W<br>NEXT |                                     |                                     |             |             |   |   |   |   |

| ROTR.W #2,Rd  | R:W<br>NEXT |                                     |                                     |             |             |   |   |   |   |

| ROTR.L ERd    | R:W<br>NEXT |                                     |                                     |             |             |   |   |   |   |

| ROTR.L #2,ERd | R:W<br>NEXT |                                     |                                     |             |             |   |   |   |   |

| Instruction                                  | 1           | 2                           | 3                                   | 4                        | 5                      | 6      | 7 | 8 | 9 |

|----------------------------------------------|-------------|-----------------------------|-------------------------------------|--------------------------|------------------------|--------|---|---|---|

| SLEEP                                        | R:W<br>NEXT | Internal<br>operation:<br>M |                                     |                          |                        |        |   |   |   |

| STC CCR,Rd                                   | R:W<br>NEXT |                             |                                     |                          |                        |        |   |   |   |

| STC EXR,Rd                                   | R:W<br>NEXT |                             |                                     |                          |                        |        |   |   |   |

| STC<br>CCR,@ERd                              | R:W 2nd     | R:W<br>NEXT                 | W:W EA                              |                          |                        |        |   |   |   |

| STC<br>EXR,@ERd                              | R:W 2nd     | R:W<br>NEXT                 | W:W EA                              |                          |                        |        |   |   |   |

| STC CCR,<br>@(d:16,ERd)                      | R:W 2nd     | R:W 3rd                     | R:W<br>NEXT                         | W:W EA                   |                        |        |   |   |   |

| STC EXR,<br>@(d:16,ERd)                      | R:W 2nd     | R:W 3rd                     | R:W<br>NEXT                         | W:W EA                   |                        |        |   |   |   |

| STC CCR,<br>@(d:32,ERd)                      | R:W 2nd     | R:W 3rd                     | R:W 4th                             | R:W 5th                  | R:W<br>NEXT            | W:W EA |   |   |   |

| STC EXR,<br>@(d:32,ERd)                      | R:W 2nd     | R:W 3rd                     | R:W 4th                             | R:W 5th                  | R:W<br>NEXT            | W:W EA |   |   |   |

| STC CCR,<br>@-ERd                            | R:W 2nd     | R:W<br>NEXT                 | 1 state of<br>internal<br>operation | W:W EA                   |                        |        |   |   |   |

| STC EXR,<br>@-ERd                            | R:W 2nd     | R:W<br>NEXT                 | 1 state of<br>internal<br>operation | W:W EA                   |                        |        |   |   |   |

| STC<br>CCR,@aa:16                            | R:W 2nd     | R:W 3rd                     | R:W<br>NEXT                         | W:W EA                   |                        |        |   |   |   |

| STC<br>EXR,@aa:16                            | R:W 2nd     | R:W 3rd                     | R:W<br>NEXT                         | W:W EA                   |                        |        |   |   |   |

| STC<br>CCR,@aa:32                            | R:W 2nd     | R:W 3rd                     | R:W 4th                             | R:W<br>NEXT              | W:W EA                 |        |   |   |   |

| STC<br>EXR,@aa:32                            | R:W 2nd     | R:W 3rd                     | R:W 4th                             | R:W<br>NEXT              | W:W EA                 |        |   |   |   |

| STM.L (ERn-<br>ERn+1),<br>@-SP <sup>*8</sup> | R:W 2nd     | R:W<br>NEXT                 | 1 state of<br>internal<br>operation | W:W:M<br>Stack (H)<br>*2 | W:W<br>Stack (L)<br>*2 |        |   |   |   |

| STM.L (ERn-<br>ERn+2),<br>@-SP <sup>*8</sup> | R:W 2nd     | R:W<br>NEXT                 | 1 state of<br>internal<br>operation | W:W:M<br>Stack (H)<br>*2 | W:W<br>Stack (L)<br>*2 |        |   |   |   |