Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                      |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 34MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI, SmartCard                                        |

| Peripherals                | DMA, POR, PWM, WDT                                                            |

| Number of I/O              | 96                                                                            |

| Program Memory Size        | 256KB (256K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 24K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b; D/A 6x8b                                                          |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 145-TFLGA                                                                     |

| Supplier Device Package    | 145-TFLGA (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2371vlp34v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 2.7.9 Effective Address Calculation                        | 66  |

|-------|------------------------------------------------------------|-----|

| 2.8   | Processing States                                          | 68  |

| 2.9   | Usage Note                                                 | 69  |

|       | 2.9.1 Note on Bit Manipulation Instructions                | 69  |

| Secti | on 3 MCU Operating Modes                                   | 71  |

| 3.1   | Operating Mode Selection                                   | 71  |

| 3.2   | Register Descriptions                                      | 72  |

|       | 3.2.1 Mode Control Register (MDCR)                         |     |

|       | 3.2.2 System Control Register (SYSCR)                      |     |

| 3.3   | Operating Mode Descriptions                                |     |

|       | 3.3.1 Mode 1                                               |     |

|       | 3.3.2 Mode 2                                               |     |

|       | 3.3.3 Mode 3                                               |     |

|       | 3.3.4 Mode 4                                               |     |

|       | 3.3.5 Mode 5                                               |     |

|       | 3.3.6 Mode 7                                               |     |

|       | 3.3.7 Pin Functions                                        |     |

| 3.4   | Memory Map in Each Operating Mode                          | 78  |

| Secti | on 4 Exception Handling                                    | 93  |

| 4.1   | Exception Handling Types and Priority                      | 93  |

| 4.2   | Exception Sources and Exception Vector Table               |     |

| 4.3   | Reset                                                      |     |

|       | 4.3.1 Reset Exception Handling                             | 95  |

|       | 4.3.2 Interrupts after Reset                               |     |

|       | 4.3.3 On-Chip Peripheral Functions after Reset Release     |     |

| 4.4   | Trace Exception Handling                                   |     |

| 4.5   | Interrupt Exception Handling                               |     |

| 4.6   | Trap Instruction Exception Handling                        |     |

| 4.7   | Stack Status after Exception Handling 1                    |     |

| 4.8   | Usage Note 1                                               | .01 |

| Secti | on 5 Interrupt Controller                                  | 03  |

| 5.1   | Features 1                                                 | .03 |

| 5.2   | Input/Output Pins 1                                        | 05  |

| 5.3   | Register Descriptions 1                                    |     |

|       | 5.3.1 Interrupt Control Register (INTCR) 1                 | .06 |

|       | 5.3.2 Interrupt Priority Registers A to K (IPRA to IPRK) 1 | .06 |

|       | 5.3.3 IRQ Enable Register (IER) 1                          | .08 |

|       | 5.3.4 IRQ Sense Control Registers H and L (ISCRH, ISCRL) 1 | 10  |

|       |                                                            |     |

Rev.7.00 Mar. 18, 2009 page xxiv of Ixvi REJ09B0109-0700

| Addressing Mode and Instruction Format | Effective Address Calculation            | Effective Address (EA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Absolute address                       |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| @aa:8                                  |                                          | <b>31</b> 24 23 8 7 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| op abs                                 |                                          | Don't care H'FFFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| @22:16                                 |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        |                                          | 31 24 23 16 15 0<br>Don't care Sign extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| @aa:24                                 |                                          | <u>31 24 23 0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| op abs                                 |                                          | Don't care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                        |                                          | <b>_</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| @aa:32                                 |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ор                                     |                                          | <b>31</b> 24 23 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| abs                                    |                                          | Don't care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                        |                                          | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Immediate                              |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| #xx:8/#xx:16/#xx:32                    |                                          | Operand is immediate data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| op IMM                                 |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| op disp                                | 23 0                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        | extension disp                           | <u>31 24 23 0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                        | Ť                                        | Don't care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Normal mode*                           |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| op abs                                 |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        |                                          | 31         24 23         16         15         0           Don't care         H'00         Image: H'00 |

|                                        | - Wennory contents                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Advanced mode                          |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        | 31 87 0                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| op abs                                 | H'000000 abs                             | <u>31 24 23 0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                        | 310                                      | Don't care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                        | Memory contents                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        | Absolute address @aa:8   op abs   @aa:16 | Absolute address       @aa:8         op       abs         @aa:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Note: \* For this LSI, normal mode is not available.

| ABWCR | ASTCR | W   | FCRA, W | TCRB | Bus Speci | fications (Ba    | sic Bus Interface)     |

|-------|-------|-----|---------|------|-----------|------------------|------------------------|

| ABWn  | ASTn  | Wn2 | Wn1     | Wn0  | Bus Width | Access<br>States | Program Wait<br>States |

| 0     | 0     | _   | _       |      | 16        | 2                | 0                      |

|       | 1     | 0   | 0       | 0    | _         | 3                | 0                      |

|       |       |     |         | 1    | -         |                  | 1                      |

|       |       |     | 1       | 0    | -         |                  | 2                      |

|       |       |     |         | 1    | -         |                  | 3                      |

|       |       | 1   | 0       | 0    | -         |                  | 4                      |

|       |       |     |         | 1    | _         |                  | 5                      |

|       |       |     | 1       | 0    | _         |                  | 6                      |

|       |       |     |         | 1    | -         |                  | 7                      |

| 1     | 0     | _   | _       | —    | 8         | 2                | 0                      |

|       | 1     | 0   | 0       | 0    | _         | 3                | 0                      |

|       |       |     |         | 1    | _         |                  | 1                      |

|       |       |     | 1       | 0    | _         |                  | 2                      |

|       |       |     |         | 1    | _         |                  | 3                      |

|       |       | 1   | 0       | 0    | _         |                  | 4                      |

|       |       |     |         | 1    | _         |                  | 5                      |

|       |       |     | 1       | 0    | -         |                  | 6                      |

|       |       |     |         | 1    | _         |                  | 7                      |

Table 6.2

Bus Specifications for Each Area (Basic Bus Interface)

(n = 0 to 7)

**Read Strobe Timing:** RDNCR can be used to select either of two negation timings (at the end of the read cycle or one half-state before the end of the read cycle) for the read strobe ( $\overline{\text{RD}}$ ) used in the basic bus interface space.

**Chip Select** ( $\overline{CS}$ ) **Assertion Period Extension States:** Some external I/O devices require a setup time and hold time between address and  $\overline{CS}$  signals and strobe signals such as  $\overline{RD}$ ,  $\overline{HWR}$ , and  $\overline{LWR}$ . CSACR can be used to insert states in which only the  $\overline{CS}$ ,  $\overline{AS}$ , and address signals are asserted before and after a basic bus space access cycle.

## Renesas

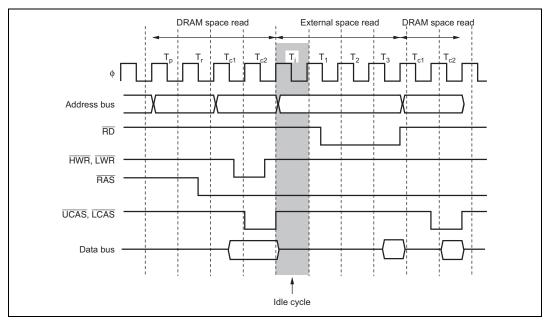

• Normal space access after DRAM space write access While the ICIS2 bit is set to 1 in BCR and a normal space read access occurs after DRAM space write access, idle cycle is inserted in the first read cycle. The number of states of the idle cycle to be inserted is in accordance with the setting of the IDLC bit. It does not depend on the DRMI bit in DRACCR. Figure 6.78 shows an example of idle cycle operation when the ICIS2 bit is set to 1.

Figure 6.78 Example of Idle Cycle Operation after DRAM Write Access (IDLC = 0, ICIS1 = 0, RAST = 0, CAST = 0)

# Idle Cycle in Case of Normal Space Access after Continuous Synchronous DRAM Space Access:

Note: In the H8S/2378 Group, the synchronous DRAM interface is not supported.

• Normal space access after a continuous synchronous DRAM space read access While the DRMI bit is cleared to 0 in DRACCR, idle cycle insertion after continuous synchronous DRAM space read access is disabled. Idle cycle insertion after continuous synchronous DRAM space read access can be enabled by setting the DRMI bit to 1. The conditions and number of states of the idle cycle to be inserted are in accordance with the settings of bits ICIS1, ICIS0, and IDLC in RCR. Figure 6.79 shows an example of idle cycle operation when the DRMI bit is set to 1. When the DRMI bit is cleared to 0, an idle cycle is

## Renesas

#### 7.3.4 DMA Control Registers (DMACRA and DMACRB)

DMACR controls the operation of each DMAC channel.

The DMA has four DMACR registers: DMACR\_0A in channel 0 (channel 0A), DMACR\_0B in channel 0 (channel 0B), DMACR\_1A in channel 1 (channel 1A), and DMACR\_1B in channel 1 (channel 1B).

In short address mode, channels A and B operate independently, and in full address mode, channels A and B operate together. The bit functions in the DMACR registers differ according to the transfer mode.

**Short Address Mode:**

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                                                 |

|-----|----------|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DTSZ     | 0             | R/W | Data Transfer Size                                                                                                                                                          |

|     |          |               |     | Selects the size of data to be transferred at one time.                                                                                                                     |

|     |          |               |     | 0: Byte-size transfer                                                                                                                                                       |

|     |          |               |     | 1: Word-size transfer                                                                                                                                                       |

| 6   | DTID     | 0             | R/W | Data Transfer Increment/Decrement                                                                                                                                           |

|     |          |               |     | Selects incrementing or decrementing of MAR after<br>every data transfer in sequential mode or repeat<br>mode. In idle mode, MAR is neither incremented<br>nor decremented. |

|     |          |               |     | 0: MAR is incremented after a data transfer<br>(Initial value)                                                                                                              |

|     |          |               |     | • When DTSZ = 0, MAR is incremented by 1                                                                                                                                    |

|     |          |               |     | • When DTSZ = 1, MAR is incremented by 2                                                                                                                                    |

|     |          |               |     | 1: MAR is decremented after a data transfer                                                                                                                                 |

|     |          |               |     | • When DTSZ = 0, MAR is decremented by 1                                                                                                                                    |

|     |          |               |     | • When DTSZ = 1, MAR is decremented by 2                                                                                                                                    |

• DMACR\_0A, DMACR\_0B, DMACR\_1A, and DMARC\_1B

## 7.7.3 Write Data Buffer Function

When the WDBE bit of BCR in the bus controller is set to 1, enabling the write data buffer function, dual address transfer external write cycles or single address transfers and internal accesses (on-chip memory or internal I/O registers) are executed in parallel.

• Write data buffer function and DMAC register setting

If the setting of a register that controls external accesses is changed during execution of an external access by means of the write data buffer function, the external access may not be performed normally. Registers that control external accesses should only be manipulated when external reads, etc., are used with DMAC operation disabled, and the operation is not performed in parallel with external access.

• Write data buffer function and DMAC operation timing

The DMAC can start its next operation during external access using the write data buffer function. Consequently, the  $\overline{\text{DREQ}}$  pin sampling timing,  $\overline{\text{TEND}}$  output timing, etc., are different from the case in which the write data buffer function is disabled. Also, internal bus cycles maybe hidden, and not visible.

### 7.7.4 **TEND** Output

If the last transfer cycle is for an internal address, note that even if low-level output at the  $\overline{\text{TEND}}$  pin has been set, a low level may not be output at the  $\overline{\text{TEND}}$  pin under the following external bus conditions since the last transfer cycle (internal bus cycle) and the external bus cycle are executed in parallel.

- 1. EXDMAC cycle

- 2. Write cycle with write buffer mode enabled

- 3. DMAC single address cycle for a different channel with write buffer mode enabled

- 4. Bus release cycle

- 5. CBR refresh cycle

Figure 7.41 shows an example in which a low level is not output from the  $\overline{\text{TEND}}$  pin in case 2 above.

If the last transfer cycle is an external address cycle, a low level is output at the  $\overline{\text{TEND}}$  pin in synchronization with the bus cycle.

## 9.5 Operation

The DTC stores register information in the on-chip RAM. When activated, the DTC reads register information that is already stored in the on-chip RAM and transfers data on the basis of that register information. After the data transfer, it writes updated register information back to the on-chip RAM. Pre-storage of register information in the on-chip RAM makes it possible to transfer data over any required number of channels. There are three transfer modes: normal mode, repeat mode, and block transfer mode. Setting the CHNE bit to 1 makes it possible to perform a number of transfers with a single activation (chain transfer). A setting can also be made to have chain transfer performed only when the transfer counter value is 0. This enables DTC re-setting to be performed by the DTC itself.

The 24-bit SAR designates the DTC transfer source address and the 24-bit DAR designates the transfer destination address. After each transfer, SAR and DAR are independently incremented, decremented, or left fixed.

Figure 9.5 shows a flowchart of DTC operation, and table 9.3 summarizes the chain transfer conditions (combinations for performing the second and third transfers are omitted).

|      |                                         | *3                    | *3                                        |                    | Мо       | de 7                    | Input/                                                     |

|------|-----------------------------------------|-----------------------|-------------------------------------------|--------------------|----------|-------------------------|------------------------------------------------------------|

| Port | Description                             | Mode 1 <sup>***</sup> | Node 1 <sup>*3</sup> Mode 2 <sup>*3</sup> | Mode 4             | EXPE = 1 | EXPE = 0                | Output<br>Type                                             |

|      | General I/O port                        | PH3/CS7/              | (IRQ7)/OE                                 | /CKE <sup>*1</sup> |          | PH3/(IRQ7)              | Only PH2                                                   |

| н    | also functioning<br>as interrupt inputs | PH2/CS6/              | (IRQ6)                                    |                    |          | PH2/(IRQ6)              | and PH3<br>are                                             |

|      | and bus control                         | PH1/CS5/              | RAS5/SDR                                  | RAM∳ <sup>*1</sup> |          | PH1/SDRAM <sup>*1</sup> | Schmitt-                                                   |

|      | I/Os                                    | PH0/CS4/              | RAS4/WE*                                  | <1                 |          | РНО                     | triggered<br>inputs<br>when<br>used as<br>the IRQ<br>input |

Notes: 1. Not supported by the H8S/2378 0.18 $\mu m$  F-ZTAT Group, H8S/2377, H8S/2375, and H8S/2373.

- 2. Not supported by the H8S/2375, H8S/2375R, H8S/2373, and H8S/2373R.

- 3. Only modes 1 and 2 are supported on ROM-less versions.

## 10.1 Port 1

Port 1 is an 8-bit I/O port that also has other functions. The port 1 has the following registers.

- Port 1 data direction register (P1DDR)

- Port 1 data register (P1DR)

- Port 1 register (PORT1)

#### 10.1.1 Port 1 Data Direction Register (P1DDR)

The individual bits of P1DDR specify input or output for the pins of port 1.

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                             |

|-----|----------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------|

| 7   | P17DDR   | 0             | W   | When a pin function is specified to a general                                                                           |

| 6   | P16DDR   | 0             | W   | <ul> <li>purpose I/O, setting this bit to 1 makes the</li> <li>corresponding port 1 pin an output pin, while</li> </ul> |

| 5   | P15DDR   | 0             | W   | clearing this bit to 0 makes the pin an input pin.                                                                      |

| 4   | P14DDR   | 0             | W   |                                                                                                                         |

| 3   | P13DDR   | 0             | W   | —                                                                                                                       |