Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                       |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 34MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI, SmartCard                                         |

| Peripherals                | DMA, POR, PWM, WDT                                                             |

| Number of I/O              | 96                                                                             |

| Program Memory Size        | 384KB (384K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b; D/A 6x8b                                                           |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 145-TFLGA                                                                      |

| Supplier Device Package    | 145-TFLGA (9x9)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2374rvlp34v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

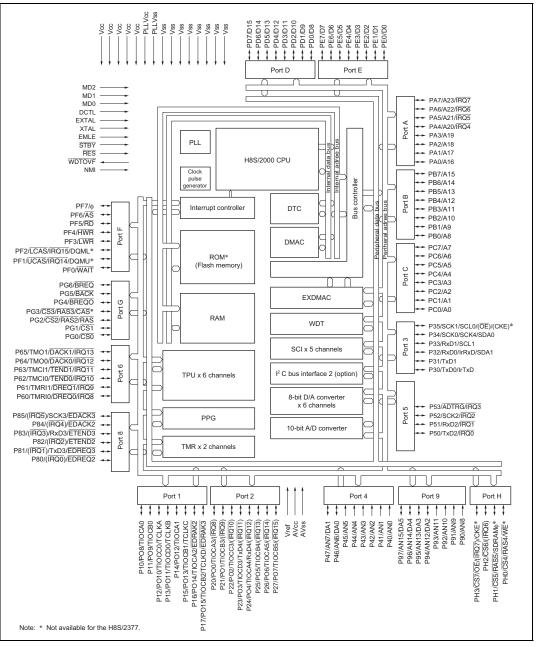

Figure 1.2 Internal Block Diagram for H8S/2377 and H8S/2377R

| Туре           | Symbol                          | H8S/2378<br>0.18μm<br>F-ZTAT Group,<br>H8S/2378R<br>0.18μm<br>F-ZTAT Group<br>(LQFP-144) | H8S/2378<br>0.18μm<br>F-ZTAT Group,<br>H8S/2378R<br>0.18μm<br>F-ZTAT Group<br>(LGA-145) | H8S/2377            | H8S/2375<br>H8S/2373<br>H8S/2375R<br>H8S/2373R | ı/o    | Function                                                                                                                                                                         |

|----------------|---------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------|------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus<br>control | RAS/<br>RAS2<br>RAS3 to<br>RAS5 | 109, 110,<br>35, 36                                                                      | A12,<br>A13,<br>L1,<br>M1                                                               | 109, 110,<br>35, 36 | 109, 110,<br>35, 36                            | Output | Row address strobe<br>signal for the<br>synchronous DRAM<br>interface.<br>RAS signal is a row<br>address strobe<br>signal when areas 2<br>to 5 are set to the<br>continuous DRAM |

|                | RAS*1                           | 109                                                                                      | A12                                                                                     | 109                 | 109                                            | Output | space.<br>Row address strobe<br>signal for the<br>synchronous DRAM<br>of the synchronous<br>DRAM interface.                                                                      |

|                | CAS*1                           | 110                                                                                      | A13                                                                                     | 110                 | 110                                            | Output | Column address<br>strobe signal for the<br>synchronous DRAM<br>of the synchronous<br>DRAM interface.                                                                             |

|                | WE <sup>*1</sup>                | 35                                                                                       | L1                                                                                      | 35                  | 35                                             | Output | Write enable signal<br>for the synchronous<br>DRAM of the<br>synchronous DRAM<br>interface.                                                                                      |

|                | WAIT                            | 84                                                                                       | J11                                                                                     | 84                  | 84                                             | Input  | Requests insertion<br>of a wait state in the<br>bus cycle when<br>accessing external<br>3-state address<br>space.                                                                |

- - -

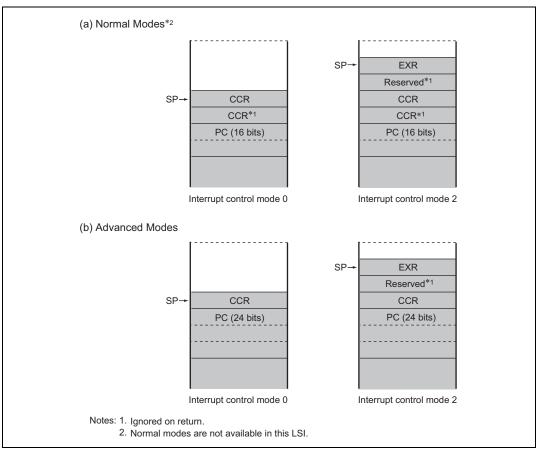

# 4.7 Stack Status after Exception Handling

Figure 4.3 shows the stack after completion of trap instruction exception handling and interrupt exception handling.

Figure 4.3 Stack Status after Exception Handling

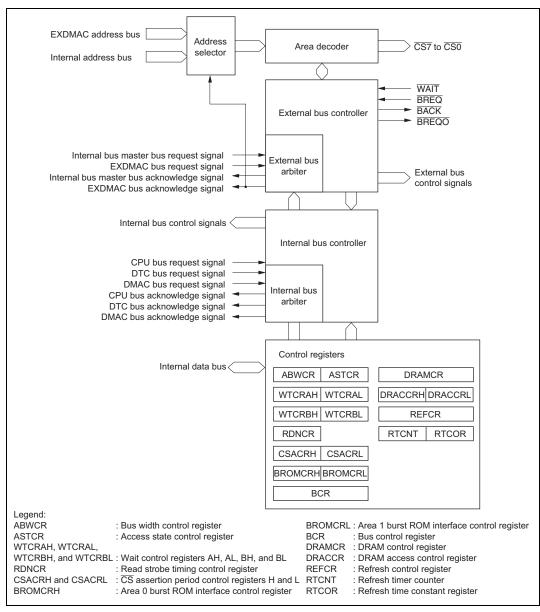

Figure 6.1 Block Diagram of Bus Controller

# 6.2 Input/Output Pins

Table 6.1 shows the pin configuration of the bus controller.

### Table 6.1Pin Configuration

| Name                                                                           | Symbol                             | I/O    | Function                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------|------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address strobe                                                                 | ĀS                                 | Output | Strobe signal indicating that normal space<br>is accessed and address output on<br>address bus is enabled.                                                                                                                                                                           |

| Read                                                                           | RD                                 | Output | Strobe signal indicating that normal space is being read.                                                                                                                                                                                                                            |

| High write/write enable                                                        | HWR/WE                             | Output | Strobe signal indicating that normal space<br>is written to, and upper half (D15 to D8) of<br>data bus is enabled or DRAM space write<br>enable signal.                                                                                                                              |

| Low write                                                                      | LWR                                | Output | Strobe signal indicating that normal space<br>is written to, and lower half (D7 to D0) of<br>data bus is enabled.                                                                                                                                                                    |

| Chip select 0                                                                  | CS0                                | Output | Strobe signal indicating that area 0 is selected.                                                                                                                                                                                                                                    |

| Chip select 1                                                                  | CS1                                | Output | Strobe signal indicating that area 1 is selected                                                                                                                                                                                                                                     |

| Chip select 2/<br>row address strobe 2/<br>row address strobe <sup>*1</sup>    | CS2/<br>RAS2/<br>RAS <sup>*1</sup> | Output | Strobe signal indicating that area 2 is<br>selected, DRAM row address strobe signal<br>when area 2 is DRAM space or areas 2 to<br>5 are set as continuous DRAM space, or<br>row address strobe signal of the<br>synchronous DRAM when the<br>synchronous DRAM interface is selected. |

| Chip select 3/<br>row address strobe 3/<br>column address strobe <sup>*1</sup> | CS3/<br>RAS3/<br>CAS <sup>*1</sup> | Output | Strobe signal indicating that area 3 is<br>selected, DRAM row address strobe signal<br>when area 3 is DRAM space, or column<br>address strobe signal of the synchronous<br>DRAM when the synchronous DRAM<br>interface is selected.                                                  |

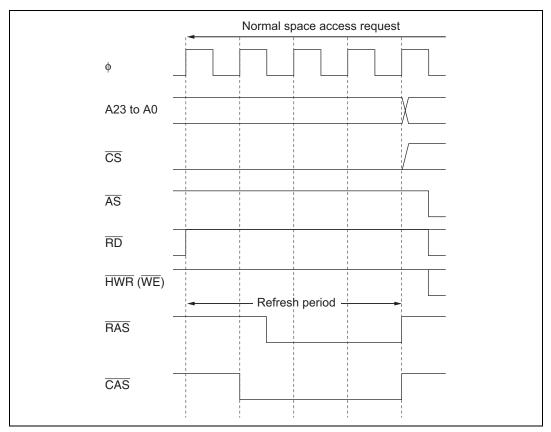

Figure 6.38 Example of CBR Refresh Timing (CBRM = 1)

**Self-Refreshing:** A self-refresh mode (battery backup mode) is provided for DRAM as a kind of standby mode. In this mode, refresh timing and refresh addresses are generated within the DRAM.

To select self-refreshing, set the RFSHE bit and SLFRF bit to 1 in REFCR. When a SLEEP instruction is executed to enter software standby mode, the  $\overline{CAS}$  and  $\overline{RAS}$  signals are output and DRAM enters self-refresh mode, as shown in figure 6.39.

When software standby mode is exited, the SLFRF bit is cleared to 0 and self-refresh mode is exited automatically. If a CBR refresh request occurs when making a transition to software standby mode, CBR refreshing is executed, then self-refresh mode is entered.

When using self-refresh mode, the OPE bit must not be cleared to 0 in the SBYCR register.

### 7.2 Input/Output Pins

Table 7.1 shows the pin configuration of the interrupt controller.

#### Table 7.1Pin Configuration

| Channel | Pin Name                   | Symbol | I/O    | Function                                      |

|---------|----------------------------|--------|--------|-----------------------------------------------|

| 0       | DMA request 0              | DREQ0  | Input  | Channel 0 external request                    |

|         | DMA transfer acknowledge 0 | DACK0  | Output | Channel 0 single address transfer acknowledge |

|         | DMA transfer end 0         | TEND0  | Output | Channel 0 transfer end                        |

| 1       | DMA request 1              | DREQ1  | Input  | Channel 1 external request                    |

|         | DMA transfer acknowledge 1 | DACK1  | Output | Channel 1 single address transfer acknowledge |

|         | DMA transfer end 1         | TEND1  | Output | Channel 1 transfer end                        |

### 7.3 **Register Descriptions**

- Memory address register\_0AH (MAR\_0AH)

- Memory address register\_0AL (MAR\_0AL)

- I/O address register\_0A (IOAR\_0A)

- Transfer count register\_0A (ECTR\_0A)

- Memory address register\_0BH (MAR\_0BH)

- Memory address register\_0BL (MAR\_0BL)

- I/O address register\_0B (IOAR\_0B)

- Transfer count register\_0B (ECTR\_0B)

- Memory address register\_1AH (MAR\_1AH)

- Memory address register\_1AL (MAR\_1AL)

- I/O address register\_1A (IOAR\_1A)

- Transfer count register\_1A (ETCR\_1B)

- Memory address register\_1BH (MAR\_1BH)

- Memory address register\_1BL (MAR\_1BL)

- I/O address register\_1B (IOAR\_1B)

- Transfer count register\_1B (ETCR\_1B)

- DMA control register\_0A (DMACR\_0A)

- DMA control register\_0B (DMACR\_0B)

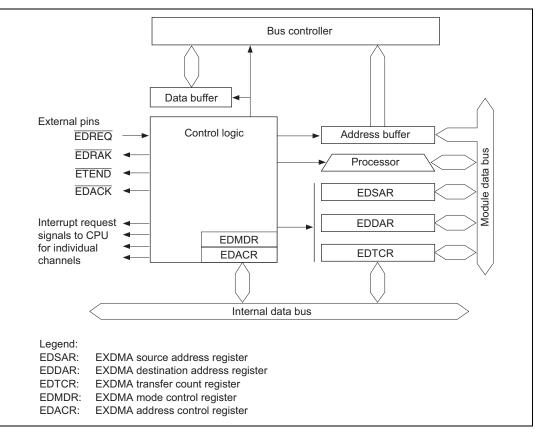

Figure 8.1 Block Diagram of EXDMAC

### 8.3.4 EXDMA Mode Control Register (EDMDR)

EDMDR controls EXDMAC operations.

| Bit | Bit Name | Initial Value | R/W   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | EDA      | 0             | R/(W) | EXDMA Active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |          |               |       | Enables or disables data transfer on the corresponding channel. When this bit is set to 1, this indicates that an EXDMA operation is in progress.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |          |               |       | When auto request mode is specified (by bits MDS1 and MDS0), transfer processing begins when this bit is set to 1. With external requests, transfer processing begins when a transfer request is issued after this bit has been set to 1. When this bit is cleared to 0 during an EXDMA operation, transfer is halted. If this bit is cleared to 0 during an EXDMA operation in block transfer mode, transfer processing is continued for the currently executing one-block transfer, and the bit is cleared on completion of the currently executing one-block transfer. |

|     |          |               |       | If an external source that ends (aborts) transfer<br>occurs, this bit is automatically cleared to 0 and<br>transfer is terminated. Do not change the operating<br>mode, transfer method, or other parameters while<br>this bit is set to 1.                                                                                                                                                                                                                                                                                                                               |

|     |          |               |       | 0: Data transfer disabled on corresponding channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |          |               |       | [Clearing conditions]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |          |               |       | When the specified number of transfers end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |          |               |       | <ul> <li>When operation is halted by a repeat area<br/>overflow interrupt</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |          |               |       | <ul> <li>When 0 is written to EDA while EDA = 1<br/>(In block transfer mode, write is effective after<br/>end of one-block transfer)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |          |               |       | Reset, NMI interrupt, hardware standby mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |          |               |       | 1: Data transfer enabled on corresponding channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |          |               |       | Note: The value written in the EDA bit may not be effective immediately.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1st T | ransfer |       | 2nd Transfer |      |       |       |                          |

|------|-------|---------|-------|--------------|------|-------|-------|--------------------------|

| CHNE | CHNS  | DISEL   | CR    | CHNE         | CHNS | DISEL | CR    | DTC Transfer             |

| 0    |       | 0       | Not 0 | —            | —    | —     | —     | Ends at 1st transfer     |

| 0    |       | 0       | 0     | _            | _    | _     | —     | Ends at 1st transfer     |

| 0    |       | 1       | _     | _            | _    | _     | —     | Interrupt request to CPU |

| 1    | 0     |         | _     | 0            | _    | 0     | Not 0 | Ends at 2nd transfer     |

|      |       |         |       | 0            | _    | 0     | 0     | Ends at 2nd transfer     |

|      |       |         |       | 0            | _    | 1     | —     | Interrupt request to CPU |

| 1    | 1     | 0       | Not 0 | _            | _    | _     | —     | Ends at 1st transfer     |

| 1    | 1     |         | 0     | 0            | _    | 0     | Not 0 | Ends at 2nd transfer     |

|      |       |         |       | 0            | _    | 0     | 0     | Ends at 2nd transfer     |

|      |       |         |       | 0            | _    | 1     | _     | Interrupt request to CPU |

| 1    | 1     | 1       | Not 0 |              |      | _     | _     | Ends at 1st transfer     |

|      |       |         |       |              |      |       |       | Interrupt request to CPU |

#### Table 9.3 Chain Transfer Conditions

#### 10.2.4 Pin Functions

Port 2 pins also function as PPG outputs, TPU I/Os, and interrupt inputs. The correspondence between the register specification and the pin functions is shown below.

#### • P27/PO7/TIOCB5/(IRQ15)

The pin function is switched as shown below according to the combination of the TPU channel 5 settings (by bits MD3 to MD0 in TMDR\_5, bits IOB3 to IOB0 in TIOR\_5, and bits CCLR1 and CCLR0 in TCR\_5), bit NDER7 in NDERL, bit P27DDR, and bit ITS15 in ITSR.

| TPU channel 5 settings | (1) in table<br>below | (2) in table below                 |            |            |  |  |  |

|------------------------|-----------------------|------------------------------------|------------|------------|--|--|--|

| P27DDR                 | —                     | 0                                  | 1          | 1          |  |  |  |

| NDER7                  | —                     | _                                  | 0          | 1          |  |  |  |

| Pin function           | TIOCB5 output         | P27 input                          | P27 output | PO7 output |  |  |  |

|                        |                       | TIOCB5 input <sup>*1</sup>         |            |            |  |  |  |

|                        |                       | IRQ5 interrupt input <sup>*2</sup> |            |            |  |  |  |

Notes: 1. TIOCB5 input when MD3 to MD0 = B'0000 or  $B'01 \times x$  and IOB3 = 1.

2.  $\overline{\text{IRQ15}}$  input when ITS15 = 1.

| TPU channel 5 settings | (2)                        | (1)                                        | (2)    | (2)               | (1)                   | (2)  |  |

|------------------------|----------------------------|--------------------------------------------|--------|-------------------|-----------------------|------|--|

| MD3 to MD0             | B'0000                     | , B'01××                                   | B'0010 |                   | B'0011                |      |  |

| IOB3 to IOB0           | B'0000<br>B'0100<br>B'1××× | B'0001 to<br>B'0011<br>B'0101 to<br>B'0111 | B'××00 | Other than B'××00 |                       |      |  |

| CCLR1, CCLR0           |                            |                                            |        |                   | Other<br>than<br>B'10 | B'10 |  |

| Output function        | —                          | Output<br>compare<br>output                |        |                   | PWM mode<br>2 output  | —    |  |

Legend:

×: Don't care

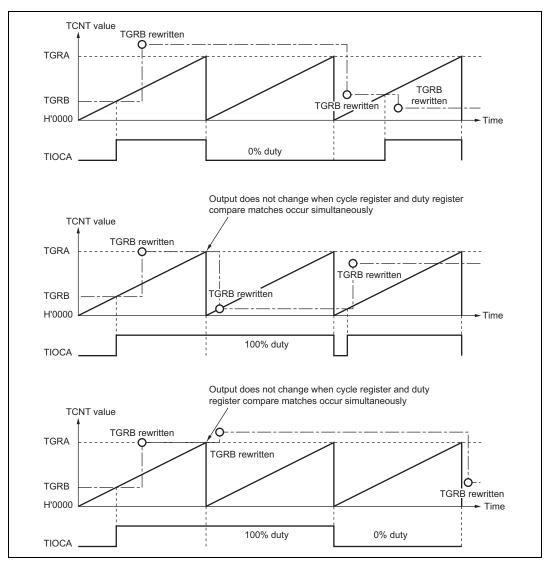

Figure 11.23 shows examples of PWM waveform output with 0% duty cycle and 100% duty cycle in PWM mode.

Figure 11.23 Example of PWM Mode Operation (3)

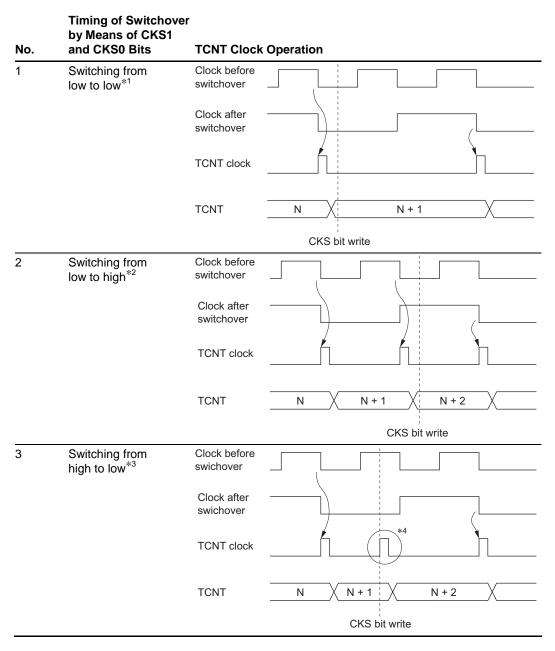

#### Table 13.5 Switching of Internal Clock and TCNT Operation

Rev.7.00 Mar. 18, 2009 page 674 of 1136 REJ09B0109-0700

# Section 18 D/A Converter

# **18.1** Features

D/A converter features are listed below.

- 8-bit resolution

- Output channels:

Six channels for the H8S/2378  $0.18\mu m$  F-ZTAT Group, H8S/2378R  $0.18\mu m$  F-ZTAT Group, H8S/2377, and H8S/2377R

Two channels for the H8S/2375, H8S/2375R, H8S/2373, and H8S/2373R

- Maximum conversion time of 10 µs (with 20 pF load)

- Output voltage of 0 V to Vref

- D/A output hold function in software standby mode

- Setting the module stop mode

|                                                                      | Store          |                     | utable Area                             |             | Selected            | MAT                                 |  |

|----------------------------------------------------------------------|----------------|---------------------|-----------------------------------------|-------------|---------------------|-------------------------------------|--|

|                                                                      | Stora          | DIe/Exect           | 1                                       |             | Selected            |                                     |  |

| Item                                                                 | On-chip<br>RAM | User<br>Boot<br>MAT | External<br>Space<br>(Expanded<br>Mode) | User<br>MAT | User<br>Boot<br>MAT | Embedded<br>Program<br>Storage Area |  |

| Storage Area for<br>Program Data                                     | 0              | ×*1                 | 0                                       |             |                     |                                     |  |

| Operation for<br>Selection of On-chip<br>Program to be<br>Downloaded | 0              | 0                   | 0                                       |             | 0                   |                                     |  |

| Operation for Writing<br>H'A5 to FKEY                                | 0              | 0                   | 0                                       |             | 0                   |                                     |  |

| Execution of Writing<br>SC0 = 1 to FCCS<br>(Download)                | 0              | ×                   | ×                                       |             |                     | 0                                   |  |

| Operation for FKEY<br>Clear                                          | 0              | 0                   | 0                                       |             | 0                   |                                     |  |

| Determination of<br>Download Result                                  | 0              | 0                   | 0                                       |             | 0                   |                                     |  |

| Operation for<br>Download Error                                      | 0              | 0                   | 0                                       |             | 0                   |                                     |  |

| Operation for Settings<br>of Initial Parameter                       | 0              | 0                   | 0                                       |             | 0                   |                                     |  |

| Execution of<br>Initialization                                       | 0              | ×                   | ×                                       |             | 0                   |                                     |  |

| Determination of<br>Initialization Result                            | 0              | 0                   | 0                                       |             | 0                   |                                     |  |

| Operation for<br>Initialization Error                                | 0              | 0                   | 0                                       |             | 0                   |                                     |  |

| NMI Handling Routine                                                 | 0              | ×                   | 0                                       |             | 0                   |                                     |  |

| Operation for Interrupt<br>Inhibit                                   | 0              | 0                   | 0                                       |             | 0                   |                                     |  |

| Switching MATs by<br>FMATS                                           | 0              | ×                   | ×                                       | 0           |                     |                                     |  |

| Operation for Writing<br>H'5A to FKEY                                | 0              | ×                   | 0                                       | 0           |                     |                                     |  |

### Table 21.8 (3) Useable Area for Programming in User Boot Mode

- ERROR: (one byte): Error code

- H'11: Checksum error

- H'53: Programming error An error has occurred in programming and programming cannot be continued.

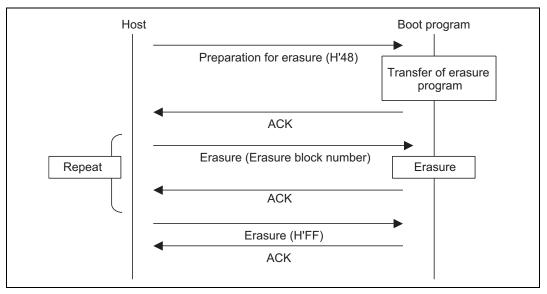

#### (10) Erasure

Erasure is performed with the erasure selection and block erasure command.

Firstly, erasure is selected by the erasure selection command and the boot program then erases the specified block. The command should be repeatedly executed if two or more blocks are to be erased. Sending a block-erasure command from the host with the block number H'FF will stop the erasure operating. On completion of erasing, the boot program will wait for selection of programming or erasing.

The sequences of the issuing of erasure selection commands and the erasure of data are shown in figure 21.22.

Figure 21.22 Erasure Sequence

### (a) Erasure Selection

The boot program will transfer the erasure program. User MAT data is erased by the transferred erasure program.

#### 24.2.2 Sleep Mode

**Transition to Sleep Mode:** When the SLEEP instruction is executed when the SSBY bit is 0 in SBYCR, the CPU enters the sleep mode. In sleep mode, CPU operation stops but the contents of the CPU's internal registers are retained. Other peripheral functions do not stop.

**Exiting Sleep Mode:** Sleep mode is exited by any interrupt, or signals at the  $\overline{\text{RES}}$ , or  $\overline{\text{STBY}}$  pins.

• Exiting Sleep Mode by Interrupts:

When an interrupt occurs, sleep mode is exited and interrupt exception processing starts. Sleep mode is not exited if the interrupt is disabled, or interrupts other than NMI are masked by the CPU.

- Exiting Sleep Mode by RES Pin: Setting the RES pin level low selects the reset state. After the stipulated reset input duration, driving the RES pin high starts the CPU performing reset exception processing.

- Exiting Sleep Mode by STBY Pin: When the STBY pin level is driven low, a transition is made to hardware standby mode.

#### 24.2.3 Software Standby Mode

**Transition to Software Standby Mode:** If a SLEEP instruction is executed when the SSBY bit in SBYCR is set to 1, software standby mode is entered. In this mode, the CPU, on-chip peripheral functions, and oscillator all stop. However, the contents of the CPU's internal registers, RAM data, and the states of on-chip peripheral functions other than the SCI and A/D converter, and I/O ports, are retained. Whether the address bus and bus control signals are placed in the high-impedance state or retain the output state can be specified by the OPE bit in SBYCR.

In this mode the oscillator stops, and therefore power dissipation is significantly reduced.

**Clearing Software Standby Mode:** Software standby mode is cleared by an external interrupt (NMI pin, or pins  $\overline{IRQ0}$  to  $\overline{IRQ15}$ ), or by means of the  $\overline{RES}$  pin or  $\overline{STBY}$  pin. Setting the SSI bit in SSIER to 1 enables  $\overline{IRQ0}$  to  $\overline{IRQ15}$  to be used as software standby mode clearing sources.

Clearing with an Interrupt:

When an NMI or IRQ0 to IRQ15 interrupt request signal is input, clock oscillation starts, and after the elapse of the time set in bits STS3 to STS0 in SBYCR, stable clocks are supplied to the entire LSI, software standby mode is cleared, and interrupt exception handling is started.

When clearing software standby mode with an IRQ0 to IRQ15 interrupt, set the corresponding enable bit to 1 and ensure that no interrupt with a higher priority than interrupts IRQ0 to IRQ15 is

### 24.4.3 EXDMAC, DMAC, and DTC Module Stop

Depending on the operating status of the EXDMAC, DMAC, or DTC, the MSTP14 to MSTP13 and may not be set to 1. Setting of the EXDMAC, DMAC, or DTC module stop mode should be carried out only when the respective module is not activated.

For details, refer to section 8, EXDMA Controller (EXDMAC), section 7, DMA Controller (DMAC), and section 9, Data Transfer Controller (DTC).

Note: The EXDMAC is not supported by the H8S/2375, H8S/2375R, H8S/2373, and H8S/2373R.

### 24.4.4 On-Chip Peripheral Module Interrupts

Relevant interrupt operations cannot be performed in module stop mode. Consequently, if module stop mode is entered when an interrupt has been requested, it will not be possible to clear the CPU interrupt source or the DMAC or DTC activation source.

Interrupts should therefore be disabled before entering module stop mode.

Note: The EXDMAC is not supported by the H8S/2375, H8S/2375R, H8S/2373, and H8S/2373R

### 24.4.5 Writing to MSTPCR, EXMSTPCR

MSTPCR and EXMSTPCR should only be written to by the CPU.

#### 24.4.6 Notes on Clock Division Mode

The following points should be noted in clock division mode.

- Select the clock division ratio specified by the SCK2 to SCK0 bits so that the frequency of φ is within the operation guaranteed range of clock cycle time tcyc shown in the Electrical Characteristics. In other words, the range of φ must be specified to 8 MHz (min); outside of this range (φ < 8 MHz) must be prevented.</li>

- All the on-chip peripheral modules operate on the φ. Therefore, note that the time processing

of modules such as a timer and SCI differ before and after changing the clock division ratio. In

addition, wait time for clearing software standby mode differs by changing the clock division

ratio.

- Note that the frequency of  $\phi$  will be changed by changing the clock division ratio.

#### (2) Control Signal Timing

#### Table 26.32 Control Signal Timing

Conditions:  $V_{CC} = 3.0 \text{ V}$  to 3.6 V,  $AV_{CC} = 3.0 \text{ V}$  to 3.6 V,  $V_{ref} = 3.0 \text{ V}$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}$ ,  $\phi = 8 \text{ MHz}$  to 34 MHz,  $T_a = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$  (regular specifications),  $T_a = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (wide-range specifications)

| Item                                                     | Symbol            | Min. | Max. | Unit             | Test Conditions |

|----------------------------------------------------------|-------------------|------|------|------------------|-----------------|

| RES setup time                                           | t <sub>RESS</sub> | 200  | _    | ns               | Figure 26.5     |

| RES pulse width                                          | t <sub>RESW</sub> | 20   | —    | t <sub>cyc</sub> | _               |

| NMI setup time                                           | t <sub>NMIS</sub> | 150  | _    | ns               | Figure 26.6     |

| NMI hold time                                            | t <sub>NMIH</sub> | 10   | —    | _                |                 |

| NMI pulse width (in recovery from software standby mode) | t <sub>NMIW</sub> | 200  | _    | _                |                 |

| IRQ setup time                                           | t <sub>IRQS</sub> | 150  | _    | ns               | _               |

| IRQ hold time                                            | t <sub>IRQH</sub> | 10   | _    |                  |                 |

| IRQ pulse width (in recovery from software standby mode) | t <sub>IRQW</sub> | 200  |      |                  |                 |