Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                        |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 33MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI, SmartCard                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 96                                                                              |

| Program Memory Size        | 384KB (384K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 24K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b; D/A 6x8b                                                            |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP                                                                        |

| Supplier Device Package    | 144-LQFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2377rvfq33wv |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin No.                                                           |                                                |                                                                                          |                                                                                         |                                    |                                                |                  |                                                                     |

|-------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------|------------------|---------------------------------------------------------------------|

| Туре                                                              | Symbol                                         | H8S/2378<br>0.18μm<br>F-ZTAT Group,<br>H8S/2378R<br>0.18μm<br>F-ZTAT Group<br>(LQFP-144) | H8S/2378<br>0.18μm<br>F-ZTAT Group,<br>H8S/2378R<br>0.18μm<br>F-ZTAT Group<br>(LGA-145) | H8S/2377                           | H8S/2375<br>H8S/2373<br>H8S/2375R<br>H8S/2373R | 1/0              | Function                                                            |

| Program-<br>mable<br>pulse<br>generator<br>(PPG)                  | PO15 to<br>PO0                                 | 49 to 42,<br>58 to 51                                                                    | N5, M6, L5,<br>M5, N4, L4,<br>M4, L3, M8,<br>N7, K8, K7,<br>K6, N6, M7,<br>L6           | 49 to 42,<br>58 to 51              | 49 to 42,<br>58 to 51                          | Output           | Pulse output pins.                                                  |

| 8-bit timer<br>(TMR)                                              | TMO0<br>TMO1                                   | 105,<br>106                                                                              | C12,<br>C13                                                                             | 105,<br>106                        | 105,<br>106                                    | Output           | Waveform output<br>pins with output<br>compare function.            |

|                                                                   | TMCI0<br>TMCI1                                 | 83,<br>104                                                                               | J10,<br>D10                                                                             | 83,<br>104                         | 83,<br>104                                     | Input            | External event input pins.                                          |

|                                                                   | TMRI0<br>TMRI1                                 | 82,<br>81                                                                                | K13,<br>J12                                                                             | 82,<br>81                          | 82,<br>81                                      | Input            | Counter reset input pins.                                           |

| Watchdog<br>timer<br>(WDT)                                        | WDTOVF                                         | 39                                                                                       | M3                                                                                      | 39                                 | 39                                             | Output           | Counter overflow<br>signal output pin in<br>watchdog timer<br>mode. |

| Serial<br>commu-<br>nication<br>interface<br>(SCI)/<br>smart card | TxD4<br>TxD3<br>TxD2<br>TxD1<br>TxD0/<br>IrTxD | 54,<br>33,<br>133,<br>141,<br>142                                                        | K6,<br>L2,<br>A6,<br>B3,<br>C4                                                          | 54,<br>33,<br>133,<br>141,<br>142  | 54,<br>33,<br>133,<br>141,<br>142              | Output           | Data output pins.                                                   |

| interface<br>(SCI_0<br>with IrDA<br>function)                     | RxD4<br>RxD3<br>RxD2<br>RxD1<br>RxD0/<br>IrRxD | 55,<br>59,<br>134,<br>139,<br>140                                                        | K7,<br>L7,<br>B5,<br>C5,<br>A4                                                          | 55,<br>59,<br>134,<br>139,<br>140  | 55,<br>59,<br>134,<br>139,<br>140              | Input            | Data input pins.                                                    |

|                                                                   | SCK4<br>SCK3<br>SCK2<br>SCK1<br>SCK0           | 138,<br>61,<br>135,<br>137,<br>138                                                       | B4,<br>N8,<br>C6,<br>A5,<br>B4                                                          | 138,<br>61,<br>135,<br>137,<br>138 | 138,<br>61,<br>135,<br>137,<br>138             | Input/<br>output | Clock input/output pins.                                            |

| Туре                                  | Symbol           | H8S/2378<br>0.18μm<br>F-ZTAT Group,<br>H8S/2378R<br>0.18μm<br>F-ZTAT Group<br>(LQFP-144) | H8S/2378<br>0.18μm<br>F-ZTAT Group,<br>H8S/2378R<br>0.18μm<br>F-ZTAT Group<br>(LGA-145) | H8S/2377 | H8S/2375<br>H8S/2373<br>H8S/2375R<br>H8S/2373R | -<br>I/O | Function                                                                                                                                    |

|---------------------------------------|------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------|------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| A/D<br>converter,<br>D/A<br>converter | AV <sub>CC</sub> | 111                                                                                      | B11                                                                                     | 111      | 111                                            | Input    | The analog power-<br>supply pin for the<br>A/D converter and<br>D/A converter.                                                              |

|                                       |                  |                                                                                          |                                                                                         |          |                                                |          | When the A/D<br>converter and D/A<br>converter are not<br>used, this pin<br>should be<br>connected to the<br>system power<br>supply (+3 V). |

|                                       | $AV_{SS}$        | 129                                                                                      | A7                                                                                      | 129      | 129                                            | Input    | The ground pin for<br>the A/D converter<br>and D/A converter.                                                                               |

|                                       |                  |                                                                                          |                                                                                         |          |                                                |          | This pin should be<br>connected to the<br>system power<br>supply (0 V).                                                                     |

|                                       | Vref             | 112                                                                                      | B12                                                                                     | 112      | 112                                            | Input    | The reference<br>voltage input pin for<br>the A/D converter<br>and D/A converter.                                                           |

|                                       |                  |                                                                                          |                                                                                         |          |                                                |          | When the A/D<br>converter and D/A<br>converter are not<br>used, this pin<br>should be<br>connected to the<br>system power<br>supply (+3 V). |

### 2.2.2 Advanced Mode

Address space

Linear access to a maximum address space of 16 Mbytes is possible.

• Extended registers (En)

The extended registers (E0 to E7) can be used as 16-bit registers. They can also be used as the upper 16-bit segments of 32-bit registers or address registers.

• Instruction set

All instructions and addressing modes can be used.

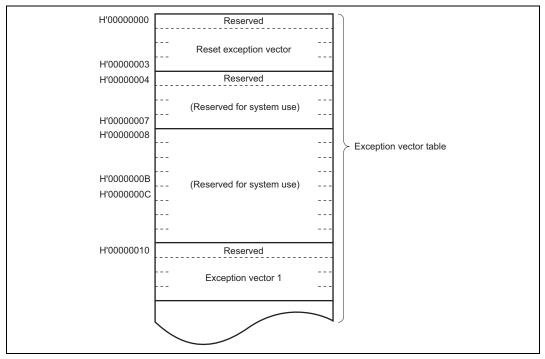

• Exception vector table and memory indirect branch addresses

In advanced mode, the top area starting at H'00000000 is allocated to the exception vector table in 32-bit units. In each 32 bits, the upper 8 bits are ignored and a branch address is stored in the lower 24 bits (see figure 2.3). For details of the exception vector table, see section 4, Exception Handling.

Figure 2.3 Exception Vector Table (Advanced Mode)

## 2.8 Processing States

The H8S/2000 CPU has five main processing states: the reset state, exception handling state, program execution state, bus-released state, and program stop state. Figure 2.13 indicates the state transitions.

• Reset state

In this state the CPU and internal peripheral modules are all initialized and stopped. When the  $\overline{\text{RES}}$  input goes low, all current processing stops and the CPU enters the reset state. All interrupts are masked in the reset state. Reset exception handling starts when the  $\overline{\text{RES}}$  signal changes from low to high. For details, refer to section 4, Exception Handling. The reset state can also be entered by a watchdog timer overflow.

• Exception-handling state

The exception-handling state is a transient state that occurs when the CPU alters the normal processing flow due to an exception source, such as, a reset, trace, interrupt, or trap instruction. The CPU fetches a start address (vector) from the exception vector table and branches to that address. For further details, refer to section 4, Exception Handling.

• Program execution state

In this state the CPU executes program instructions in sequence.

Bus-released state

In a product which has a DMA controller and a data transfer controller (DTC), the bus-released state occurs when the bus has been released in response to a bus request from a bus master other than the CPU. While the bus is released, the CPU halts operations.

• Program stop state

This is a power-down state in which the CPU stops operating. The program stop state occurs when a SLEEP instruction is executed or the CPU enters hardware standby mode. For details, refer to section 24, Power-Down Modes.

| Bit          | Bit Name       | Initial Value | R/W                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                  |

|--------------|----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5            | RLW1           | 0             | R/W                                                                                                                                                                                                                                                                | Refresh Cycle Wait Control                                                                                                                                                                                                                                                                   |

| 4 RLW0 0 R/V |                | R/W           | These bits select the number of wait states to be<br>inserted in a DRAM interface CAS-before-RAS<br>refresh cycle/synchronous DRAM interface auto-<br>refresh cycle. This setting applies to all areas<br>designated as DRAM/continuous synchronous<br>DRAM space. |                                                                                                                                                                                                                                                                                              |

|              |                |               |                                                                                                                                                                                                                                                                    | 00: No wait state inserted                                                                                                                                                                                                                                                                   |

|              |                |               |                                                                                                                                                                                                                                                                    | 01: 1 wait state inserted                                                                                                                                                                                                                                                                    |

|              |                |               |                                                                                                                                                                                                                                                                    | 10: 2 wait states inserted                                                                                                                                                                                                                                                                   |

|              |                |               |                                                                                                                                                                                                                                                                    | 11: 3 wait states inserted                                                                                                                                                                                                                                                                   |

| 3            | SLFRF          | 0             | R/W                                                                                                                                                                                                                                                                | Self-Refresh Enable                                                                                                                                                                                                                                                                          |

|              |                |               |                                                                                                                                                                                                                                                                    | If this bit is set to 1, DRAM/synchronous DRAM<br>self-refresh mode is selected when a transition is<br>made to the software standby state. This bit is valid<br>when the RFSHE bit is set to 1, enabling refresh<br>operations. It is cleared after recovery from<br>software standby mode. |

|              |                |               |                                                                                                                                                                                                                                                                    | 0: Self-refreshing is disabled                                                                                                                                                                                                                                                               |

|              |                |               |                                                                                                                                                                                                                                                                    | 1: Self-refreshing is enabled                                                                                                                                                                                                                                                                |

| 2            | TPCS2          | 0             | R/W                                                                                                                                                                                                                                                                | Self-Refresh Precharge Cycle Control                                                                                                                                                                                                                                                         |

| 1<br>0       | TPCS1<br>TPCS0 | 0<br>0        | R/W<br>R/W                                                                                                                                                                                                                                                         | These bits select the number of states in the precharge cycle immediately after self-refreshing.                                                                                                                                                                                             |

|              |                |               |                                                                                                                                                                                                                                                                    | The number of states in the precharge cycle<br>immediately after self-refreshing are added to the<br>number of states set by bits TPC1 and TPC0 in<br>DRACCR.                                                                                                                                |

|              |                |               |                                                                                                                                                                                                                                                                    | 000: [TPC set value] states                                                                                                                                                                                                                                                                  |

|              |                |               |                                                                                                                                                                                                                                                                    | 001: [TPC set value + 1] states                                                                                                                                                                                                                                                              |

|              |                |               |                                                                                                                                                                                                                                                                    | 010: [TPC set value + 2] states                                                                                                                                                                                                                                                              |

|              |                |               |                                                                                                                                                                                                                                                                    | 011: [TPC set value + 3] states                                                                                                                                                                                                                                                              |

|              |                |               |                                                                                                                                                                                                                                                                    | 100: [TPC set value + 4] states                                                                                                                                                                                                                                                              |

|              |                |               |                                                                                                                                                                                                                                                                    | 101: [TPC set value + 5] states                                                                                                                                                                                                                                                              |

|              |                |               |                                                                                                                                                                                                                                                                    | 110: [TPC set value + 6] states                                                                                                                                                                                                                                                              |

|              |                |               |                                                                                                                                                                                                                                                                    | 111: [TPC set value + 7] states                                                                                                                                                                                                                                                              |

- a refresh operation is initiated in the RAS down state

- self-refreshing is performed

- the chip enters software standby mode

- the external bus is released

- the RCDM bit or BE bit is cleared to 0

If a transition is made to the all-module-clocks-stopped mode in the  $\overline{RAS}$  down state, the clock will stop with  $\overline{RAS}$  low. To enter the all-module-clocks-stopped mode with  $\overline{RAS}$  high, the RCDM bit must be cleared to 0 before executing the SLEEP instruction.

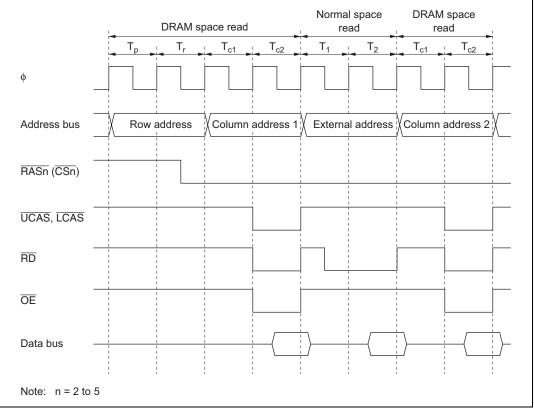

Figure 6.32 Example of Operation Timing in RAS Down Mode (RAST = 0, CAST = 0)

| Bit                          | Bit Name                                              | Initial Value                                       | R/W                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------|-------------------------------------------------------|-----------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit<br>4<br>3<br>2<br>1<br>0 | Bit Name<br>DARA4<br>DARA3<br>DARA2<br>DARA1<br>DARA0 | Initial Value 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | R/W<br>R/W<br>R/W<br>R/W | Destination Address Repeat Area<br>These bits specify the destination address<br>(EDDAR) repeat area. The repeat area function<br>updates the specified lower address bits, leaving<br>the remaining upper address bits always the same.<br>A repeat area size of 2 bytes to 8 Mbytes can be<br>specified. The setting interval is a power-of-two<br>number of bytes. When repeat area overflow<br>results from incrementing or decrementing an<br>address, the lower address is the start address of<br>the repeat area in the case of address<br>incrementing, or the last address of the repeat area<br>in the case of address decrementing. If the DARIE<br>bit is set to 1, an interrupt can be requested when<br>repeat area overflow occurs.<br>00000: Not designated as repeat area<br>00001: Lower 1 bit (2-byte area) designated as<br>repeat area |

|                              |                                                       |                                                     |                          | 00010: Lower 2 bits (4-byte area) designated as<br>repeat area<br>00011: Lower 3 bits (8-byte area) designated as<br>repeat area<br>00100: Lower 4 bits (16-byte area) designated as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                              |                                                       |                                                     |                          | repeat area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                              |                                                       |                                                     |                          | 10011: Lower 19 bits (512-kbyte area) designated<br>as repeat area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                              |                                                       |                                                     |                          | <ul><li>10100: Lower 20 bits (1-Mbyte area) designated as repeat area</li><li>10101: Lower 21 bits (2-Mbyte area) designated as</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                              |                                                       |                                                     |                          | repeat area<br>10110: Lower 22 bits (4-Mbyte area) designated as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                              |                                                       |                                                     |                          | repeat area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                              |                                                       |                                                     |                          | 10111: Lower 23 bits (8-Mbyte area) designated as<br>repeat area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                              |                                                       |                                                     |                          | 11×××: Setting prohibited                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Legend: ×: Don't care

### • P25/PO5/TIOCB4/(IRQ13)

The pin function is switched as shown below according to the combination of the TPU channel 4 settings (by bits MD3 to MD0 in TMDR\_4, bits IOB3 to IOB0 in TIOR\_4, and bits CCLR1 and CCLR0 in TCR\_4), bit NDER5 in NDERL, bit P25DDR, and bit ITS13 in ITSR.

| TPU channel 4 settings  | (1) in table<br>below | (2) in table below |                            |            |  |  |

|-------------------------|-----------------------|--------------------|----------------------------|------------|--|--|

| P25DDR                  |                       | 0                  | 1                          | 1          |  |  |

| NDER5                   |                       |                    | 0                          | 1          |  |  |

| Pin function            | TIOCB4 output         | P25 input          | P25 output                 | PO5 output |  |  |

|                         |                       |                    | TIOCB4 input <sup>*1</sup> |            |  |  |

| IRQ13 interrupt input*2 |                       |                    |                            |            |  |  |

Notes: 1. TIOCB4 input when MD3 to MD0 = B'0000 or B'01×× and IOB3 to IOB0 = B'10××.

2.  $\overline{\text{IRQ13}}$  input when ITS13 = 1.

| TPU channel 4 settings | (2)                        | (1)                                        | (2)    | (2)    | (1)                   | (2)      |

|------------------------|----------------------------|--------------------------------------------|--------|--------|-----------------------|----------|

| MD3 to MD0             | B'0000                     | , B'01××                                   | B'0010 |        | B'0011                |          |

| IOB3 to IOB0           | B'0000<br>B'0100<br>B'1××× | B'0001 to<br>B'0011<br>B'0101 to<br>B'0111 |        | B'××00 | Other than            | ר B'××00 |

| CCLR1, CCLR0           |                            |                                            |        |        | Other<br>than<br>B'10 | B'10     |

| Output function        | _                          | Output<br>compare<br>output                |        |        | PWM mode<br>2 output  | —        |

Legend:

×: Don't care

| Table | 11.13 | TIORL | 0 |

|-------|-------|-------|---|

|-------|-------|-------|---|

|               |               |               |               | Description                         |                                               |  |  |

|---------------|---------------|---------------|---------------|-------------------------------------|-----------------------------------------------|--|--|

| Bit 7<br>IOD3 | Bit 6<br>IOD2 | Bit 5<br>IOD1 | Bit 4<br>IOD0 | TGRD_0<br>Function                  | TIOCD0 Pin Function                           |  |  |

| 0             | 0             | 0             | 0             | Output                              | Output disabled                               |  |  |

|               |               |               | 1             | compare<br>register <sup>*2</sup>   | Initial output is 0 output                    |  |  |

|               |               |               |               | register                            | 0 output at compare match                     |  |  |

|               |               | 1             | 0             | _                                   | Initial output is 0 output                    |  |  |

|               |               |               |               |                                     | 1 output at compare match                     |  |  |

|               |               |               | 1             | _                                   | Initial output is 0 output                    |  |  |

|               |               |               |               |                                     | Toggle output at compare match                |  |  |

|               | 1             | 0             | 0             |                                     | Output disabled                               |  |  |

|               |               |               | 1             |                                     | Initial output is 1 output                    |  |  |

|               |               |               |               |                                     | 0 output at compare match                     |  |  |

|               |               | 1             | 0             |                                     | Initial output is 1 output                    |  |  |

|               |               |               |               |                                     | 1 output at compare match                     |  |  |

|               |               |               | 1             | _                                   | Initial output is 1 output                    |  |  |

|               |               |               |               |                                     | Toggle output at compare match                |  |  |

| 1             | 0             | 0             | 0             | Input                               | Capture input source is TIOCD0 pin            |  |  |

|               |               |               |               | capture<br>– register <sup>*2</sup> | Input capture at rising edge                  |  |  |

|               |               |               | 1             |                                     | Capture input source is TIOCD0 pin            |  |  |

|               |               |               |               |                                     | Input capture at falling edge                 |  |  |

|               |               | 1             | ×             | _                                   | Capture input source is TIOCD0 pin            |  |  |

|               |               |               |               |                                     | Input capture at both edges                   |  |  |

|               | 1             | х             | ×             |                                     | Capture input source is channel 1/count clock |  |  |

|               |               |               |               |                                     | Input capture at TCNT_1 count-up/count-down*1 |  |  |

Legend: x: Don't care

Notes: 1. When bits TPSC2 to TPSC0 in TCR\_1 are set to B'000 and  $\phi/1$  is used as the TCNT\_1 count clock, this setting is invalid and input capture is not generated.

2. When the BFB bit in TMDR\_0 is set to 1 and TGRD\_0 is used as a buffer register, this setting is invalid and input capture/output compare is not generated.

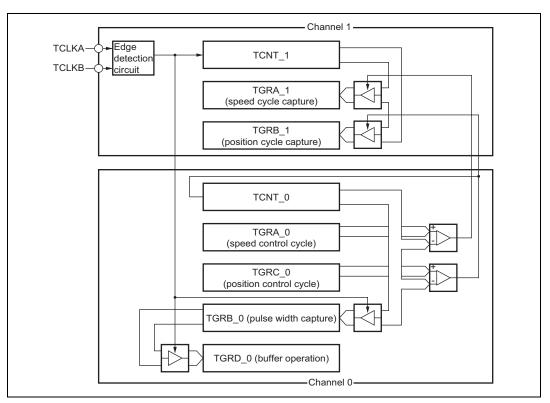

Figure 11.29 Phase Counting Mode Application Example

### **11.5** Interrupt Sources

There are three kinds of TPU interrupt source: TGR input capture/compare match, TCNT overflow, and TCNT underflow. Each interrupt source has its own status flag and enable/disable bit, allowing generation of interrupt request signals to be enabled or disabled individually.

When an interrupt request is generated, the corresponding status flag in TSR is set to 1. If the corresponding enable/disable bit in TIER is set to 1 at this time, an interrupt is requested. The interrupt request is cleared by clearing the status flag to 0.

Relative channel priorities can be changed by the interrupt controller, but the priority order within a channel is fixed. For details, see section 5, Interrupt Controller.

Table 11.36 lists the TPU interrupt sources.

## Renesas

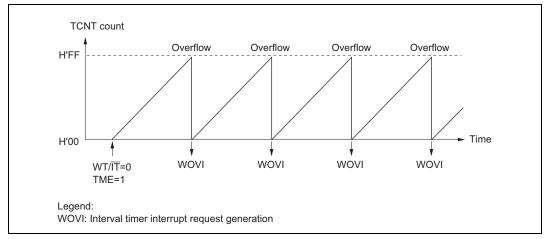

Figure 14.3 Operation in Interval Timer Mode

## 14.5 Interrupt Source

During interval timer mode operation, an overflow generates an interval timer interrupt (WOVI). The interval timer interrupt is requested whenever the OVF flag is set to 1 in TCSR. OVF must be cleared to 0 in the interrupt handling routine.

#### Table 14.2WDT Interrupt Source

| Name | Interrupt Source | Interrupt Flag | DTC Activation |

|------|------------------|----------------|----------------|

| WOVI | TCNT overflow    | OVF            | Impossible     |

### 14.6 Usage Notes

#### 14.6.1 Notes on Register Access

The watchdog timer's TCNT, TCSR, and RSTCSR registers differ from other registers in being more difficult to write to. The procedures for writing to and reading these registers are given below.

### Writing to TCNT, TCSR, and RSTCSR

TCNT and TCSR must be written to by a word transfer instruction. They cannot be written to by a byte transfer instruction.

## 15.6.4 Serial Data Reception (Clocked Synchronous Mode)

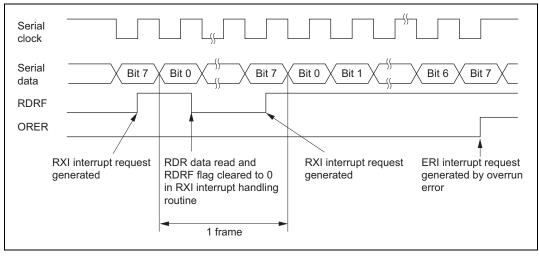

Figure 15.18 shows an example of SCI operation for reception in clocked synchronous mode. In serial reception, the SCI operates as described below.

- 1. The SCI performs internal initialization in synchronization with a synchronization clock input or output, starts receiving data, and stores the received data in RSR.

- 2. If an overrun error (when reception of the next data is completed while the RDRF flag is still set to 1) occurs, the ORER bit in SSR is set to 1. If the RIE bit in SCR is set to 1 at this time, an ERI interrupt request is generated. Receive data is not transferred to RDR. The RDRF flag remains to be set to 1.

- 3. If reception finishes successfully, the RDRF bit in SSR is set to 1, and receive data is transferred to RDR. If the RIE bit in SCR is set to 1 at this time, an RXI interrupt request is generated. Because the RXI interrupt routine reads the receive data transferred to RDR before reception of the next receive data has finished, continuous reception can be enabled.

Figure 15.18 Example of SCI Operation in Reception

Transfer cannot be resumed while a receive error flag is set to 1. Accordingly, clear the ORER, FER, PER, and RDRF bits to 0 before resuming reception. Figure 15.19 shows a sample flowchart for serial data reception.

#### Section 18 D/A Converter

• DACR45 (Available only for the H8S/2377, H8S/2377R, H8S/2378 0.18µm F-ZTAT Group, and H8S/2378R 0.18µm F-ZTAT Group)

| Bit  | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                                                                                   |

|------|----------|---------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | DAOE4    | 0             | R/W | D/A Output Enable 5                                                                                                                                                                                                                                           |

|      |          |               |     | Controls D/A conversion and analog output.                                                                                                                                                                                                                    |

|      |          |               |     | 0: Analog output (DA5) is disabled                                                                                                                                                                                                                            |

|      |          |               |     | 1: Channel 5 D/A conversion is enabled; analog output (DA5) is enabled                                                                                                                                                                                        |

| 6    | DAOE5    | 0             | R/W | D/A Output Enable 4                                                                                                                                                                                                                                           |

|      |          |               |     | Controls D/A conversion and analog output.                                                                                                                                                                                                                    |

|      |          |               |     | 0: Analog output (DA4) is disabled                                                                                                                                                                                                                            |

|      |          |               |     | 1: Channel 4 D/A conversion is enabled; analog output<br>(DA4) is enabled                                                                                                                                                                                     |

| 5    | DAE      | 0             | R/W | D/A Enable                                                                                                                                                                                                                                                    |

|      |          |               |     | Used together with the DAOE4 and DAOE5 bits to control D/A conversion. When the DAE bit is cleared to 0, channel 4 and 5 D/A conversions are controlled independently. When the DAE bit is set to 1, channel 4 and 5 D/A conversions are controlled together. |

|      |          |               |     | Output of conversion results is always controlled independently by the DAOE4 and DAOE5 bits. For details, see table 18.4.                                                                                                                                     |

| 4 to | _        | All 1         | —   | Reserved                                                                                                                                                                                                                                                      |

| 0    |          |               |     | These bits are always read as 1 and cannot be modified.                                                                                                                                                                                                       |

#### Table 18.4 Control of D/A Conversion

| Bit 5<br>DAE | Bit 7<br>DAOE5 | Bit 6<br>DAOE4              | Description                                                        |

|--------------|----------------|-----------------------------|--------------------------------------------------------------------|

| 0            | 0              | 0 0 D/A conversion disabled |                                                                    |

|              |                | 1                           | Channel 4 D/A conversion enabled, channel5 D/A conversion disabled |

|              | 1              | 0                           | Channel 5 D/A conversion enabled, channel4 D/A conversion disabled |

|              |                | 1                           | Channel 4 and 5 D/A conversions enabled                            |

| 1            | 0              | 0                           | D/A conversion disabled                                            |

|              |                | 1                           | Channel 4 and 5 D/A conversions enabled                            |

|              | 1              | 0                           | _                                                                  |

|              |                | 1                           | _                                                                  |

## 21.3 Register Descriptions

The registers/parameters which control flash memory are shown as follows.

- Flash code control status register (FCCS)

- Flash program code select register (FPCS)

- Flash erase code select register (FECS)

- Flash key code register (FKEY)

- Flash MAT select register (FMATS)

- Flash transfer destination address register (FTDAR)

- Download pass and fail result (DPFP)

- Flash pass and fail result (FPFR)

- Flash multipurpose address area (FMPAR)

- Flash multipurpose data destination area (FMPDR)

- Flash erase Block select (FEBS)

- Flash program and erase frequency control (FPEFEQ)

- Flash vector address control register (FVACR)

There are several operating modes for accessing flash memory, for example, read mode/program mode.

There are two memory MATs: user MAT and user boot MAT. The dedicated registers/parameters are allocated for each operating mode and MAT selection. The correspondence of operating modes and registers/parameters for use is shown in table 21.3.

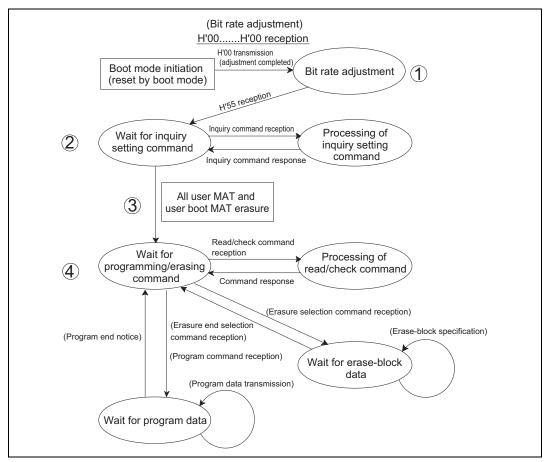

programming/erasing command. The erasure must be used when the specified block is programmed without a reset start after programming is executed in boot mode. When programming can be executed by only one operation, all blocks are erased before the state for waiting programming/erasing/other command is entered. The erasing operation is not required.

— There are many commands other than programming/erasing. Examples are sum check, blank check (erasure check), and memory read of the user MAT/user boot MAT and acquisition of current status information.

Note that memory read of the user MAT/user boot MAT can only read the programmed data after all user MAT/user boot MAT has automatically been erased.

Figure 21.8 Overview of Boot Mode State Transition Diagram

### 23.5.3 Notes on Board Design

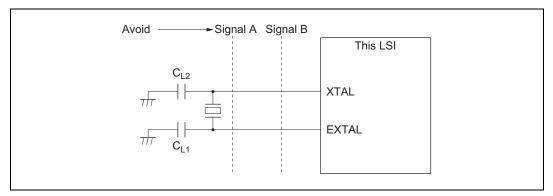

When using the crystal resonator, place the crystal resonator and its load capacitors as close as possible to the XTAL and EXTAL pins. Other signal lines should be routed away from the oscillation circuit to prevent induction from interfering with correct oscillation. See figure 23.6.

Figure 23.6 Note on Board Design for Oscillation Circuit

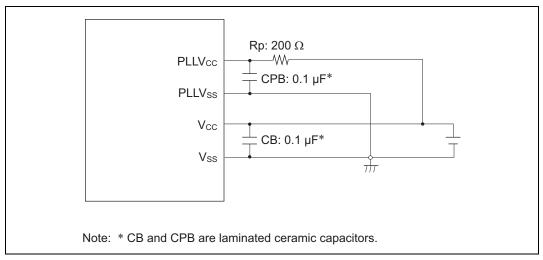

Figure 23.7 shows the external circuitry recommended for the PLL circuit. Separate PLLVcc and PLLVss from the other Vcc and Vss lines at the board power supply source, and be sure to insert bypass capacitors CPB and CB close to the pins.

Figure 23.7 Recommended External Circuitry for PLL Circuit

#### (4) DMAC and EXDMAC Timing

### Table 26.22 DMAC and EXDMAC Timing

$\begin{array}{ll} \mbox{Conditions:} & V_{CC} = 3.0 \mbox{ V to } 3.6 \mbox{ V}, \mbox{AV}_{CC} = 3.0 \mbox{ V to } 3.6 \mbox{ V}, \mbox{V}_{ref} = 3.0 \mbox{ V to } AV_{CC}, \mbox{V}_{SS} = AV_{SS} = \\ & 0 \mbox{ V}, \mbox{ } \phi = 8 \mbox{ MHz to } 35 \mbox{ MHz}, \mbox{T}_a = -20^{\circ}\mbox{C to } +75^{\circ}\mbox{C} \mbox{ (regular specifications)}, \\ & T_a = -40^{\circ}\mbox{C to } +85^{\circ}\mbox{C} \mbox{ (wide-range specifications)} \end{array}$

| Item               | Symbol              | Min. | Max. | Unit | Test Conditions         |

|--------------------|---------------------|------|------|------|-------------------------|

| DREQ setup time    | t <sub>DRQS</sub>   | 25   | _    | ns   | Figure 26.31            |

| DREQ hold time     | t <sub>DRQH</sub>   | 10   | _    | _    |                         |

| TEND delay time    | t <sub>TED</sub>    | _    | 18   | ns   | Figure 26.30            |

| DACK delay time 1  | t <sub>DACD1</sub>  | _    | 18   |      | Figures 26.28 and 26.29 |

| DACK delay time 2  | t <sub>DACD2</sub>  | _    | 18   |      |                         |

| EDREQ setup time   | t <sub>EDRQS</sub>  | 25   | _    | ns   | Figure 26.31            |

| EDREQ hold time    | t <sub>EDRQH</sub>  | 10   | _    |      |                         |

| ETEND delay time   | t <sub>ETED</sub>   | —    | 18   | ns   | Figure 26.30            |

| EDACK delay time 1 | t <sub>EDACD1</sub> | _    | 18   |      | Figure 26.28 and 26.29  |

| EDACK delay time 2 | t <sub>EDACD2</sub> |      | 18   |      |                         |

| EDRAK delay time   | t <sub>EDRKD</sub>  | _    | 18   | ns   | Figure 26.32            |

| Instruction           | 1           | 2        | 3             | 4             | 5             | 6      | 7 | 8 | 9 |

|-----------------------|-------------|----------|---------------|---------------|---------------|--------|---|---|---|

| BILD<br>#xx:3,@aa:8   | R:W 2nd     | R:B EA   | R:W<br>NEXT   |               |               |        |   |   |   |

| BILD<br>#xx:3,@aa:16  | R:W 2nd     | R:W 3rd  | R:B EA        | R:W<br>NEXT   |               |        |   |   |   |

| BILD<br>#xx:3,@aa:32  | R:W 2nd     | R:W 3rd  | R:W 4th       | R:B EA        | R:W<br>NEXT   |        |   |   |   |

| BIOR #xx:3,Rd         | R:W<br>NEXT |          |               |               |               |        |   |   |   |

| BIOR<br>#xx:3,@ERd    | R:W 2nd     | R:B EA   | R:W<br>NEXT   |               |               |        |   |   |   |

| BIOR<br>#xx:3,@aa:8   | R:W 2nd     | R:B EA   | R:W<br>NEXT   |               |               |        |   |   |   |

| BIOR<br>#xx:3,@aa:16  | R:W 2nd     | R:W 3rd  | R:B EA        | R:W<br>NEXT   |               |        |   |   |   |

| BIOR<br>#xx:3,@aa:32  | R:W 2nd     | R:W 3rd  | R:W 4th       | R:B EA        | R:W<br>NEXT   |        |   |   |   |

| BIST #xx:3,Rd         | R:W<br>NEXT |          |               |               |               |        |   |   |   |

| BIST<br>#xx:3,@ERd    | R:W 2nd     | R:B:M EA | R:W:M<br>NEXT | W:B EA        |               |        |   |   |   |

| BIST<br>#xx:3,@aa:8   | R:W 2nd     | R:B:M EA | R:W:M<br>NEXT | W:B EA        |               |        |   |   |   |

| BIST<br>#xx:3,@aa:16  | R:W 2nd     | R:W 3rd  | R:B:M EA      | R:W:M<br>NEXT | W:B EA        |        |   |   |   |

| BIST<br>#xx:3,@aa:32  | R:W 2nd     | R:W 3rd  | R:W 4th       | R:B:M EA      | R:W:M<br>NEXT | W:B EA |   |   |   |

| BIXOR #xx:3,Rd        | R:W<br>NEXT |          |               |               |               |        |   |   |   |

| BIXOR<br>#xx:3,@ERd   | R:W 2nd     | R:B EA   | R:W<br>NEXT   |               |               |        |   |   |   |

| BIXOR<br>#xx:3,@aa:8  | R:W 2nd     | R:B EA   | R:W<br>NEXT   |               |               |        |   |   |   |

| BIXOR<br>#xx:3,@aa:16 | R:W 2nd     | R:W 3rd  | R:B EA        | R:W<br>NEXT   |               |        |   |   |   |

| BIXOR<br>#xx:3,@aa:32 | R:W 2nd     | R:W 3rd  | R:W 4th       | R:B EA        | R:W<br>NEXT   |        |   |   |   |

| BLD #xx:3,Rd          | R:W<br>NEXT |          |               |               |               |        |   |   |   |

| BLD<br>#xx:3,@ERd     | R:W 2nd     | R:B EA   | R:W<br>NEXT   |               |               |        |   |   |   |

| Instru                 | ction    | 1           | 2                                   | 3                                   | 4                                   | 5                | 6      | 7 | 8 | 9 |

|------------------------|----------|-------------|-------------------------------------|-------------------------------------|-------------------------------------|------------------|--------|---|---|---|

| JMP<br>@@aa:<br>8      | Advanced | R:W<br>NEXT | R:W:M<br>aa:8                       | R:W aa:8                            | 1 State of<br>internal<br>operation | R:W EA           |        |   |   |   |

| JSR<br>@ERn            | Advanced | R:W<br>NEXT | R:W EA                              | W:W:M<br>Stack (H)                  | W:W<br>Stack (L)                    |                  |        |   |   |   |

| JSR<br>@aa:24          | Advanced | R:W 2nd     | 1 State of<br>internal<br>operation | R:W EA                              | W:W:M<br>Stack (H)                  | W:W<br>Stack (L) |        |   |   |   |

| JSR<br>@@aa:<br>8      | Advanced | R:W<br>NEXT | R:W:M<br>aa:8                       | R:W aa:8                            | W:W:M<br>Stack (H)                  | W:W<br>Stack (L) | R:W EA |   |   |   |

| LDC #xx                | :8,CCR   | R:W<br>NEXT |                                     |                                     |                                     |                  |        |   |   |   |

| LDC #xx                | :8,EXR   | R:W 2nd     | R:W<br>NEXT                         |                                     |                                     |                  |        |   |   |   |

| LDC Rs,                | CCR      | R:W<br>NEXT |                                     |                                     |                                     |                  |        |   |   |   |

| LDC Rs,                | EXR      | R:W<br>NEXT |                                     |                                     |                                     |                  |        |   |   |   |

| LDC<br>@ERs,C          | CR       | R:W 2nd     | R:W<br>NEXT                         | R:W EA                              |                                     |                  |        |   |   |   |

| LDC<br>@ERs,E          | XR       | R:W 2nd     | R:W<br>NEXT                         | R:W EA                              |                                     |                  |        |   |   |   |

| LDC<br>@(d:16,I<br>CR  | ERs),C   | R:W 2nd     | R:W 3rd                             | R:W<br>NEXT                         | R:W EA                              |                  |        |   |   |   |

| LDC<br>@(d:16,I<br>EXR | ERs),    | R:W 2nd     | R:W 3rd                             | R:W<br>NEXT                         | R:W EA                              |                  |        |   |   |   |

| LDC<br>@(d:32,I<br>CCR | ERs),    | R:W 2nd     | R:W 3rd                             | R:W 4th                             | R:W 5th                             | R:W<br>NEXT      | R:W EA |   |   |   |

| LDC<br>@(d:32,I<br>EXR | ERs),    | R:W 2nd     | R:W 3rd                             | R:W 4th                             | R:W 5th                             | R:W<br>NEXT      | R:W EA |   |   |   |

| LDC<br>@ERs+,          | CCR      | R:W 2nd     | R:W<br>NEXT                         | 1 State of<br>internal<br>operation | R:W EA                              |                  |        |   |   |   |

| LDC<br>@ERs+,          | EXR      | R:W 2nd     | R:W<br>NEXT                         | 1 State of<br>internal<br>operation | R:W EA                              |                  |        |   |   |   |

| Instruction   | 1           | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

|---------------|-------------|---|---|---|---|---|---|---|---|

| SHAL.L #2,ERd | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHAR.B Rd     | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHAR.B #2,Rd  | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHAR.W Rd     | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHAR.W #2,Rd  | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHAR.L ERd    | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHAR.L #2,ERd | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHLL.B Rd     | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHLL.B #2,Rd  | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHLL.W Rd     | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHLL.W #2,Rd  | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHLL.L ERd    | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHLL.L #2,ERd | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHLR.B Rd     | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHLR.B #2,Rd  | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHLR.W Rd     | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHLR.W #2,Rd  | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHLR.L ERd    | R:W<br>NEXT |   |   |   |   |   |   |   |   |

| SHLR.L #2,ERd | R:W<br>NEXT |   |   |   |   |   |   |   |   |