Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 010                      |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | H8S/2000                                                                        |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 34MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI, SmartCard                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 96                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b; D/A 6x8b                                                            |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP                                                                        |

| Supplier Device Package    | 144-LQFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2378rvfq34wv |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 11.11 Example of Synchronous Operation                                  | 591 |

|--------------------------------------------------------------------------------|-----|

| Figure 11.12 Compare Match Buffer Operation                                    | 592 |

| Figure 11.13 Input Capture Buffer Operation                                    | 592 |

| Figure 11.14 Example of Buffer Operation Setting Procedure                     | 593 |

| Figure 11.15 Example of Buffer Operation (1)                                   | 594 |

| Figure 11.16 Example of Buffer Operation (2)                                   | 595 |

| Figure 11.17 Cascaded Operation Setting Procedure                              | 596 |

| Figure 11.18 Example of Cascaded Operation (1)                                 | 597 |

| Figure 11.19 Example of Cascaded Operation (2)                                 |     |

| Figure 11.20 Example of PWM Mode Setting Procedure                             |     |

| Figure 11.21 Example of PWM Mode Operation (1)                                 | 601 |

| Figure 11.22 Example of PWM Mode Operation (2)                                 | 601 |

| Figure 11.23 Example of PWM Mode Operation (3)                                 | 602 |

| Figure 11.24 Example of Phase Counting Mode Setting Procedure                  | 603 |

| Figure 11.25 Example of Phase Counting Mode 1 Operation                        | 604 |

| Figure 11.26 Example of Phase Counting Mode 2 Operation                        | 605 |

| Figure 11.27 Example of Phase Counting Mode 3 Operation                        | 606 |

| Figure 11.28 Example of Phase Counting Mode 4 Operation                        | 607 |

| Figure 11.29 Phase Counting Mode Application Example                           | 609 |

| Figure 11.30 Count Timing in Internal Clock Operation                          | 612 |

| Figure 11.31 Count Timing in External Clock Operation                          | 612 |

| Figure 11.32 Output Compare Output Timing                                      | 613 |

| Figure 11.33 Input Capture Input Signal Timing                                 | 613 |

| Figure 11.34 Counter Clear Timing (Compare Match)                              |     |

| Figure 11.35 Counter Clear Timing (Input Capture)                              | 614 |

| Figure 11.36 Buffer Operation Timing (Compare Match)                           | 615 |

| Figure 11.37 Buffer Operation Timing (Input Capture)                           | 615 |

| Figure 11.38 TGI Interrupt Timing (Compare Match)                              | 616 |

| Figure 11.39 TGI Interrupt Timing (Input Capture)                              | 616 |

| Figure 11.40 TCIV Interrupt Setting Timing                                     | 617 |

| Figure 11.41 TCIU Interrupt Setting Timing                                     | 617 |

| Figure 11.42 Timing for Status Flag Clearing by CPU                            | 618 |

| Figure 11.43 Timing for Status Flag Clearing by DTC/DMAC Activation            | 618 |

| Figure 11.44 Phase Difference, Overlap, and Pulse Width in Phase Counting Mode | 619 |

| Figure 11.45 Contention between TCNT Write and Clear Operations                | 620 |

| Figure 11.46 Contention between TCNT Write and Increment Operations            | 621 |

| Figure 11.47 Contention between TGR Write and Compare Match                    | 622 |

| Figure 11.48 Contention between Buffer Register Write and Compare Match        | 623 |

| Figure 11.49 Contention between TGR Read and Input Capture                     | 624 |

| Figure 11.50 Contention between TGR Write and Input Capture                    | 625 |

| Figure 11.51 Contention between Buffer Register Write and Input Capture        | 626 |

#### 2.5.2 Memory Data Formats

Figure 2.10 shows the data formats in memory. The H8S/2000 CPU can access word data and longword data in memory, but word or longword data must begin at an even address. If an attempt is made to access word or longword data at an odd address, no address error occurs but the least significant bit of the address is regarded as 0, so the access starts at the preceding address. This also applies to instruction fetches.

When SP (ER7) is used as an address register to access the stack, the operand size should be word size or longword size.

| Data  | а Туре | Address                                                    | Data Format |   |   |   |          |   |   |     |

|-------|--------|------------------------------------------------------------|-------------|---|---|---|----------|---|---|-----|

|       |        | [                                                          | 7           |   |   |   | <u> </u> | _ |   | 0   |

| 1-bit | data   | Address L                                                  | 7           | 6 | 5 | 4 | 3        | 2 | 1 | 0   |

| Byte  | data   | Address L                                                  | MSB         |   |   |   |          | 1 |   | LSB |

| Word  |        | Address 2M<br>Address 2M+1                                 | MSB         |   |   |   |          |   |   | LSB |

| Long  |        | Address 2N<br>Address 2N+1<br>Address 2N+2<br>Address 2N+3 | MSB         |   |   |   |          |   |   | LSB |

|       |        |                                                            | _           |   |   | _ | _        | _ |   |     |

Figure 2.10 Memory Data Formats

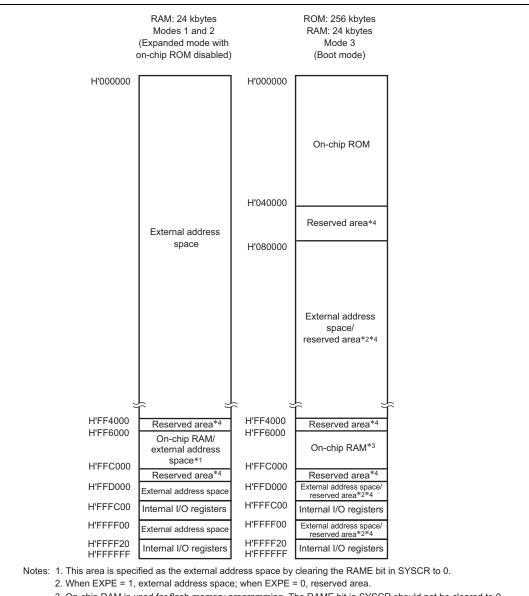

- 3. On-chip RAM is used for flash memory programming. The RAME bit in SYSCR should not be cleared to 0.

- 4. A reserved area should not be accessed.

Figure 3.12 Memory Map for H8S/2371 and H8S/2371R (1)

| Bit    | Bit Name           | Initial Value | R/W        | Description                                                                    |

|--------|--------------------|---------------|------------|--------------------------------------------------------------------------------|

| 9<br>8 | IRQ4SCB<br>IRQ4SCA | 0<br>0        | R/W<br>R/W | IRQ4 Sense Control B<br>IRQ4 Sense Control A                                   |

|        |                    |               |            | 00: Interrupt request generated at IRQ4 input low level                        |

|        |                    |               |            | 01: Interrupt request generated at falling edge of IRQ4 input                  |

|        |                    |               |            | 10: Interrupt request generated at rising edge of IRQ4 input                   |

|        |                    |               |            | 11: Interrupt request generated at both falling and rising edges of IRQ4 input |

| 7<br>6 | IRQ3SCB<br>IRQ3SCA | 0<br>0        | R/W<br>R/W | IRQ3 Sense Control B<br>IRQ3 Sense Control A                                   |

|        |                    |               |            | 00: Interrupt request generated at IRQ3 input low level                        |

|        |                    |               |            | 01: Interrupt request generated at falling edge of IRQ3 input                  |

|        |                    |               |            | 10: Interrupt request generated at rising edge of IRQ3 input                   |

|        |                    |               |            | 11: Interrupt request generated at both falling and rising edges of IRQ3 input |

| 5<br>4 | IRQ2SCB<br>IRQ2SCA | 0<br>0        | R/W<br>R/W | IRQ2 Sense Control B<br>IRQ2 Sense Control A                                   |

|        |                    |               |            | 00: Interrupt request generated at IRQ2 input low level                        |

|        |                    |               |            | 01: Interrupt request generated at falling edge of IRQ2 input                  |

|        |                    |               |            | 10: Interrupt request generated at rising edge of IRQ2 input                   |

|        |                    |               |            | 11: Interrupt request generated at both falling and rising edges of IRQ2 input |

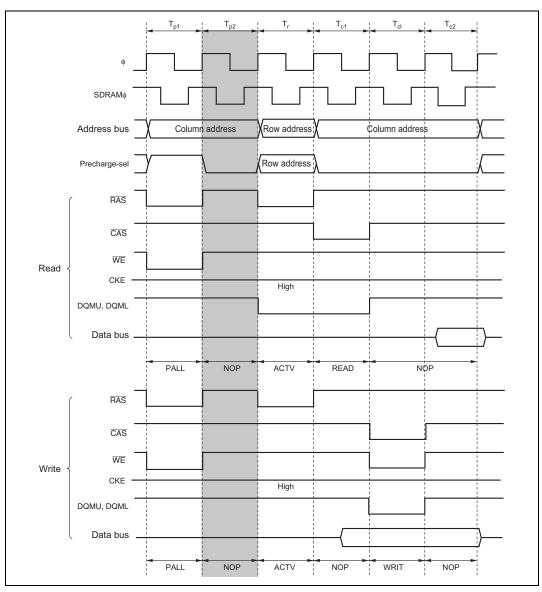

The setting of bits TPC1 and TPC0 is also valid for T<sub>p</sub> states in refresh cycles.

Figure 6.47 Example of Timing with Two-State Precharge Cycle (TPC1 = 0, TPC0 = 1, SDWCD = 0, CAS Latency 2)

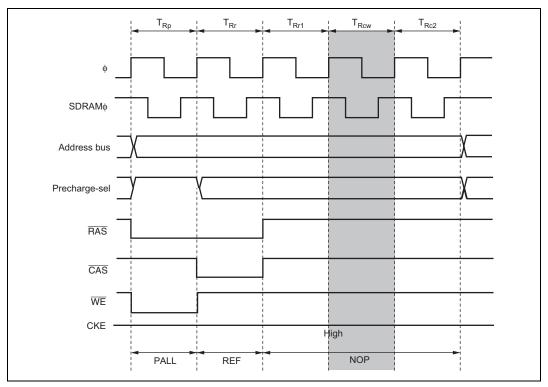

Figure 6.56 Auto Refresh Timing (TPC = 0, TPC0 = 0, RLW1 = 0, RLW0 = 1)

**Self-Refreshing:** A self-refresh mode (battery backup mode) is provided for synchronous DRAM as a kind of standby mode. In this mode, refresh timing and refresh addresses are generated within the synchronous DRAM.

To select self-refreshing, set the RFSHE bit to 1 in REFCR. When a SLEEP instruction is executed to enter software standby mode, the SELF command is issued, as shown in figure 6.57.

When software standby mode is exited, the SLFRF bit in REFCR is cleared to 0 and self-refresh mode is exited automatically. If an auto refresh request occurs when making a transition to software standby mode, auto refreshing is executed, then self-refresh mode is entered.

When using self-refresh mode, the OPE bit must not be cleared to 0 in SBYCR.

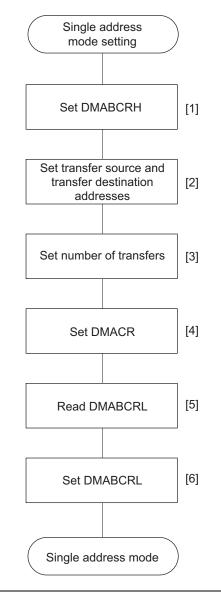

- [1] Set each bit in DMABCRH.

- Clear the FAE bit to 0 to select short address mode.

- Set the SAE bit to 1 to select single address mode.

- Specify enabling or disabling of internal interrupt clearing with the DTA bit.

- [2] Set the transfer source address/transfer destination address in MAR.

- [3] Set the number of transfers in ETCR.

- [4] Set each bit in DMACR.

- Set the transfer data size with the DTSZ bit.

- Specify whether MAR is to be incremented or decremented with the DTID bit.

- Clear the RPE bit to 0 to select sequential mode.

- Specify the transfer direction with the DTDIR bit.

- Select the activation source with bits DTF3 to DTF0.

- [5] Read the DTE bit in DMABCRL as 0.

- [6] Set each bit in DMABCRL.

- Specify enabling or disabling of transfer end interrupts with the DTIE bit.

- Set the DTE bit to 1 to enable transfer.

Figure 7.10 Example of Single Address Mode Setting Procedure (When Sequential Mode Is Specified)

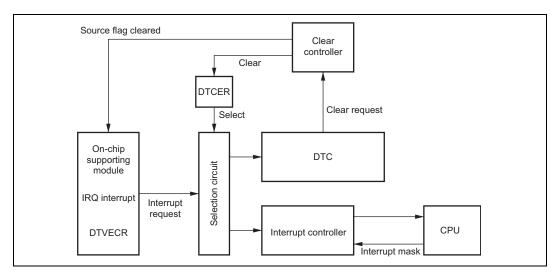

Figure 9.2 Block Diagram of DTC Activation Source Control

### 9.4 Location of Register Information and DTC Vector Table

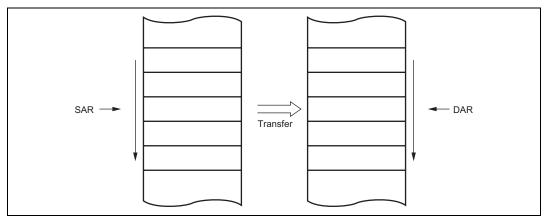

Locate the register information in the on-chip RAM (addresses: H'FFBC00 to H'FFBFFF). Register information should be located at the address that is multiple of four within the range. Locating the register information in address space is shown in figure 9.3. Locate the MRA, SAR, MRB, DAR, CRA, and CRB registers, in that order, from the start address of the register information. In the case of chain transfer, register information should be located in consecutive areas as shown in figure 9.3 and the register information start address should be located at the corresponding vector address to the activation source. Figure 9.4 shows correspondences between the DTC vector address and register information. The DTC reads the start address of the register information from the vector address set for each activation source, and then reads the register information from that start address.

When the DTC is activated by software, the vector address is obtained from:  $H'0400 + (DTVECR[6:0] \times 2)$ . For example, if DTVECR is H'10, the vector address is H'0420.

The configuration of the vector address is the same in both normal<sup>\*</sup> and advanced modes, a 2-byte unit being used in both cases. These two bytes specify the lower bits of the register information start address.

Note: \* Not available in this LSI.

#### 9.5.1 Normal Mode

In normal mode, one operation transfers one byte or one word of data. Table 9.4 lists the register function in normal mode. From 1 to 65,536 transfers can be specified. Once the specified number of transfers has ended, a CPU interrupt can be requested.

#### Table 9.4 Register Function in Normal Mode

| Name                             | Abbreviation | Function                       |

|----------------------------------|--------------|--------------------------------|

| DTC source address register      | SAR          | Designates source address      |

| DTC destination address register | DAR          | Designates destination address |

| DTC transfer count register A    | CRA          | Designates transfer count      |

| DTC transfer count register B    | CRB          | Not used                       |

Figure 9.6 Memory Mapping in Normal Mode

### 10.8 Port 9

Port 9 is an 8-bit input-only port. Port 4 has the following register.

• Port 9 register (PORT4)

#### 10.8.1 Port 9 Register (PORT9)

PORT9 is an 8-bit read-only register that shows port 4 pin states.

PORT9 cannot be modified.

| Bit | Bit Name | Initial Value | R/W | Description                                          |

|-----|----------|---------------|-----|------------------------------------------------------|

| 7   | P97      | *             | R   | The pin states are always read when a port 9 read is |

| 6   | P96      | *             | R   | performed.                                           |

| 5   | P95      | *             | R   | —                                                    |

| 4   | P99      | *             | R   |                                                      |

| 3   | P93      | *             | R   | —                                                    |

| 2   | P92      | *             | R   |                                                      |

| 1   | P91      | *             | R   |                                                      |

| 0   | P90      | *             | R   |                                                      |

Note: \* Determined by the states of pins P97 to P90.

### 13.8 Usage Notes

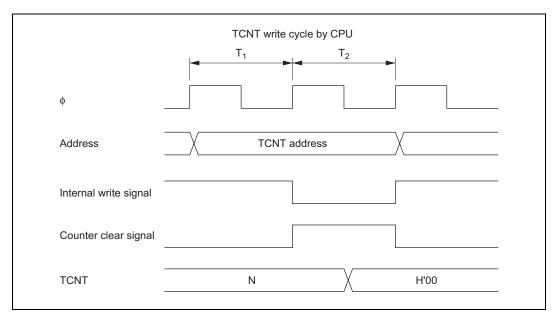

#### 13.8.1 Contention between TCNT Write and Clear

If a timer counter clock pulse is generated during the  $T_2$  state of a TCNT write cycle, the clear takes priority, so that the counter is cleared and the write is not performed.

Figure 13.10 shows this operation.

Figure 13.10 Contention between TCNT Write and Clear

### 15.5 Multiprocessor Communication Function

Use of the multiprocessor communication function enables data transfer to be performed among a number of processors sharing communication lines by means of asynchronous serial communication using the multiprocessor format, in which a multiprocessor bit is added to the transfer data. When multiprocessor communication is carried out, each receiving station is addressed by a unique ID code. The serial communication cycle consists of two component cycles: an ID transmission cycle which specifies the receiving station, and a data transmission cycle to the specified receiving station. The multiprocessor bit is used to differentiate between the ID transmission cycle and the data transmission cycle. If the multiprocessor bit is 1, the cycle is an ID transmission cycle, and if the multiprocessor bit is 0, the cycle is a data transmission cycle. Figure 15.10 shows an example of inter-processor communication using the multiprocessor format. The transmitting station first sends communication data with a 1 multiprocessor bit added to the ID code of the receiving station. It then sends transmit data as data with a 0 multiprocessor bit added. When data with a 1 multiprocessor bit is received, the receiving station compares that data with its own ID. The station whose ID matches then receives the data sent next. Stations whose ID does not match continue to skip data until data with a 1 multiprocessor bit is again received.

The SCI uses the MPIE bit in SCR to implement this function. When the MPIE bit is set to 1, transfer of receive data from RSR to RDR, error flag detection, and setting the SSR status flags, RDRF, FER, and ORER to 1 are inhibited until data with a 1 multiprocessor bit is received. On reception of receive character with a 1 multiprocessor bit, the MPBR bit in SSR is set to 1 and the MPIE bit is automatically cleared, thus normal reception is resumed. If the RIE bit in SCR is set to 1 at this time, an RXI interrupt is generated.

When the multiprocessor format is selected, the parity bit setting is invalid. All other bit settings are the same as those in normal asynchronous mode. The clock used for multiprocessor communication is the same as that in normal asynchronous mode.

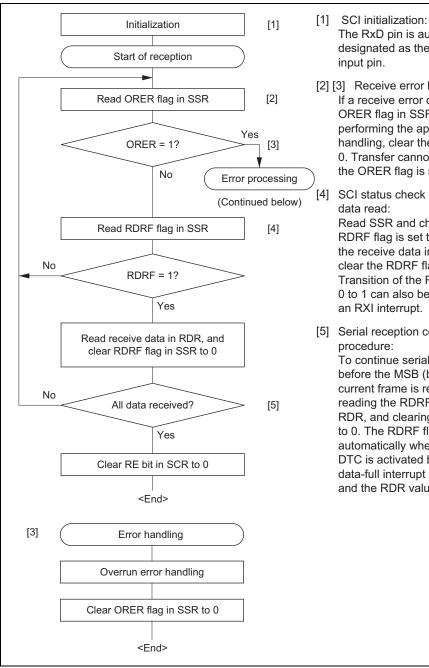

The RxD pin is automatically designated as the receive data

- [2] [3] Receive error handling: If a receive error occurs, read the ORER flag in SSR, and after performing the appropriate error handling, clear the ORER flag to 0. Transfer cannot be resumed if the ORER flag is set to 1.

- [4] SCI status check and receive Read SSR and check that the RDRF flag is set to 1, then read the receive data in RDR and clear the RDRF flag to 0. Transition of the RDRF flag from 0 to 1 can also be identified by an RXI interrupt.

- [5] Serial reception continuation

To continue serial reception, before the MSB (bit 7) of the current frame is received, finish reading the RDRF flag, reading RDR, and clearing the RDRF flag to 0. The RDRF flag is cleared automatically when the DMAC or DTC is activated by a receivedata-full interrupt (RXI) request and the RDR value is read.

#### Figure 15.19 Sample Serial Reception Flowchart

#### 15.7.6 Data Transmission (Except for Block Transfer Mode)

As data transmission in Smart Card interface mode involves error signal sampling and retransmission processing, the operations are different from those in normal serial communication interface mode (except for block transfer mode). Figure 15.26 illustrates the retransfer operation when the SCI is in transmit mode.

- 1. If an error signal is sampled from the receiving end after transmission of one frame is completed, the ERS bit in SSR is set to 1. If the RIE bit in SCR is set at this time, an ERI interrupt request is generated. The ERS bit in SSR should be cleared to 0 before the next parity bit is sampled.

- 2. The TEND bit in SSR is not set for a frame for which an error signal is received. Data is retransferred from TDR to TSR, and retransmitted automatically.

- 3. If an error signal is not sent back from the receiving end, the ERS bit in SSR is not set.

- 4. Transmission of one frame, including a retransfer, is judged to have been completed, and the TEND bit in SSR is set to 1. If the TIE bit in SCR is set at this time, a TXI interrupt request is generated. Writing transmit data to TDR transfers the next transmit data.

Figure 15.28 shows a flowchart for transmission. The sequence of transmit operations can be performed automatically by specifying the DTC or DMAC to be activated with a TXI interrupt source. In a transmit operation, the TDRE flag is also set to 1 at the same time as the TEND flag in SSR, and a TXI interrupt will be generated if the TIE bit in SCR has been set to 1. If the TXI request is designated beforehand as a DTC or DMAC activation source, the DTC or DMAC will be activated by the TXI request, and transfer of the transmit data will be carried out. The TDRE and TEND flags are automatically cleared to 0 when data transfer is performed by the DTC or DMAC. In the event of an error, the SCI retransmits the same data automatically. During this period, the TEND flag remains cleared to 0 and the DTC or DMAC is not activated. Therefore, the SCI and DTC or DMAC will automatically transmit the specified number of bytes in the event of an error, including retransmission. However, the ERS flag is not cleared automatically when an error occurs, and so the RIE bit should be set to 1 beforehand so that an ERI request will be generated in the event of an error, and the ERS flag will be cleared.

When performing transfer using the DTC or DMAC, it is essential to set and enable the DTC or DMAC before carrying out SCI setting. For details on the DTC or DMAC setting procedures, refer to section 9, Data Transfer Controller (DTC) or section 7, DMA Controller (DMAC).

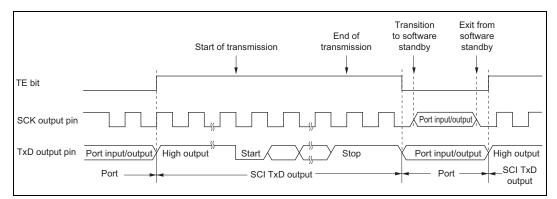

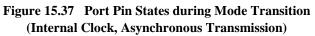

#### Figure 15.38 Port Pin States during Mode Transition (Internal Clock, Synchronous Transmission)

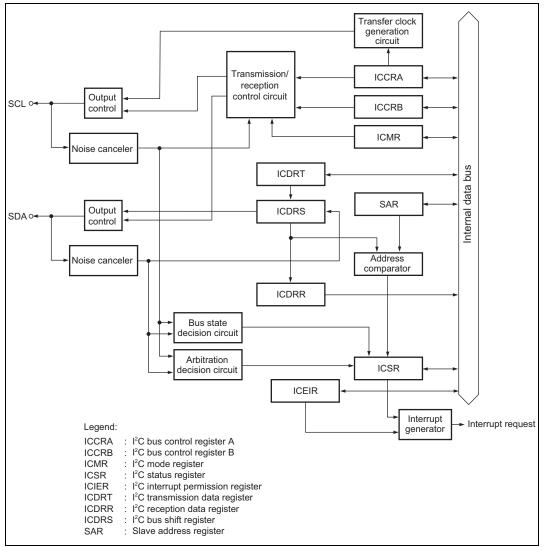

Figure 16.1 Block Diagram of I<sup>2</sup>C Bus Interface 2

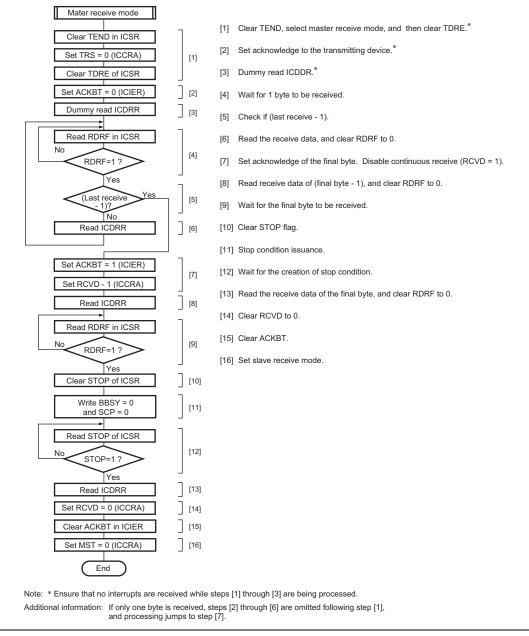

Figure 16.15 Sample Flowchart for Master Receive Mode

Rev.7.00 Mar. 18, 2009 page 798 of 1136 REJ09B0109-0700

# Section 24 Power-Down Modes

In addition to the normal program execution state, this LSI has power-down modes in which operation of the CPU and oscillator is halted and power dissipation is reduced. Low-power operation can be achieved by individually controlling the CPU, on-chip peripheral modules, and so on.

This LSI's operating modes are high-speed mode and six power down modes:

- Clock division mode

- Sleep mode

- Module stop mode

- All module clock stop mode

- Software standby mode

- Hardware standby mode

Sleep mode is a CPU state, clock division mode is an on-chip peripheral function (including bus masters and the CPU) state, and module stop mode is an on-chip peripheral function (including bus masters other than the CPU) state. A combination of these modes can be set.

After a reset, this LSI is in high-speed mode.

Table 24.1 shows the internal states of this LSI in each mode. Figure 24.1 shows the mode transition diagram.

### 24.1 Register Descriptions

The registers relating to the power-down mode are shown below. For details on the system clock control register (SCKCR), refer to section 23.1.1, System Clock Control Register (SCKCR).

- System clock control register (SCKCR)

- Standby control register (SBYCR)

- Module stop control register H (MSTPCRH)

- Module stop control register L (MSTPCRL)

- Extension module stop control register H (EXMSTPCRH)

- Extension module stop control register L (EXMSTPCRL)

#### 24.1.1 Standby Control Register (SBYCR)

SBYCR performs software standby mode control.

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                          |  |  |

|-----|----------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7   | SSBY     | 0             | R/W | Software Standby                                                                                                                                                                                     |  |  |

|     |          |               |     | This bit specifies the transition mode after<br>executing the SLEEP instruction                                                                                                                      |  |  |

|     |          |               |     | 0: Shifts to sleep mode after the SLEEP instruction<br>is executed                                                                                                                                   |  |  |

|     |          |               |     | 1: Shifts to software standby mode after the SLEEP<br>instruction is executed                                                                                                                        |  |  |

|     |          |               |     | This bit does not change when clearing the software standby mode by using external interrupts and shifting to normal operation. This bit should be written 0 when clearing.                          |  |  |

| 6   | OPE      | 1             | R/W | Output Port Enable                                                                                                                                                                                   |  |  |

|     |          |               |     | Specifies whether the output of the address bus<br>and bus control signals (CS0 to CS7, AS, RD,<br>HWR, LWR, UCAS, LCAS) is retained or set to the<br>high-impedance state in software standby mode. |  |  |

|     |          |               |     | 0: In software standby mode, address bus and bus<br>control signals are high-impedance                                                                                                               |  |  |

|     |          |               |     | 1: In software standby mode, address bus and bus<br>control signals retain output state                                                                                                              |  |  |

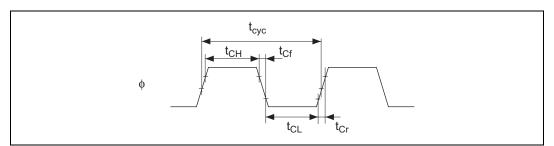

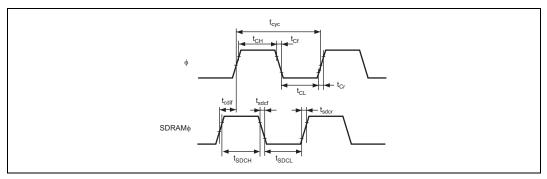

### 26.4 Timing Charts

### 26.4.1 Clock Timing

The clock timings are shown below.

Figure 26.3 SDRAM¢ Timing