Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                 |

|----------------------------|----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                     |

| Speed                      | 80MHz                                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                             |

| Number of I/O              | 52                                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 64K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                  |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 64-LQFP                                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l443rct6                  |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   | 1                  | 2    | 3   | 4                       | 5               | 6   | 7   | 8    | 9    | 10   | 11     | 12   |        |

|---|--------------------|------|-----|-------------------------|-----------------|-----|-----|------|------|------|--------|------|--------|

| А | PE3                | PE1  | PB8 | PH3/BOOT0               | PD7             | PD5 | PB4 | PB3  | PA15 | PA14 | PA13   | PA12 |        |

| в | PE4                | PE2  | PB9 | PB7 PB6 PD6 PD4 PD3 PD1 |                 |     |     |      |      | PC12 | PC10   | PA11 |        |

| с | PC13               | PE5  | PE0 | VDD                     | VDD PB5 PD2 PD0 |     |     |      |      |      | VDDUSB | PA10 |        |

| D | PC14-<br>OSC32_IN  | PE6  | VSS |                         |                 |     |     |      |      | PA9  | PA8    | PC9  |        |

| E | PC15-<br>OSC32_OUT | VBAT | vss |                         |                 | PC8 | PC7 | PC6  |      |      |        |      |        |

| F | PH0-OSC_IN         | VSS  |     | -                       | UFBGA100        |     |     |      |      |      |        |      |        |

| G | PH1-<br>OSC_OUT    | VDD  |     | _                       |                 |     |     | )    |      |      | VDD    | VDD  |        |

| н | PC0                | NRST | VDD |                         |                 |     |     |      |      | PD15 | PD14   | PD13 |        |

| J | VSSA               | PC1  | PC2 |                         |                 |     |     |      |      | PD12 | PD11   | PD10 |        |

| к | VREF-              | PC3  | PA2 | PA5                     | PC4             |     |     | PD9  | PD8  | PB15 | PB14   | PB13 |        |

| L | VREF+              | PA0  | PA3 | PA6                     | PC5             | PB2 | PE8 | PE10 | PE12 | PB10 | PB11   | PB12 |        |

| м | VDDA               | PA1  | PA4 | PA7                     | PB0             | PB1 | PE7 | PE9  | PE11 | PE13 | PE14   | PE15 |        |

|   |                    |      |     |                         |                 |     |     |      |      |      |        | MSv3 | 36894V |

Figure 6. STM32L443Vx UFBGA100 ballout<sup>(1)</sup>

1. The above figure shows the package top view.

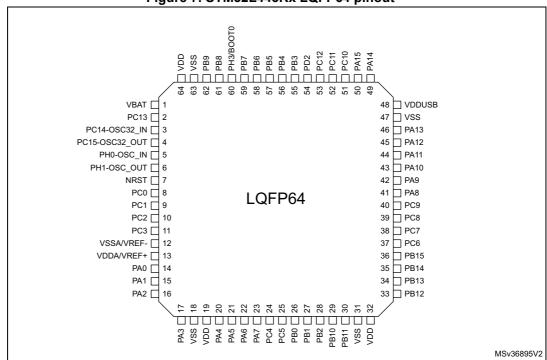

Figure 7. STM32L443Rx LQFP64 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

|        |                 |         | Pin N   | lum    | ber     | Tub     |          |                                       |          | pinac         |       | tions (continued)<br>Pin functio                                                                                                                                      | ns                      |

|--------|-----------------|---------|---------|--------|---------|---------|----------|---------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP48 | <b>UFQFPN48</b> | WLCSP49 | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                                   | Additional<br>functions |

| 25     | 25              | F1      | G3      | 33     | H8      | 51      | L12      | PB12                                  | I/O      | FT_I          | _     | TIM1_BKIN,<br>TIM1_BKIN_COMP2,<br>I2C2_SMBA, SPI2_NSS,<br>USART3_CK,<br>LPUART1_RTS_DE,<br>TSC_G1_I01,<br>LCD_SEG12,<br>SWPMI1_IO, SAI1_FS_A,<br>TIM15_BKIN, EVENTOUT | -                       |

| 26     | 26              | E2      | G2      | 34     | G8      | 52      | K12      | PB13                                  | I/O      | FT_fl         | -     | TIM1_CH1N, I2C2_SCL,<br>SPI2_SCK,<br>USART3_CTS,<br>LPUART1_CTS,<br>TSC_G1_IO2,<br>LCD_SEG13,<br>SWPMI1_TX,<br>SAI1_SCK_A,<br>TIM15_CH1N,<br>EVENTOUT                 | -                       |

| 27     | 27              | E1      | G1      | 35     | F8      | 53      | K11      | PB14                                  | I/O      | FT_fl         | -     | TIM1_CH2N, I2C2_SDA,<br>SPI2_MISO,<br>USART3_RTS_DE,<br>TSC_G1_IO3,<br>LCD_SEG14,<br>SWPMI1_RX,<br>SAI1_MCLK_A,<br>TIM15_CH1, EVENTOUT                                | -                       |

| 28     | 28              | D3      | F2      | 36     | F7      | 54      | K10      | PB15                                  | I/O      | FT_I          | -     | RTC_REFIN, TIM1_CH3N,<br>SPI2_MOSI,<br>TSC_G1_IO4,<br>LCD_SEG15,<br>SWPMI1_SUSPEND,<br>SAI1_SD_A, TIM15_CH2,<br>EVENTOUT                                              | -                       |

| -      | -               | -       | -       | -      | -       | 55      | K9       | PD8                                   | I/O      | FT_I          | -     | USART3_TX,<br>LCD_SEG28, EVENTOUT                                                                                                                                     | -                       |

| -      | -               | -       | -       | -      | -       | 56      | K8       | PD9                                   | I/O      | FT_I          | -     | USART3_RX,<br>LCD_SEG29, EVENTOUT                                                                                                                                     | -                       |

| -      | -               | -       | -       | -      | -       | 57      | J12      | PD10                                  | I/O      | FT_I          | -     | USART3_CK,<br>TSC_G6_IO1,<br>LCD_SEG30, EVENTOUT                                                                                                                      | -                       |

Table 13. STM32L443xx pin definitions (continued)

|        | Table 14. Alternate function AF0 to AF7 (for AF8 to AF15 see Table 15) (continued) |        |                      |           |        |                |           |      |                              |  |  |  |  |  |

|--------|------------------------------------------------------------------------------------|--------|----------------------|-----------|--------|----------------|-----------|------|------------------------------|--|--|--|--|--|

|        |                                                                                    | AF0    | AF1                  | AF2       | AF3    | AF4            | AF5       | AF6  | AF7                          |  |  |  |  |  |

| Po     | ort                                                                                | SYS_AF | TIM1/TIM2/<br>LPTIM1 | TIM1/TIM2 | USART2 | 12C1/12C2/12C3 | SPI1/SPI2 | SPI3 | USART1/<br>USART2/<br>USART3 |  |  |  |  |  |

|        | PD0                                                                                | -      | -                    | -         | -      | -              | SPI2_NSS  | -    | -                            |  |  |  |  |  |

|        | PD1                                                                                | -      | -                    | -         | -      | -              | SPI2_SCK  | -    | -                            |  |  |  |  |  |

|        | PD2                                                                                | -      | -                    | -         | -      | -              | -         | -    | USART3_RTS_<br>DE            |  |  |  |  |  |

|        | PD3                                                                                | -      | -                    | -         | -      | -              | SPI2_MISO | -    | USART2_CTS                   |  |  |  |  |  |

|        | PD4                                                                                | -      | -                    | -         | -      | -              | SPI2_MOSI | -    | USART2_RTS_<br>DE            |  |  |  |  |  |

|        | PD5                                                                                | -      | -                    | -         | -      | -              | -         | -    | USART2_TX                    |  |  |  |  |  |

|        | PD6                                                                                | -      | -                    | -         | -      | -              | -         | -    | USART2_RX                    |  |  |  |  |  |

| Port D | PD7                                                                                | -      | -                    | -         | -      | -              | -         | -    | USART2_CK                    |  |  |  |  |  |

|        | PD8                                                                                | -      | -                    | -         | -      | -              | -         | -    | USART3_TX                    |  |  |  |  |  |

|        | PD9                                                                                | -      | -                    | -         | -      | -              | -         | -    | USART3_RX                    |  |  |  |  |  |

|        | PD10                                                                               | -      | -                    | -         | -      | -              | -         | -    | USART3_CK                    |  |  |  |  |  |

|        | PD11                                                                               | -      | -                    | -         | -      | -              | -         | -    | USART3_CTS                   |  |  |  |  |  |

|        | PD12                                                                               | -      | -                    | -         | -      | -              | -         | -    | USART3_RTS_<br>DE            |  |  |  |  |  |

|        | PD13                                                                               | -      | -                    | -         | -      | -              | -         | -    | -                            |  |  |  |  |  |

|        | PD14                                                                               | -      | -                    | -         | -      | -              | -         | -    | -                            |  |  |  |  |  |

|        | PD15                                                                               | -      | -                    | -         | -      | -              | -         | -    | -                            |  |  |  |  |  |

| Port E | PE0                                                                                | -      | -                    | -         | -      | -              | -         | -    | -                            |  |  |  |  |  |

DocID028739 Rev 2

577

69/207

STM32L443CC STM32L443RC STM32L443VC

|        |      | AF0     | AF1                  | AF2        | AF3                  | AF4            | AF5       | AF6  | AF7                          |

|--------|------|---------|----------------------|------------|----------------------|----------------|-----------|------|------------------------------|

| Po     | ort  | SYS_AF  | TIM1/TIM2/<br>LPTIM1 | TIM1/TIM2  | USART2               | 12C1/12C2/12C3 | SPI1/SPI2 | SPI3 | USART1/<br>USART2/<br>USART3 |

|        | PE1  | -       | -                    | -          | -                    | -              | -         | -    | -                            |

|        | PE2  | TRACECK | -                    | -          | -                    | -              | -         | -    | -                            |

|        | PE3  | TRACED0 | -                    | -          | -                    | -              | -         | -    | -                            |

|        | PE4  | TRACED1 | -                    | -          | -                    | -              | -         | -    | -                            |

|        | PE5  | TRACED2 | -                    | -          | -                    | -              | -         | -    | -                            |

|        | PE6  | TRACED3 | -                    | -          | -                    | -              | -         | -    | -                            |

|        | PE7  | -       | TIM1_ETR             | -          | -                    | -              | -         | -    | -                            |

|        | PE8  | -       | TIM1_CH1N            | -          | -                    | -              | -         | -    | -                            |

| Port E | PE9  | -       | TIM1_CH1             | -          | -                    | -              | -         | -    | -                            |

|        | PE10 | -       | TIM1_CH2N            | -          | -                    | -              | -         | -    | -                            |

|        | PE11 | -       | TIM1_CH2             | -          | -                    | -              | -         | -    | -                            |

|        | PE12 | -       | TIM1_CH3N            | -          | -                    | -              | SPI1_NSS  | -    | -                            |

|        | PE13 | -       | TIM1_CH3             | -          | -                    | -              | SPI1_SCK  | -    | -                            |

|        | PE14 | -       | TIM1_CH4             | TIM1_BKIN2 | TIM1_BKIN2_<br>COMP2 | -              | SPI1_MISO | -    | -                            |

|        | PE15 | -       | TIM1_BKIN            | -          | TIM1_BKIN_<br>COMP1  | -              | SPI1_MOSI | -    | -                            |

|        | PH0  | -       | -                    | -          | -                    | -              | -         | -    | -                            |

| Port H | PH1  | -       | -                    | -          | -                    | -              | -         | -    | -                            |

|        | PH3  | _       | -                    | -          | _                    | _              | -         | -    | _                            |

# Pinouts and pin description

STM32L443CC STM32L443RC STM32L443VC

DocID028739 Rev 2

5

70/207

| Symbol         | Parameter                   | Conditions                           | Min                                                                                                                                                                                                                                                     | Мах | Unit |

|----------------|-----------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|

|                | Ambient temperature for the | Maximum power dissipation            | -40                                                                                                                                                                                                                                                     | 85  |      |

|                | suffix 6 version            | Low-power dissipation <sup>(5)</sup> | -40                                                                                                                                                                                                                                                     | 105 |      |

| Та             | Ambient temperature for the | Maximum power dissipation            | -40                                                                                                                                                                                                                                                     | 105 | °C   |

| IA             | suffix 7 version            | Low-power dissipation <sup>(5)</sup> | -40                                                                                                                                                                                                                                                     | 125 |      |

|                | Ambient temperature for the | Maximum power dissipation            | -40                                                                                                                                                                                                                                                     | 125 |      |

|                | suffix 3 version            | Low-power dissipation <sup>(5)</sup> | -40                                                                                                                                                                                                                                                     | 130 |      |

|                |                             | Suffix 6 version                     | -40                                                                                                                                                                                                                                                     | 105 |      |

| Τ <sub>J</sub> | Junction temperature range  | Suffix 7 version                     | -40                                                                                                                                                                                                                                                     | 125 | °C   |

|                |                             | Suffix 3 version                     | ower dissipation $-40$ 85dissipation <sup>(5)</sup> $-40$ 105ower dissipation $-40$ 105dissipation <sup>(5)</sup> $-40$ 125ower dissipation $-40$ 125ower dissipation <sup>(5)</sup> $-40$ 130dissipation <sup>(5)</sup> $-40$ 105dissipation $-40$ 125 | 130 |      |

1. When RESET is released functionality is guaranteed down to  $V_{BOR0}\,\text{Min}.$

2. This formula has to be applied only on the power supplies related to the IO structure described by the pin definition table. Maximum I/O input voltage is the smallest value between MIN( $V_{DD}$ ,  $V_{DDA}$ ,  $V_{DDUSB}$ ,  $V_{LCD}$ )+3.6 V and 5.5V.

3. For operation with voltage higher than Min (V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDUSB</sub>, V<sub>LCD</sub>) +0.3 V, the internal Pull-up and Pull-Down resistors must be disabled.

4. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$  (see Section 7.9: Thermal characteristics).

In low-power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.9: Thermal characteristics).

### 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 21* are derived from tests performed under the ambient temperature condition summarized in *Table 20*.

| Symbol              | Parameter                         | Conditions | Min | Мах | Unit |

|---------------------|-----------------------------------|------------|-----|-----|------|

| t <sub>VDD</sub>    | V <sub>DD</sub> rise time rate    |            | 0   | 8   |      |

|                     | V <sub>DD</sub> fall time rate    | -          | 10  | ∞   | μs/V |

| +                   | V <sub>DDA</sub> rise time rate   |            | 0   | ∞   |      |

| t <sub>VDDA</sub>   | V <sub>DDA</sub> fall time rate   | -          | 10  | 8   |      |

| +                   | V <sub>DDUSB</sub> rise time rate |            | 0   | ∞   |      |

| <sup>t</sup> VDDUSB | V <sub>DDUSB</sub> fall time rate | -          | 10  | ∞   |      |

Table 21. Operating conditions at power-up / power-down

#### 6.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 22* are derived from tests performed under the ambient temperature conditions summarized in *Table 20: General operating conditions*.

| Symbol                                | Parameter                                         | Conditions <sup>(1)</sup> | Min  | Тур  | Max  | Unit |  |

|---------------------------------------|---------------------------------------------------|---------------------------|------|------|------|------|--|

| V                                     | V <sub>DDA</sub> peripheral voltage               | Rising edge               | 1.61 | 1.65 | 1.69 | V    |  |

| V <sub>PVM3</sub>                     | monitoring                                        | Falling edge              | 1.6  | 1.64 | 1.68 | v    |  |

| V <sub>PVM4</sub>                     | V <sub>DDA</sub> peripheral voltage               | Rising edge               | 1.78 | 1.82 | 1.86 | V    |  |

|                                       | monitoring                                        | Falling edge              | 1.77 | 1.81 | 1.85 | v    |  |

| V <sub>hyst_PVM3</sub>                | PVM3 hysteresis                                   | -                         | -    | 10   | -    | mV   |  |

| V <sub>hyst_PVM4</sub>                | PVM4 hysteresis                                   | -                         | -    | 10   | -    | mV   |  |

| I <sub>DD</sub> (PVM1)<br>(2)         | PVM1 consumption from $V_{DD}$                    | -                         | -    | 0.2  | -    | μA   |  |

| I <sub>DD</sub><br>(PVM3/PVM4)<br>(2) | PVM3 and PVM4<br>consumption from V <sub>DD</sub> | -                         | -    | 2    | -    | μA   |  |

Table 22. Embedded reset and power control block characteristics (continued)

1. Continuous mode means Run/Sleep modes, or temperature sensor enable in Low-power run/Low-power sleep modes.

2. Guaranteed by design.

3. BOR0 is enabled in all modes (except shutdown) and its consumption is therefore included in the supply current characteristics tables.

|                         |                                  |                                                                                         | Conditio                           | ns                          | ТҮР   |      | ТҮР   |        |  |  |  |  |

|-------------------------|----------------------------------|-----------------------------------------------------------------------------------------|------------------------------------|-----------------------------|-------|------|-------|--------|--|--|--|--|

| Symbol                  | Parameter                        | -                                                                                       | Voltage<br>scaling                 | Code                        | 25 °C | Unit | 25 °C | Unit   |  |  |  |  |

|                         |                                  |                                                                                         | Hz                                 | Reduced code <sup>(1)</sup> | 2.66  |      | 102   |        |  |  |  |  |

|                         |                                  |                                                                                         | Range 2<br><sub>LK</sub> = 26 MHz  | Coremark                    | 2.44  |      | 94    |        |  |  |  |  |

| I <sub>DD</sub> (Run)   |                                  | f <sub>HCLK</sub> = f <sub>HSE</sub> up to                                              | inge<br>= 2(                       | Dhrystone 2.1               | 2.46  | mA   | 95    | µA/MHz |  |  |  |  |

|                         | Supply<br>current in<br>Run mode | 48 MHz included,<br>bypass mode<br>PLL ON above<br>48 MHz<br>all peripherals<br>disable | Ra                                 | Fibonacci                   | 2.27  |      | 87    |        |  |  |  |  |

|                         |                                  |                                                                                         |                                    | While(1)                    | 2.20  |      | 84.6  |        |  |  |  |  |

|                         |                                  |                                                                                         | Range 1<br><sub>:LK</sub> = 80 MHz | Reduced code <sup>(1)</sup> | 8.56  | mA   | 107   | µA/MHz |  |  |  |  |

|                         |                                  |                                                                                         |                                    | Coremark                    | 8.00  |      | 100   |        |  |  |  |  |

|                         |                                  |                                                                                         |                                    | Dhrystone 2.1               | 7.98  |      | 100   |        |  |  |  |  |

|                         |                                  |                                                                                         | Ra<br>fhclk                        | Fibonacci                   | 7.41  |      | 93    |        |  |  |  |  |

|                         |                                  |                                                                                         | fHc                                | While(1)                    | 7.83  |      | 98    |        |  |  |  |  |

|                         |                                  |                                                                                         |                                    | Reduced code <sup>(1)</sup> | 310   |      | 155   |        |  |  |  |  |

|                         | Supply                           | f _f _0.MI                                                                              | 1-                                 | Coremark                    | 342   |      | 171   |        |  |  |  |  |

| I <sub>DD</sub> (LPRun) | current in<br>Low-power          | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2 MI<br>all peripherals disa                     |                                    | Dhrystone 2.1               | 324   | μA   | 162   | µA/MHz |  |  |  |  |

|                         | run                              |                                                                                         |                                    | Fibonacci                   | 324   |      | 162   |        |  |  |  |  |

|                         |                                  |                                                                                         |                                    | While(1)                    | 384   |      | 192   |        |  |  |  |  |

# Table 28. Typical current consumption in Run and Low-power run modes, with different codesrunning from Flash, ART disable

1. Reduced code used for characterization results provided in *Table 24, Table 25, Table 26.*

| Table 29. Typical current consumption in Run and Low-power run modes, with different codes |

|--------------------------------------------------------------------------------------------|

| running from SRAM1                                                                         |

|                         |                                  |                                                                     | Conditio                                      | ons                         | ТҮР   |      | ТҮР   |        |

|-------------------------|----------------------------------|---------------------------------------------------------------------|-----------------------------------------------|-----------------------------|-------|------|-------|--------|

| Symbol                  | Parameter                        | -                                                                   | Voltage<br>scaling                            | Code                        | 25 °C | Unit | 25 °C | Unit   |

|                         |                                  | f <sub>HCLK</sub> = f <sub>HSE</sub> up to                          | 2<br>MHz                                      | Reduced code <sup>(1)</sup> | 2.42  |      | 93    |        |

| I <sub>DD</sub> (Run)   |                                  |                                                                     | ≥ S                                           | Coremark                    | 2.18  |      | 84    |        |

|                         |                                  |                                                                     | ange<br>= 2(                                  | Dhrystone 2.1               | 2.40  | mA   | 92    | µA/MHz |

|                         | Supply<br>current in<br>Run mode | 48 MHz included,                                                    | luded, 한 또 Fibonacci 2.40<br>de While(1) 2.29 |                             | 92    |      |       |        |

|                         |                                  | bypass mode<br>PLL ON above                                         |                                               |                             | 88    |      |       |        |

|                         |                                  | 48 MHz all<br>peripherals<br>disable                                | e 1<br>0 MHz                                  | Reduced code <sup>(1)</sup> | 8.63  |      | 108   | µA/MHz |

|                         |                                  |                                                                     |                                               | Coremark                    | 7.76  | mA   | 97    |        |

|                         |                                  |                                                                     | Range 1<br><sub>LK</sub> = 80 I               | Dhrystone 2.1               | 8.55  |      | 107   |        |

|                         |                                  |                                                                     | Ra<br>f <sub>HCLK</sub> ⁼                     | Fibonacci                   | 8.56  |      | 107   |        |

|                         |                                  |                                                                     | рн                                            | While(1)                    | 8.12  |      | 102   |        |

|                         |                                  |                                                                     |                                               | Reduced code <sup>(1)</sup> | 205   |      | 103   |        |

|                         | Supply                           | 6 _6 _0.MI                                                          | -                                             | Coremark                    | 188   |      | 94    |        |

| I <sub>DD</sub> (LPRun) | current in<br>Low-power<br>run   | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2 MH<br>all peripherals disa |                                               | Dhrystone 2.1               | 222   | μA   | 111   | µA/MHz |

|                         |                                  |                                                                     | ~.~                                           | Fibonacci                   | 204   |      | 102   | ]      |

|                         |                                  |                                                                     |                                               | While(1)                    | 211   |      | 106   |        |

1. Reduced code used for characterization results provided in Table 24, Table 25, Table 26.

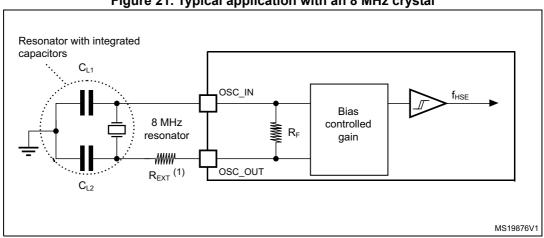

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 48 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 44*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                  | bol Parameter Conditions <sup>(2)</sup> Min Ty |                                                           |   |      |     | Unit |

|-------------------------|------------------------------------------------|-----------------------------------------------------------|---|------|-----|------|

| Gymbol                  |                                                | Conditions                                                |   | -    | Max |      |

| f <sub>OSC_IN</sub>     | Oscillator frequency                           | -                                                         | 4 | 8    | 48  | MHz  |

| $R_F$                   | Feedback resistor                              | -                                                         | - | 200  | -   | kΩ   |

|                         |                                                | During startup <sup>(3)</sup>                             | - | -    | 5.5 |      |

| I <sub>DD(HSE)</sub>    |                                                | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 10 pF@8 MHz  | - | 0.44 | -   |      |

|                         | HSE current consumption                        | V <sub>DD</sub> = 3 V,<br>Rm = 45 Ω,<br>CL = 10 pF@8 MHz  | - | 0.45 | -   |      |

|                         |                                                | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 5 pF@48 MHz  | - | 0.68 | -   | mA   |

|                         |                                                | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 10 pF@48 MHz | - | 0.94 | -   |      |

|                         |                                                | V <sub>DD</sub> = 3 V,<br>Rm = 30 Ω,<br>CL = 20 pF@48 MHz | - | 1.77 | -   |      |

| G <sub>m</sub>          | Maximum critical crystal transconductance      | Startup                                                   | - | -    | 1.5 | mA/V |

| $t_{\rm SU(HSE)}^{(4)}$ | Startup time                                   | V <sub>DD</sub> is stabilized                             | - | 2    | -   | ms   |

| Table 44. HSE oscillator characteristics <sup>(1)</sup> | Table 44. | HSE os | cillator | characteristics <sup>(1)</sup> |

|---------------------------------------------------------|-----------|--------|----------|--------------------------------|

|---------------------------------------------------------|-----------|--------|----------|--------------------------------|

1. Guaranteed by design.

2. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

3. This consumption level occurs during the first 2/3 of the  $t_{SU(HSE)}$  startup time

4. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 20 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 21*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 21. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 45*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                      | Conditions <sup>(2)</sup>                        | Min | Тур | Max  | Unit   |

|-------------------------------------|--------------------------------|--------------------------------------------------|-----|-----|------|--------|

| I <sub>DD(LSE)</sub>                |                                | LSEDRV[1:0] = 00<br>Low drive capability         | -   | 250 | -    |        |

|                                     | LSE ourrent consumption        | LSEDRV[1:0] = 01<br>Medium low drive capability  | -   | 315 | -    | nA     |

|                                     | LSE current consumption        | LSEDRV[1:0] = 10<br>Medium high drive capability | -   | 500 | -    |        |

|                                     |                                | LSEDRV[1:0] = 11<br>High drive capability        | -   | 630 | -    |        |

|                                     | Maximum critical crystal<br>gm | LSEDRV[1:0] = 00<br>Low drive capability         | -   | -   | 0.5  |        |

| Gm                                  |                                | LSEDRV[1:0] = 01<br>Medium low drive capability  | -   | -   | 0.75 |        |

| Gm <sub>critmax</sub>               |                                | LSEDRV[1:0] = 10<br>Medium high drive capability | -   | -   | 1.7  | - μΑ/V |

|                                     |                                | LSEDRV[1:0] = 11<br>High drive capability        | -   | -   | 2.7  |        |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time                   | V <sub>DD</sub> is stabilized                    | -   | 2   | -    | s      |

| Table 45. LSE oscillator characteristics | s (f <sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup> |

|------------------------------------------|--------------------------------------------------|

|------------------------------------------|--------------------------------------------------|

## 6.3.10 Flash memory characteristics

| Table 51. Flash memory characteristics |                                          |                    |               |       |      |  |  |  |  |

|----------------------------------------|------------------------------------------|--------------------|---------------|-------|------|--|--|--|--|

| Symbol                                 | Parameter                                | Conditions         | Тур           | Max   | Unit |  |  |  |  |

| t <sub>prog</sub>                      | 64-bit programming time                  | -                  | 81.69         | 90.76 | μs   |  |  |  |  |

| +                                      | one row (32 double                       | normal programming | 2.61          | 2.90  |      |  |  |  |  |

| t <sub>prog_row</sub>                  | word) programming time                   | fast programming   | 1.91          | 2.12  |      |  |  |  |  |

| +                                      | one page (2 Kbyte)                       | normal programming | 20.91         | 23.24 | ms   |  |  |  |  |

| t <sub>prog_page</sub>                 | programming time                         | fast programming   | 15.29         | 16.98 |      |  |  |  |  |

| t <sub>ERASE</sub>                     | Page (2 KB) erase time                   | -                  | 22.02         | 24.47 |      |  |  |  |  |

| +                                      | one bank (512 Kbyte)<br>programming time | normal programming | 5.35          | 5.95  | s    |  |  |  |  |

| t <sub>prog_bank</sub>                 |                                          | fast programming   | 3.91          | 4.35  | 5    |  |  |  |  |

| t <sub>ME</sub>                        | Mass erase time<br>(one or two banks)    | -                  | 22.13         | 24.59 | ms   |  |  |  |  |

|                                        | Average consumption                      | Write mode         | 3.4           | -     |      |  |  |  |  |

|                                        | from V <sub>DD</sub>                     | Erase mode         | 3.4           | -     | mA   |  |  |  |  |

| I <sub>DD</sub>                        | Maximum aurrant (naak)                   | Write mode         | 7 (for 2 µs)  | -     |      |  |  |  |  |

|                                        | Maximum current (peak)                   | Erase mode         | 7 (for 41 µs) | -     |      |  |  |  |  |

Table 51. Flash memory characteristics<sup>(1)</sup>

1. Guaranteed by design.

| Symbol           | Parameter      | Conditions                                           | Min <sup>(1)</sup> | Unit    |

|------------------|----------------|------------------------------------------------------|--------------------|---------|

| N <sub>END</sub> | Endurance      | T <sub>A</sub> = -40 to +105 °C                      | 10                 | kcycles |

|                  | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C    | 30                 |         |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C   | 15                 |         |

| +                |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 125 °C   | 7                  | Years   |

| t <sub>RET</sub> |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C  | 30                 | rears   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 15                 |         |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 |         |

#### Table 52. Flash memory endurance and data retention

1. Guaranteed by characterization results.

2. Cycling performed over the whole temperature range.

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                                                                           | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit |

|------------------|------------|------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------|------|

|                  |            |                                                                                                      | inequency build             | 8 MHz/ 80 MHz                                     |      |

|                  |            | V <sub>DD</sub> = 3.6 V, T <sub>A</sub> = 25 °C,<br>LQFP100 package<br>compliant with IEC<br>61967-2 | 0.1 MHz to 30 MHz           | -8                                                |      |

|                  |            |                                                                                                      | 30 MHz to 130 MHz           | 2                                                 | dBµV |

| S <sub>EMI</sub> | Peak level |                                                                                                      | 130 MHz to 1 GHz            | 5                                                 | υБμν |

|                  |            |                                                                                                      | 1 GHz to 2 GHz              | 8                                                 |      |

|                  |            |                                                                                                      | EMI Level                   | 2.5                                               | -    |

Table 54. EMI characteristics

#### 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symbol                | Ratings Conditions                                          |                                                                    | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------------|--------------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)          | $T_A = +25 \degree C$ , conforming<br>to ANSI/ESDA/JEDEC<br>JS-001 | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge<br>voltage (charge device<br>model) | $T_A = +25 $ °C,<br>conforming to ANSI/ESD<br>STM5.3.1             | C3    | 250                             | v    |

1. Guaranteed by characterization results.

| Sym-<br>bol      | Parameter               | (                                               | Conditions <sup>(4</sup> | )                        | Min  | Тур  | Max | Unit |

|------------------|-------------------------|-------------------------------------------------|--------------------------|--------------------------|------|------|-----|------|

|                  |                         |                                                 | Single                   | Fast channel (max speed) | -    | 4    | 5   |      |

| ET               | Total<br>unadjusted     |                                                 | ended                    | Slow channel (max speed) | -    | 4    | 5   |      |

|                  | error                   |                                                 | Differential             | Fast channel (max speed) | -    | 3.5  | 4.5 |      |

|                  |                         |                                                 | Dillerential             | Slow channel (max speed) | -    | 3.5  | 4.5 |      |

|                  |                         |                                                 | Single                   | Fast channel (max speed) | -    | 1    | 2.5 |      |

| EO               | Offset                  |                                                 | ended                    | Slow channel (max speed) | -    | 1    | 2.5 |      |

| LO               | error                   |                                                 | Differential             | Fast channel (max speed) | -    | 1.5  | 2.5 |      |

|                  |                         |                                                 | Dillerential             | Slow channel (max speed) | -    | 1.5  | 2.5 |      |

|                  |                         |                                                 | Single                   | Fast channel (max speed) | -    | 2.5  | 4.5 |      |

| EG               | Gain error              |                                                 | ended                    | Slow channel (max speed) | -    | 2.5  | 4.5 | LSB  |

| EG               | Gainenoi                |                                                 | Differential             | Fast channel (max speed) | -    | 2.5  | 3.5 | LOD  |

|                  |                         |                                                 | Differential             | Slow channel (max speed) | -    | 2.5  | 3.5 | -    |

|                  |                         | ferential<br>earity<br>or ADC clock frequency ≤ | Single<br>ended          | Fast channel (max speed) | -    | 1    | 1.5 |      |

| ED               | Differential            |                                                 |                          | Slow channel (max speed) | -    | 1    | 1.5 |      |

|                  | error                   |                                                 | Differential             | Fast channel (max speed) | -    | 1    | 1.2 |      |

|                  |                         |                                                 |                          | Slow channel (max speed) | -    | 1    | 1.2 |      |

|                  |                         | $V_{DDA} = VREF + = 3 V,$<br>TA = 25 °C         | Single<br>ended          | Fast channel (max speed) | -    | 1.5  | 2.5 | -    |

| EL               | Integral                |                                                 |                          | Slow channel (max speed) | -    | 1.5  | 2.5 |      |

| EL               | error                   |                                                 | Differential             | Fast channel (max speed) | -    | 1    | 2   |      |

|                  |                         |                                                 |                          | Slow channel (max speed) | -    | 1    | 2   |      |

|                  |                         |                                                 | Single                   | Fast channel (max speed) | 10.4 | 10.5 | -   |      |

| ENOB             | Effective number of     |                                                 | ended                    | Slow channel (max speed) | 10.4 | 10.5 | -   | bits |

| ENOD             | bits                    |                                                 | Differential             | Fast channel (max speed) | 10.8 | 10.9 | -   | DILS |

|                  |                         |                                                 | Dillerential             | Slow channel (max speed) | 10.8 | 10.9 | -   |      |

|                  | Signal to               |                                                 | Single                   | Fast channel (max speed) | 64.4 | 65   | -   |      |

| SINAD            | Signal-to-<br>noise and |                                                 | ended                    | Slow channel (max speed) | 64.4 | 65   | -   |      |

| distortion ratio |                         | Differential                                    | Fast channel (max speed) | 66.8                     | 67.4 | -    |     |      |

|                  | 1400                    |                                                 | Differential             | Slow channel (max speed) | 66.8 | 67.4 | -   | ЧD   |

|                  |                         |                                                 | Single                   | Fast channel (max speed) | 65   | 66   | -   | dB   |

| SNR              | Signal-to-              |                                                 | ended                    | Slow channel (max speed) | 65   | 66   | -   |      |

| SINK             | noise ratio             |                                                 | Differential             | Fast channel (max speed) | 67   | 68   | -   |      |

|                  |                         |                                                 | Differential             | Slow channel (max speed) | 67   | 68   | -   |      |

Table 65. ADC accuracy - limited test conditions 1<sup>(1)(2)(3)</sup>

|             | Table 67. Abc accuracy - Innited test conditions 5. A A (continued) |                                                                              |              |                          |     |      |     |    |  |  |

|-------------|---------------------------------------------------------------------|------------------------------------------------------------------------------|--------------|--------------------------|-----|------|-----|----|--|--|

| Sym-<br>bol | Parameter                                                           | C                                                                            | Min          | Тур                      | Max | Unit |     |    |  |  |

|             |                                                                     | 80 MHz,<br>I Sampling rate ≤ 5.33 Msps, –<br>nonic 1.65 V ≤ V== - = V=== - ≤ | Single       | Fast channel (max speed) | -   | -69  | -67 |    |  |  |

|             | Total                                                               |                                                                              | ended        | Slow channel (max speed) | -   | -71  | -67 |    |  |  |

| THD         | harmonic<br>distortion                                              |                                                                              |              | Fast channel (max speed) | -   | -72  | -71 | dB |  |  |

|             |                                                                     | 3.6 V,<br>Voltage scaling Range 1                                            | Differential | Slow channel (max speed) | -   | -72  | -71 |    |  |  |

Table 67. ADC accuracy - limited test conditions  $3^{(1)(2)(3)}$  (continued)

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

<sup>4.</sup> The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4 V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V. No oversampling.

| Symbol                         | Parameter | Conditions                 | Min | Тур | Мах | Unit |  |

|--------------------------------|-----------|----------------------------|-----|-----|-----|------|--|

| I <sub>DDA</sub> (VREF<br>BUF) | from Vpp  | I <sub>load</sub> = 0 μA   | -   | 16  | 25  |      |  |

|                                |           | I <sub>load</sub> = 500 μA | -   | 18  | 30  | μA   |  |

|                                |           | I <sub>load</sub> = 4 mA   | -   | 35  | 50  |      |  |

Table 71. VREFBUF characteristics<sup>(1)</sup> (continued)

1. Guaranteed by design, unless otherwise specified.

In degraded mode, the voltage reference buffer can not maintain accurately the output voltage which will follow (V<sub>DDA</sub> drop voltage).

3. Guaranteed by test in production.

4. The capacitive load must include a 100 nF capacitor in order to cut-off the high frequency noise.

5. To correctly control the VREFBUF inrush current during start-up phase and scaling change, the  $V_{DDA}$  voltage should be in the range [2.4 V to 3.6 V] and [2.8 V to 3.6 V] respectively for  $V_{RS}$  = 0 and  $V_{RS}$  = 1.

# 6.3.20 Comparator characteristics

| Symbol                    | Parameter                                       | Co                       | onditions                                         | Min  | Тур                 | Мах              | Unit     |  |

|---------------------------|-------------------------------------------------|--------------------------|---------------------------------------------------|------|---------------------|------------------|----------|--|

| V <sub>DDA</sub>          | Analog supply voltage                           |                          | -                                                 | 1.62 | -                   | 3.6              |          |  |

| V <sub>IN</sub>           | Comparator input voltage range                  | -                        |                                                   | 0    | -                   | V <sub>DDA</sub> | V        |  |

| $V_{BG}^{(2)}$            | Scaler input voltage                            |                          | -                                                 |      | V <sub>REFINT</sub> | -                |          |  |

| V <sub>SC</sub>           | Scaler offset voltage                           |                          | -                                                 | -    | ±5                  | ±10              | mV       |  |

|                           | Scaler static consumption                       | BRG_EN=0 (bi             | ridge disable)                                    | -    | 200                 | 300              | nA       |  |

| I <sub>DDA</sub> (SCALER) | from V <sub>DDA</sub>                           | BRG_EN=1 (bi             | ridge enable)                                     | -    | 0.8                 | 1                | μA       |  |

| t <sub>START_SCALER</sub> | Scaler startup time                             |                          | -                                                 | -    | 100                 | 200              | μs       |  |

|                           |                                                 | High-speed               | V <sub>DDA</sub> ≥ 2.7 V                          | -    | -                   | 5                |          |  |

|                           | Comparator startup time to                      | mode                     | V <sub>DDA</sub> < 2.7 V                          | -    | -                   | 7                |          |  |

| t <sub>START</sub>        | reach propagation delay                         | Medium mode              | V <sub>DDA</sub> ≥ 2.7 V                          | -    | -                   | 15               | μs       |  |

|                           | specification                                   | medium mode              | V <sub>DDA</sub> < 2.7 V                          | -    | -                   | 25               |          |  |

|                           |                                                 | Ultra-low-power mode     |                                                   | -    | -                   | 40               |          |  |

|                           | Propagation delay with<br>100 mV overdrive      | High-speed<br>mode       | V <sub>DDA</sub> ≥ 2.7 V                          | -    | 55                  | 80               | ns       |  |

| t <sub>D</sub> (3)        |                                                 |                          | V <sub>DDA</sub> < 2.7 V                          | -    | 65                  | 100              |          |  |

| <sup>L</sup> D(*)         |                                                 | Medium mode              |                                                   | -    | 0.55                | 0.9              |          |  |

|                           |                                                 | Ultra-low-powe           | Ultra-low-power mode                              |      | 4                   | 7                | μs       |  |

| V <sub>offset</sub>       | Comparator offset error                         | Full common              |                                                   | -    | ±5                  | ±20              | mV       |  |

|                           |                                                 | No hysteresis            |                                                   | -    | 0                   | -                |          |  |

| M                         |                                                 | Low hysteresis           | i .                                               | -    | 8                   | -                | -        |  |

| V <sub>hys</sub>          | Comparator hysteresis                           | Medium hysteresis        |                                                   | -    | 15                  | -                | mV       |  |

|                           |                                                 | High hysteresis          |                                                   | -    | 27                  | -                |          |  |

|                           |                                                 |                          | Static                                            | -    | 400                 | 600              | nA       |  |

|                           |                                                 | Ultra-low-<br>power mode | With 50 kHz<br>±100 mV overdrive<br>square signal | -    | 1200                | -                |          |  |

| I <sub>DDA</sub> (COMP)   |                                                 |                          | Static                                            | -    | 5                   | 7                |          |  |

|                           | Comparator consumption<br>from V <sub>DDA</sub> | Medium mode              | With 50 kHz<br>±100 mV overdrive<br>square signal | -    | 6                   | -                |          |  |

|                           |                                                 |                          | Static                                            | -    | 70                  | 100              | μA       |  |

|                           |                                                 | High-speed<br>mode       | With 50 kHz<br>±100 mV overdrive<br>square signal | -    | 75                  | -                | <u> </u> |  |

| Table 72. COMP characteristics |

|--------------------------------|

|--------------------------------|

1. Guaranteed by design, unless otherwise specified.

## 6.3.22 Temperature sensor characteristics

| Symbol                                        | Parameter                                                          | Min   | Тур  | Max   | Unit  |

|-----------------------------------------------|--------------------------------------------------------------------|-------|------|-------|-------|

| T <sub>L</sub> <sup>(1)</sup>                 | V <sub>TS</sub> linearity with temperature                         | -     | ±1   | ±2    | °C    |

| Avg_Slope <sup>(2)</sup>                      | Average slope                                                      | 2.3   | 2.5  | 2.7   | mV/°C |

| V <sub>30</sub>                               | Voltage at 30°C (±5 °C) <sup>(3)</sup>                             | 0.742 | 0.76 | 0.785 | V     |

| t <sub>START</sub><br>(TS_BUF) <sup>(1)</sup> | Sensor Buffer Start-up time in continuous mode <sup>(4)</sup>      | -     | 8    | 15    | μs    |

| t <sub>START</sub> <sup>(1)</sup>             | Start-up time when entering in continuous mode <sup>(4)</sup>      | -     | 70   | 120   | μs    |

| t <sub>S_temp</sub> <sup>(1)</sup>            | ADC sampling time when reading the temperature                     | 5     | -    | -     | μs    |

| I <sub>DD</sub> (TS) <sup>(1)</sup>           | Temperature sensor consumption from $V_{DD},$ when selected by ADC | -     | 4.7  | 7     | μA    |

#### Table 74. TS characteristics

1. Guaranteed by design.

2. Guaranteed by characterization results.

3. Measured at  $V_{DDA}$  = 3.0 V ±10 mV. The  $V_{30}$  ADC conversion result is stored in the TS\_CAL1 byte. Refer to *Table 6: Temperature sensor calibration values*.

4. Continuous mode means Run/Sleep modes, or temperature sensor enable in Low-power run/Low-power sleep modes.

## 6.3.23 V<sub>BAT</sub> monitoring characteristics

#### Table 75. V<sub>BAT</sub> monitoring characteristics

| Symbol                             | Parameter                               | Min | Тур | Max | Unit |

|------------------------------------|-----------------------------------------|-----|-----|-----|------|

| R                                  | Resistor bridge for V <sub>BAT</sub>    | -   | 39  | -   | kΩ   |

| Q                                  | Ratio on V <sub>BAT</sub> measurement   | -   | 3   | -   | -    |

| Er <sup>(1)</sup>                  | Error on Q                              | -10 | -   | 10  | %    |

| t <sub>S_vbat</sub> <sup>(1)</sup> | ADC sampling time when reading the VBAT | 12  | -   | -   | μs   |

1. Guaranteed by design.

#### Table 76. V<sub>BAT</sub> charging characteristics

| Symbol          | Parameter            | Conditions | Min | Тур | Мах | Unit |

|-----------------|----------------------|------------|-----|-----|-----|------|

|                 | Battery              | VBRS = 0   | -   | 5   | -   |      |

| R <sub>BC</sub> | charging<br>resistor | VBRS = 1   | -   | 1.5 | -   | kΩ   |

Г

Т

Т

Т

#### **SPI characteristics**

Unless otherwise specified, the parameters given in *Table 82* for SPI are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and supply voltage conditions summarized in *Table 20: General operating conditions*.

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| Symbol                                                | Parameter                | Conditions                                                                              | Min                              | Тур               | Max                  | Unit |     |

|-------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------|----------------------------------|-------------------|----------------------|------|-----|

|                                                       |                          | Master mode receiver/full duplex<br>2.7 < $V_{DD}$ < 3.6 V<br>Voltage Range 1           |                                  |                   | 40                   |      |     |

|                                                       |                          | Master mode receiver/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1   |                                  |                   | 16                   |      |     |

|                                                       |                          | Master mode transmitter<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1            |                                  |                   | 40                   |      |     |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>             | SPI clock frequency      | Slave mode receiver<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1                | -                                | -                 | -                    | 40   | MHz |

|                                                       |                          | Slave mode transmitter/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1  | ull duplex                       |                   | 37 <sup>(2)</sup>    |      |     |

|                                                       |                          | Slave mode transmitter/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1 |                                  |                   | 20 <sup>(2)</sup>    |      |     |

|                                                       |                          | Voltage Range 2                                                                         |                                  |                   | 13                   |      |     |

| t <sub>su(NSS)</sub>                                  | NSS setup time           | Slave mode, SPI prescaler = 2                                                           | 4 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                    | ns   |     |

| t <sub>h(NSS)</sub>                                   | NSS hold time            | Slave mode, SPI prescaler = 2                                                           | 2 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                    | ns   |     |

| $\begin{array}{c}t_{w(SCKH)}\\t_{w(SCKL)}\end{array}$ | SCK high and low time    | Master mode                                                                             | T <sub>PCLK</sub> -2             | T <sub>PCLK</sub> | T <sub>PCLK</sub> +2 | ns   |     |

| t <sub>su(MI)</sub>                                   | Data input setup time    | Master mode                                                                             | 4                                | -                 | -                    | ns   |     |

| t <sub>su(SI)</sub>                                   |                          | Slave mode                                                                              | 1.5                              | -                 | -                    | 115  |     |

| t <sub>h(MI)</sub>                                    | Data input hold time     | Master mode                                                                             |                                  | -                 | -                    | ns   |     |

| t <sub>h(SI)</sub>                                    |                          | Slave mode                                                                              | 1.5                              | -                 | -                    | 115  |     |

| t <sub>a(SO)</sub>                                    | Data output access time  | Slave mode                                                                              | 9                                | -                 | 36                   | ns   |     |

| t <sub>dis(SO)</sub>                                  | Data output disable time | Slave mode                                                                              | 9                                | -                 | 16                   | ns   |     |

| Table | 82. | SPI | characteristics | (1) |

|-------|-----|-----|-----------------|-----|

|-------|-----|-----|-----------------|-----|

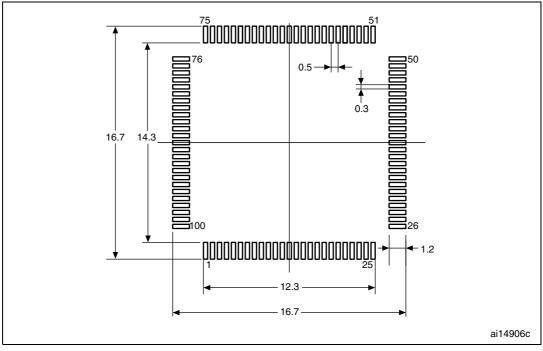

Figure 42. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

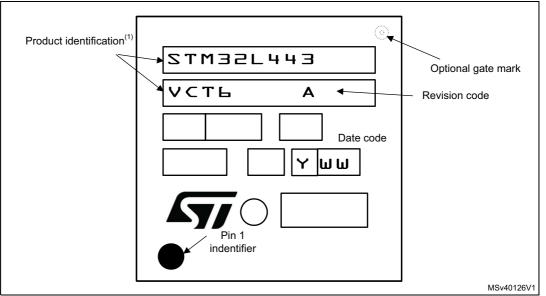

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 43. LQFP100 marking (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering

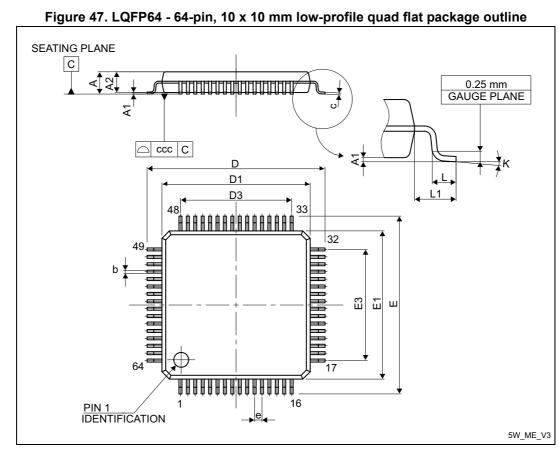

# 7.3 LQFP64 package information

1. Drawing is not to scale.

| Table 93. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat |

|-------------------------------------------------------------|

| package mechanical data                                     |

| Symbol | millimeters |        |       |        | inches <sup>(1)</sup> |        |

|--------|-------------|--------|-------|--------|-----------------------|--------|

| Symbol | Min         | Тур    | Max   | Min    | Тур                   | Max    |

| А      | -           | -      | 1.600 | -      | -                     | 0.0630 |

| A1     | 0.050       | -      | 0.150 | 0.0020 | -                     | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170       | 0.220  | 0.270 | 0.0067 | 0.0087                | 0.0106 |

| С      | 0.090       | -      | 0.200 | 0.0035 | -                     | 0.0079 |

| D      | -           | 12.000 | -     | -      | 0.4724                | -      |

| D1     | -           | 10.000 | -     | -      | 0.3937                | -      |

| D3     | -           | 7.500  | -     | -      | 0.2953                | -      |

| E      | -           | 12.000 | -     | -      | 0.4724                | -      |

| E1     | -           | 10.000 | -     | -      | 0.3937                | -      |

| Symbol           | millimeters |        |       |        | inches <sup>(1)</sup> |        |

|------------------|-------------|--------|-------|--------|-----------------------|--------|

| Symbol           | Min         | Тур    | Max   | Min    | Тур                   | Мах    |

| b <sup>(3)</sup> | 0.190       | 0.220  | 0.250 | 0.0075 | 0.0087                | 0.0098 |

| D                | 3.106       | 3.141  | 3.176 | 0.1223 | 0.1237                | 0.1250 |