Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                 |

|----------------------------|----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                     |

| Speed                      | 80MHz                                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                             |

| Number of I/O              | 52                                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 64K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                  |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 64-UFBGA, WLCSP                                                                        |

| Supplier Device Package    | 64-WLCSP (3.14x3.13)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l443rcy6tr                |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat                                  |                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| package mechanical data                                                            | 184                                                                                                                                                                                                 |

| UFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch ultra profile fine pitch ball grid array |                                                                                                                                                                                                     |

| package mechanical data                                                            | 187                                                                                                                                                                                                 |

| UFBGA64 recommended PCB design rules (0.5 mm pitch BGA)                            | 188                                                                                                                                                                                                 |

| WLCSP64 - 64-ball, 3.141 x 3.127 mm, 0.35 mm pitch wafer level chip scale          |                                                                                                                                                                                                     |

| package mechanical data                                                            | 190                                                                                                                                                                                                 |

|                                                                                    | 191                                                                                                                                                                                                 |

|                                                                                    |                                                                                                                                                                                                     |

|                                                                                    |                                                                                                                                                                                                     |

|                                                                                    | 195                                                                                                                                                                                                 |

|                                                                                    |                                                                                                                                                                                                     |

|                                                                                    | 197                                                                                                                                                                                                 |

|                                                                                    |                                                                                                                                                                                                     |

| package mechanical data                                                            | 200                                                                                                                                                                                                 |

| Package thermal characteristics                                                    | 202                                                                                                                                                                                                 |

| STM32L443xx ordering information scheme                                            | 205                                                                                                                                                                                                 |

| Document revision history                                                          | 206                                                                                                                                                                                                 |

|                                                                                    | package mechanical data<br>UFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch ultra profile fine pitch ball grid array<br>package mechanical data<br>UFBGA64 recommended PCB design rules (0.5 mm pitch BGA) |

# 3.27 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32L443xx devices have three embedded universal synchronous receiver transmitters (USART1, USART2 and USART3).

These interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. They provide hardware management of the CTS and RTS signals, and RS485 Driver Enable. They are able to communicate at speeds of up to 10Mbit/s.

USART1, USART2 and USART3 also provide Smart Card mode (ISO 7816 compliant) and SPI-like communication capability.

All USART have a clock domain independent from the CPU clock, allowing the USARTx (x=1,2,3) to wake up the MCU from Stop mode using baudrates up to 200 Kbaud. The wake up events from Stop mode are programmable and can be:

- Start bit detection

- Any received data frame

- A specific programmed data frame

All USART interfaces can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>   | USART1 | USART2      | USART3    | LPUART1 |  |  |  |  |  |  |

|---------------------------------------|--------|-------------|-----------|---------|--|--|--|--|--|--|

| Hardware flow control for modem       | Х      | Х           | Х         | Х       |  |  |  |  |  |  |

| Continuous communication using DMA    | X      | Х           | Х         | Х       |  |  |  |  |  |  |

| Multiprocessor communication          | Х      | Х           | Х         | Х       |  |  |  |  |  |  |

| Synchronous mode                      | Х      | Х           | Х         | -       |  |  |  |  |  |  |

| Smartcard mode                        | Х      | Х           | Х         | -       |  |  |  |  |  |  |

| Single-wire half-duplex communication | Х      | Х           | Х         | Х       |  |  |  |  |  |  |

| IrDA SIR ENDEC block                  | Х      | Х           | Х         | -       |  |  |  |  |  |  |

| LIN mode                              | Х      | Х           | Х         | -       |  |  |  |  |  |  |

| Dual clock domain                     | Х      | Х           | Х         | Х       |  |  |  |  |  |  |

| Wakeup from Stop 0 / Stop 1 modes     | Х      | Х           | Х         | Х       |  |  |  |  |  |  |

| Wakeup from Stop 2 mode               | -      | -           | -         | Х       |  |  |  |  |  |  |

| Receiver timeout interrupt            | Х      | Х           | Х         | -       |  |  |  |  |  |  |

| Modbus communication                  | Х      | Х           | Х         | -       |  |  |  |  |  |  |

| Auto baud rate detection              |        | X (4 modes) |           | -       |  |  |  |  |  |  |

| Driver Enable                         | Х      | Х           | Х         | Х       |  |  |  |  |  |  |

| LPUART/USART data length              |        | 7, 8 a      | nd 9 bits |         |  |  |  |  |  |  |

#### Table 10. STM32L443xx USART/LPUART features

1. X = supported.

- Transmission

- Three transmit mailboxes

- Configurable transmit priority

- Reception

- Two receive FIFOs with three stages

- 14 Scalable filter banks

- Identifier list feature

- Configurable FIFO overrun

- Time-triggered communication option

- Disable automatic retransmission mode

- 16-bit free running timer

- Time Stamp sent in last two data bytes

- Management

- Maskable interrupts

- Software-efficient mailbox mapping at a unique address space

# 3.33 Secure digital input/output and MultiMediaCards Interface (SDMMC)

The card host interface (SDMMC) provides an interface between the APB peripheral bus and MultiMediaCards (MMCs), SD memory cards and SDIO cards.

The SDMMC features include the following:

- Full compliance with MultiMediaCard System Specification Version 4.2. Card support for three different databus modes: 1-bit (default), 4-bit and 8-bit

- Full compatibility with previous versions of MultiMediaCards (forward compatibility)

- Full compliance with SD Memory Card Specifications Version 2.0

- Full compliance with SD I/O Card Specification Version 2.0: card support for two different databus modes: 1-bit (default) and 4-bit

- Data transfer up to 48 MHz for the 8 bit mode

- Data write and read with DMA capability

## 3.34 Universal serial bus (USB)

The STM32L443xx devices embed a full-speed USB device peripheral compliant with the USB specification version 2.0. The internal USB PHY supports USB FS signaling, embedded DP pull-up and also battery charging detection according to Battery Charging Specification Revision 1.2. The USB interface implements a full-speed (12 Mbit/s) function interface with added support for USB 2.0 Link Power Management. It has software-configurable endpoint setting with packet memory up-to 1 KB and suspend/resume support. It requires a precise 48 MHz clock which can be generated from the internal main PLL (the clock source must use a HSE crystal oscillator) or by the internal 48 MHz oscillator in automatic trimming mode. The synchronization for this oscillator can be taken from the USB data stream itself (SOF signalization) which allows crystal less operation.

|        |                 |         | Pin N   | lum    | ber     |         |          |                                       |          |               |       | Pin functions                                                                                  |                         |  |  |

|--------|-----------------|---------|---------|--------|---------|---------|----------|---------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------|-------------------------|--|--|

| LQFP48 | <b>UFQFPN48</b> | WLCSP49 | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                            | Additional<br>functions |  |  |

| -      | -               | -       | -       | -      | -       | 58      | J11      | PD11                                  | I/O      | FT_I          | -     | USART3_CTS,<br>TSC_G6_IO2,<br>LCD_SEG31,<br>LPTIM2_ETR,<br>EVENTOUT                            | -                       |  |  |

| -      | -               | -       | -       | -      | -       | 59      | J10      | PD12                                  | I/O      | FT_I          | -     | USART3_RTS_DE,<br>TSC_G6_IO3,<br>LCD_SEG32,<br>LPTIM2_IN1, EVENTOUT                            | -                       |  |  |

| -      | -               | -       | -       | -      | -       | 60      | H12      | PD13                                  | I/O      | FT_I          | -     | TSC_G6_IO4,<br>LCD_SEG33,<br>LPTIM2_OUT,<br>EVENTOUT                                           | -                       |  |  |

| -      | -               | -       | -       | -      | -       | 61      | H11      | PD14                                  | I/O      | FT_I          | -     | LCD_SEG34, EVENTOUT                                                                            | -                       |  |  |

| -      | -               | -       | -       | -      | -       | 62      | H10      | PD15                                  | I/O      | FT_I          | -     | LCD_SEG35, EVENTOUT                                                                            | -                       |  |  |

| -      | -               | -       | F1      | 37     | F6      | 63      | E12      | PC6                                   | I/O      | FT_I          | -     | TSC_G4_IO1,<br>LCD_SEG24,<br>SDMMC1_D6,<br>EVENTOUT                                            | -                       |  |  |

| -      | -               | -       | E1      | 38     | E7      | 64      | E11      | PC7                                   | I/O      | FT_I          | -     | TSC_G4_IO2,<br>LCD_SEG25,<br>SDMMC1_D7,<br>EVENTOUT                                            | -                       |  |  |

| -      | -               | -       | F3      | 39     | E8      | 65      | E10      | PC8                                   | I/O      | FT_I          | -     | TSC_G4_IO3,<br>LCD_SEG26,<br>SDMMC1_D0,<br>EVENTOUT                                            | -                       |  |  |

| -      | -               | -       | E2      | 40     | D8      | 66      | D12      | PC9                                   | I/O      | FT_I          | -     | TSC_G4_IO4, USB_NOE,<br>LCD_SEG27,<br>SDMMC1_D1,<br>EVENTOUT                                   | -                       |  |  |

| 29     | 29              | D1      | E3      | 41     | D7      | 67      | D11      | PA8                                   | I/O      | FT_I          | -     | MCO, TIM1_CH1,<br>USART1_CK,<br>LCD_COM0, SWPMI1_IO,<br>SAI1_SCK_A,<br>LPTIM2_OUT,<br>EVENTOUT | -                       |  |  |

| 30     | 30              | D2      | D1      | 42     | C7      | 68      | D10      | PA9                                   | I/O      | FT_fl         | -     | TIM1_CH2, I2C1_SCL,<br>USART1_TX,<br>LCD_COM1, SAI1_FS_A,<br>TIM15_BKIN, EVENTOUT              | -                       |  |  |

Table 13. STM32L443xx pin definitions (continued)

| 1 | 1 |

|---|---|

|   | Q |

|   | Ň |

|   | 0 |

|   | 7 |

|   |   |

#### Table 15. Alternate function AF8 to AF15 (for AF0 to AF7 see *Table 14*) (continued)

|        |     | AF8     | AF9      | AF10        | AF11 | AF12                                  | AF13 | AF14                        | AF15     |  |

|--------|-----|---------|----------|-------------|------|---------------------------------------|------|-----------------------------|----------|--|

| Port   |     | LPUART1 | CAN1/TSC | USB/QUADSPI | LCD  | SDMMC1/<br>COMP1/<br>COMP2/<br>SWPMI1 | SAI1 | TIM2/TIM15/<br>TIM16/LPTIM2 | EVENTOUT |  |

|        | PH0 | -       | -        | -           | -    | -                                     | -    | -                           | EVENTOUT |  |

| Port H | PH1 | -       | -        | -           | -    | -                                     | -    | -                           | EVENTOUT |  |

|        | PH3 | -       | -        | -           | -    | -                                     | -    | -                           | EVENTOUT |  |

## 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = V_{DDA} = 3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 6.1.4 Loading capacitor

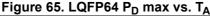

The loading conditions used for pin parameter measurement are shown in Figure 14.

## 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 15.

## 6.3.4 Embedded voltage reference

The parameters given in *Table 23* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*.

| Table 25. Ellibedded internal voltage reference |                                                                     |                                   |                  |       |                     |                          |  |  |  |  |

|-------------------------------------------------|---------------------------------------------------------------------|-----------------------------------|------------------|-------|---------------------|--------------------------|--|--|--|--|

| Symbol                                          | Parameter                                                           | Conditions                        | Min              | Тур   | Мах                 | Unit                     |  |  |  |  |

| V <sub>REFINT</sub>                             | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +130 °C | 1.182            | 1.212 | 1.232               | V                        |  |  |  |  |

| t <sub>S_vrefint</sub> <sup>(1)</sup>           | ADC sampling time when<br>reading the internal reference<br>voltage | -                                 | 4 <sup>(2)</sup> | -     | -                   | μs                       |  |  |  |  |

| t <sub>start_vrefint</sub>                      | Start time of reference voltage buffer when ADC is enable           | -                                 | -                | 8     | 12 <sup>(2)</sup>   | μs                       |  |  |  |  |

| I <sub>DD</sub> (V <sub>REFINTBUF</sub> )       | $V_{REFINT}$ buffer consumption from $V_{DD}$ when converted by ADC | -                                 | -                | 12.5  | 20 <sup>(2)</sup>   | μΑ                       |  |  |  |  |

| $\Delta V_{REFINT}$                             | Internal reference voltage spread over the temperature range        | V <sub>DD</sub> = 3 V             | -                | 5     | 7.5 <sup>(2)</sup>  | mV                       |  |  |  |  |

| T <sub>Coeff</sub>                              | Temperature coefficient                                             | –40°C < T <sub>A</sub> < +130°C   | -                | 30    | 50 <sup>(2)</sup>   | ppm/°C                   |  |  |  |  |

| A <sub>Coeff</sub>                              | Long term stability                                                 | 1000 hours, T = 25°C              | -                | -     | TBD <sup>(2)</sup>  | ppm                      |  |  |  |  |

| V <sub>DDCoeff</sub>                            | Voltage coefficient                                                 | 3.0 V < V <sub>DD</sub> < 3.6 V   | -                | 250   | 1200 <sup>(2)</sup> | ppm/V                    |  |  |  |  |

| V <sub>REFINT_DIV1</sub>                        | 1/4 reference voltage                                               |                                   | 24               | 25    | 26                  |                          |  |  |  |  |

| V <sub>REFINT_DIV2</sub>                        | 1/2 reference voltage                                               | ] -                               | 49               | 50    | 51                  | %<br>V <sub>REFINT</sub> |  |  |  |  |

| V <sub>REFINT_DIV3</sub>                        | 3/4 reference voltage                                               |                                   | 74               | 75    | 76                  |                          |  |  |  |  |

1. The shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design.

| STM32L443CC |  |

|-------------|--|

| STM32L443RC |  |

| SIM32L443VC |  |

|                           |                                        | Con                         | Conditions TYP     |                   |       |       |       |        | MAX <sup>(1)</sup> |       |       |       |        |        |     |

|---------------------------|----------------------------------------|-----------------------------|--------------------|-------------------|-------|-------|-------|--------|--------------------|-------|-------|-------|--------|--------|-----|

| Symbol                    | Parameter                              | -                           | Voltage<br>scaling | f <sub>HCLK</sub> | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C             | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | Uni |

|                           |                                        |                             |                    | 26 MHz            | 0.68  | 0.69  | 0.74  | 0.81   | 0.95               | 0.8   | 0.8   | 0.9   | 1.0    | 1.3    |     |

|                           |                                        |                             |                    | 16 MHz            | 0.46  | 0.48  | 0.52  | 0.59   | 0.73               | 0.5   | 0.6   | 0.6   | 0.8    | 1.1    |     |

|                           |                                        |                             |                    | 8 MHz             | 0.29  | 0.30  | 0.34  | 0.41   | 0.55               | 0.3   | 0.4   | 0.4   | 0.6    | 0.9    |     |

|                           |                                        |                             | Range 2            | 4 MHz             | 0.20  | 0.21  | 0.25  | 0.32   | 0.46               | 0.2   | 0.3   | 0.3   | 0.5    | 0.8    |     |

|                           | Supply<br>current in<br>sleep<br>mode, | t in mode<br>p pll ON above |                    | 2 MHz             | 0.16  | 0.17  | 0.21  | 0.28   | 0.42               | 0.2   | 0.2   | 0.3   | 0.4    | 0.7    |     |

|                           |                                        |                             |                    | 1 MHz             | 0.13  | 0.15  | 0.19  | 0.26   | 0.40               | 0.1   | 0.2   | 0.3   | 0.4    | 0.7    |     |

| I <sub>DD</sub> (Sleep)   |                                        |                             |                    | 100 kHz           | 0.11  | 0.13  | 0.17  | 0.24   | 0.38               | 0.1   | 0.2   | 0.2   | 0.4    | 0.7    | mA  |

| IDD(Gleep)                |                                        |                             | Range 1            | 80 MHz            | 2.23  | 2.25  | 2.30  | 2.38   | 2.54               | 2.5   | 2.5   | 2.6   | 2.8    | 3.1    |     |

|                           |                                        |                             |                    | 72 MHz            | 2.02  | 2.04  | 2.10  | 2.18   | 2.34               | 2.2   | 2.3   | 2.4   | 2.5    | 2.9    |     |

|                           |                                        |                             |                    | 64 MHz            | 1.82  | 1.84  | 1.89  | 1.98   | 2.14               | 2.0   | 2.1   | 2.1   | 2.3    | 2.6    |     |

|                           |                                        |                             |                    | 48 MHz            | 1.34  | 1.36  | 1.42  | 1.50   | 1.66               | 1.5   | 1.6   | 1.7   | 1.8    | 2.2    |     |

|                           |                                        |                             |                    | 32 MHz            | 0.93  | 0.95  | 1.01  | 1.09   | 1.25               | 1.1   | 1.1   | 1.2   | 1.4    | 1.7    |     |

|                           |                                        |                             |                    | 24 MHz            | 0.73  | 0.75  | 0.80  | 0.88   | 1.04               | 0.8   | 0.9   | 1.0   | 1.1    | 1.4    |     |

|                           |                                        |                             |                    | 16 MHz            | 0.53  | 0.55  | 0.60  | 0.68   | 0.84               | 0.6   | 0.6   | 0.7   | 0.9    | 1.2    |     |

|                           | Supply                                 |                             |                    | 2 MHz             | 71.8  | 80.7  | 125   | 200    | 350                | 91.1  | 122.7 | 191.3 | 341.5  | 653.5  |     |

| I <sub>DD</sub> (LPSleep) | current in                             | nt in                       |                    | 1 MHz             | 45.0  | 57.3  | 101   | 176    | 325                | 63.2  | 95.4  | 165.4 | 316.5  | 628.7  | μA  |

| IDD(LI Sleep)             | sleep                                  | all peripherals dis         | able               | 400 kHz           | 27.0  | 40.7  | 84.6  | 158    | 308                | 43.9  | 75.8  | 147.2 | 297.6  | 609.2  | μ   |

|                           | mode                                   |                             |                    | 100 kHz           | 22.8  | 30.9  | 63.3  | 113.2  | 207.7              | 35.2  | 67.9  | 140.9 | 290.8  | 602.4  | 1   |

1. Guaranteed by characterization results, unless otherwise specified.

#### 1. Guaranteed by characterization results, unless otherwise specified.

- 2. LCD enabled with external voltage source. Consumption from VLCD excluded. Refer to LCD controller characteristics for I<sub>VLCD</sub>.

- 3. Guaranteed by test in production.

- 4. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8 pF loading capacitors.

- 5. Wakeup with code execution from Flash. Average value given for a typical wakeup time as specified in Table 39: Low-power mode wakeup timings.

DocID028739 Rev 2

100/207

#### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 38*. The MCU is placed under the following conditions:

- All I/O pins are in Analog mode

- The given value is calculated by measuring the difference of the current consumptions:

- when the peripheral is clocked on

- when the peripheral is clocked off

- Ambient operating temperature and supply voltage conditions summarized in *Table 17: Voltage characteristics*

- The power consumption of the digital part of the on-chip peripherals is given in *Table 38*. The power consumption of the analog part of the peripherals (where applicable) is indicated in each related section of the datasheet.

|      | Peripheral                        | Range 1 | Range 2 | Low-power run<br>and sleep | Unit   |

|------|-----------------------------------|---------|---------|----------------------------|--------|

|      | Bus Matrix <sup>(1)</sup>         | 3.2     | 2.9     | 3.1                        |        |

|      | ADC independent clock domain      | 0.4     | 0.1     | 0.2                        |        |

|      | ADC clock domain                  | 2.1     | 1.9     | 1.9                        |        |

|      | AES                               | 1.7     | 1.5     | 1.6                        |        |

|      | CRC                               | 0.4     | 0.2     | 0.3                        |        |

|      | DMA1                              | 1.4     | 1.3     | 1.4                        |        |

|      | DMA2                              | 1.5     | 1.3     | 1.4                        |        |

|      | FLASH                             | 6.2     | 5.2     | 5.8                        |        |

|      | GPIOA <sup>(2)</sup>              | 1.7     | 1.4     | 1.6                        |        |

|      | GPIOB <sup>(2)</sup> )            | 1.6     | 1.3     | 1.6                        |        |

| AHB  | GPIOC <sup>(2)</sup>              | 1.7     | 1.5     | 1.6                        |        |

|      | GPIOD <sup>(2)</sup>              | 1.8     | 1.6     | 1.7                        | µA/MHz |

|      | GPIOE <sup>(2)</sup>              | 1.7     | 1.6     | 1.6                        |        |

|      | GPIOH <sup>(2)</sup>              | 0.6     | 0.6     | 0.5                        |        |

|      | QSPI                              | 7.0     | 5.8     | 7.3                        |        |

|      | RNG independent clock domain      | 2.2     | NA      | NA                         |        |

|      | RNG clock domain                  | 0.5     | NA      | NA                         |        |

|      | SRAM1                             | 0.8     | 0.9     | 0.7                        |        |

|      | SRAM2                             | 1.0     | 0.8     | 0.8                        |        |

|      | TSC                               | 1.6     | 1.3     | 1.3                        |        |

|      | All AHB Peripherals               | 25.2    | 21.7    | 23.6                       |        |

|      | AHB to APB1 bridge <sup>(3)</sup> | 0.9     | 0.7     | 0.9                        |        |

| APB1 | CAN1                              | 4.1     | 3.2     | 3.9                        |        |

#### Table 38. Peripheral current consumption

|      | Peripheral                      | Range 1 | Range 2 | Low-power run<br>and sleep | Unit   |

|------|---------------------------------|---------|---------|----------------------------|--------|

| APB1 | USART3 independent clock domain | 4.3     | 3.5     | 4.2                        |        |

|      | USART3 clock domain             | 1.5     | 1.1     | 1.3                        |        |

|      | WWDG                            | 0.5     | 0.5     | 0.5                        |        |

|      | All APB1 on                     | 51.5    | 35.5    | 48.6                       |        |

|      | AHB to APB2 <sup>(4)</sup>      | 1.0     | 0.9     | 0.9                        |        |

|      | FW                              | 0.2     | 0.2     | 0.2                        |        |

|      | SAI1 independent clock domain   | 2.3     | 1.8     | 1.9                        |        |

|      | SAI1 clock domain               | 2.1     | 1.8     | 2.0                        |        |

|      | SDMMC1 independent clock domain | 4.7     | 3.9     | 3.9                        |        |

|      | SDMMC1 clock domain             | 2.5     | 1.9     | 1.9                        | µA/MHz |

| APB2 | SPI1                            | 1.8     | 1.6     | 1.7                        |        |

| AFDZ | SYSCFG/VREFBUF/COMP             | 0.6     | 0.5     | 0.6                        |        |

|      | TIM1                            | 8.1     | 6.5     | 7.6                        |        |

|      | TIM15                           | 3.7     | 3.0     | 3.4                        |        |

|      | TIM16                           | 2.7     | 2.1     | 2.6                        |        |

|      | USART1 independent clock domain | 4.8     | 4.2     | 4.6                        |        |

|      | USART1 clock domain             | 1.5     | 1.3     | 1.7                        |        |

|      | All APB2 on                     | 24.2    | 19.9    | 22.6                       |        |

|      | ALL                             | 100.9   | 77.1    | 94.8                       |        |

Table 38. Peripheral current consumption (continued)

1. The BusMatrix is automatically active when at least one master is ON (CPU, DMA).

The GPIOx (x= A...H) dynamic current consumption is approximately divided by a factor two versus this table values when the GPIO port is locked thanks to LCKK and LCKy bits in the GPIOx\_LCKR register. In order to save the full GPIOx current consumption, the GPIOx clock should be disabled in the RCC when all port I/Os are used in alternate function or analog mode (clock is only required to read or write into GPIO registers, and is not used in AF or analog modes).

3. The AHB to APB1 Bridge is automatically active when at least one peripheral is ON on the APB1.

4. The AHB to APB2 Bridge is automatically active when at least one peripheral is ON on the APB2.

## 6.3.6 Wakeup time from low-power modes and voltage scaling transition times

The wakeup times given in *Table 39* are the latency between the event and the execution of the first user instruction.

The device goes in low-power mode after the WFE (Wait For Event) instruction.

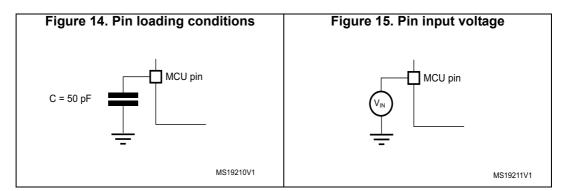

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 21. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 45*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                | Conditions <sup>(2)</sup>                        | Min | Тур | Max  | Unit |

|-------------------------------------|--------------------------|--------------------------------------------------|-----|-----|------|------|

|                                     |                          | LSEDRV[1:0] = 00<br>Low drive capability         | -   | 250 | -    |      |

|                                     | LSE ourrent consumption  | LSEDRV[1:0] = 01<br>Medium low drive capability  | -   | 315 | -    | nA   |

| IDD(LSE)                            | LSE current consumption  | LSEDRV[1:0] = 10<br>Medium high drive capability | -   | 500 | -    |      |

|                                     |                          | LSEDRV[1:0] = 11<br>High drive capability        | -   | 630 | -    |      |

|                                     |                          | LSEDRV[1:0] = 00<br>Low drive capability         | -   | -   | 0.5  |      |

| Gm                                  | Maximum critical crystal | LSEDRV[1:0] = 01<br>Medium low drive capability  | -   | -   | 0.75 | μΑ/V |

| Gm <sub>critmax</sub>               | gm                       | LSEDRV[1:0] = 10<br>Medium high drive capability | -   | -   | 1.7  | μΑνν |

|                                     |                          | LSEDRV[1:0] = 11<br>High drive capability        | -   | -   | 2.7  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time             | V <sub>DD</sub> is stabilized                    | -   | 2   | -    | s    |

| Table 45. LSE oscillator characteristics | s (f <sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup> |

|------------------------------------------|--------------------------------------------------|

|------------------------------------------|--------------------------------------------------|

| Symbol                | Parameter                                                                  | Conditions | Min | Тур                    | Max | Unit |

|-----------------------|----------------------------------------------------------------------------|------------|-----|------------------------|-----|------|

| N <sub>T</sub> jitter | Next transition jitter<br>Accumulated jitter on 28 cycles <sup>(4)</sup>   | -          | -   | +/-0.15 <sup>(2)</sup> | -   | ns   |

| P <sub>T</sub> jitter | Paired transition jitter<br>Accumulated jitter on 56 cycles <sup>(4)</sup> | -          | -   | +/-0.25 <sup>(2)</sup> | -   | ns   |

Table 48. HSI48 oscillator characteristics<sup>(1)</sup> (continued)

1. V\_{DD} = 3 V, T\_A = -40 to 125°C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

4. Jitter measurement are performed without clock source activated in parallel.

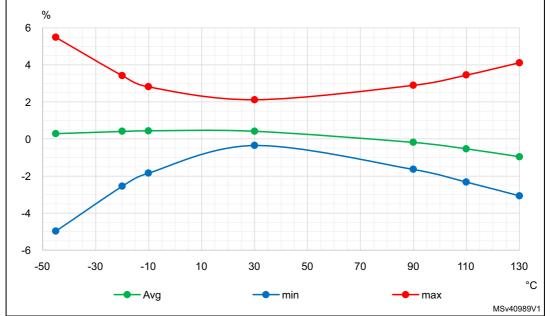

## Figure 25. HSI48 frequency versus temperature

## Low-speed internal (LSI) RC oscillator

| Symbol                                 | Parameter                            | Conditions                                      | Min   | Тур | Max   | Unit |

|----------------------------------------|--------------------------------------|-------------------------------------------------|-------|-----|-------|------|

| f                                      | LSI Frequency                        | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 30 °C | 31.04 | -   | 32.96 | kHz  |

| f <sub>LSI</sub>                       |                                      | $V_{DD}$ = 1.62 to 3.6 V, TA = -40 to 125 °C    | 29.5  | -   | 34    | κΠΖ  |

| t <sub>SU</sub> (LSI) <sup>(2)</sup>   | LSI oscillator start-<br>up time     | -                                               | -     | 80  | 130   | μs   |

| t <sub>STAB</sub> (LSI) <sup>(2)</sup> | LSI oscillator<br>stabilization time | 5% of final frequency                           | -     | 125 | 180   | μs   |

| I <sub>DD</sub> (LSI) <sup>(2)</sup>   | LSI oscillator power consumption     | -                                               | -     | 110 | 180   | nA   |

1. Guaranteed by characterization results.

2. Guaranteed by design.

| Speed | Symbol   | Parameter                       | Conditions                                 | Min | Max                | Unit |  |  |  |  |

|-------|----------|---------------------------------|--------------------------------------------|-----|--------------------|------|--|--|--|--|

|       |          |                                 | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 50                 |      |  |  |  |  |

|       |          |                                 | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 25                 |      |  |  |  |  |

|       | Emoy     | Maximum fraguanau               | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 5                  |      |  |  |  |  |

|       | Fmax     | Maximum frequency               | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 100 <sup>(3)</sup> | MHz  |  |  |  |  |

|       |          |                                 | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 37.5               |      |  |  |  |  |

| 10    |          |                                 | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 5                  |      |  |  |  |  |

| 10    |          |                                 | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 5.8                |      |  |  |  |  |

|       |          |                                 | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 11                 |      |  |  |  |  |

|       |          | Tr/Tf Output rise and fall time | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 28                 | ns   |  |  |  |  |

|       | 11/11    |                                 | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 2.5                |      |  |  |  |  |

|       |          |                                 | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 5                  |      |  |  |  |  |

|       |          |                                 | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 12                 |      |  |  |  |  |

|       |          |                                 | C=30 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 120 <sup>(3)</sup> |      |  |  |  |  |

|       |          |                                 | C=30 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 50                 |      |  |  |  |  |

|       | <b>F</b> | NA                              | C=30 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 10                 | MHz  |  |  |  |  |

|       | Fmax     | Maximum frequency               | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 180 <sup>(3)</sup> |      |  |  |  |  |

| 11    |          |                                 | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 75                 |      |  |  |  |  |

|       |          |                                 | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 10                 |      |  |  |  |  |

|       |          |                                 | C=30 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 3.3                |      |  |  |  |  |

|       | Tr/Tf    | Output rise and fall time       | C=30 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 6                  | ns   |  |  |  |  |

|       |          |                                 | C=30 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 16                 |      |  |  |  |  |

| Emt   | Fmax     | Maximum frequency               | C = 50  pE = 1.6  V/cV = -2.6  V/c         | -   | 1                  | MHz  |  |  |  |  |

| Fm+   | Tf       | Output fall time <sup>(4)</sup> | −C=50 pF, 1.6 V≤V <sub>DDIOx</sub> ≤3.6 V  | -   | 5                  | ns   |  |  |  |  |

The I/O speed is configured using the OSPEEDRy[1:0] bits. The Fm+ mode is configured in the SYSCFG\_CFGR1 register. Refer to the RM0394 reference manual for a description of GPIO Port configuration register.

2. Guaranteed by design.

3. This value represents the I/O capability but the maximum system frequency is limited to 80 MHz.

4. The fall time is defined between 70% and 30% of the output waveform accordingly to I<sup>2</sup>C specification.

## 6.3.18 Digital-to-Analog converter characteristics

| Symbol                             | Parameter                                               | Co                                                             | onditions                            | Min | Тур              | Max                        | Unit |

|------------------------------------|---------------------------------------------------------|----------------------------------------------------------------|--------------------------------------|-----|------------------|----------------------------|------|

| V <sub>DDA</sub>                   | Analog supply voltage for<br>DAC ON                     |                                                                | -                                    | 1.8 | -                | 3.6                        |      |

| V <sub>REF+</sub>                  | Positive reference voltage                              | -                                                              |                                      | 1.8 | -                | V <sub>DDA</sub>           | V    |

| V <sub>REF-</sub>                  | Negative reference voltage                              |                                                                | -                                    |     | V <sub>SSA</sub> |                            |      |

| RL                                 | Resistive load                                          | DAC oulput                                                     |                                      | 5   | -                | -                          | kΩ   |

| ••                                 |                                                         | buffer ON                                                      | connected to $V_{DDA}$               | 25  | -                | -                          |      |

| R <sub>O</sub>                     | Output Impedance                                        | DAC output bu                                                  | ffer OFF                             | 9.6 | 11.7             | 13.8                       | kΩ   |

|                                    | Output impedance sample                                 | V <sub>DD</sub> = 2.7 V                                        |                                      | -   | -                | 2                          |      |

| R <sub>BON</sub>                   | and hold mode, output buffer ON                         | V <sub>DD</sub> = 2.0 V                                        |                                      | -   | -                | 3.5                        | kΩ   |

| _                                  | Output impedance sample                                 | V <sub>DD</sub> = 2.7 V                                        |                                      | -   | -                | 16.5                       |      |

| R <sub>BOFF</sub>                  | and hold mode, output<br>buffer OFF                     | V <sub>DD</sub> = 2.0 V                                        |                                      | -   | -                | 18.0                       | kΩ   |

| CL                                 | Concettive lead                                         | DAC output buffer ON                                           |                                      | -   | -                | 50                         | pF   |

| C <sub>SH</sub>                    | Capacitive load                                         | Sample and hold mode                                           |                                      | -   | 0.1              | 1                          | μF   |

| V <sub>DAC_OUT</sub>               | Voltage on DAC_OUT                                      | DAC output buffer ON                                           |                                      | 0.2 | -                | V <sub>REF+</sub><br>- 0.2 | V    |

|                                    | συιραι                                                  | DAC output buffer OFF                                          |                                      | 0   | -                | V <sub>REF+</sub>          |      |

|                                    |                                                         |                                                                | ±0.5 LSB                             | -   | 1.7              | 3                          |      |

|                                    | Settling time (full scale: for a 12-bit code transition | Normal mode<br>DAC output                                      | ±1 LSB                               | -   | 1.6              | 2.9                        | μs   |

|                                    | between the lowest and                                  | buffer ON                                                      | ±2 LSB                               | -   | 1.55             | 2.85                       |      |

| t <sub>SETTLING</sub>              | the highest input codes<br>when DAC_OUT reaches         | CL ≤ 50 pF,<br>RL ≥ 5 kΩ                                       | ±4 LSB                               | -   | 1.48             | 2.8                        |      |

|                                    | final value ±0.5LSB,<br>±1 LSB, ±2 LSB, ±4 LSB,         | -                                                              | ±8 LSB                               | -   | 1.4              | 2.75                       |      |

|                                    | ±8 LSB)                                                 | Normal mode DAC output buffer<br>OFF, ±1LSB, CL = 10 pF        |                                      | -   | 2                | 2.5                        |      |

| + (2)                              | Wakeup time from off state (setting the ENx bit in the  | Normal mode DAC output buffer ON CL ≤ 50 pF, RL ≥ 5 k $\Omega$ |                                      | -   | 4.2              | 7.5                        | - µs |

| t <sub>WAKEUP</sub> <sup>(2)</sup> | DAC Control register) until final value ±1 LSB          | Normal mode DAC output buffer<br>OFF, CL ≤ 10 pF               |                                      | -   | 2                | 5                          |      |

| PSRR                               | V <sub>DDA</sub> supply rejection ratio                 | Normal mode [<br>CL ≤ 50 pF, RL                                | DAC output buffer ON<br>. = 5 kΩ, DC | -   | -80              | -28                        | dB   |

| Table ( | 69. | DAC | characteristics <sup>(1)</sup> |

|---------|-----|-----|--------------------------------|

|---------|-----|-----|--------------------------------|

## 6.3.24 LCD controller characteristics

The devices embed a built-in step-up converter to provide a constant LCD reference voltage independently from the V<sub>DD</sub> voltage. An external capacitor C<sub>ext</sub> must be connected to the VLCD pin to decouple this converter.

| Symbol                          | Parameter                                        | Conditions                                 | Min | Тур                  | Max | Unit |  |

|---------------------------------|--------------------------------------------------|--------------------------------------------|-----|----------------------|-----|------|--|

| V <sub>LCD</sub>                | LCD external voltage                             |                                            | -   | -                    | 3.6 |      |  |

| V <sub>LCD0</sub>               | LCD internal reference volta                     | ge 0                                       | -   | 2.62                 | -   |      |  |

| V <sub>LCD1</sub>               | LCD internal reference volta                     | ge 1                                       | -   | 2.76                 | -   |      |  |

| V <sub>LCD2</sub>               | LCD internal reference volta                     | ge 2                                       | -   | 2.89                 | -   |      |  |

| V <sub>LCD3</sub>               | LCD internal reference volta                     | ge 3                                       | -   | 3.04                 | -   | V    |  |

| $V_{LCD4}$                      | LCD internal reference volta                     | ge 4                                       | -   | 3.19                 | -   |      |  |

| $V_{LCD5}$                      | LCD internal reference volta                     | ge 5                                       | -   | 3.32                 | -   |      |  |

| $V_{LCD6}$                      | LCD internal reference volta                     | ge 6                                       | -   | 3.46                 | -   |      |  |

| V <sub>LCD7</sub>               | LCD internal reference volta                     | ge 7                                       | -   | 3.62                 | -   |      |  |

| C                               | V <sub>I CD</sub> external capacitance           | Buffer OFF<br>(BUFEN=0 is LCD_CR register) | 0.2 | -                    | 2   | μF   |  |

| C <sub>ext</sub>                |                                                  | Buffer ON<br>(BUFEN=1 is LCD_CR register)  | 1   | -                    | 2   | μ    |  |

| ı (2)                           | Supply current from $V_{DD}$ at $V_{DD}$ = 2.2 V | Buffer OFF<br>(BUFEN=0 is LCD_CR register) | -   | 3                    | -   |      |  |

| I <sub>LCD</sub> <sup>(2)</sup> | Supply current from $V_{DD}$ at $V_{DD}$ = 3.0 V | Buffer OFF<br>(BUFEN=0 is LCD_CR register) | -   | 1.5                  | -   | μA   |  |

|                                 |                                                  | Buffer OFF<br>(BUFFEN = 0, PON = 0)        | -   | 0.5                  | -   |      |  |

|                                 | Supply current from V <sub>LCD</sub>             | Buffer ON<br>(BUFFEN = 1, 1/2 Bias)        | -   | 0.6                  | -   |      |  |

| I <sub>VLCD</sub>               | $(V_{LCD} = 3 V)$                                | Buffer ON<br>(BUFFEN = 1, 1/3 Bias)        | -   | 0.8                  | -   | μA   |  |

|                                 |                                                  | Buffer ON<br>(BUFFEN = 1, 1/4 Bias)        | -   | 1                    | -   |      |  |

| R <sub>HN</sub>                 | Total High Resistor value for                    | Low drive resistive network                | -   | 5.5                  | -   | MΩ   |  |

| R <sub>LN</sub>                 | Total Low Resistor value for                     | High drive resistive network               | -   | 240                  | -   | kΩ   |  |

| V <sub>44</sub>                 | Segment/Common highest I                         | evel voltage                               | -   | V <sub>LCD</sub>     | -   |      |  |

| V <sub>34</sub>                 | Segment/Common 3/4 level                         | voltage                                    | -   | 3/4 V <sub>LCD</sub> | -   |      |  |

| V <sub>23</sub>                 | Segment/Common 2/3 level                         | voltage                                    | -   | 2/3 V <sub>LCD</sub> | -   | 1    |  |

| V <sub>12</sub>                 | Segment/Common 1/2 level                         | voltage                                    | -   | 1/2 V <sub>LCD</sub> | -   | V    |  |

| V <sub>13</sub>                 | Segment/Common 1/3 level                         | voltage                                    | -   | 1/3 V <sub>LCD</sub> | -   |      |  |

| V <sub>14</sub>                 | Segment/Common 1/4 level                         | voltage                                    | -   | 1/4 V <sub>LCD</sub> | -   |      |  |

| V <sub>0</sub>                  | Segment/Common lowest le                         | evel voltage                               | -   | 0                    | -   | 1    |  |

| Table 77. | LCD | controller | characteristics <sup>(1)</sup> |

|-----------|-----|------------|--------------------------------|

|           |     | CONTROLLET | Characteristics                |

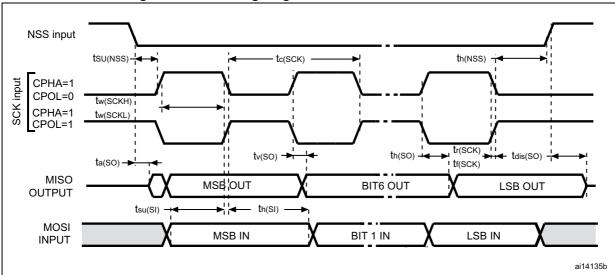

Figure 33. SPI timing diagram - slave mode and CPHA = 1

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

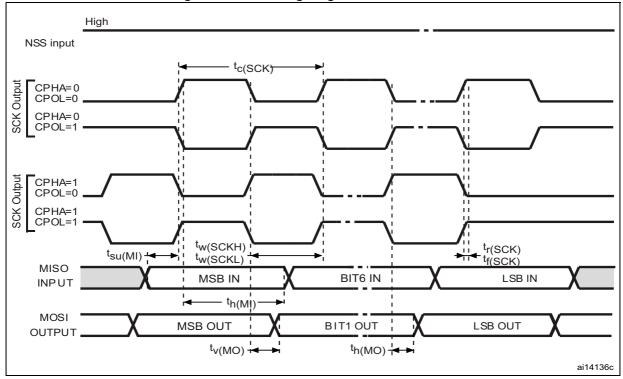

## Figure 34. SPI timing diagram - master mode

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

DocID028739 Rev 2

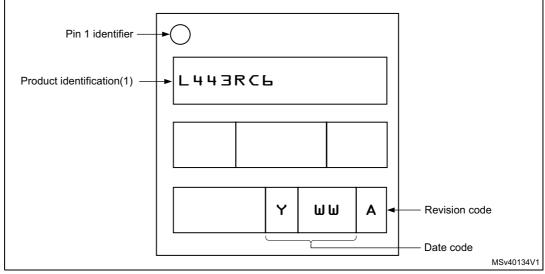

## **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

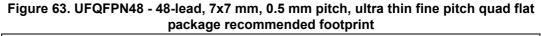

| Cumhal |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Мах   | Min    | Тур                   | Мах    |

| А      | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217                | 0.0236 |

| A1     | 0.000 | 0.020       | 0.050 | 0.0000 | 0.0008                | 0.0020 |

| D      | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795 |

| E      | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795 |

| D2     | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244 |

| E2     | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244 |

| L      | 0.300 | 0.400       | 0.500 | 0.0118 | 0.0157                | 0.0197 |

| Т      | -     | 0.152       | -     | -      | 0.0060                | -      |

| b      | 0.200 | 0.250       | 0.300 | 0.0079 | 0.0098                | 0.0118 |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |

| ddd    | -     | -           | 0.080 | -      | -                     | 0.0031 |

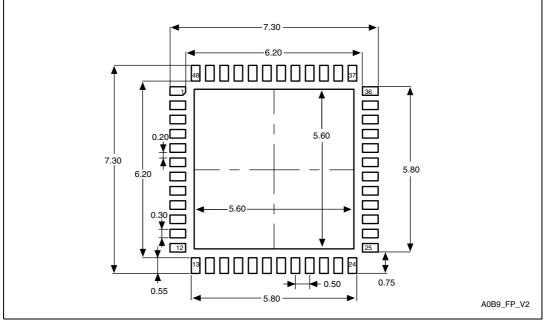

## Table 101. UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

DocID028739 Rev 2

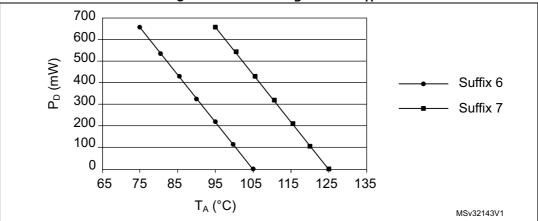

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 100 °C (measured according to JESD51-2), I<sub>DDmax</sub> = 20 mA, V<sub>DD</sub> = 3.5 V, maximum 20 I/Os used at the same time in output at low level with I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V

P<sub>INTmax</sub> = 20 mA × 3.5 V= 70 mW

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$

This gives:  $P_{INTmax}$  = 70 mW and  $P_{IOmax}$  = 64 mW:

P<sub>Dmax</sub> = 70 + 64 = 134 mW

Thus: P<sub>Dmax</sub> = 134 mW

Using the values obtained in Table 102  $T_{Jmax}$  is calculated as follows:

- For LQFP64, 46 °C/W

- T<sub>Jmax</sub> = 100 °C + (46 °C/W × 134 mW) = 100 °C + 6.164 °C = 106.164 °C

This is above the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Section 8: Part numbering*) unless we reduce the power dissipation in order to be able to use suffix 6 parts.

Refer to *Figure 65* to select the required temperature range (suffix 6 or 7) according to your ambient temperature or power requirements.