# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | 8051                                                                      |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 50MHz                                                                     |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), CANbus, LINbus, SPI, UART/USART |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                                |

| Number of I/O              | 40                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 4.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                              |

| Data Converters            | A/D 32x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 48-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 48-QFN (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f500-imr           |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 23.3. SMB0DAT: SMBus Data                                | . 236 |

|-------------------------------------------------------------------------|-------|

| SFR Definition 24.1. SCON0: Serial Port 0 Control                       | . 248 |

| SFR Definition 24.2. SMOD0: Serial Port 0 Control                       | . 249 |

| SFR Definition 24.3. SBUF0: Serial (UART0) Port Data Buffer             |       |

| SFR Definition 24.4. SBCON0: UART0 Baud Rate Generator Control          | . 250 |

| SFR Definition 24.6. SBRLL0: UART0 Baud Rate Generator Reload Low Byte  | . 251 |

| SFR Definition 24.5. SBRLH0: UART0 Baud Rate Generator Reload High Byte | . 251 |

| SFR Definition 25.1. SPI0CFG: SPI0 Configuration                        | . 259 |

| SFR Definition 25.2. SPI0CN: SPI0 Control                               |       |

| SFR Definition 25.3. SPI0CKR: SPI0 Clock Rate                           | . 261 |

| SFR Definition 25.4. SPI0DAT: SPI0 Data                                 | . 261 |

| SFR Definition 26.1. CKCON: Clock Control                               | . 266 |

| SFR Definition 26.2. TCON: Timer Control                                | . 271 |

| SFR Definition 26.3. TMOD: Timer Mode                                   | . 272 |

| SFR Definition 26.4. TL0: Timer 0 Low Byte                              | . 273 |

| SFR Definition 26.5. TL1: Timer 1 Low Byte                              | . 273 |

| SFR Definition 26.6. TH0: Timer 0 High Byte                             |       |

| SFR Definition 26.7. TH1: Timer 1 High Byte                             |       |

| SFR Definition 26.8. TMR2CN: Timer 2 Control                            | . 278 |

| SFR Definition 26.9. TMR2RLL: Timer 2 Reload Register Low Byte          | . 279 |

| SFR Definition 26.10. TMR2RLH: Timer 2 Reload Register High Byte        | . 279 |

| SFR Definition 26.11. TMR2L: Timer 2 Low Byte                           | . 280 |

| SFR Definition 26.12. TMR2H Timer 2 High Byte                           | . 280 |

| SFR Definition 26.13. TMR3CN: Timer 3 Control                           | . 284 |

| SFR Definition 26.14. TMR3RLL: Timer 3 Reload Register Low Byte         | . 285 |

| SFR Definition 26.15. TMR3RLH: Timer 3 Reload Register High Byte        | . 285 |

| SFR Definition 26.16. TMR3L: Timer 3 Low Byte                           | . 286 |

| SFR Definition 26.17. TMR3H Timer 3 High Byte                           | . 286 |

| SFR Definition 27.1. PCA0CN: PCA Control                                |       |

| SFR Definition 27.2. PCA0MD: PCA Mode                                   | . 301 |

| SFR Definition 27.3. PCA0PWM: PCA PWM Configuration                     |       |

| SFR Definition 27.4. PCA0CPMn: PCA Capture/Compare Mode                 | . 303 |

| SFR Definition 27.5. PCA0L: PCA Counter/Timer Low Byte                  | . 304 |

| SFR Definition 27.6. PCA0H: PCA Counter/Timer High Byte                 | . 304 |

| SFR Definition 27.7. PCA0CPLn: PCA Capture Module Low Byte              | . 305 |

| SFR Definition 27.8. PCA0CPHn: PCA Capture Module High Byte             | . 305 |

| C2 Register Definition 28.1. C2ADD: C2 Address                          | . 306 |

| C2 Register Definition 28.2. DEVICEID: C2 Device ID                     |       |

| C2 Register Definition 28.3. REVID: C2 Revision ID                      |       |

| C2 Register Definition 28.4. FPCTL: C2 Flash Programming Control        | . 308 |

| C2 Register Definition 28.5. FPDAT: C2 Flash Programming Data           | . 308 |

|                                                                         |       |

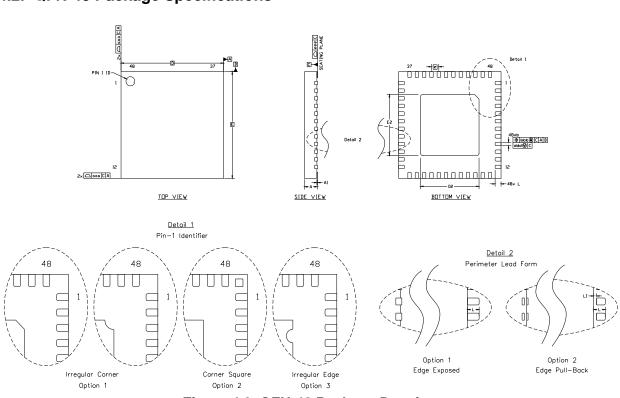

#### 4.2. QFN-48 Package Specifications

Figure 4.3. QFN-48 Package Drawing

#### Table 4.3. QFN-48 Package Dimensions

| Dimension | Min      | Тур      | Max  | Dimension | Min  | Тур  | Ma  |

|-----------|----------|----------|------|-----------|------|------|-----|

| A         | 0.80     | 0.90     | 1.00 | E2        | 3.90 | 4.00 | 4.1 |

| A1        | 0.00     | -        | 0.05 | L         | 0.30 | 0.40 | 0.5 |

| b         | 0.18     | 0.23     | 0.30 | L1        | 0.00 | -    | 0.0 |

| D         | 7.00 BSC |          |      | aaa       | -    | -    | 0.1 |

| D2        | 3.90     | 4.00     | 4.10 | bbb       | -    | -    | 0.1 |

| е         |          | 0.50 BSC | •    | ddd       | -    | -    | 0.0 |

| E         |          | 7.00 BSC |      | eee       | -    | -    | 0.0 |

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC outline MO-220, variation VKKD-4 except for features D2 and L which are toleranced per supplier designation.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

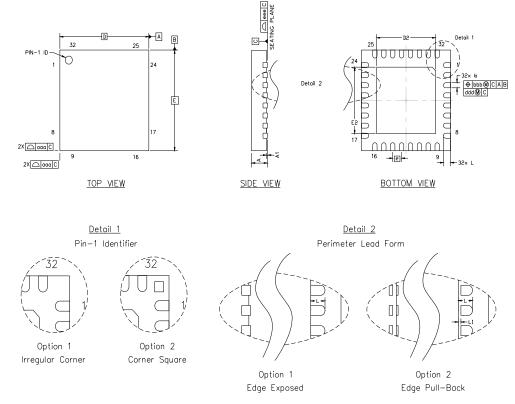

### 4.5. QFN-32 Package Specifications

Figure 4.9. QFN-32 Package Drawing

| Dimension | Min       | Тур  | Max  | Dimension | Min  | Тур  | Max  |

|-----------|-----------|------|------|-----------|------|------|------|

| А         | 0.80      | 0.9  | 1.00 | E2        | 3.20 | 3.30 | 3.40 |

| A1        | 0.00      | 0.02 | 0.05 | L         | 0.30 | 0.40 | 0.50 |

| b         | 0.18      | 0.25 | 0.30 | L1        | 0.00 | —    | 0.15 |

| D         | 5.00 BSC. |      |      | aaa       |      | —    | 0.15 |

| D2        | 3.20      | 3.30 | 3.40 | bbb       | _    | —    | 0.15 |

| е         | 0.50 BSC. |      |      | ddd       | _    | —    | 0.05 |

| E         | 5.00 BSC. |      |      | eee       | _    | —    | 0.08 |

#### Table 4.9. QFN-32 Package Dimensions

Notes:

- **1.** All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation VGGD except for custom features D2, E2, and L which are toleranced per supplier designation.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

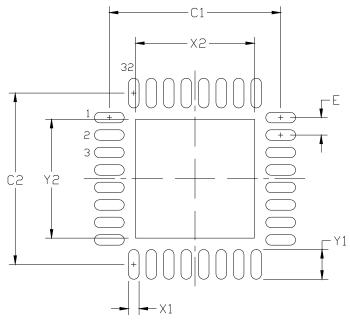

Figure 4.10. QFN-32 Package Drawing

| Dimension | Min      | Мах  | Dimension | Min  | Max  |

|-----------|----------|------|-----------|------|------|

| C1        | 4.80     | 4.90 | X2        | 3.20 | 3.40 |

| C2        | 4.80     | 4.90 | Y1        | 0.75 | 0.85 |

| е         | 0.50 BSC |      | Y2        | 3.20 | 3.40 |

| X1        | 0.20     | 0.30 |           |      |      |

Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

Solder Mask Design

**3.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60μm minimum, all the way around the pad.

Stencil Design

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- 7. A 3x3 array of 1.0 mm openings on a 1.20 mm pitch should be used for the center ground pad.

Card Assembly

- 8. A No-Clean, Type-3 solder paste is recommended.

- **9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### **Table 5.4. Reset Electrical Characteristics**

-40 to +125 °C unless otherwise specified.

| Parameter                                              | Conditions                                                                            | Min                   | Тур  | Max                   | Units |

|--------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| RST Output Low Voltage                                 | VIO = 5 V; IOL = 70 µA                                                                |                       | _    | 40                    | mV    |

| RST Input High Voltage                                 |                                                                                       | 0.7 x V <sub>IO</sub> | _    | —                     |       |

| RST Input Low Voltage                                  |                                                                                       | —                     | —    | 0.3 x V <sub>IO</sub> |       |

| RST Input Pullup Current                               | $\overline{\text{RST}}$ = 0.0 V, VIO = 5 V                                            |                       | 47   | 115                   | μA    |

| $V_{DD}$ RST Threshold ( $V_{RST-LOW}$ )               |                                                                                       | 1.65                  | 1.75 | 1.80                  | V     |

| V <sub>DD</sub> RST Threshold (V <sub>RST-HIGH</sub> ) |                                                                                       | 2.25                  | 2.30 | 2.45                  | V     |

| Missing Clock Detector Timeout                         | Time from last system clock<br>rising edge to reset initiation<br>VDD = 2.1V          | 200                   | 370  | 600                   | μs    |

|                                                        | VDD = 2.5V                                                                            | 200                   | 270  | 600                   |       |

| Reset Time Delay                                       | Delay between release of<br>any reset source and code<br>execution at location 0x0000 | _                     | 130  | 160                   | μs    |

| Minimum RST Low Time to<br>Generate a System Reset     |                                                                                       | 6                     | _    | _                     | μs    |

| V <sub>DD</sub> Monitor Turn-on Time                   |                                                                                       |                       | 60   | 100                   | μs    |

| V <sub>DD</sub> Monitor Supply Current                 |                                                                                       |                       | 1    | 2                     | μA    |

#### **Table 5.5. Flash Electrical Characteristics**

$V_{DD}$  = 1.8 to 2.75 V, –40 to +125 °C unless otherwise specified.

| Parameter                                                                                                                                                               | ameter Conditions        |                                    | Тур                | Max | Units       |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------|--------------------|-----|-------------|--|--|

| Flash Size                                                                                                                                                              | C8051F500/1/2/3/8/9      | 6                                  | 65536 <sup>*</sup> |     |             |  |  |

|                                                                                                                                                                         | C8051F504/5/6/7-F510/1   | 32768                              |                    |     | Bytes       |  |  |

| Endurance                                                                                                                                                               |                          | 20 k                               | 150 k              | _   | Erase/Write |  |  |

| Flash Retention                                                                                                                                                         | 85 °C                    | 10                                 | —                  |     | Years       |  |  |

| Erase Cycle Time                                                                                                                                                        | 25 MHz System Clock      | 28                                 | 30                 | 45  | ms          |  |  |

| Write Cycle Time                                                                                                                                                        | 25 MHz System Clock      | 79                                 | 84                 | 125 | μs          |  |  |

| V <sub>DD</sub>                                                                                                                                                         | Write / Erase operations | V <sub>RST-HIGH</sub> <sup>2</sup> |                    | _   | V           |  |  |

| <ol> <li>On the 64K Flash devices, 1024 bytes at addresses 0xFC00 to 0xFFFF are reserved.</li> <li>See Table 5.4 for the V<sub>RST-HIGH</sub> specification.</li> </ol> |                          |                                    |                    |     |             |  |  |

### 6.2. Output Code Formatting

The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code. When the repeat count is set to 1, conversion codes are represented in 12-bit unsigned integer format and the output conversion code is updated after each conversion. Inputs are measured from 0 to  $V_{REF} \times 4095/4096$ . Data can be right-justified or left-justified, depending on the setting of the AD0LJST bit (ADC0CN.2). Unused bits in the ADC0H and ADC0L registers are set to 0. Example codes are shown below for both right-justified and left-justified data.

| Input Voltage    | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|------------------|----------------------------------------------|---------------------------------------------|

| VREF x 4095/4096 | 0x0FFF                                       | 0xFFF0                                      |

| VREF x 2048/4096 | 0x0800                                       | 0x8000                                      |

| VREF x 2047/4096 | 0x07FF                                       | 0x7FF0                                      |

| 0                | 0x0000                                       | 0x0000                                      |

When the ADC0 Repeat Count is greater than 1, the output conversion code represents the accumulated result of the conversions performed and is updated after the last conversion in the series is finished. Sets of 4, 8, or 16 consecutive samples can be accumulated and represented in unsigned integer format. The repeat count can be selected using the AD0RPT bits in the ADC0CF register. The value must be right-justified (AD0LJST = 0), and unused bits in the ADC0H and ADC0L registers are set to 0. The following example shows right-justified codes for repeat counts greater than 1. Notice that accumulating  $2^n$  samples is equivalent to left-shifting by *n* bit positions when all samples returned from the ADC have the same value.

| Input Voltage                | Repeat Count = 4 | Repeat Count = 8 | Repeat Count = 16 |

|------------------------------|------------------|------------------|-------------------|

| V <sub>REF</sub> x 4095/4096 | 0x3FFC           | 0x7FF8           | 0xFFF0            |

| V <sub>REF</sub> x 2048/4096 | 0x2000           | 0x4000           | 0x8000            |

| V <sub>REF</sub> x 2047/4096 | 0x1FFC           | 0x3FF8           | 0x7FF0            |

| 0                            | 0x0000           | 0x0000           | 0x0000            |

#### 6.2.1. Settling Time Requirements

A minimum tracking time is required before an accurate conversion is performed. This tracking time is determined by any series impedance, including the AMUX0 resistance, the ADC0 sampling capacitance, and the accuracy required for the conversion.

Figure 6.5 shows the equivalent ADC0 input circuit. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 6.1. When measuring the Temperature Sensor output, use the settling time specified in Table 5.10 on page 50. When measuring V<sub>DD</sub> with respect to GND,  $R_{TO-TAL}$  reduces to  $R_{MUX}$ . See Table 5.9 for ADC0 minimum settling time requirements as well as the mux impedance and sampling capacitor values.

$$t = ln\left(\frac{2^{n}}{SA}\right) \times R_{TOTAL}C_{SAMPLE}$$

#### Equation 6.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance.

n is the ADC resolution in bits (10).

Comparator outputs can be polled in software, used as an interrupt source, and/or routed to a Port pin. When routed to a Port pin, Comparator outputs are available asynchronous or synchronous to the system clock; the asynchronous output is available even in STOP mode (with no system clock active). When disabled, the Comparator output (if assigned to a Port I/O pin via the Crossbar) defaults to the logic low state, and the power supply to the comparator is turned off. See Section "20.3. Priority Crossbar Decoder" on page 180 for details on configuring Comparator outputs via the digital Crossbar. Comparator inputs can be externally driven from -0.25 V to (V<sub>DD</sub>) + 0.25 V without damage or upset. The complete Comparator electrical specifications are given in Table 5.12.

The Comparator response time may be configured in software via the CPTnMD registers (see SFR Definition 9.2). Selecting a longer response time reduces the Comparator supply current. See Table 5.12 on page 51 for complete timing and supply current requirements.

Comparator hysteresis is software-programmable via its Comparator Control register CPTnCN.

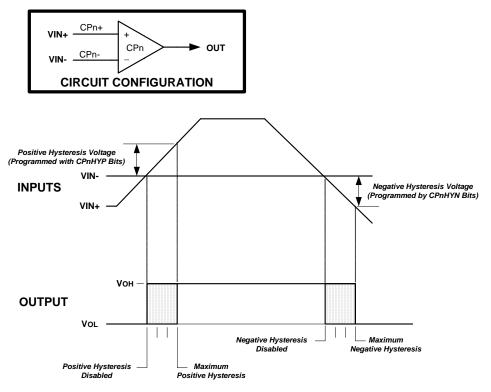

The amount of negative hysteresis voltage is determined by the settings of the CPnHYN bits. As shown in Figure 9.2, various levels of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CPnHYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see "14. Interrupts" on page 117.) The CPnFIF flag is set to 1 upon a Comparator falling-edge, and the CPnRIF flag is set to 1 upon the Comparator rising-edge. Once set, these bits remain set until cleared by software. The output state of the Comparator can be obtained at any time by reading the CPnOUT bit. The Comparator is enabled by setting the CPnEN bit to 1, and is disabled by clearing this bit to 0.

## SFR Definition 9.3. CPT1CN: Comparator1 Control

| Bit   | 7     | 6      | 5      | 4      | 3    | 2       | 1    | 0       |

|-------|-------|--------|--------|--------|------|---------|------|---------|

| Name  | CP1EN | CP1OUT | CP1RIF | CP1FIF | CP1H | YP[1:0] | CP1H | /N[1:0] |

| Туре  | R/W   | R      | R/W    | R/W    | R/   | W       | R/   | W       |

| Reset | 0     | 0      | 0      | 0      | 0    | 0       | 0    | 0       |

### SFR Address = 0x9D; SFR Page = 0x00

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP1EN       | Comparator1 Enable Bit.                                                       |

|     |             | 0: Comparator1 Disabled.                                                      |

|     |             | 1: Comparator1 Enabled.                                                       |

| 6   | CP1OUT      | Comparator1 Output State Flag.                                                |

|     |             | 0: Voltage on CP1+ < CP1–.                                                    |

|     |             | 1: Voltage on CP1+ > CP1                                                      |

| 5   | CP1RIF      | Comparator1 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator1 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator1 Rising Edge has occurred.                                      |

| 4   | CP1FIF      | Comparator1 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator1 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator1 Falling-Edge has occurred.                                     |

| 3:2 | CP1HYP[1:0] | Comparator1 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP1HYN[1:0] | Comparator1 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

## SFR Definition 13.2. SFRPAGE: SFR Page

| Bit  | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|------|---|--------------|---|---|---|---|---|---|--|--|--|

| Name |   | SFRPAGE[7:0] |   |   |   |   |   |   |  |  |  |

| Туре |   | R/W          |   |   |   |   |   |   |  |  |  |

|      |   |              |   |   |   | _ | _ | - |  |  |  |

#### SFR Address = 0xA7; SFR Page = All Pages

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SFRPAGE[7:0] | SFR Page Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |              | Represents the SFR Page the C8051 core uses when reading or modifying SFRs.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |              | Write: Sets the SFR Page.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |              | Read: Byte is the SFR page the C8051 core is using.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |              | When enabled in the SFR Page Control Register (SFR0CN), the C8051 core will automatically switch to the SFR Page that contains the SFRs of the correspond-<br>ing peripheral/function that caused the interrupt, and return to the previous SFR page upon return from interrupt (unless SFR Stack was altered before a return-<br>ing from the interrupt). SFRPAGE is the top byte of the SFR Page Stack, and push/pop events of this stack are caused by interrupts (and not by reading/writ-<br>ing to the SFRPAGE register) |

## Table 13.3. Special Function Registers

| Register    | Address | Description                              | Page |

|-------------|---------|------------------------------------------|------|

| ACC         | 0xE0    | Accumulator                              | 94   |

| ADC0CF      | 0xBC    | ADC0 Configuration                       | 63   |

| ADC0CN      | 0xE8    | ADC0 Control                             | 65   |

| ADC0GTH     | 0xC4    | ADC0 Greater-Than Compare High           | 67   |

| ADC0GTL     | 0xC3    | ADC0 Greater-Than Compare Low            | 67   |

| ADC0H       | 0xBE    | ADC0 High                                | 64   |

| ADC0L       | 0xBD    | ADC0 Low                                 | 64   |

| ADC0LTH     | 0xC6    | ADC0 Less-Than Compare Word High         | 68   |

| ADC0LTL     | 0xC5    | ADC0 Less-Than Compare Word Low          | 68   |

| ADC0MX      | 0xBB    | ADC0 Mux Configuration                   | 71   |

| ADC0TK      | 0xBA    | ADC0 Tracking Mode Select                | 66   |

| В           | 0xF0    | B Register                               | 94   |

| CCH0CN      | 0xE3    | Cache Control                            | 137  |

| CKCON       | 0x8E    | Clock Control                            | 266  |

| CLKMUL      | 0x97    | Clock Multiplier                         | 171  |

| CLKSEL 0x8F |         | Clock Select                             | 166  |

| CPT0CN      | 0x9A    | Comparator0 Control                      | 77   |

| CPT0MD      | 0x9B    | Comparator0 Mode Selection               | 78   |

| CPT0MX      | 0x9C    | Comparator0 MUX Selection                | 82   |

| CPT1CN      | 0x9D    | Comparator1 Control                      | 77   |

| CPT1MD      | 0x9E    | Comparator1 Mode Selection               | 78   |

| CPT1MX      | 0x9F    | Comparator1 MUX Selection                | 82   |

| DPH         | 0x83    | Data Pointer High                        | 93   |

| DPL         | 0x82    | Data Pointer Low                         | 93   |

| EIE1        | 0xE6    | Extended Interrupt Enable 1              | 123  |

| EIE2        | 0xE7    | Extended Interrupt Enable 2              | 123  |

| EIP1        | 0xF6    | Extended Interrupt Priority 1            | 124  |

| EIP2        | 0xF7    | Extended Interrupt Priority 2            | 125  |

| EMI0CF      | 0xB2    | External Memory Interface Configuration  | 152  |

| EMI0CN      | 0xAA    | External Memory Interface Control        | 151  |

| EMIOTC      | 0xAA    | External Memory Interface Timing Control | 157  |

| FLKEY       | 0xB7    | Flash Lock and Key                       | 135  |

| FLSCL       | 0xB6    | Flash Scale                              | 136  |

| IE          | 0xA8    | Interrupt Enable                         | 121  |

| IP          | 0xB8    | Interrupt Priority                       | 122  |

#### 15.4.3. System Clock

- 1. If operating from an external crystal, be advised that crystal performance is susceptible to electrical interference and is sensitive to layout and to changes in temperature. If the system is operating in an electrically noisy environment, use the internal oscillator or use an external CMOS clock.

- 2. If operating from the external oscillator, switch to the internal oscillator during Flash write or erase operations. The external oscillator can continue to run, and the CPU can switch back to the external oscillator after the Flash operation has completed.

Additional Flash recommendations and example code can be found in "AN201: Writing to Flash from Firm-ware" available from the Silicon Laboratories web site.

### SFR Definition 15.1. PSCTL: Program Store R/W Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|-------|---|---|---|---|---|---|------|------|

| Name  |   |   |   |   |   |   | PSEE | PSWE |

| Туре  | R | R | R | R | R | R | R/W  | R/W  |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0    |

#### SFR Address = 0x8F; SFR Page = 0x00

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b, Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1   | PSEE   | <ul> <li>Program Store Erase Enable.</li> <li>Setting this bit (in combination with PSWE) allows an entire page of Flash program memory to be erased. If this bit is logic 1 and Flash writes are enabled (PSWE is logic 1), a write to Flash memory using the MOVX instruction will erase the entire page that contains the location addressed by the MOVX instruction. The value of the data byte written does not matter.</li> <li>0: Flash program memory erasure disabled.</li> </ul> |

|     |        | 1: Flash program memory erasure enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0   | PSWE   | <ul> <li>Program Store Write Enable.</li> <li>Setting this bit allows writing a byte of data to the Flash program memory using the MOVX write instruction. The Flash location should be erased before writing data.</li> <li>0: Writes to Flash program memory disabled.</li> <li>1: Writes to Flash program memory enabled; the MOVX write instruction targets Flash memory.</li> </ul>                                                                                                   |

### 16.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the controller core to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the device performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout of 100  $\mu$ s.

#### 16.3. Suspend Mode

Setting the SUSPEND bit (OSCICN.5) causes the hardware to halt the CPU and the high-frequency internal oscillator, and go into Suspend mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. Most digital peripherals are not active in Suspend mode. The exception to this is the Port Match feature.

Suspend mode can be terminated by three types of events, a port match (described in Section "20.5. Port Match" on page 187), a Comparator low output (if enabled), or a device reset event. When Suspend mode is terminated, the device will continue execution on the instruction following the one that set the SUSPEND bit. If the wake event was configured to generate an interrupt, the interrupt will be serviced upon waking the device. If Suspend mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

Note: When entering suspend mode, firmware must set the ZTCEN bit in REF0CN (SFR Definition 8.1).

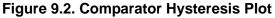

## 17. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the  $\overrightarrow{RST}$  pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source. Program execution begins at location 0x0000.

Figure 17.1. Reset Sources

## 18. External Data Memory Interface and On-Chip XRAM

For C8051F50x/F51x devices, 4 kB of RAM are included on-chip and mapped into the external data memory space (XRAM). Additionally, an External Memory Interface (EMIF) is available on the C8051F500/1/4/5 and C8051F508/9-F510/1 devices, which can be used to access off-chip data memories and memorymapped devices connected to the GPIO ports. The external memory space may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using the MOVX indirect addressing mode using R0 or R1. If the MOVX instruction is used with an 8-bit address operand (such as @R1), then the high byte of the 16-bit address is provided by the External Memory Interface Control Register (EMI0CN, shown in SFR Definition 18.1).

**Note:** The MOVX instruction can also be used for writing to the Flash memory. See Section "15. Flash Memory" on page 129 for details. The MOVX instruction accesses XRAM by default.

#### 18.1. Accessing XRAM

The XRAM memory space is accessed using the MOVX instruction. The MOVX instruction has two forms, both of which use an indirect addressing method. The first method uses the Data Pointer, DPTR, a 16-bit register which contains the effective address of the XRAM location to be read from or written to. The second method uses R0 or R1 in combination with the EMI0CN register to generate the effective XRAM address. Examples of both of these methods are given below.

#### 18.1.1. 16-Bit MOVX Example

The 16-bit form of the MOVX instruction accesses the memory location pointed to by the contents of the DPTR register. The following series of instructions reads the value of the byte at address 0x1234 into the accumulator A:

MOVDPTR, #1234h; load DPTR with 16-bit address to read (0x1234)MOVXA, @DPTR; load contents of 0x1234 into accumulator A

The above example uses the 16-bit immediate MOV instruction to set the contents of DPTR. Alternately, the DPTR can be accessed through the SFR registers DPH, which contains the upper 8-bits of DPTR, and DPL, which contains the lower 8-bits of DPTR.

#### 18.1.2. 8-Bit MOVX Example

The 8-bit form of the MOVX instruction uses the contents of the EMI0CN SFR to determine the upper 8-bits of the effective address to be accessed and the contents of R0 or R1 to determine the lower 8-bits of the effective address to be accessed. The following series of instructions read the contents of the byte at address 0x1234 into the accumulator A.

| MOV  | EMIOCN, #12h | ; load high byte of address into EMIOCN      |

|------|--------------|----------------------------------------------|

| MOV  | R0, #34h     | ; load low byte of address into R0 (or R1)   |

| MOVX | a, @R0       | ; load contents of 0x1234 into accumulator A |

### 23.1. Supporting Documents

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The I<sup>2</sup>C-Bus and How to Use It (including specifications), Philips Semiconductor.

- 2. The I<sup>2</sup>C-Bus Specification—Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification—Version 1.1, SBS Implementers Forum.

#### 23.2. SMBus Configuration

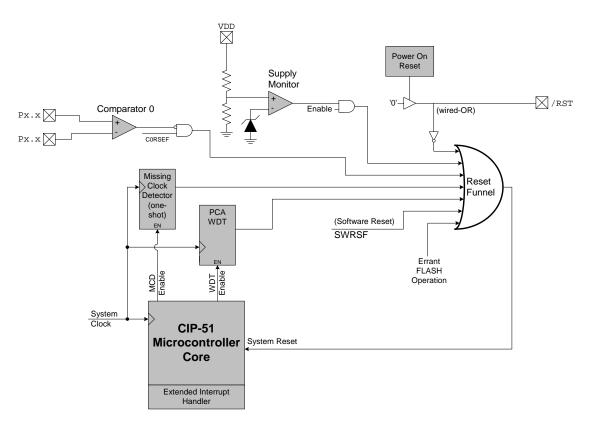

Figure 23.2 shows a typical SMBus configuration. The SMBus specification allows any recessive voltage between 3.0 V and 5.0 V; different devices on the bus may operate at different voltage levels. The bi-directional SCL (serial clock) and SDA (serial data) lines must be connected to a positive power supply voltage through a pullup resistor or similar circuit. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines, so that both are pulled high (recessive state) when the bus is free. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus not exceed 300 ns and 1000 ns, respectively.

Figure 23.2. Typical SMBus Configuration

### 23.3. SMBus Operation

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. The SMBus interface may operate as a master or a slave, and multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. It is not necessary to specify one device as the Master in a system; any device who transmits a START and a slave address becomes the master for the duration of that transfer.

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7–1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Bytes that are received (by a master or slave) are acknowledged (ACK) with a low SDA during a high SCL (see Figure 23.3). If the receiving device does not ACK, the transmitting device will read a NACK (not acknowledge), which is a high SDA during a high SCL.

The direction bit (R/W) occupies the least-significant bit position of the address byte. The direction bit is set to logic 1 to indicate a "READ" operation and cleared to logic 0 to indicate a "WRITE" operation.

|                     | Values Read Current SMbus State |   | Current SMbus State | Typical Response Options | Values to<br>Write |                                                                                             |                                                            | s<br>ected |     |     |                                |

|---------------------|---------------------------------|---|---------------------|--------------------------|--------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------|------------|-----|-----|--------------------------------|

| Mode                | Status<br>Vector                |   | ACKKG               | ARBLOST                  | ACK                |                                                                                             |                                                            | STA        | STO | ACK | Next Status<br>Vector Expected |

|                     | 0100                            | 0 |                     | 0                        | 0                  | A slave byte was transmitted;<br>NACK received.                                             | No action required (expecting STOP condition).             | 0          | 0   | Х   | 0001                           |

| ter                 |                                 | 0 |                     | 0                        | 1                  | A slave byte was transmitted;<br>ACK received.                                              | Load SMB0DAT with next data byte to transmit.              | 0          | 0   | Х   | 0100                           |

| ansmitt             |                                 | 0 |                     | 1                        | Х                  | A Slave byte was transmitted; error detected.                                               | No action required (expecting Master to end transfer).     | 0          | 0   | Х   | 0001                           |

| Slave Transmitter   | 0101                            | 0 |                     | X                        | Х                  | An illegal STOP or bus error<br>was detected while a Slave<br>Transmission was in progress. | Clear STO.                                                 | 0          | 0   | Х   | —                              |

|                     | 0010                            | 1 | (                   | 0                        | Х                  | A slave address + R/W was received; ACK requested.                                          | If Write, Acknowledge received address                     | 0          | 0   | 1   | 0000                           |

|                     |                                 |   |                     |                          |                    |                                                                                             | If Read, Load SMB0DAT with data byte; ACK received address | 0          | 0   | 1   | 0100                           |

|                     |                                 |   |                     |                          |                    |                                                                                             | NACK received address.                                     | 0          | 0   | 0   | —                              |

|                     |                                 | 1 |                     | 1                        | Х                  | Lost arbitration as master;<br>slave address + R/W received;                                | If Write, Acknowledge received address                     | 0          | 0   | 1   | 0000                           |

|                     |                                 |   |                     |                          |                    | ACK requested.                                                                              | If Read, Load SMB0DAT with data byte; ACK received address | 0          | 0   | 1   | 0100                           |

|                     |                                 |   |                     |                          |                    |                                                                                             | NACK received address.                                     | 0          | 0   | 0   | —                              |

|                     |                                 |   |                     |                          |                    |                                                                                             | Reschedule failed transfer;<br>NACK received address.      | 1          | 0   | 0   | 1110                           |

|                     | 0001                            | 0 |                     | 0                        | Х                  | A STOP was detected while<br>addressed as a Slave Trans-<br>mitter or Slave Receiver.       | Clear STO.                                                 | 0          | 0   | Х   |                                |

| eiver               |                                 | 1 |                     | 1                        | Х                  | Lost arbitration while attempt-<br>ing a STOP.                                              | No action required (transfer complete/aborted).            | 0          | 0   | 0   | —                              |

| Slave Rece          | 0000                            | 1 | (                   | 0                        | Х                  | A slave byte was received;<br>ACK requested.                                                | Acknowledge received byte;<br>Read SMB0DAT.                | 0          | 0   | 1   | 0000                           |

| Slav                |                                 |   |                     |                          |                    |                                                                                             | NACK received byte.                                        | 0          | 0   | 0   |                                |

|                     | 0010                            | 0 | )                   | 1                        | Х                  | Lost arbitration while attempt-                                                             | Abort failed transfer.                                     | 0          | 0   | Х   | —                              |

| ditic               |                                 |   |                     |                          |                    | ing a repeated START.                                                                       | Reschedule failed transfer.                                | 1          | 0   | Х   | 1110                           |

| Con                 | 0001                            | 0 | )                   | 1                        | Х                  | Lost arbitration due to a                                                                   | Abort failed transfer.                                     | 0          | 0   | Х   | —                              |

| Bus Error Condition |                                 |   |                     |                          |                    | detected STOP.                                                                              | Reschedule failed transfer.                                | 1          | 0   | Х   | 1110                           |

| sЦ                  | 0000                            | 1 |                     | 1                        | Х                  | Lost arbitration while transmit-                                                            | Abort failed transfer.                                     | 0          | 0   | 0   | —                              |

| Bu                  |                                 |   |                     |                          |                    | ting a data byte as master.                                                                 | Reschedule failed transfer.                                | 1          | 0   | 0   | 1110                           |

## Table 23.4. SMBus Status Decoding

## SFR Definition 24.5. SBRLH0: UART0 Baud Rate Generator Reload High Byte

| Bit     | 7                                   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-------------------------------------|---|---|---|---|---|---|---|--|--|

| Name    | SBRLH0[7:0]                         |   |   |   |   |   |   |   |  |  |

| Туре    | R/W                                 |   |   |   |   |   |   |   |  |  |

| Reset   | et 0 0 0 0 0 0 0 0                  |   |   |   |   |   |   | 0 |  |  |

| SFR Add | SFR Address = 0xAD; SFR Page = 0x0F |   |   |   |   |   |   |   |  |  |

| Bit | Name        | Function                                                                                                                   |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SBRLH0[7:0] | High Byte of Reload Value for UART0 Baud Rate Generator.                                                                   |

|     |             | This value is loaded into the high byte of the UART0 baud rate generator when the counter overflows from 0xFFFF to 0x0000. |

## SFR Definition 24.6. SBRLL0: UART0 Baud Rate Generator Reload Low Byte

| Bit              | 7             | 6                                                                                                                         | 5        | 4 | 3 | 2 | 1 | 0 |  |  |

|------------------|---------------|---------------------------------------------------------------------------------------------------------------------------|----------|---|---|---|---|---|--|--|

| Name SBRLL0[7:0] |               |                                                                                                                           |          |   |   |   |   |   |  |  |

| Туре             | Type R/W      |                                                                                                                           |          |   |   |   |   |   |  |  |

| Rese             | et 0          | 0                                                                                                                         | 0        | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR A            | Address = 0xA | C; SFR Page                                                                                                               | e = 0x0F |   |   |   |   |   |  |  |

| Bit              | Name          | Function                                                                                                                  |          |   |   |   |   |   |  |  |

| 7:0              | SBRLL0[7:0]   | BRLL0[7:0] Low Byte of Reload Value for UART0 Baud Rate Generator.                                                        |          |   |   |   |   |   |  |  |

|                  |               | This value is loaded into the low byte of the UART0 baud rate generator when the counter overflows from 0xFFFF to 0x0000. |          |   |   |   |   |   |  |  |

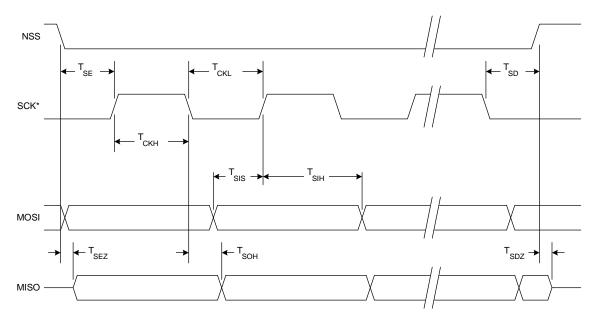

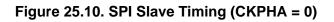

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

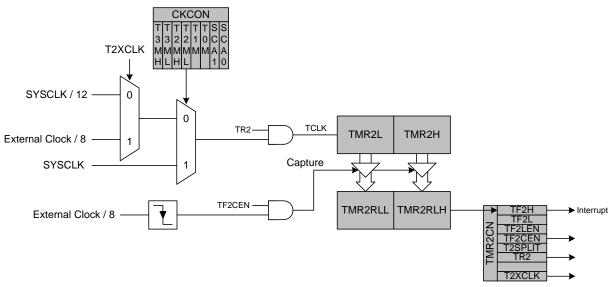

Figure 26.6. Timer 2 External Oscillator Capture Mode Block Diagram

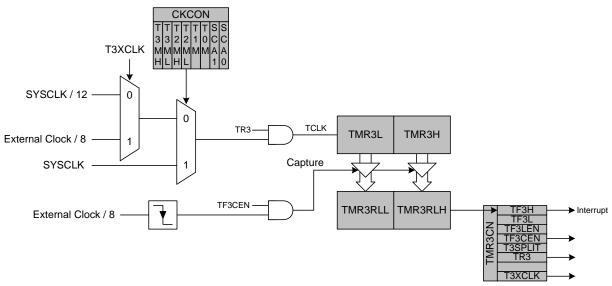

Figure 26.9. Timer 3 External Oscillator Capture Mode Block Diagram