#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 4.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 25x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-LQFP                                                        |

| Supplier Device Package    | 32-LQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f503-iq |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 5.12. Comparator 0 and Comparator 1 Electrical Characteristics

VIO = 1.8 to 5.125 V, -40 to +125 °C unless otherwise noted.

| Parameter                                         | Conditions             | Min   | Тур  | Max                    | Units |

|---------------------------------------------------|------------------------|-------|------|------------------------|-------|

| Response Time:                                    | CPn+ – CPn– = 100 mV   | _     | 310  | —                      | ns    |

| Mode 0, Vcm <sup>*</sup> = 1.5 V                  | CPn+-CPn-=-100 mV      | _     | 340  | —                      | ns    |

| Response Time:                                    | CPn+ – CPn– = 100 mV   | _     | 410  | —                      | ns    |

| Mode 1, Vcm <sup>*</sup> = 1.5 V                  | CPn+-CPn-=-100 mV      | _     | 510  | —                      | ns    |

| Response Time:                                    | CPn+ – CPn– = 100 mV   | _     | 480  | —                      | ns    |

| Mode 2, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV  | _     | 620  | —                      | ns    |

| Response Time:                                    | CPn+ – CPn– = 100 mV   | _     | 1600 | —                      | ns    |

| Mode 3, Vcm <sup>*</sup> = 1.5 V                  | CPn+ - CPn- = -100 mV  | _     | 2600 | —                      | ns    |

| Common-Mode Rejection Ratio                       |                        | _     | 1.7  | 8.9                    | mV/V  |

| Positive Hysteresis 1                             | CPnHYP1–0 = 00         | -2    | 0    | 2                      | mV    |

| Positive Hysteresis 2                             | CPnHYP1–0 = 01         | 2     | 6    | 10                     | mV    |

| Positive Hysteresis 3                             | CPnHYP1–0 = 10         | 5     | 11   | 20                     | mV    |

| Positive Hysteresis 4                             | CPnHYP1–0 = 11         | 13    | 21   | 40                     | mV    |

| Negative Hysteresis 1                             | CPnHYN1-0 = 00         | -2    | 0    | 2                      | mV    |

| Negative Hysteresis 2                             | CPnHYN1-0 = 01         | 2     | 6    | 10                     | mV    |

| Negative Hysteresis 3                             | CPnHYN1–0 = 10         | 5     | 11   | 20                     | mV    |

| Negative Hysteresis 4                             | CPnHYN1–0 = 11         | 13    | 21   | 40                     | mV    |

| Inverting or Non-Inverting Input<br>Voltage Range |                        | -0.25 | _    | V <sub>IO</sub> + 0.25 | V     |

| Input Capacitance                                 |                        | _     | 8    | —                      | pF    |

| Input Offset Voltage                              |                        | -10   |      | +10                    | mV    |

| Power Supply                                      | ·                      |       |      |                        |       |

| Power Supply Rejection                            |                        |       | 0.33 | —                      | mV/V  |

| Power-Up Time                                     |                        | _     | 3    | —                      | μs    |

|                                                   | Mode 0                 |       | 6.2  | 20                     | μA    |

| Supply Current at DC                              | Mode 1                 |       | 3.8  | 10                     | μA    |

| Supply Current at DC                              | Mode 2                 |       | 2.6  | 7.5                    | μA    |

|                                                   | Mode 3                 | —     | 0.6  | 3                      | μA    |

| *Note: Vcm is the common-mode vo                  | bltage on CP0+ and CP0 |       |      |                        |       |

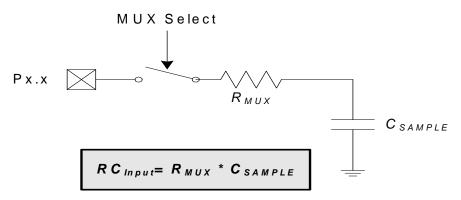

Figure 6.5. ADC0 Equivalent Input Circuit

## 6.3. Selectable Gain

ADC0 on the C8051F50x/F51x family of devices implements a selectable gain adjustment option. By writing a value to the gain adjust address range, the user can select gain values between 0 and 1.016.

For example, three analog sources to be measured have full-scale outputs of 5.0 V, 4.0 V, and 3.0 V, respectively. Each ADC measurement would ideally use the full dynamic range of the ADC with an internal voltage reference of 1.5 V or 2.2 V (set to 2.2 V for this example). When selecting the first source (5.0 V full-scale), a gain value of 0.44 (5 V full scale x 0.44 = 2.2 V full scale) provides a full-scale signal of 2.2 V when the input signal is 5.0 V. Likewise, a gain value of 0.55 (4 V full scale x 0.55 = 2.2 V full scale) for the second source and 0.73 (3 V full scale x 0.73 = 2.2 V full scale) for the third source provide full-scale ADC0 measurements when the input signal is full-scale.

Additionally, some sensors or other input sources have small part-to-part variations that must be accounted for to achieve accurate results. In this case, the programmable gain value could be used as a calibration value to eliminate these part-to-part variations.

#### 6.3.1. Calculating the Gain Value

The ADC0 selectable gain feature is controlled by 13 bits in three registers. ADC0GNH contains the 8 upper bits of the gain value and ADC0GNL contains the 4 lower bits of the gain value. The final GAINADD bit (ADC0GNA.0) controls an optional extra 1/64 (0.016) of gain that can be added in addition to the ADC0GNH and ADC0GNL gain. The ADC0GNA.0 bit is set to 1 after a power-on reset.

The equivalent gain for the ADC0GNH, ADC0GNL and ADC0GNA registers is as follows:

gain =

$$\left(\frac{\text{GAIN}}{4096}\right)$$

+ GAINADD ×  $\left(\frac{1}{64}\right)$

#### Equation 6.2. Equivalent Gain from the ADC0GNH and ADC0GNL Registers

Where:

*GAIN* is the 12-bit word of ADC0GNH[7:0] and ADC0GNL[7:4] *GAINADD* is the value of the GAINADD bit (ADC0GNA.0) *gain* is the equivalent gain value from 0 to 1.016

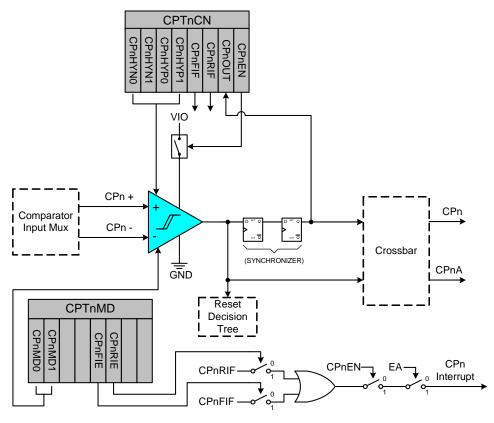

# 9. Comparators

The C8051F50x/F51x devices include two on-chip programmable voltage Comparators. A block diagram of the comparators is shown in Figure 9.1, where "n" is the comparator number (0 or 1). The two Comparators operate identically except that Comparator0 can also be used a reset source. For input selection details, refer to SFR Definition 9.5 and SFR Definition 9.6.

Each Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0, CP1), or an asynchronous "raw" output (CP0A, CP1A). The asynchronous signal is available even when the system clock is not active. This allows the Comparators to operate and generate an output with the device in STOP mode. When assigned to a Port pin, the Comparator outputs may be configured as open drain or push-pull (see Section "20.4. Port I/O Initialization" on page 182). Comparator0 may also be used as a reset source (see Section "17.5. Comparator0 Reset" on page 145).

The Comparator0 inputs are selected in the CPT0MX register (SFR Definition 9.5). The CMX0P1-CMX0P0 bits select the Comparator0 positive input; the CMX0N1-CMX0N0 bits select the Comparator0 negative input. The Comparator1 inputs are selected in the CPT1MX register (SFR Definition 9.6). The CMX1P1-CMX1P0 bits select the Comparator1 positive input; the CMX1N1-CMX1N0 bits select the Comparator1 negative input.

**Important Note About Comparator Inputs:** The Port pins selected as Comparator inputs should be configured as analog inputs in their associated Port configuration register, and configured to be skipped by the Crossbar (for details on Port configuration, see Section "20.1. Port I/O Modes of Operation" on page 178).

Figure 9.1. Comparator Functional Block Diagram

# C8051F50x/F51x

# SFR Definition 9.5. CPT0MX: Comparator0 MUX Selection

| Bit   | 7            | 6           | 5           | 4         | 3          | 2 | 1 | 0 |  |

|-------|--------------|-------------|-------------|-----------|------------|---|---|---|--|

| Name  |              | CMX0        | N[3:0]      |           | CMX0P[3:0] |   |   |   |  |

| Туре  | <b>;</b>     | R/          | W           |           | R/W        |   |   |   |  |

| Rese  | et 0         | 1           | 1           | 1         | 0          | 1 | 1 | 1 |  |

| SFR A | ddress = 0x9 | C; SFR Page | e = 0x00    |           |            |   |   |   |  |

| Bit   | Name         |             |             |           | Function   |   |   |   |  |

| 7:4   | CMX0N[3:0]   | Comparato   | r0 Negative | Input MUX | Selection. |   |   |   |  |

|       |              | 0000:       | P0.         | 1         |            |   |   |   |  |

|       |              | 0001:       | P0.3        | 3         |            |   |   |   |  |

|       |              | 0010:       | P0.         | 5         |            |   |   |   |  |

|       |              | 0011:       | P0.         | 7         |            |   |   |   |  |

|       |              | 0100:       | P1.         | 1         |            |   |   |   |  |

|       |              | 0101:       | P1.3        | 3         |            |   |   |   |  |

|       |              | 0110:       | P1.         | 5         |            |   |   |   |  |

|       |              | 0111:       | P1.         | 7         |            |   |   |   |  |

|       |              | 1000:       | P2.         | 1         |            |   |   |   |  |

|       |              | 1001:       | P2.3        | 3         |            |   |   |   |  |

|       |              | 1010:       | P2.         | 5         |            |   |   |   |  |

|       |              | 1011:       | P2.         | 7         |            |   |   |   |  |

|       |              | 1100–1111:  | Nor         | ne        |            |   |   |   |  |

| 3:0   | CMX0P[3:0]   | Comparato   | r0 Positive | Input MUX | Selection. |   |   |   |  |

|       |              | 0000:       | P0.         | 0         |            |   |   |   |  |

|       |              | 0001:       | P0.2        | 2         |            |   |   |   |  |

|       |              | 0010:       | P0.4        | 4         |            |   |   |   |  |

|       |              | 0011:       | P0.         | 6         |            |   |   |   |  |

|       |              | 0100:       | P1.0        | 0         |            |   |   |   |  |

|       |              | 0101:       | P1.:        | 2         |            |   |   |   |  |

|       |              | 0110:       | P1.4        | 4         |            |   |   |   |  |

|       |              | 0111:       | P1.         | 6         |            |   |   |   |  |

|       |              | 1000:       | P2.         | 0         |            |   |   |   |  |

|       |              | 1001:       | P2.2        | 2         |            |   |   |   |  |

|       |              | 1010:       | P2.4        | 4         |            |   |   |   |  |

|       |              | 1011:       | P2.         | 6         |            |   |   |   |  |

|       |              | 1100–1111:  | Nor         | ne        |            |   |   |   |  |

# 11.4. Serial Number Special Function Registers (SFRs)

The C8051F50x/F51x devices include four SFRs, SN0 through SN3, that are pre-programmed during production with a unique, 32-bit serial number. The serial number provides a unique identification number for each device and can be read from the application firmware. If the serial number is not used in the application, these four registers can be used as general purpose SFRs.

# SFR Definition 11.7. SNn: Serial Number n

| Bit               | 7              | 6                                                                                                                                          | 5          | 4           | 3          | 2         | 1         | 0 |  |  |  |

|-------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|------------|-----------|-----------|---|--|--|--|

| Name SERNUMn[7:0] |                |                                                                                                                                            |            |             |            |           |           |   |  |  |  |

| Тур               | e              | R/W                                                                                                                                        |            |             |            |           |           |   |  |  |  |

| Rese              | et             | Varies—Unique 32-bit value                                                                                                                 |            |             |            |           |           |   |  |  |  |

| SFR /             | Addresses: SN0 | ) = 0xF9; SN                                                                                                                               | V1 = 0xFA; | SN2 = 0xFB; | SN3 = 0xFC | ; SFR Pag | e = 0x0F; |   |  |  |  |

| Bit               | Name           |                                                                                                                                            |            |             | Function   |           |           |   |  |  |  |

| 7:0               | SERNUMn[7:0    | ERNUMn[7:0] Serial Number Bits.                                                                                                            |            |             |            |           |           |   |  |  |  |

|                   |                | The four serial number registers form a 32-bit serial number, with SN3 as the most significant byte and SN0 as the least significant byte. |            |             |            |           |           |   |  |  |  |

# **13. Special Function Registers**

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the C8051F50x/F51x's resources and peripherals. The CIP-51 controller core duplicates the SFRs found in a typical 8051 implementation as well as implementing additional SFRs used to configure and access the sub-systems unique to the C8051F50x/F51x. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 13.3 lists the SFRs implemented in the C8051F50x/F51x device family.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g., P0, TCON, SCON0, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing unoccupied addresses in the SFR space will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the data sheet, as indicated in Table 13.3, for a detailed description of each register.

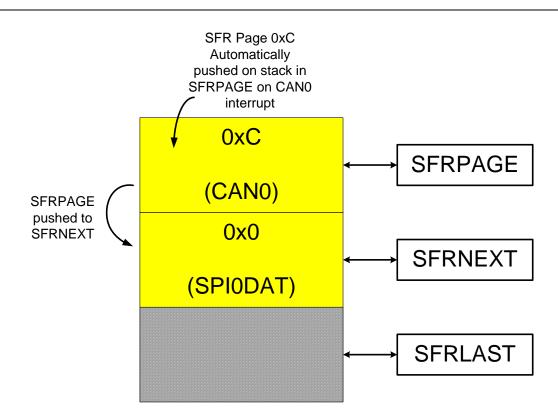

## 13.1. SFR Paging

The CIP-51 features SFR paging, allowing the device to map many SFRs into the 0x80 to 0xFF memory address space. The SFR memory space has 256 *pages*. In this way, each memory location from 0x80 to 0xFF can access up to 256 SFRs. The C8051F50x/F51x family of devices utilizes three SFR pages: 0x0, 0xC, and 0xF. SFR pages are selected using the Special Function Register Page Selection register, SFRP-AGE (see SFR Definition 11.3). The procedure for reading and writing an SFR is as follows:

- 1. Select the appropriate SFR page number using the SFRPAGE register.

- 2. Use direct accessing mode to read or write the special function register (MOV instruction).

### 13.2. Interrupts and SFR Paging

When an interrupt occurs, the SFR Page Register will automatically switch to the SFR page containing the flag bit that caused the interrupt. The automatic SFR Page switch function conveniently removes the burden of switching SFR pages from the interrupt service routine. Upon execution of the RETI instruction, the SFR page is automatically restored to the SFR Page in use prior to the interrupt. This is accomplished via a three-byte SFR Page Stack. The top byte of the stack is SFRPAGE, the current SFR Page. The second byte of the SFR Page Stack is SFRNEXT. The third, or bottom byte of the SFR Page Stack is SFRLAST. Upon an interrupt, the current SFRPAGE value is pushed to the SFRNEXT byte, and the value of SFRNEXT is pushed to SFRLAST. Hardware then loads SFRPAGE with the SFR Page containing the flag bit associated with the interrupt. On a return from interrupt, the SFR Page Stack is popped resulting in the value of SFRNEXT returning to the SFRPAGE register, thereby restoring the SFR page context without software intervention. The value in SFRLAST (0x00 if there is no SFR Page value in the bottom of the stack) of the stack is placed in SFRNEXT register. If desired, the values stored in SFRNEXT and SFR-LAST may be modified during an interrupt, enabling the CPU to return to a different SFR Page upon execution of the RETI instruction (on interrupt exit). Modifying registers in the SFR Page Stack does not cause a push or pop of the stack. Only interrupt calls and returns will cause push/pop operations on the SFR Page Stack.

On the C8051F50x/F51x devices, vectoring to an interrupt will switch SFRPAGE to page 0x00, except for the CAN0 interrupt which will switch SFRPAGE to page 0x0C.

Figure 13.3. SFR Page Stack After CAN0 Interrupt Occurs

While in the CAN0 ISR, a PCA interrupt occurs. Recall the PCA interrupt is configured as a high priority interrupt, while the CAN0 interrupt is configured as a *low* priority interrupt. Thus, the CIP-51 will now vector to the high priority PCA ISR. Upon doing so, the CIP-51 will automatically place the SFR page needed to access the PCA's special function registers into the SFRPAGE register, SFR Page 0x00. The value that was in the SFRPAGE register before the PCA interrupt (SFR Page 0x0C for CAN0) is pushed down the stack into SFRNEXT. Likewise, the value that was in the SFRNEXT register before the PCA interrupt (in this case SFR Page 0x00 for SPI0DAT) is pushed down to the SFRLAST register, the "bottom" of the stack. Note that a value stored in SFRLAST (via a previous software write to the SFRLAST register) will be overwritten. See Figure 13.4.

|    |                      |                     |                    | 5                  | , ,                |                    |                      |                        |

|----|----------------------|---------------------|--------------------|--------------------|--------------------|--------------------|----------------------|------------------------|

|    | 0(8)                 | 1(9)                | 2(A)               | 3(B)               | 4(C)               | 5(D)               | 6(E)                 | 7(F)                   |

| F8 |                      | _                   | CAN0IF2DA2L        | CAN0IF2DA2H        | CAN0IF2DB1L        | CAN0IF2DB1H        | CAN0IF2DB2L          | CAN0IF2DB2H            |

| F0 | B<br>(All Pages)     |                     | CAN0IF2A2L         | CAN0IF2A2H         |                    |                    | CAN0IF2DA1L          | CAN0IF2DA1H            |

| E8 |                      |                     | CAN0IF2M1L         | CAN0IF2M1H         | CAN0IF2M2L         | CAN0IF2M2H         | CAN0IF2A1L           | CAN0IF2A1H             |

| E0 | ACC<br>(All Pages)   |                     | CAN0IF2CML         | CAN0IF2CMH         |                    |                    | EIE1<br>(All Pages)  | EIE2<br>(All Pages)    |

| D8 |                      | <u> </u>            | CAN0IF1DB1L        | CAN0IF1DB1H        | CAN0IF1DB2L        | CAN0IF1DB2H        | CAN0IF2CRL           | CAN0IF2CRH             |

| D0 | PSW<br>(All Pages)   |                     | CAN0IF1MCL         | CAN0IF1MCH         | CAN0IF1DA1L        | CAN0IF1DA1H        | CAN0IF1DA2L          | CAN0IF1DA2H            |

| C8 |                      | <u> </u>            | CAN0IF1A1L         | CAN0IF1A1H         | CAN0IF1A2L         | CAN0IF1A2H         | CAN0IF2MCL           | CAN0IF2MCH             |

| C0 | CANOCN               |                     | CAN0IF1CML         | CAN0IF1CMH         | CAN0IF1M1L         | CAN0IF1M1H         | CAN0IF1M2L           | CAN0IF1M2H             |

| B8 | IP<br>(All Pages)    |                     | CAN0MV1L           | CAN0MV1H           | CAN0MV2L           | CAN0MV2H           | CAN0IF1CRL           | CAN0IF1CRH             |

| B0 | P3<br>(All Pages)    |                     | CAN0IP2L           | CAN0IP2H           |                    | P4<br>(All Pages)  | FLSCL<br>(All Pages) | FLKEY<br>(All Pages)   |

| A8 | IE<br>(All Pages)    |                     | CAN0ND1L           | CAN0ND1H           | CAN0ND2L           | CAN0ND2H           | CAN0IP1L             | CAN0IP1H               |

| A0 | P2<br>(All Pages)    | CAN0BRPE            | CAN0TR1L           | CAN0TR1H           | CAN0TR2L           | CAN0TR2H           |                      | SFRPAGE<br>(All Pages) |

| 98 | SCON0<br>(All Pages) |                     | CAN0BTL            | CAN0BTH            | CAN0IIDL           | CAN0IIDH           | CAN0TST              |                        |

| 90 | P1<br>(All Pages)    |                     | CAN0CFG            |                    | CAN0STAT           |                    | CAN0ERRL             | CAN0ERRH               |

| 88 | TCON<br>(All Pages)  | TMOD<br>(All Pages) | TL0<br>(All Pages) | TL1<br>(All Pages) | TH0<br>(All Pages) | TH1<br>(All Pages) | CKCON<br>(All Pages) |                        |

| 80 | P0                   | SP<br>(All Pages)   | (All Pages)        | (All Pages)        | 37                 | (All Pages)        | (All Pages)          | PCON<br>(All Pages)    |

|    | 0(8)                 | 1(9)                | 2(A)               | 3(B)               | 4(C)               | 5(D)               | 6(E)                 | 7(F)                   |

|    | (bit addres          |                     | ~ /                | - ( )              | x - 7              | - \ /              | - \ /                |                        |

# Table 13.2. Special Function Register (SFR) Memory Map for Page 0xC

# Table 13.3. Special Function Registers

| Register | Address | Description                              | Page |

|----------|---------|------------------------------------------|------|

| ACC      | 0xE0    | Accumulator                              | 94   |

| ADC0CF   | 0xBC    | ADC0 Configuration                       | 63   |

| ADC0CN   | 0xE8    | ADC0 Control                             | 65   |

| ADC0GTH  | 0xC4    | ADC0 Greater-Than Compare High           | 67   |

| ADC0GTL  | 0xC3    | ADC0 Greater-Than Compare Low            | 67   |

| ADC0H    | 0xBE    | ADC0 High                                | 64   |

| ADC0L    | 0xBD    | ADC0 Low                                 | 64   |

| ADC0LTH  | 0xC6    | ADC0 Less-Than Compare Word High         | 68   |

| ADC0LTL  | 0xC5    | ADC0 Less-Than Compare Word Low          | 68   |

| ADC0MX   | 0xBB    | ADC0 Mux Configuration                   | 71   |

| ADC0TK   | 0xBA    | ADC0 Tracking Mode Select                | 66   |

| В        | 0xF0    | B Register                               | 94   |

| CCH0CN   | 0xE3    | Cache Control                            | 137  |

| CKCON    | 0x8E    | Clock Control                            | 266  |

| CLKMUL   | 0x97    | Clock Multiplier                         | 171  |

| CLKSEL   | 0x8F    | Clock Select                             | 166  |

| CPT0CN   | 0x9A    | Comparator0 Control                      | 77   |

| CPT0MD   | 0x9B    | Comparator0 Mode Selection               | 78   |

| CPT0MX   | 0x9C    | Comparator0 MUX Selection                | 82   |

| CPT1CN   | 0x9D    | Comparator1 Control                      | 77   |

| CPT1MD   | 0x9E    | Comparator1 Mode Selection               | 78   |

| CPT1MX   | 0x9F    | Comparator1 MUX Selection                | 82   |

| DPH      | 0x83    | Data Pointer High                        | 93   |

| DPL      | 0x82    | Data Pointer Low                         | 93   |

| EIE1     | 0xE6    | Extended Interrupt Enable 1              | 123  |

| EIE2     | 0xE7    | Extended Interrupt Enable 2              | 123  |

| EIP1     | 0xF6    | Extended Interrupt Priority 1            | 124  |

| EIP2     | 0xF7    | Extended Interrupt Priority 2            | 125  |

| EMI0CF   | 0xB2    | External Memory Interface Configuration  | 152  |

| EMI0CN   | 0xAA    | External Memory Interface Control        | 151  |

| EMIOTC   | 0xAA    | External Memory Interface Timing Control | 157  |

| FLKEY    | 0xB7    | Flash Lock and Key                       | 135  |

| FLSCL    | 0xB6    | Flash Scale                              | 136  |

| IE       | 0xA8    | Interrupt Enable                         | 121  |

| IP       | 0xB8    | Interrupt Priority                       | 122  |

# SFR Definition 14.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7     | 6   | 5    | 4    | 3     | 2     | 1      | 0     |

|-------|-------|-----|------|------|-------|-------|--------|-------|

| Name  | ELIN0 | ET3 | ECP1 | ECP0 | EPCA0 | EADC0 | EWADC0 | ESMB0 |

| Туре  | R/W   | R/W | R/W  | R/W  | R/W   | R/W   | R/W    | R/W   |

| Reset | 0     | 0   | 0    | 0    | 0     | 0     | 0      | 0     |

### SFR Address = 0xE6; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                                                          |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ELIN0  | Enable LIN0 Interrupt.<br>This bit sets the masking of the LIN0 interrupt.<br>0: Disable LIN0 interrupts.<br>1: Enable interrupt requests generated by the LIN0INT flag.                                                                                                          |

| 6   | ET3    | <ul> <li>Enable Timer 3 Interrupt.</li> <li>This bit sets the masking of the Timer 3 interrupt.</li> <li>0: Disable Timer 3 interrupts.</li> <li>1: Enable interrupt requests generated by the TF3L or TF3H flags.</li> </ul>                                                     |

| 5   | ECP1   | <ul> <li>Enable Comparator1 (CP1) Interrupt.</li> <li>This bit sets the masking of the CP1 interrupt.</li> <li>0: Disable CP1 interrupts.</li> <li>1: Enable interrupt requests generated by the CP1RIF or CP1FIF flags.</li> </ul>                                               |

| 4   | ECP0   | <ul> <li>Enable Comparator0 (CP0) Interrupt.</li> <li>This bit sets the masking of the CP0 interrupt.</li> <li>0: Disable CP0 interrupts.</li> <li>1: Enable interrupt requests generated by the CP0RIF or CP0FIF flags.</li> </ul>                                               |

| 3   | EPCA0  | <ul> <li>Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> </ul>                                              |

| 2   | EADC0  | <ul> <li>Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> </ul>          |

| 1   | EWADC0 | <ul> <li>Enable Window Comparison ADC0 Interrupt.</li> <li>This bit sets the masking of ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).</li> </ul> |

| 0   | ESMB0  | Enable SMBus (SMB0) Interrupt.<br>This bit sets the masking of the SMB0 interrupt.<br>0: Disable all SMB0 interrupts.<br>1: Enable interrupt requests generated by SMB0.                                                                                                          |

# SFR Definition 17.1. VDM0CN: V<sub>DD</sub> Monitor Control

| Bit   | 7      | 6       | 5      | 4 | 3 | 2 | 1 | 0 |

|-------|--------|---------|--------|---|---|---|---|---|

| Name  | VDMEN  | VDDSTAT | VDMLVL |   |   |   |   |   |

| Туре  | R/W    | R       | R/W    | R | R | R | R | R |

| Reset | Varies | Varies  | 0      | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xFF; SFR Page = 0x00

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN   | V <sub>DD</sub> Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |         | This bit turns the V <sub>DD</sub> monitor circuit on/off. The V <sub>DD</sub> Monitor cannot generate system resets until it is also selected as a reset source in register RSTSRC (SFR Definition 17.2). Selecting the V <sub>DD</sub> monitor as a reset source before it has stabilized may generate a system reset. In systems where this reset would be undesirable, a delay should be introduced between enabling the V <sub>DD</sub> Monitor and selecting it as a reset source. See Table 5.4 for the minimum V <sub>DD</sub> Monitor turn-on time.<br>0: V <sub>DD</sub> Monitor Disabled.<br>1: V <sub>DD</sub> Monitor Enabled. |

| 6   | VDDSTAT | V <sub>DD</sub> Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |         | This bit indicates the current power supply status ( $V_{DD}$ Monitor output).<br>0: $V_{DD}$ is at or below the $V_{DD}$ monitor threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |         | 1: V <sub>DD</sub> is above the V <sub>DD</sub> monitor threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5   | VDMLVL  | V <sub>DD</sub> Monitor Level Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |         | 0: $V_{DD}$ Monitor Threshold is set to VRST-LOW<br>1: $V_{DD}$ Monitor Threshold is set to VRST-HIGH. This setting is required for any system includes code that writes to and/or erases Flash.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4:0 | Unused  | Read = 00000b; Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# 17.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 5.4 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

# 17.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than the value specified in Table 5.4, "Reset Electrical Characteristics," on page 46, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

# SFR Definition 17.2. RSTSRC: Reset Source

| Bit   | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| Name  |   | FERROR | CORSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | 0 | Varies |

SFR Address = 0xEF; SFR Page = 0x00

| Bit   | Name       | Description                                                                                  | Write                                                                                                                                                                | Read                                                                                                                                           |

|-------|------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Unused     | Unused.                                                                                      | Don't care.                                                                                                                                                          | 0                                                                                                                                              |

| 6     | FERROR     | Flash Error Reset Flag.                                                                      | N/A                                                                                                                                                                  | Set to 1 if Flash<br>read/write/erase error<br>caused the last reset.                                                                          |

| 5     | CORSEF     | Comparator0 Reset Enable<br>and Flag.                                                        | Writing a 1 enables<br>Comparator0 as a reset<br>source (active-low).                                                                                                | Set to 1 if Comparator0 caused the last reset.                                                                                                 |

| 4     | SWRSF      | Software Reset Force and Flag.                                                               | Writing a 1 forces a sys-<br>tem reset.                                                                                                                              | Set to 1 if last reset was<br>caused by a write to<br>SWRSF.                                                                                   |

| 3     | WDTRSF     | Watchdog Timer Reset Flag.                                                                   | N/A                                                                                                                                                                  | Set to 1 if Watchdog Timer overflow caused the last reset.                                                                                     |

| 2     | MCDRSF     | Missing Clock Detector<br>Enable and Flag.                                                   | Writing a 1 enables the<br>Missing Clock Detector.<br>The MCD triggers a reset<br>if a missing clock condition<br>is detected.                                       | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                                                                        |

| 1     | PORSF      | Power-On/V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | Writing a 1 enables the $V_{DD}$ monitor as a reset source.<br>Writing 1 to this bit before the $V_{DD}$ monitor is enabled and stabilized may cause a system reset. | Set to 1 anytime a power-<br>on or V <sub>DD</sub> monitor reset<br>occurs.<br>When set to 1 all other<br>RSTSRC flags are inde-<br>terminate. |

| 0     | PINRSF     | HW Pin Reset Flag.                                                                           | N/A                                                                                                                                                                  | Set to 1 if $\overline{RST}$ pin caused the last reset.                                                                                        |

| Note: | Do not use | read-modify-write operations on this                                                         | s register                                                                                                                                                           | 1                                                                                                                                              |

# 18.2. Configuring the External Memory Interface

Configuring the External Memory Interface consists of five steps:

- 1. Configure the Output Modes of the associated port pins as either push-pull or open-drain (push-pull is most common), and skip the associated pins in the crossbar.

- 2. Configure Port latches to "park" the EMIF pins in a dormant state (usually by setting them to logic 1).

- 3. Select Multiplexed mode or Non-multiplexed mode.

- 4. Select the memory mode (on-chip only, split mode without bank select, split mode with bank select, or off-chip only).

- 5. Set up timing to interface with off-chip memory or peripherals.

Each of these five steps is explained in detail in the following sections. The Port selection, Multiplexed mode selection, and Mode bits are located in the EMI0CF register shown in SFR Definition .

### 18.3. Port Configuration

The External Memory Interface appears on Ports 1, 2, 3, and 4 when it is used for off-chip memory access. When the EMIF is used, the Crossbar should be configured to skip over the /RD control line (P1.6) and the /WR control line (P1.7) using the P1SKIP register. When the EMIF is used in multiplexed mode, the Crossbar should also skip over the ALE control line (P1.5). For more information about configuring the Crossbar, see Section "20.6. Special Function Registers for Accessing and Configuring Port I/O" on page 191. The EMIF pinout is shown in Table 18.1 on page 149.

The External Memory Interface claims the associated Port pins for memory operations ONLY during the execution of an off-chip MOVX instruction. Once the MOVX instruction has completed, control of the Port pins reverts to the Port latches or to the Crossbar settings for those pins. See Section "20. Port Input/Output" on page 177 for more information about the Crossbar and Port operation and configuration. **The Port latches should be explicitly configured to "park" the External Memory Interface pins in a dormant state, most commonly by setting them to a logic 1**.

During the execution of the MOVX instruction, the External Memory Interface will explicitly disable the drivers on all Port pins that are acting as Inputs (Data[7:0] during a READ operation, for example). The Output mode of the Port pins (whether the pin is configured as Open-Drain or Push-Pull) is unaffected by the External Memory Interface operation, and remains controlled by the PnMDOUT registers. In most cases, the output modes of all EMIF pins should be configured for push-pull mode.

The C8051F500/1/4/5 devices support both the multiplexed and non-multiplexed modes and the C8051F508/9-F510/1 devices support only multiplexed modes. Accessing off-chip memory is not supported by the C8051F502/3/6/7 devices.

148

# C8051F50x/F51x

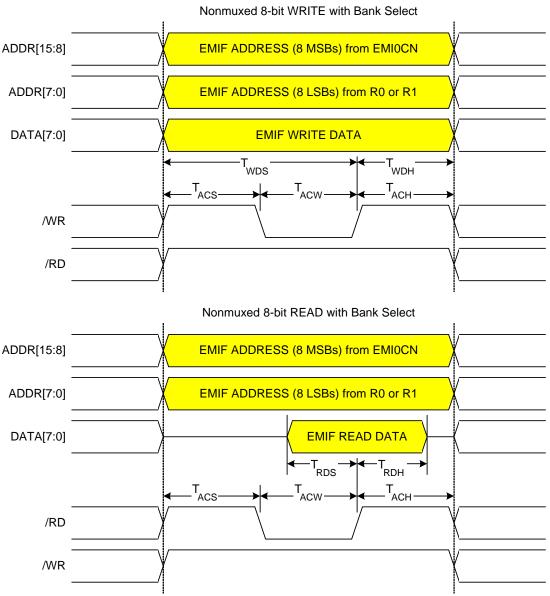

#### 18.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110

Figure 18.6. Non-multiplexed 8-bit MOVX with Bank Select Timing

# C8051F50x/F51x

# SFR Definition 19.2. OSCICN: Internal Oscillator Control

| Bit   | 7           | 6   | 5       | 4     | 3        | 2         | 1 | 0 |

|-------|-------------|-----|---------|-------|----------|-----------|---|---|

| Name  | IOSCEN[1:0] |     | SUSPEND | IFRDY | Reserved | IFCN[2:0] |   |   |

| Туре  | R/W         | R/W | R/W     | R     | R        | R/W       |   |   |

| Reset | 1           | 1   | 0       | 1     | 0        | 0         | 0 | 0 |

### SFR Address = 0xA1; SFR Page = 0x0F;

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | IOSCEN[1:0] | Internal Oscillator Enable Bits.<br>00: Oscillator Disabled.<br>01: Reserved.<br>10: Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |             | 11: Oscillator enabled in normal mode and disabled in suspend mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5   | SUSPEND     | Internal Oscillator Suspend Enable Bit.<br>Setting this bit to logic 1 places the internal oscillator in SUSPEND mode. The inter-<br>nal oscillator resumes operation when one of the SUSPEND mode awakening<br>events occurs.                                                                                                                                                                                                                                                                                                                                           |

| 4   | IFRDY       | Internal Oscillator Frequency Ready Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |             | <ul><li>0: Internal oscillator is not running at programmed frequency.</li><li>1: Internal oscillator is running at programmed frequency.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3   | Reserved    | Read = 0b; Must Write = 0b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2:0 | IFCN[2:0]   | Internal Oscillator Frequency Divider Control Bits.<br>000: SYSCLK derived from Internal Oscillator divided by 128.<br>001: SYSCLK derived from Internal Oscillator divided by 64.<br>010: SYSCLK derived from Internal Oscillator divided by 32.<br>011: SYSCLK derived from Internal Oscillator divided by 16.<br>100: SYSCLK derived from Internal Oscillator divided by 8.<br>101: SYSCLK derived from Internal Oscillator divided by 4.<br>110: SYSCLK derived from Internal Oscillator divided by 2.<br>111: SYSCLK derived from Internal Oscillator divided by 1. |

## 20.5. Port Match

Port match functionality allows system events to be triggered by a logic value change on P0, P1, P2 or P3. A software controlled value stored in the PnMATCH registers specifies the expected or normal logic values of P0, P1, P2, and P3. A Port mismatch event occurs if the logic levels of the Port's input pins no longer match the software controlled value. This allows Software to be notified if a certain change or pattern occurs on P0, P1, P2, or P3 input pins regardless of the XBRn settings.

The PnMASK registers can be used to individually select which of the port pins should be compared against the PnMATCH registers. A Port mismatch event is generated if (Pn & PnMASK) does not equal (PnMATCH & PnMASK), where n is 0, 1, 2 or 3

A Port mismatch event may be used to generate an interrupt or wake the device from a low power mode, such as IDLE or SUSPEND. See the Interrupts and Power Options chapters for more details on interrupt and wake-up sources.

| Bit   | 7              | 6          | 5                 | 4 | 3 | 2 | 1 | 0 |

|-------|----------------|------------|-------------------|---|---|---|---|---|

| Nam   | POMAŠK[7:0]    |            |                   |   |   |   |   |   |

| Туре  | Type R/W       |            |                   |   |   |   |   |   |

| Rese  | et 0           | 0          | 0                 | 0 | 0 | 0 | 0 | 0 |

| SFR A | Address = 0xF2 | ; SFR Page | $e = 0 \times 00$ |   |   |   |   |   |

| Bit   | Name           |            | Function          |   |   |   |   |   |

| 7:0   | P0MASK[7:0]    | Port 0 M   | ask Value.        |   |   |   |   |   |

#### SFR Definition 20.4. P0MASK: Port 0 Mask Register

| P0MASK[7:0] | Port 0 Mask Value.                                                         |

|-------------|----------------------------------------------------------------------------|

|             | Selects P0 pins to be compared to the corresponding bits in P0MAT.         |

|             | 0: P0.n pin logic value is ignored and cannot cause a Port Mismatch event. |

|             | 1: P0.n pin logic value is compared to P0MAT.n.                            |

## SFR Definition 20.5. P0MAT: Port 0 Match Register

| Bit   | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|-----|---|---|---|---|---|---|--|--|

| Name  | POMAT[7:0] |     |   |   |   |   |   |   |  |  |

| Туре  |            | R/W |   |   |   |   |   |   |  |  |

| Reset | 1          | 1   | 1 | 1 | 1 | 1 | 1 | 1 |  |  |

SFR Address = 0xF1; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                                                                   |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MAT[7:0] | Port 0 Match Value.                                                                                                                                                                        |

|     |            | Match comparison value used on Port 0 for bits in P0MAT which are set to 1.<br>0: P0.n pin logic value is compared with logic LOW.<br>1: P0.n pin logic value is compared with logic HIGH. |

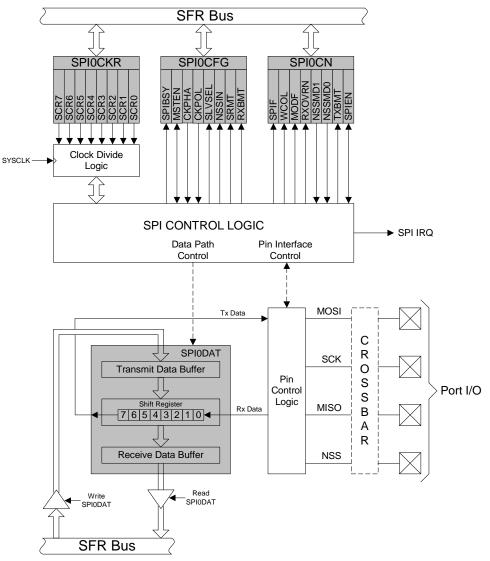

# 25. Enhanced Serial Peripheral Interface (SPI0)

The Enhanced Serial Peripheral Interface (SPI0) provides access to a flexible, full-duplex synchronous serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

# 28. C2 Interface

C8051F50x/F51x devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow Flash programming and in-system debugging with the production part installed in the end application. The C2 interface uses a clock signal (C2CK) and a bi-directional C2 data signal (C2D) to transfer information between the device and a host system. See the C2 Interface Specification for details on the C2 protocol.

## 28.1. C2 Interface Registers

The following describes the C2 registers necessary to perform Flash programming through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

# C2 Register Definition 28.1. C2ADD: C2 Address

| Bit   | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|-----|---|---|---|---|---|---|--|--|

| Name  | C2ADD[7:0] |     |   |   |   |   |   |   |  |  |

| Туре  |            | R/W |   |   |   |   |   |   |  |  |

| Reset | 0          | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| Bit | Name       |             | Function                                                                                                                                                 |  |  |  |  |  |

|-----|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0 | C2ADD[7:0] | C2 Address. | <b>2 Address.</b><br>The C2ADD register is accessed via the C2 interface to select the target Data register<br>for C2 Data Read and Data Write commands. |  |  |  |  |  |

|     |            | •           |                                                                                                                                                          |  |  |  |  |  |

|     |            | Address     | Description                                                                                                                                              |  |  |  |  |  |

|     |            | 0x00        | Selects the Device ID register for Data Read instructions                                                                                                |  |  |  |  |  |

|     |            | 0x01        | Selects the Revision ID register for Data Read instructions                                                                                              |  |  |  |  |  |

|     |            | 0x02        | Selects the C2 Flash Programming Control register for Data<br>Read/Write instructions                                                                    |  |  |  |  |  |

|     |            | 0xB4        | Selects the C2 Flash Programming Data register for Data Read/Write instructions                                                                          |  |  |  |  |  |

# C8051F50x/F51x

# C2 Register Definition 28.2. DEVICEID: C2 Device ID

| Bit                | 7            | 6           | 5              | 4              | 3              | 2             | 1           | 0     |  |  |

|--------------------|--------------|-------------|----------------|----------------|----------------|---------------|-------------|-------|--|--|

| Name DEVICEID[7:0] |              |             |                |                |                |               |             |       |  |  |

| Туре               | R/W          |             |                |                |                |               |             |       |  |  |

| Rese               | et O         | 0           | 0              | 1              | 0              | 1             | 0           | 0     |  |  |

| C2 Ad              | dress: 0xFD; | SFR Addres  | s = 0xFD; SF   | R Page = 0     | k0F            |               |             |       |  |  |

| Bit                | Name         |             |                |                | Function       |               |             |       |  |  |

| 7:0                | DEVICEID[7   | 0] Device I | Device ID.     |                |                |               |             |       |  |  |

|                    |              | This read   | d-only registe | er returns the | e 8-bit device | e ID: 0x1C (0 | C8051F50x/F | 51x). |  |  |

# C2 Register Definition 28.3. REVID: C2 Revision ID

| Bit             | 7                | 6                  | 5               | 4             | 3              | 2           | 1             | 0           |  |  |

|-----------------|------------------|--------------------|-----------------|---------------|----------------|-------------|---------------|-------------|--|--|

| Name REVID[7:0] |                  |                    |                 |               |                |             |               |             |  |  |

| Туре            | Type         R/W |                    |                 |               |                |             |               |             |  |  |

| Rese            | t Varies         | Varies             | Varies          | Varies        | Varies         | Varies      | Varies        | Varies      |  |  |

| C2 Ac           | ldress: 0xFE;    | SFR Address        | s = 0xFE; SF    | R Page = 0    | k0F            |             |               |             |  |  |

| Bit             | Name             |                    |                 |               | Function       |             |               |             |  |  |

| 7:0             | REVID[7:0]       | <b>Revision ID</b> | Revision ID.    |               |                |             |               |             |  |  |

|                 |                  | This read-or       | nly register re | eturns the 8- | bit revision I | D. For exam | ple: 0x00 = I | Revision A. |  |  |

# **DOCUMENT CHANGE LIST**

# **Revision 0.2 to Revision 1.0**

- Added documentation for 40-pin QFN devices in all relevant chapters.

- Change oscillator specification for devices initially specified to have ±1.0% oscillators. All devices are now rated for ±0.5% across operating voltage and temperature.

- Removed all content from "1. System Overview" after block diagrams.

- Updated "5. Electrical Characteristics"—Updated various specifications and filled in all TBD values for all specifications.

- Updated "Table 5.11. Voltage Reference Electrical Characteristics"—Changed Minimum external reference input voltage from 0 V to 1 V.

- Updated "9. Comparators"—Fixed incorrect references to SFR Definitions 7.x.

- Updated "Table 13.1"—Added SFRs SN0, SN1, SN2, and SN3 to SFR map.

- Updated "SFR Definition 19.2" (OSCICN) Removed errant row for Bit 6. Also, Bit 3 definition changed to a Reserved bit from an Unused bit.

- Updated "20. Port Input/Output"—Added Port 4 to the crossbar diagrams and documentation.

- Updated "27.4. Watchdog Timer Mode"—Fixed incorrect references from Module 2 as the watchdog module to Module 5.

# **Revision 1.0 to Revision 1.1**

- Updated "Ordering Information" on page 20 and Table 2.1, "Product Selection Guide," on page 21 to include -A (Automotive) devices and automotive qualification information.

- Updated supply current related specifications throughout "5. Electrical Characteristics".

- Updated SFR Definition 8.1 to change VREF high setting to 2.20 V from 2.25 V.

- Updated Table 5.12 on page 51 and Figure 9.1 on page 75 to indicate that Comparators are powered from V<sub>IO</sub> and not V<sub>DDA</sub>.

- Updated Table 5.12 on page 51 to fix Comparator Supply Current Typical values for Modes 2 and 3.

- Updated the Gain Table in "6.3.1. Calculating the Gain Value" to fix the ADC0GNH Value in the last row.

- Updated Table 11.1 on page 89 with correct timing for all branch instructions, MOVC, and CPL A.

- Updated "15.1. Programming the Flash Memory" to clarify behavior of 8-bit MOVX instructions and when writing/erasing Flash.

- Updated SFR Definition 15.3 to include FLEWT bit definition. This bit must be set before writing or erasing Flash. Also updated Table 5.5 to reflect new Flash Write and Erase timing.

- Updated "17.7. Flash Error Reset" with an additional cause of a Flash Error reset.

- Updated "20.1.3. Interfacing Port I/O in a Multi-Voltage System" to remove note regarding interfacing to voltages above VIO.

- Updated "23. SMBus" to remove all hardware ACK features, including SMB0ADM and SMB0ADR SFRs.

- Updated "24.3.2. Data Reception" to clarify UART receive FIFO behavior.

- Updated SFR Definition 24.1 for SCON0 to correct SFR Page to 0x00 from All Pages.

**Note:** All items from the C8051F50x-F51x Errata dated July 1, 2009 are incorporated into this data sheet.