# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | 8051                                                                      |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 50MHz                                                                     |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), CANbus, LINbus, SPI, UART/USART |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                                |

| Number of I/O              | 40                                                                        |

| Program Memory Size        | 32КВ (32К х 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 4.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                              |

| Data Converters            | A/D 32x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 48-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 48-QFN (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f504-imr           |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                  | 005 |

|------------------------------------------------------------------|-----|

| Table 21.3. Autobaud Parameters Examples                         | 205 |

| Table 21.4. LIN Registers (Indirectly Addressable)               | 210 |

| Table 22.1. Background System Information                        | 220 |

| Table 22.2. Standard CAN Registers and Reset Values              | 223 |

| Table 23.1. SMBus Clock Source Selection                         | 230 |

| Table 23.2. Minimum SDA Setup and Hold Times                     | 231 |

| Table 23.3. Sources for Hardware Changes to SMB0CN               | 235 |

| Table 23.4. SMBus Status Decoding                                | 241 |

| Table 24.1. Baud Rate Generator Settings for Standard Baud Rates | 244 |

| Table 25.1. SPI Slave Timing Parameters                          | 264 |

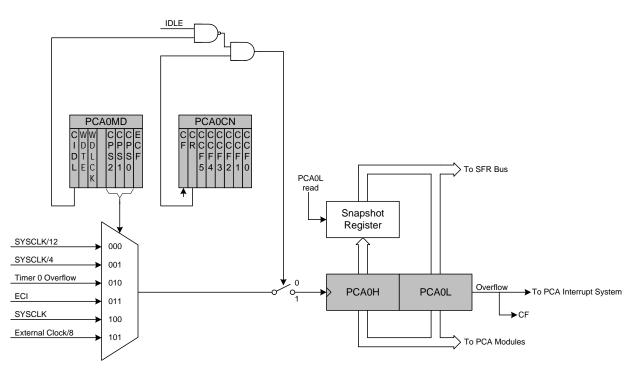

| Table 27.1. PCA Timebase Input Options                           | 288 |

| Table 27.2. PCA0CPM and PCA0PWM Bit Settings for                 |     |

| PCA Capture/Compare Modules                                      | 290 |

| Table 27.3. Watchdog Timer Timeout Intervals1                    | 299 |

#### Table 5.6. Internal High-Frequency Oscillator Electrical Characteristics

V<sub>DD</sub> = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified; Using factory-calibrated settings.

| Parameter                                            | Conditions                                      | Min              | Тур             | Max       | Units               |

|------------------------------------------------------|-------------------------------------------------|------------------|-----------------|-----------|---------------------|

| Oscillator Frequency                                 | IFCN = 111b;<br>VDD $\geq$ VREGMIN <sup>1</sup> | 24 – 0.5%        | 24 <sup>2</sup> | 24 + 0.5% | MHz                 |

|                                                      | IFCN = 111b;<br>VDD < VREGMIN <sup>1</sup>      | 24 – 1.0%        | 24 <sup>2</sup> | 24 + 1.0% |                     |

| Oscillator Supply Current<br>(from V <sub>DD</sub> ) | Internal Oscillator On<br>OSCICN[7:6] = 11b     | _                | 830             | 1300      | μA                  |

| Internal Oscillator Suspend                          | Temp = 25 °C                                    | —                | 66              | _         | μA                  |

| OSCICN[7:6] = 00b                                    | Temp = 85 °C                                    | —                | 110             | —         |                     |

| ZTCEN = 1                                            | Temp = 125 °C                                   | —                | 190             | —         |                     |

| Wake-up Time From Suspend                            | OSCICN[7:6] = 00b                               | —                | 1               | —         | μs                  |

| Power Supply Sensitivity                             | Constant Temperature                            | —                | 0.10            | _         | %/V                 |

| Temperature Sensitivity <sup>3</sup>                 | Constant Supply                                 |                  |                 |           |                     |

|                                                      | TC <sub>1</sub>                                 | —                | 5.0             | —         | ppm/°C              |

|                                                      | TC <sub>2</sub>                                 | —                | -0.65           | —         | ppm/°C <sup>2</sup> |

| 1 VREGMIN is the minimum (                           | output of the voltage regulator for             | r its low settin | a (REGO         |           | = 0b) See           |

VREGMIN is the minimum output of the voltage regulator for its low setting (REG0CN: REG0MD = 0b). See Table 5.8, "Voltage Regulator Electrical Characteristics," on page 48.

2. This is the average frequency across the operating temperature range.

3. Use temperature coefficients TC<sub>1</sub> and TC<sub>2</sub> to calculate the new internal oscillator frequency using the following equation:

$f(T) = f0 x (1 + TC_1 x (T - T0) + TC_2 x (T - T0)^2)$

where f0 is the internal oscillator frequency at 25 °C and T0 is 25 °C.

### 6.1. Modes of Operation

In a typical system, ADC0 is configured using the following steps:

- 1. If a gain adjustment is required, refer to Section "6.3. Selectable Gain" on page 58.

- 2. Choose the start of conversion source.

- 3. Choose Normal Mode or Burst Mode operation.

- 4. If Burst Mode, choose the ADC0 Idle Power State and set the Power-Up Time.

- 5. Choose the tracking mode. Note that Pre-Tracking Mode can only be used with Normal Mode.

- 6. Calculate the required settling time and set the post convert-start tracking time using the AD0TK bits.

- 7. Choose the repeat count.

- 8. Choose the output word justification (Right-Justified or Left-Justified).

- 9. Enable or disable the End of Conversion and Window Comparator Interrupts.

#### 6.1.1. Starting a Conversion

A conversion can be initiated in one of four ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM1–0) in register ADC0CN. Conversions may be initiated by one of the following:

- Writing a 1 to the AD0BUSY bit of register ADC0CN

- A rising edge on the CNVSTR input signal (pin P0.1)

- A Timer 1 overflow (i.e., timed continuous conversions)

- A Timer 2 overflow (i.e., timed continuous conversions)

Writing a 1 to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand." During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). Note: When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. Note that when Timer 2 overflows are used as the conversion source, Low Byte overflows are used if Timer2 is in 8-bit mode; High byte overflows are used if Timer 2 is in 16-bit mode. See Section "26. Timers" on page 265 for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as Port pin P0.1. When the CNVSTR input is used as the ADC0 conversion source, Port pin P0.1 should be skipped by the Digital Crossbar. To configure the Crossbar to skip P0.1, set to 1 Bit1 in register P0SKIP. See Section "20. Port Input/Output" on page 177 for details on Port I/O configuration.

#### 6.1.2. Tracking Modes

Each ADC0 conversion must be preceded by a minimum tracking time for the converted result to be accurate. ADC0 has three tracking modes: Pre-Tracking, Post-Tracking, and Dual-Tracking. Pre-Tracking Mode provides the minimum delay between the convert start signal and end of conversion by tracking continuously before the convert start signal. This mode requires software management in order to meet minimum tracking requirements. In Post-Tracking Mode, a programmable tracking time starts after the convert start signal and is managed by hardware. Dual-Tracking Mode maximizes tracking time by tracking before and after the convert start signal. Figure 6.2 shows examples of the three tracking modes.

Pre-Tracking Mode is selected when AD0TM is set to 10b. Conversions are started immediately following the convert start signal. ADC0 is tracking continuously when not performing a conversion. Software must allow at least the minimum tracking time between each end of conversion and the next convert start signal. The minimum tracking time must also be met prior to the first convert start signal after ADC0 is enabled.

### Gain Register Definition 6.3. ADC0GNA: ADC0 Additional Selectable Gain

| Bit      | 7                        | 6        | 5           | 4        | 3        | 2                 | 1 | 0       |  |  |  |  |  |  |

|----------|--------------------------|----------|-------------|----------|----------|-------------------|---|---------|--|--|--|--|--|--|

| Name     | Reserved                 | Reserved | Reserved    | Reserved | Reserved | Reserved Reserved |   | GAINADD |  |  |  |  |  |  |

| Туре     | W                        | W        | W           | W        | W        | W                 | W | W       |  |  |  |  |  |  |

| Reset    | 0                        | 0        | 0           | 0 0      |          | 0                 | 0 | 1       |  |  |  |  |  |  |

| Indirect | Indirect Address = 0x08; |          |             |          |          |                   |   |         |  |  |  |  |  |  |

| D:4      | Manaa                    |          | Francisco - |          |          |                   |   |         |  |  |  |  |  |  |

| Bit  | Name                                                                                                         | Function                                                                                                                       |  |  |  |  |  |  |  |  |

|------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 7:1  | Reserved                                                                                                     | Must Write 000000b.                                                                                                            |  |  |  |  |  |  |  |  |

| 0    | GAINADD                                                                                                      | ADC0 Additional Gain Bit.<br>Setting this bit add 1/64 (0.016) gain to the gain value in the ADC0GNH and<br>ADC0GNL registers. |  |  |  |  |  |  |  |  |

| Note | <b>Note</b> : This register is accessed indirectly; See Section 6.3.2 for details for writing this register. |                                                                                                                                |  |  |  |  |  |  |  |  |

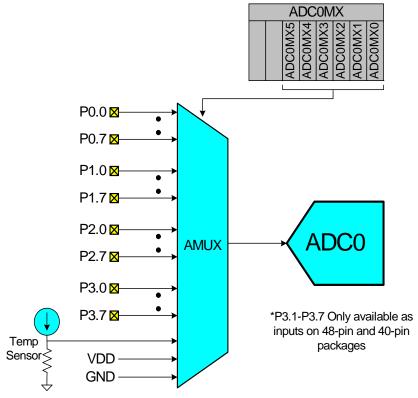

### 6.5. ADC0 Analog Multiplexer

ADC0 includes an analog multiplexer to enable multiple analog input sources. Any of the following may be selected as an input: P0.0–P3.7, the on-chip temperature sensor, the core power supply ( $V_{DD}$ ), or ground (GND). **ADC0 is single-ended and all signals measured are with respect to GND.** The ADC0 input channels are selected using the ADC0MX register as described in SFR Definition 6.13.

Figure 6.8. ADC0 Multiplexer Block Diagram

**Important Note About ADC0 Input Configuration:** Port pins selected as ADC0 inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set to 0 the corresponding bit in register PnMDIN. To force the Crossbar to skip a Port pin, set to 1 the corresponding bit in register PnSKIP. See Section "20. Port Input/Output" on page 177 for more Port I/O configuration details.

## 11. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware (see description in Section 28), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 11.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 50 MIPS Peak Throughput with 50 MHz Clock

- 0 to 50 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

### 11.1. Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

### 14.2. Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described in this section. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

### SFR Definition 18.2. EMI0CF: External Memory Configuration

| Bit   | 7   | 6 | 5 | 4    | 3   | 2      | 1         | 0 |  |  |  |  |

|-------|-----|---|---|------|-----|--------|-----------|---|--|--|--|--|

| Name  |     |   |   | EMD2 | EMD | 0[1:0] | EALE[1:0] |   |  |  |  |  |

| Туре  | R/W |   |   |      |     |        |           |   |  |  |  |  |

| Reset | 0   | 0 | 0 | 0    | 0   | 0      | 1         | 1 |  |  |  |  |

### SFR Address = 0xB2; SFR Page = 0x0F

| Bit | Name      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Unused    | Read = 000b; Write = Don't Care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4   | EMD2      | EMIF Multiplex Mode Select Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |           | 0: EMIF operates in multiplexed address/data mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |           | 1: EMIF operates in non-multiplexed mode (separate address and data pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3:2 | EMD[1:0]  | EMIF Operating Mode Select Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |           | 00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to on-chip memory space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |           | <ul> <li>01: Split Mode without Bank Select: Accesses below the 4 kB boundary are directed on-chip. Accesses above the 4 kB boundary are directed off-chip. 8-bit off-chip MOVX operations use current contents of the Address high port latches to resolve the upper address byte. To access off chip space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4 kB boundary are directed on-chip. Accesses above the 4 kB boundary are directed off-chip. 8-bit off-chip MOVX operations uses the contents of EMI0CN to determine the high-byte of the address.</li> <li>11: External Only: MOVX accesses off-chip XRAM only. On-chip XRAM is not visible to the CPU.</li> </ul> |

| 1:0 | EALE[1:0] | ALE Pulse-Width Select Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |           | These bits only have an effect when $EMD2 = 0$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |           | 00: ALE high and ALE low pulse width = 1 SYSCLK cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |           | 01: ALE high and ALE low pulse width = 2 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |           | 10: ALE high and ALE low pulse width = 3 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |           | 11: ALE high and ALE low pulse width = 4 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

### SFR Definition 18.3. EMI0TC: External Memory Timing Control

| Bit                                       | 7                                        | 6                                                                                                             | 5                                                                                                                                                                                  | 4           | 3           | 2   | 1   | 0     |  |  |  |  |

|-------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-----|-----|-------|--|--|--|--|

| Nam                                       | e EA                                     | S[1:0]                                                                                                        |                                                                                                                                                                                    | EWF         | R[3:0]      |     | EAH | [1:0] |  |  |  |  |

| Туре                                      | e l                                      | R/W                                                                                                           |                                                                                                                                                                                    | R           |             | R/W |     |       |  |  |  |  |

| Rese                                      | et 1                                     | 1                                                                                                             | 1                                                                                                                                                                                  | 1           | 1           | 1   | 1   | 1     |  |  |  |  |

| SFR A                                     | Address = 0x/                            | AA; SFR Page                                                                                                  | e = 0x0F                                                                                                                                                                           | 1           |             | 1   | I   |       |  |  |  |  |

| Bit                                       | Name                                     |                                                                                                               |                                                                                                                                                                                    |             | Function    |     |     |       |  |  |  |  |

| 7:6                                       | EAS[1:0]                                 | EMIF Addre                                                                                                    | ss Setup Ti                                                                                                                                                                        | ime Bits.   |             |     |     |       |  |  |  |  |

| 00: Address setup time = 0 SYSCLK cycles. |                                          |                                                                                                               |                                                                                                                                                                                    |             |             |     |     |       |  |  |  |  |

|                                           | 01: Address setup time = 1 SYSCLK cycle. |                                                                                                               |                                                                                                                                                                                    |             |             |     |     |       |  |  |  |  |

|                                           |                                          | <ul><li>10: Address setup time = 2 SYSCLK cycles.</li><li>11: Address setup time = 3 SYSCLK cycles.</li></ul> |                                                                                                                                                                                    |             |             |     |     |       |  |  |  |  |

|                                           |                                          | 11: Address                                                                                                   | setup time =                                                                                                                                                                       | = 3 SYSCLK  | cycles.     |     |     |       |  |  |  |  |

| 5:2                                       | EWR[3:0]                                 | EWR[3:0] EMIF WR and RD Pulse-Width Control Bits.                                                             |                                                                                                                                                                                    |             |             |     |     |       |  |  |  |  |

|                                           |                                          | 0000: <u>WR</u> ar                                                                                            |                                                                                                                                                                                    |             |             |     |     |       |  |  |  |  |

|                                           |                                          | 0001: WR and RD pulse width = 2 SYSCLK cycles.<br>0010: WR and RD pulse width = 3 SYSCLK cycles.              |                                                                                                                                                                                    |             |             |     |     |       |  |  |  |  |

|                                           |                                          |                                                                                                               |                                                                                                                                                                                    |             | •           |     |     |       |  |  |  |  |

|                                           |                                          | 0011: WR an<br>0100: WR ar                                                                                    |                                                                                                                                                                                    |             | •           |     |     |       |  |  |  |  |

|                                           |                                          | 0100: WR an                                                                                                   |                                                                                                                                                                                    |             |             |     |     |       |  |  |  |  |

|                                           |                                          | 0110: WR ar                                                                                                   |                                                                                                                                                                                    |             | •           |     |     |       |  |  |  |  |

|                                           |                                          | 0111: WR an                                                                                                   |                                                                                                                                                                                    |             | •           |     |     |       |  |  |  |  |

|                                           |                                          | 1000: WR ar                                                                                                   | nd RD pulse                                                                                                                                                                        | width = 9 S | YSCLK cycle | es. |     |       |  |  |  |  |

|                                           |                                          | 1001: WR ar                                                                                                   |                                                                                                                                                                                    |             |             |     |     |       |  |  |  |  |

|                                           |                                          | 1010: <u>WR</u> ar                                                                                            |                                                                                                                                                                                    |             |             |     |     |       |  |  |  |  |

|                                           |                                          | 1011: WR ar                                                                                                   |                                                                                                                                                                                    |             |             |     |     |       |  |  |  |  |

|                                           |                                          |                                                                                                               | 1100: $\overline{\text{WR}}$ and $\overline{\text{RD}}$ pulse width = 13 SYSCLK cycles.<br>1101: $\overline{\text{WR}}$ and $\overline{\text{RD}}$ pulse width = 14 SYSCLK cycles. |             |             |     |     |       |  |  |  |  |

|                                           |                                          | 1101. WR an                                                                                                   |                                                                                                                                                                                    |             |             |     |     |       |  |  |  |  |

|                                           |                                          | 1110: WR an                                                                                                   |                                                                                                                                                                                    |             |             |     |     |       |  |  |  |  |

| 1:0                                       | EAH[1:0]                                 | EMIF Addre                                                                                                    | -                                                                                                                                                                                  |             | -           |     |     |       |  |  |  |  |

|                                           |                                          | 00: Address                                                                                                   |                                                                                                                                                                                    |             | •           |     |     |       |  |  |  |  |

|                                           |                                          | 01: Address                                                                                                   |                                                                                                                                                                                    |             | •           |     |     |       |  |  |  |  |

|                                           |                                          | 10: Address                                                                                                   |                                                                                                                                                                                    |             | •           |     |     |       |  |  |  |  |

|                                           |                                          | 11: Address                                                                                                   | hold time =                                                                                                                                                                        | 3 SYSCLK o  | ycles.      |     |     |       |  |  |  |  |

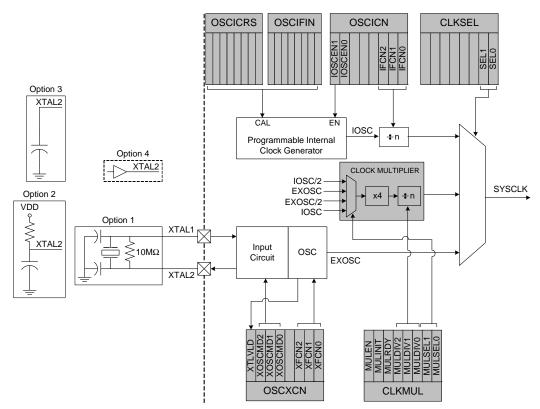

### **19. Oscillators and Clock Selection**

C8051F50x/F51x devices include a programmable internal high-frequency oscillator, an external oscillator drive circuit, and a clock multiplier. The internal oscillator can be enabled/disabled and calibrated using the OSCICN, OSCICRS, and OSCIFIN registers, as shown in Figure 19.1. The system clock can be sourced by the external oscillator circuit or the internal oscillator. The clock multiplier can produce three possible base outputs which can be scaled by a programmable factor of 1, 2/3, 2/4 (or 1/2), 2/5, 2/6 (or 1/3), or 2/7: Internal Oscillator x 2, Internal Oscillator x 4.

Figure 19.1. Oscillator Options

### 19.1. System Clock Selection

The CLKSL[1:0] bits in register CLKSEL select which oscillator source is used as the system clock. CLKSL[1:0] must be set to 01b for the system clock to run from the external oscillator; however the external oscillator may still clock certain peripherals (timers, PCA) when the internal oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal oscillator, external oscillator, and Clock Multiplier so long as the selected clock source is enabled and has settled.

The internal oscillator requires little start-up time and may be selected as the system clock immediately following the register write which enables the oscillator. The external RC and C modes also typically require no startup time.

External crystals and ceramic resonators however, typically require a start-up time before they are settled and ready for use. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to 1 by hardware when the external crystal or ceramic resonator is settled. In crystal mode, to avoid reading a false XTLVLD, software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD.

### SFR Definition 19.6. OSCXCN: External Oscillator Control

| Bit   | 7      | 6 5 |           | 4  | 3 | 2         | 1 | 0 |  |  |

|-------|--------|-----|-----------|----|---|-----------|---|---|--|--|

| Name  | XTLVLD | ×   | OSCMD[2:0 | )] |   | XFCN[2:0] |   |   |  |  |

| Туре  | R      |     | R/W       |    | R | R/W       |   |   |  |  |

| Reset | 0      | 0   | 0         | 0  | 0 | 0         | 0 | 0 |  |  |

#### SFR Address = 0x9F; SFR Page = 0x0F;

| Bit | Name        |         |                                                                                   | Function                                  |                 |  |  |  |  |  |  |  |  |

|-----|-------------|---------|-----------------------------------------------------------------------------------|-------------------------------------------|-----------------|--|--|--|--|--|--|--|--|

| 7   | XTLVLD      | Crystal | Oscillator Valid Flag.                                                            |                                           |                 |  |  |  |  |  |  |  |  |

|     |             | `       | nly when XOSCMD = 11                                                              | ,                                         |                 |  |  |  |  |  |  |  |  |

|     |             | -       | al Oscillator is unused of                                                        |                                           |                 |  |  |  |  |  |  |  |  |

|     | <u> </u>    | -       | al Oscillator is running a                                                        |                                           |                 |  |  |  |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] |         | External Oscillator Mode Select.                                                  |                                           |                 |  |  |  |  |  |  |  |  |

|     |             |         | 10: External CMOS Clock Mode.                                                     |                                           |                 |  |  |  |  |  |  |  |  |

|     |             |         | 11: External CMOS Clock Mode with divide by 2 stage.                              |                                           |                 |  |  |  |  |  |  |  |  |

|     |             |         | Coscillator Mode.                                                                 |                                           |                 |  |  |  |  |  |  |  |  |

|     |             |         | 1: Capacitor Oscillator Mode.                                                     |                                           |                 |  |  |  |  |  |  |  |  |

|     |             | -       | 0: Crystal Oscillator Mode.<br>1: Crystal Oscillator Mode with divide by 2 stage. |                                           |                 |  |  |  |  |  |  |  |  |

| 3   | Unused      |         | 0b; Write =0b                                                                     |                                           |                 |  |  |  |  |  |  |  |  |

| 2:0 | XFCN[2:0]   |         | I Oscillator Frequency                                                            | Control Bits.                             |                 |  |  |  |  |  |  |  |  |

|     |             |         |                                                                                   | quency for Crystal or RC                  | mode.           |  |  |  |  |  |  |  |  |

|     |             | Set acc | ording to the desired K F                                                         | actor for C mode.                         |                 |  |  |  |  |  |  |  |  |

|     |             | XFCN    | Crystal Mode                                                                      | RC Mode                                   | C Mode          |  |  |  |  |  |  |  |  |

|     |             | 000     | f ≤ 32 kHz                                                                        | f ≤ 25 kHz                                | K Factor = 0.87 |  |  |  |  |  |  |  |  |

|     |             | 001     | 32 kHz < f ≤ 84 kHz                                                               | 25 kHz < f ≤ 50 kHz                       | K Factor = 2.6  |  |  |  |  |  |  |  |  |

|     |             | 010     | 84 kHz < f ≤ 225 kHz                                                              | 50 kHz < f ≤ 100 kHz                      | K Factor = 7.7  |  |  |  |  |  |  |  |  |

|     |             | 011     | 225 kHz < f ≤ 590 kHz                                                             | 100 kHz < f ≤ 200 kHz                     | K Factor = 22   |  |  |  |  |  |  |  |  |

|     |             | 100     | 590 kHz < f ≤ 1.5 MHz                                                             | 200 kHz < f ≤ 400 kHz                     | K Factor = 65   |  |  |  |  |  |  |  |  |

|     |             | 101     | $1.5 \text{ MHz} < f \le 4 \text{ MHz}$                                           | 400 kHz < f ≤ 800 kHz                     | K Factor = 180  |  |  |  |  |  |  |  |  |

|     |             | 110     | $4 \text{ MHz} < f \le 10 \text{ MHz}$                                            | 800 kHz < f ≤ 1.6 MHz                     | K Factor = 664  |  |  |  |  |  |  |  |  |

|     |             | 111     | $10 \text{ MHz} < f \le 30 \text{ MHz}$                                           | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$ | K Factor = 1590 |  |  |  |  |  |  |  |  |

### SFR Definition 20.29. P4MDOUT: Port 4 Output Mode

| Bit   | 7                    | 7 6 5                                                                                     |              | 4             | 3            | 2            | 1 | 0 |  |  |  |  |  |

|-------|----------------------|-------------------------------------------------------------------------------------------|--------------|---------------|--------------|--------------|---|---|--|--|--|--|--|

| Nam   | e                    | I                                                                                         | P4MDOUT[7:0] |               |              |              |   |   |  |  |  |  |  |

| Тур   | e                    | R/W                                                                                       |              |               |              |              |   |   |  |  |  |  |  |

| Rese  | eset 0 0 0 0 0 0 0 0 |                                                                                           |              |               |              |              |   |   |  |  |  |  |  |

| SFR A | Address = 0xA        | F; SFR Page                                                                               | e = 0x0F     |               |              |              |   |   |  |  |  |  |  |

| Bit   | Name                 |                                                                                           |              |               | Function     |              |   |   |  |  |  |  |  |

| 7:0   | P4MDOUT[7:           | 0] Output                                                                                 | Configuratio | on Bits for P | 4.7–P4.0 (re | espectively) |   |   |  |  |  |  |  |

|       |                      | 0: Corresponding P4.n Output is open-drain.<br>1: Corresponding P4.n Output is push-pull. |              |               |              |              |   |   |  |  |  |  |  |

**Note:** Port 4.0 is only available on the 48-pin and 40-pin packages. P4.1-P4.7 are only available on the 48-pin packages.

Table 21.2 includes the configuration values required for the typical system clocks and baud rates:

|                 |       | Baud (bits/sec) |                |       |       |      |       |       |      |       |       |      |       |       |      |

|-----------------|-------|-----------------|----------------|-------|-------|------|-------|-------|------|-------|-------|------|-------|-------|------|

|                 |       | 20 k            | K 19.2 K 9.6 K |       |       |      | 4.8 K |       |      | 1 K   |       |      |       |       |      |

| SYSCLK<br>(MHz) | Mult. | Pres.           | Div.           | Mult. | Pres. | Div. | Mult. | Pres. | Div. | Mult. | Pres. | Div. | Mult. | Pres. | Div. |

| 25              | 0     | 1               | 312            | 0     | 1     | 325  | 1     | 1     | 325  | 3     | 1     | 325  | 19    | 1     | 312  |

| 24.5            | 0     | 1               | 306            | 0     | 1     | 319  | 1     | 1     | 319  | 3     | 1     | 319  | 19    | 1     | 306  |

| 24              | 0     | 1               | 300            | 0     | 1     | 312  | 1     | 1     | 312  | 3     | 1     | 312  | 19    | 1     | 300  |

| 22.1184         | 0     | 1               | 276            | 0     | 1     | 288  | 1     | 1     | 288  | 3     | 1     | 288  | 19    | 1     | 276  |

| 16              | 0     | 1               | 200            | 0     | 1     | 208  | 1     | 1     | 208  | 3     | 1     | 208  | 19    | 1     | 200  |

| 12.25           | 0     | 0               | 306            | 0     | 0     | 319  | 1     | 0     | 319  | 3     | 0     | 319  | 19    | 0     | 306  |

| 12              | 0     | 0               | 300            | 0     | 0     | 312  | 1     | 0     | 312  | 3     | 0     | 312  | 19    | 0     | 300  |

| 11.0592         | 0     | 0               | 276            | 0     | 0     | 288  | 1     | 0     | 288  | 3     | 0     | 288  | 19    | 0     | 276  |

| 8               | 0     | 0               | 200            | 0     | 0     | 208  | 1     | 0     | 208  | 3     | 0     | 208  | 19    | 0     | 200  |

#### 21.2.4. Baud Rate Calculations—Automatic Mode

If the LIN controller is configured for slave mode, only the prescaler and divider need to be calculated:

prescaler =

$$ln \left[ \frac{SYSCLK}{4000000} \right] \times \frac{1}{ln2} - 1$$

divider =

$$\frac{\text{SYSCLK}}{2^{(\text{prescaler}+1)} \times 20000}$$

The following example calculates the values of these variables for a 24 MHz system clock:

prescaler =

$$\ln \left[ \frac{24000000}{4000000} \right] \times \frac{1}{\ln 2} - 1 = 1.585 \cong 1$$

divider =

$$\frac{24000000}{2^{(1+1)} \times 20000}$$

= 300

Table 21.3 presents some typical values of system clock and baud rate along with their factors.

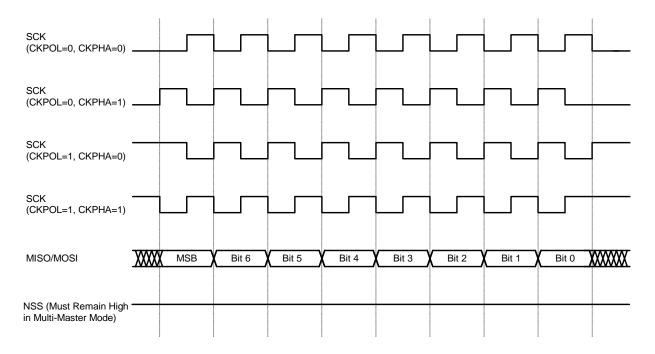

### 25.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 25.5. For slave mode, the clock and data relationships are shown in Figure 25.6 and Figure 25.7. CKPHA must be set to 0 on both the master and slave SPI when communicating between two of the following devices: C8051F04x, C8051F06x, C8051F12x, C8051F31x, C8051F32x, and C8051F33x.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 25.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

Figure 25.5. Master Mode Data/Clock Timing

### 26. Timers

Each MCU includes four counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and two are 16-bit auto-reload timer for use with the ADC, SMBus, or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 and Timer 3 offer 16-bit and split 8-bit timer functionality with auto-reload.

| Timer 0 and Timer 1 Modes               | Timer 2 Modes                     | Timer 3 Modes                     |

|-----------------------------------------|-----------------------------------|-----------------------------------|

| 13-bit counter/timer                    | 16-bit timer with auto-reload     | 16-bit timer with auto-reload     |

| 16-bit counter/timer                    | ]                                 |                                   |

| 8-bit counter/timer with auto-reload    | Two 8-bit timers with auto-reload | Two 8-bit timers with auto-reload |

| Two 8-bit counter/timers (Timer 0 only) |                                   |                                   |

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M– T0M) and the Clock Scale bits (SCA1–SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked (See SFR Definition 26.1 for pre-scaled clock selection).Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock.

Timer 2 and Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 0 and Timer 1 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin (T0 or T1). Events with a frequency of up to one-fourth the system clock frequency can be counted. The input signal need not be periodic, but it should be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

### SFR Definition 26.3. TMOD: Timer Mode

| Bit   | 7             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5           | 4            | 3             | 2             | 1              | 0            |  |  |

|-------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|---------------|---------------|----------------|--------------|--|--|

| Nam   | e GATE1       | C/T1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | T1M         | [1:0]        | GATE0         | C/T0          | T0M[1:0]       |              |  |  |

| Туре  | R/W           | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/          | W            | R/W           | R/W           | R/W            |              |  |  |

| Rese  | et 0          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0           | 0            | 0             | 0             | 0              | 0            |  |  |

| SFR / | Address = 0x8 | 9; SFR Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | = All Pages |              |               |               |                |              |  |  |

| Bit   |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |              |               |               |                |              |  |  |

| 7     | GATE1         | Timer 1 Ga                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | te Control. |              |               |               |                |              |  |  |