# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART       |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 40                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | ·                                                               |

| RAM Size                   | 4.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                    |

| Data Converters            | A/D 32x12b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                              |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 48-QFN (7x7)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f505-imr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 25.5. Master Mode Data/Clock Timing                          | . 257 |

|---------------------------------------------------------------------|-------|

| Figure 25.6. Slave Mode Data/Clock Timing (CKPHA = 0)               |       |

| Figure 25.7. Slave Mode Data/Clock Timing (CKPHA = 1)               | . 258 |

| Figure 25.8. SPI Master Timing (CKPHA = 0)                          |       |

| Figure 25.9. SPI Master Timing (CKPHA = 1)                          |       |

| Figure 25.10. SPI Slave Timing (CKPHA = 0)                          | . 263 |

| Figure 25.11. SPI Slave Timing (CKPHA = 1)                          | . 263 |

| Figure 26.1. T0 Mode 0 Block Diagram                                | . 268 |

| Figure 26.2. T0 Mode 2 Block Diagram                                | . 269 |

| Figure 26.3. T0 Mode 3 Block Diagram                                | . 270 |

| Figure 26.4. Timer 2 16-Bit Mode Block Diagram                      | . 275 |

| Figure 26.5. Timer 2 8-Bit Mode Block Diagram                       | . 276 |

| Figure 26.6. Timer 2 External Oscillator Capture Mode Block Diagram | . 277 |

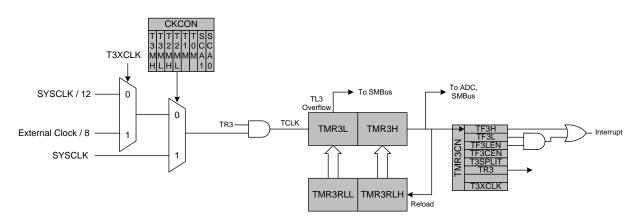

| Figure 26.7. Timer 3 16-Bit Mode Block Diagram                      | . 281 |

| Figure 26.8. Timer 3 8-Bit Mode Block Diagram                       | . 282 |

| Figure 26.9. Timer 3 External Oscillator Capture Mode Block Diagram | . 283 |

| Figure 27.1. PCA Block Diagram                                      | . 287 |

| Figure 27.2. PCA Counter/Timer Block Diagram                        | . 288 |

| Figure 27.3. PCA Interrupt Block Diagram                            |       |

| Figure 27.4. PCA Capture Mode Diagram                               | . 291 |

| Figure 27.5. PCA Software Timer Mode Diagram                        | . 292 |

| Figure 27.6. PCA High-Speed Output Mode Diagram                     | . 293 |

| Figure 27.7. PCA Frequency Output Mode                              | . 294 |

| Figure 27.8. PCA 8-Bit PWM Mode Diagram                             |       |

| Figure 27.9. PCA 9, 10 and 11-Bit PWM Mode Diagram                  | . 296 |

| Figure 27.10. PCA 16-Bit PWM Mode                                   | . 297 |

| Figure 27.11. PCA Module 2 with Watchdog Timer Enabled              |       |

| Figure 28.1. Typical C2 Pin Sharing                                 | . 309 |

|                                                                     |       |

|                                                                  | 005 |

|------------------------------------------------------------------|-----|

| Table 21.3. Autobaud Parameters Examples                         | 205 |

| Table 21.4. LIN Registers (Indirectly Addressable)               | 210 |

| Table 22.1. Background System Information                        | 220 |

| Table 22.2. Standard CAN Registers and Reset Values              | 223 |

| Table 23.1. SMBus Clock Source Selection                         | 230 |

| Table 23.2. Minimum SDA Setup and Hold Times                     | 231 |

| Table 23.3. Sources for Hardware Changes to SMB0CN               | 235 |

| Table 23.4. SMBus Status Decoding                                | 241 |

| Table 24.1. Baud Rate Generator Settings for Standard Baud Rates | 244 |

| Table 25.1. SPI Slave Timing Parameters                          | 264 |

| Table 27.1. PCA Timebase Input Options                           | 288 |

| Table 27.2. PCA0CPM and PCA0PWM Bit Settings for                 |     |

| PCA Capture/Compare Modules                                      | 290 |

| Table 27.3. Watchdog Timer Timeout Intervals1                    | 299 |

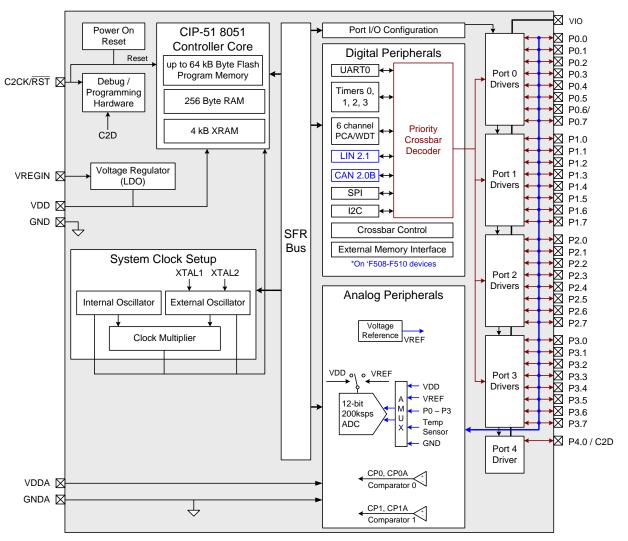

Figure 1.2. C8051F508/9-F510/1 Block Diagram

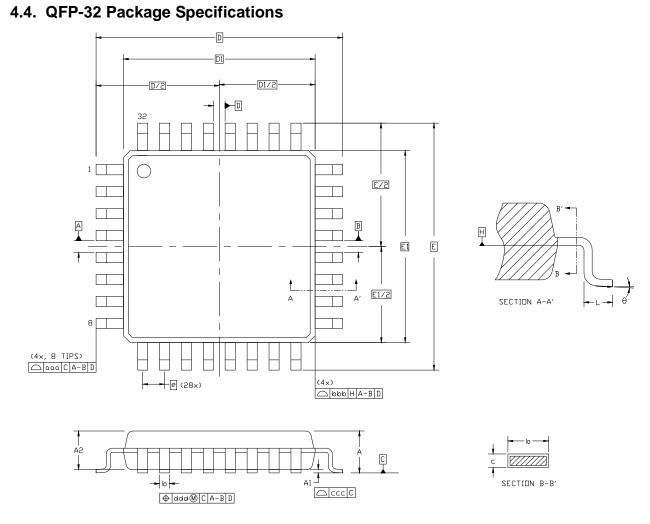

### Figure 4.7. QFP-32 Package Drawing

#### Table 4.7. QFP-32 Package Dimensions

| Dimension | Min  | Тур       | Max  |  | Dimension | Min       | Тур       | Max  |

|-----------|------|-----------|------|--|-----------|-----------|-----------|------|

| A         | _    | —         | 1.60 |  | E         | 9.00 BSC. |           |      |

| A1        | 0.05 | —         | 0.15 |  | E1        |           | 7.00 BSC. |      |

| A2        | 1.35 | 1.40      | 1.45 |  | L         | 0.45      | 0.60      | 0.75 |

| b         | 0.30 | 0.37      | 0.45 |  | aaa       | 0.20      |           |      |

| С         | 0.09 | —         | 0.20 |  | bbb       | 0.20      |           |      |

| D         |      | 9.00 BSC. |      |  | CCC       | 0.10      |           |      |

| D1        |      | 7.00 BSC. |      |  | ddd       |           | 0.20      |      |

| е         |      | 0.80 BSC. |      |  | θ         | 0°        | 3.5°      | 7°   |

#### Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC outline MS-026, variation BBA.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### Table 5.7. Clock Multiplier Electrical Specifications

$V_{DD}$  = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified.

| Parameter                            | Conditions | Min | Тур | Max | Units |

|--------------------------------------|------------|-----|-----|-----|-------|

| Input Frequency (Fcm <sub>in</sub> ) |            | 2   | —   | _   | MHz   |

| Output Frequency                     |            |     |     | 50  | MHz   |

| Power Supply Current                 |            |     | 1.1 | 1.9 | mA    |

### Table 5.8. Voltage Regulator Electrical Characteristics

$V_{DD}$  = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified.

| Parameter                                  | Conditions                                                                     | Min         | Тур     | Max   | Units |

|--------------------------------------------|--------------------------------------------------------------------------------|-------------|---------|-------|-------|

| Input Voltage Range (V <sub>REGIN</sub> )* |                                                                                | 1.8*        |         | 5.25  | V     |

| Dropout Voltage (V <sub>DO</sub> )         | Maximum Current = 50 mA                                                        | —           | 10      | _     | mV/mA |

| Output Voltage (V <sub>DD</sub> )          | 2.1 V operation (REG0MD = 0)                                                   | 2.0         | 2.1     | 2.25  | V     |

| Oulput voltage (v <sub>DD</sub> )          | 2.6 V operation (REG0MD = 1)                                                   | 2.5         | 2.6     | 2.75  | v     |

| Bias Current                               |                                                                                | —           | 1       | 9     | μA    |

| Dropout Indicator Detection<br>Threshold   | With respect to VDD                                                            | -0.21       | _       | -0.02 | V     |

| Output Voltage Temperature<br>Coefficient  |                                                                                | _           | 0.11    |       | mV/°C |

| VREG Settling Time                         | 50 mA load with $V_{REGIN} = 2.4 V$ and $V_{DD}$ load capacitor of 4.8 $\mu$ F | _           | 450     | _     | μs    |

| *Note: The minimum input voltage           | is 1.8 V or V <sub>DD</sub> + V <sub>DO</sub> (max load), whi                  | chever is g | greater |       | 1     |

### SFR Definition 6.8. ADC0TK: ADC0 Tracking Mode Select

| Bit   | 7 | 6     | 5       | 4 | 3    | 2      | 1    | 0      |

|-------|---|-------|---------|---|------|--------|------|--------|

| Name  |   | AD0PV | VR[3:0] |   | AD0T | M[1:0] | AD0T | K[1:0] |

| Туре  |   | R/    | W       |   | R/   | W      | R/   | W      |

| Reset | 1 | 1     | 1       | 1 | 1    | 1      | 1    | 1      |

SFR Address = 0xBA; SFR Page = 0x00;

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                               |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | AD0PWR[3:0] | For BURSTEN = 0: ADC0 Power state controlled by AD0EN<br>For BURSTEN = 1, AD0EN = 1: ADC0 remains enabled and does not enter the<br>very low power state<br>For BURSTEN = 1, AD0EN = 0: ADC0 enters the very low power state and is<br>enabled after each convert start signal. The Power-Up time is programmed accord-<br>ing the following equation: |

| 3:2 | AD0TM[1:0]  | AD0PWR = $\frac{\text{Tstartup}}{200\text{ns}} - 1$ or Tstartup = (AD0PWR + 1)200ns         ADC0 Tracking Mode Enable Select Bits.         00: Reserved.         01: ADC0 is configured to Post-Tracking Mode.         10: ADC0 is configured to Pre-Tracking Mode.         11: ADC0 is configured to Dual Tracking Mode.                              |

| 1:0 | AD0TK[1:0]  | ADC0 Post-Track Time.<br>00: Post-Tracking time is equal to 2 SAR clock cycles + 2 FCLK cycles.<br>01: Post-Tracking time is equal to 4 SAR clock cycles + 2 FCLK cycles.<br>10: Post-Tracking time is equal to 8 SAR clock cycles + 2 FCLK cycles.<br>11: Post-Tracking time is equal to 16 SAR clock cycles + 2 FCLK cycles.                         |

#### 6.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

## SFR Definition 8.1. REF0CN: Reference Control

| Bit   | 7 | 6 | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|---|---|-------|-------|-------|-------|-------|-------|

| Name  |   |   | ZTCEN | REFLV | REFSL | TEMPE | BIASE | REFBE |

| Туре  | R | R | R     | R     | R/W   | R/W   | R/W   | R/W   |

| Reset | 0 | 0 | 0     | 0     | 0     | 0     | 0     | 0     |

#### SFR Address = 0xD1; SFR Page = 0x00

| Bit | Name   | Function                                                                                                                                                                                                              |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b; Write = don't care.                                                                                                                                                                                       |

| 5   | ZTCEN  | Zero Temperature Coefficient Bias Enable Bit.<br>This bit must be set to 1b before entering oscillator suspend mode.                                                                                                  |

|     |        | 0: ZeroTC Bias Generator automatically enabled when required.<br>1: ZeroTC Bias Generator forced on.                                                                                                                  |

| 4   | REFLV  | Voltage Reference Output Level Select.<br>This bit selects the output voltage level for the internal voltage reference<br>0: Internal voltage reference set to 1.5 V.<br>1: Internal voltage reference set to 2.20 V. |

| 3   | REFSL  | <ul> <li>Voltage Reference Select.</li> <li>This bit selects the ADCs voltage reference.</li> <li>0: V<sub>REF</sub> pin used as voltage reference.</li> <li>1: V<sub>DD</sub> used as voltage reference.</li> </ul>  |

| 2   | TEMPE  | Temperature Sensor Enable Bit.0: Internal Temperature Sensor off.1: Internal Temperature Sensor on.                                                                                                                   |

| 1   | BIASE  | Internal Analog Bias Generator Enable Bit.<br>0: Internal Bias Generator off.<br>1: Internal Bias Generator on.                                                                                                       |

| 0   | REFBE  | <ul> <li>On-chip Reference Buffer Enable Bit.</li> <li>0: On-chip Reference Buffer off.</li> <li>1: On-chip Reference Buffer on. Internal voltage reference driven on the V<sub>REF</sub> pin.</li> </ul>             |

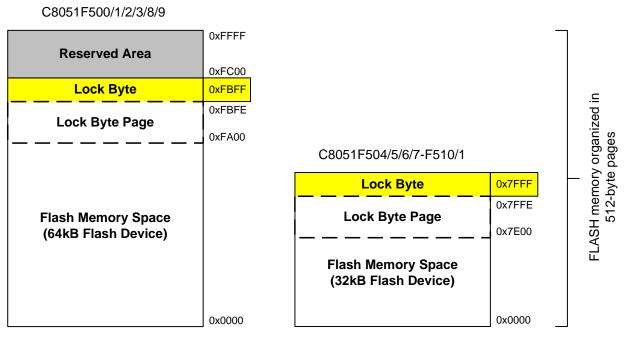

## 12.1. Program Memory

The CIP-51 core has a 64 kB program memory space. The C8051F50x/F51x devices implement 64 kB or 32 kB of this program memory space as in-system, re-programmable Flash memory, organized in a contiguous block from addresses 0x0000 to 0xFFFF in 64 kB devices and addresses 0x0000 to 0x7FFF in 32 kB devices. The address 0xFBFF in 64 kB devices and 0x7FFF in 32 kB devices serves as the security lock byte for the device. Addresses above 0xFDFF are reserved in the 64 kB devices.

Figure 12.2. Flash Program Memory Map

#### 12.1.1. MOVX Instruction and Program Memory

The MOVX instruction in an 8051 device is typically used to access external data memory. On the C8051F50x/F51x devices, the MOVX instruction is normally used to read and write on-chip XRAM, but can be re-configured to write and erase on-chip Flash memory space. MOVC instructions are always used to read Flash memory, while MOVX write instructions are used to erase and write Flash. This Flash access feature provides a mechanism for the C8051F50x/F51x to update program code and use the program memory space for non-volatile data storage. Refer to Section "15. Flash Memory" on page 129 for further details.

#### 12.2. Data Memory

The C8051F50x/F51x devices include 4352 bytes of RAM data memory. 256 bytes of this memory is mapped into the internal RAM space of the 8051. The other 4096 bytes of this memory is on-chip "external" memory. The data memory map is shown in Figure 12.1 for reference.

#### 12.2.1. Internal RAM

There are 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight

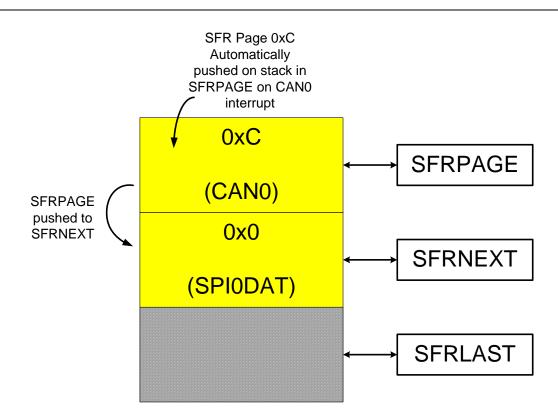

Figure 13.3. SFR Page Stack After CAN0 Interrupt Occurs

While in the CAN0 ISR, a PCA interrupt occurs. Recall the PCA interrupt is configured as a high priority interrupt, while the CAN0 interrupt is configured as a *low* priority interrupt. Thus, the CIP-51 will now vector to the high priority PCA ISR. Upon doing so, the CIP-51 will automatically place the SFR page needed to access the PCA's special function registers into the SFRPAGE register, SFR Page 0x00. The value that was in the SFRPAGE register before the PCA interrupt (SFR Page 0x0C for CAN0) is pushed down the stack into SFRNEXT. Likewise, the value that was in the SFRNEXT register before the PCA interrupt (in this case SFR Page 0x00 for SPI0DAT) is pushed down to the SFRLAST register, the "bottom" of the stack. Note that a value stored in SFRLAST (via a previous software write to the SFRLAST register) will be overwritten. See Figure 13.4.

## Table 13.3. Special Function Registers

| Register   | Address | Description                              | Page |

|------------|---------|------------------------------------------|------|

| ACC        | 0xE0    | Accumulator                              | 94   |

| ADC0CF     | 0xBC    | ADC0 Configuration                       | 63   |

| ADC0CN     | 0xE8    | ADC0 Control                             | 65   |

| ADC0GTH    | 0xC4    | ADC0 Greater-Than Compare High           | 67   |

| ADC0GTL    | 0xC3    | ADC0 Greater-Than Compare Low            | 67   |

| ADC0H      | 0xBE    | ADC0 High                                | 64   |

| ADC0L      | 0xBD    | ADC0 Low                                 | 64   |

| ADC0LTH    | 0xC6    | ADC0 Less-Than Compare Word High         | 68   |

| ADC0LTL    | 0xC5    | ADC0 Less-Than Compare Word Low          | 68   |

| ADC0MX     | 0xBB    | ADC0 Mux Configuration                   | 71   |

| ADC0TK     | 0xBA    | ADC0 Tracking Mode Select                | 66   |

| В          | 0xF0    | B Register                               | 94   |

| CCH0CN     | 0xE3    | Cache Control                            | 137  |

| CKCON      | 0x8E    | Clock Control                            | 266  |

| CLKMUL     | 0x97    | Clock Multiplier                         | 171  |

| CLKSEL     | 0x8F    | Clock Select                             | 166  |

| CPT0CN     | 0x9A    | Comparator0 Control                      | 77   |

| CPT0MD     | 0x9B    | Comparator0 Mode Selection               | 78   |

| CPT0MX     | 0x9C    | Comparator0 MUX Selection                | 82   |

| CPT1CN     | 0x9D    | Comparator1 Control                      | 77   |

| CPT1MD     | 0x9E    | Comparator1 Mode Selection               | 78   |

| CPT1MX     | 0x9F    | Comparator1 MUX Selection                | 82   |

| DPH        | 0x83    | Data Pointer High                        | 93   |

| DPL        | 0x82    | Data Pointer Low                         | 93   |

| EIE1       | 0xE6    | Extended Interrupt Enable 1              | 123  |

| EIE2       | 0xE7    | Extended Interrupt Enable 2              | 123  |

| EIP1       | 0xF6    | Extended Interrupt Priority 1            | 124  |

| EIP2       | 0xF7    | Extended Interrupt Priority 2            | 125  |

| EMI0CF     | 0xB2    | External Memory Interface Configuration  | 152  |

| EMI0CN     | 0xAA    | External Memory Interface Control        | 151  |

| EMIOTC     | 0xAA    | External Memory Interface Timing Control | 157  |

| FLKEY 0xB7 |         | Flash Lock and Key                       | 135  |

| FLSCL      | 0xB6    | Flash Scale                              | 136  |

| IE         | 0xA8    | Interrupt Enable                         | 121  |

| IP         | 0xB8    | Interrupt Priority                       | 122  |

#### 15.4. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of  $V_{DD}$ , system clock frequency, or temperature. This accidental execution of Flash modifying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

The following guidelines are recommended for any system which contains routines which write or erase Flash from code.

#### 15.4.1. $V_{\text{DD}}$ Maintenance and the $V_{\text{DD}}$ monitor

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- 2. The on-chip V<sub>DD</sub> monitor is turned on and enabled as a reset source by default by the hardware. If it is disabled by the firmware, use the following recommendations when re-enabling the V<sub>DD</sub> monitor. Turn on the V<sub>DD</sub> monitor and enable it as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For C-based systems, this will involve modifying the startup code added by the C compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the V<sub>DD</sub> monitor and enabling the V<sub>DD</sub> monitor as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware", available from the Silicon Laboratories web site.

- 3. As an added precaution, explicitly enable the V<sub>DD</sub> monitor and enable the V<sub>DD</sub> monitor as a reset source inside the functions that write and erase Flash memory. The V<sub>DD</sub> monitor enable instructions should be placed just after the instruction to set PSWE to a 1, but before the Flash write or erase operation instruction.

- 4. Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct. "RSTSRC |= 0x02" is incorrect.

- 5. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a 1. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

#### 15.4.2. PSWE Maintenance

- 1. Reduce the number of places in code where the PSWE bit (b0 in PSCTL) is set to a 1. There should be exactly one routine in code that sets PSWE to a 1 to write Flash bytes and one routine in code that sets PSWE and PSEE both to a 1 to erase Flash pages.

- Minimize the number of variable accesses while PSWE is set to a 1. Handle pointer address updates and loop variable maintenance outside the "PSWE = 1;... PSWE = 0;" area. Code examples showing this can be found in "AN201: Writing to Flash from Firmware" available from the Silicon Laboratories web site.

- 3. Disable interrupts prior to setting PSWE to a 1 and leave them disabled until after PSWE has been reset to '0'. Any interrupts posted during the Flash write or erase operation will be serviced in priority order after the Flash operation has been completed and interrupts have been re-enabled by software.

- Make certain that the Flash write and erase pointer variables are not located in XRAM. See your compiler documentation for instructions regarding how to explicitly locate variables in different memory areas.

- 5. Add address bounds checking to the routines that write or erase Flash memory to ensure that a routine called with an illegal address does not result in modification of the Flash.

## SFR Definition 17.1. VDM0CN: V<sub>DD</sub> Monitor Control

| Bit   | 7      | 6       | 5      | 4 | 3 | 2 | 1 | 0 |

|-------|--------|---------|--------|---|---|---|---|---|

| Name  | VDMEN  | VDDSTAT | VDMLVL |   |   |   |   |   |

| Туре  | R/W    | R       | R/W    | R | R | R | R | R |

| Reset | Varies | Varies  | 0      | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xFF; SFR Page = 0x00

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN   | V <sub>DD</sub> Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |         | This bit turns the V <sub>DD</sub> monitor circuit on/off. The V <sub>DD</sub> Monitor cannot generate system resets until it is also selected as a reset source in register RSTSRC (SFR Definition 17.2). Selecting the V <sub>DD</sub> monitor as a reset source before it has stabilized may generate a system reset. In systems where this reset would be undesirable, a delay should be introduced between enabling the V <sub>DD</sub> Monitor and selecting it as a reset source. See Table 5.4 for the minimum V <sub>DD</sub> Monitor turn-on time.<br>0: V <sub>DD</sub> Monitor Disabled.<br>1: V <sub>DD</sub> Monitor Enabled. |

| 6   | VDDSTAT | V <sub>DD</sub> Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |         | This bit indicates the current power supply status ( $V_{DD}$ Monitor output).<br>0: $V_{DD}$ is at or below the $V_{DD}$ monitor threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |         | 1: V <sub>DD</sub> is above the V <sub>DD</sub> monitor threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5   | VDMLVL  | V <sub>DD</sub> Monitor Level Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |         | 0: $V_{DD}$ Monitor Threshold is set to VRST-LOW<br>1: $V_{DD}$ Monitor Threshold is set to VRST-HIGH. This setting is required for any system includes code that writes to and/or erases Flash.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4:0 | Unused  | Read = 00000b; Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

### 17.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 5.4 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

### 17.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than the value specified in Table 5.4, "Reset Electrical Characteristics," on page 46, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

| Multiplexed Mode |          |  |  |  |  |  |

|------------------|----------|--|--|--|--|--|

| Signal Name      | Port Pin |  |  |  |  |  |

| RD               | P1.6     |  |  |  |  |  |

| WR               | P1.7     |  |  |  |  |  |

| ALE              | P1.5     |  |  |  |  |  |

| D0/A0            | P4.0     |  |  |  |  |  |

| D1/A1            | P4.1     |  |  |  |  |  |

| D2/A2            | P4.2     |  |  |  |  |  |

| D3/A3            | P4.3     |  |  |  |  |  |

| D4/A4            | P4.4     |  |  |  |  |  |

| D5/A5            | P4.5     |  |  |  |  |  |

| D6/A6            | P4.6     |  |  |  |  |  |

| D7/A7            | P4.7     |  |  |  |  |  |

| A8               | P3.0     |  |  |  |  |  |

| A9               | P3.1     |  |  |  |  |  |

| A10              | P3.2     |  |  |  |  |  |

| A11              | P3.3     |  |  |  |  |  |

| A12              | P3.4     |  |  |  |  |  |

| A13              | P3.5     |  |  |  |  |  |

| A14              | P3.6     |  |  |  |  |  |

| A15              | P3.7     |  |  |  |  |  |

| —                | _        |  |  |  |  |  |

| —                | —        |  |  |  |  |  |

| —                | —        |  |  |  |  |  |

| —                | _        |  |  |  |  |  |

| —                | _        |  |  |  |  |  |

| —                | —        |  |  |  |  |  |

| —                | _        |  |  |  |  |  |

## Table 18.1. EMIF Pinout (C8051F500/1/4/5)

| Non Multiplexed Mode |          |  |  |  |  |  |

|----------------------|----------|--|--|--|--|--|

| Signal Name          | Port Pin |  |  |  |  |  |

| RD                   | P1.6     |  |  |  |  |  |

| WR                   | P1.7     |  |  |  |  |  |

| D0                   | P4.0     |  |  |  |  |  |

| D1                   | P4.1     |  |  |  |  |  |

| D2                   | P4.2     |  |  |  |  |  |

| D3                   | P4.3     |  |  |  |  |  |

| D4                   | P4.4     |  |  |  |  |  |

| D5                   | P4.5     |  |  |  |  |  |

| D6                   | P4.6     |  |  |  |  |  |

| D7                   | P4.7     |  |  |  |  |  |

| A0                   | P3.0     |  |  |  |  |  |

| A1                   | P3.1     |  |  |  |  |  |

| A2                   | P3.2     |  |  |  |  |  |

| A3                   | P3.3     |  |  |  |  |  |

| A4                   | P3.4     |  |  |  |  |  |

| A5                   | P3.5     |  |  |  |  |  |

| A6                   | P3.6     |  |  |  |  |  |

| A7                   | P3.7     |  |  |  |  |  |

| A8                   | P2.0     |  |  |  |  |  |

| A9                   | P2.1     |  |  |  |  |  |

| A10                  | P2.2     |  |  |  |  |  |

| A11                  | P2.3     |  |  |  |  |  |

| A12                  | P2.4     |  |  |  |  |  |

| A13                  | P2.5     |  |  |  |  |  |

| A14                  | P2.6     |  |  |  |  |  |

| A15                  | P2.7     |  |  |  |  |  |

#### 18.5.3. Split Mode with Bank Select

When EMI0CF[3:2] are set to 10, the XRAM memory map is split into two areas, on-chip space and offchip space.

- Effective addresses below the internal XRAM size boundary will access on-chip XRAM space.

- Effective addresses above the internal XRAM size boundary will access off-chip space.

- 8-bit MOVX operations use the contents of EMI0CN to determine whether the memory access is onchip or off-chip. The upper 8-bits of the Address Bus A[15:8] are determined by EMI0CN, and the lower 8-bits of the Address Bus A[7:0] are determined by R0 or R1. All 16-bits of the Address Bus A[15:0] are driven in "Bank Select" mode.

- 16-bit MOVX operations use the contents of DPTR to determine whether the memory access is on-chip or off-chip, and the full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

#### 18.5.4. External Only

When EMI0CF[3:2] are set to 11, all MOVX operations are directed to off-chip space. On-chip XRAM is not visible to the CPU. This mode is useful for accessing off-chip memory located between 0x0000 and the internal XRAM size boundary.

- 8-bit MOVX operations ignore the contents of EMI0CN. The upper Address bits A[15:8] are not driven (identical behavior to an off-chip access in "Split Mode without Bank Select" described above). This allows the user to manipulate the upper address bits at will by setting the Port state directly. The lower 8-bits of the effective address A[7:0] are determined by the contents of R0 or R1.

- 16-bit MOVX operations use the contents of DPTR to determine the effective address A[15:0]. The full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

#### 18.6. Timing

The timing parameters of the External Memory Interface can be configured to enable connection to devices having different setup and hold time requirements. The Address Setup time, Address Hold time, RD and WR strobe widths, and in multiplexed mode, the width of the ALE pulse are all programmable in units of SYSCLK periods through EMI0TC, shown in SFR Definition 18.3, and EMI0CF[1:0].

The timing for an off-chip MOVX instruction can be calculated by adding 4 SYSCLK cycles to the timing parameters defined by the EMI0TC register. Assuming non-multiplexed operation, the minimum execution time for an off-chip XRAM operation is 5 SYSCLK cycles (1 SYSCLK for RD or WR pulse + 4 SYSCLKs). For multiplexed operations, the Address Latch Enable signal will require a minimum of 2 additional SYSCLK cycles. Therefore, the minimum execution time for an off-chip XRAM operation in multiplexed mode is 7 SYSCLK cycles (2 for /ALE + 1 for RD or WR + 4). The programmable setup and hold times default to the maximum delay settings after a reset. Table 18.3 lists the ac parameters for the External Memory Interface, and Figure 18.4 through Figure 18.9 show the timing diagrams for the different External Memory Interface modes and MOVX operations.

### SFR Definition 19.1. CLKSEL: Clock Select

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0      |

|-------|---|---|---|---|---|---|------|--------|

| Name  |   |   |   |   |   |   | CLKS | L[1:0] |

| Туре  | R | R | R | R | R | R | R/W  |        |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0      |

#### SFR Address = 0x8F; SFR Page = 0x0F;

| Bit | Name       | Function                                                                                                                                                                                                                                  |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused     | Read = 000000b; Write = Don't Care                                                                                                                                                                                                        |

| 1:0 | CLKSL[1:0] | System Clock Source Select Bits.                                                                                                                                                                                                          |

|     |            | <ul><li>00: SYSCLK derived from the Internal Oscillator and scaled per the IFCN bits in register OSCICN.</li><li>01: SYSCLK derived from the External Oscillator circuit.</li><li>10: SYSCLK derived from the Clock Multiplier.</li></ul> |

|     |            | 11: reserved.                                                                                                                                                                                                                             |

Important Note: If the selected system clock is greater than 25 MHz, please be aware of the following:

- Flash Scale Timing must be configured for the faster system clock. See SFR Definition 15.3 for more details.

- VDD and VDDA voltage must be 2 V or higher.

- It is recommended to enable the VDD monitor as a reset source and configure it for the high threshold. See SFR Definition 17.1 for details on configuring the VDD monitor. If the VDD monitor is configured to the high threshold, the VDD and VDDA voltage must be greater than the VDD monitor high threshold. See Table 5.4 for VDD monitor threshold specifications.

## SFR Definition 19.5. CLKMUL: Clock Multiplier

| Bit   | 7     | 6       | 5      | 4           | 3 | 2 | 1           | 0 |  |

|-------|-------|---------|--------|-------------|---|---|-------------|---|--|

| Name  | MULEN | MULINIT | MULRDY | MULDIV[2:0] |   |   | MULSEL[1:0] |   |  |

| Туре  | R/W   | R/W     | R      | R/W         |   |   | R/          | W |  |

| Reset | 0     | 0       | 0      | 0           | 0 | 0 | 0           | 0 |  |

#### SFR Address = 0x97; SFR Page = 0x0F;

| MULEN       | Clock Multiplier                               | . En al-la                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|-------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|             | Clock Multiplier Enable.                       |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             | 0: Clock Multiplier disabled.                  |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             | 1: Clock Multiplier enabled.                   |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| MULINIT     | <b>Clock Multiplier</b>                        | r Initialize.                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             | bit will initialize th                         | he Clock Multiplier. The MULRD                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| MULRDY      | <b>Clock Multiplier</b>                        | r Ready.                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             | 0: Clock Multiplie                             | er is not ready.                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             | 1: Clock Multiplie                             | er is ready (PLL is locked).                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| MULDIV[2:0] |                                                | • •                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             |                                                |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             |                                                |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             |                                                |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             |                                                |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             |                                                |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             |                                                |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             |                                                |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             |                                                |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| MULSEL[1:0] | Clock Multiplier                               | r Input Select.                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             | -                                              | •                                                                                                                       | Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|             | MULSEL[1:0]                                    | Selected Input Clock                                                                                                    | Clock Multiplier Output<br>for MULDIV[2:0] = 000b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|             | 00                                             | Internal Oscillator                                                                                                     | Internal Oscillator x 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|             | 01 External Oscillator External Oscilla        |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             | 10 Internal Oscillator Internal Oscillator x 4 |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |