#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 50MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), CANbus, LINbus, SPI, UART/USART |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                       |

| Number of I/O              | 25                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | •                                                                |

| RAM Size                   | 4.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                     |

| Data Converters            | A/D 25x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 32-LQFP                                                          |

| Supplier Device Package    | 32-LQFP (7x7)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f506-iq   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 25.1.3. Serial Clock (SCK)                                          |     |

|---------------------------------------------------------------------|-----|

| 25.1.4. Slave Select (NSS)                                          |     |

| 25.2. SPI0 Master Mode Operation                                    |     |

| 25.3. SPI0 Slave Mode Operation                                     |     |

| 25.4. SPI0 Interrupt Sources                                        |     |

| 25.5. Serial Clock Phase and Polarity                               |     |

| 25.6. SPI Special Function Registers                                | 258 |

| 26. Timers                                                          |     |

| 26.1. Timer 0 and Timer 1                                           |     |

| 26.1.1. Mode 0: 13-bit Counter/Timer                                | 267 |

| 26.1.2. Mode 1: 16-bit Counter/Timer                                |     |

| 26.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload                | 268 |

| 26.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)             | 269 |

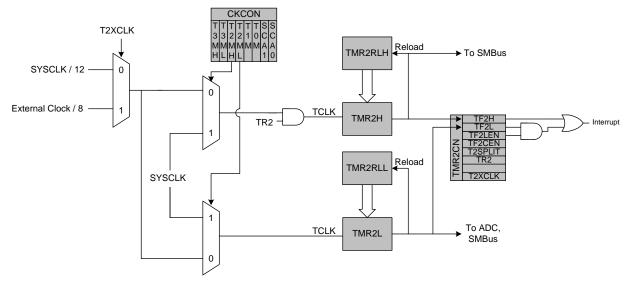

| 26.2. Timer 2                                                       | 275 |

| 26.2.1. 16-bit Timer with Auto-Reload                               | 275 |

| 26.2.2. 8-bit Timers with Auto-Reload                               | 275 |

| 26.2.3. External Oscillator Capture Mode                            |     |

| 26.3. Timer 3                                                       |     |

| 26.3.1. 16-bit Timer with Auto-Reload                               |     |

| 26.3.2. 8-bit Timers with Auto-Reload                               |     |

| 26.3.3. External Oscillator Capture Mode                            |     |

| 27. Programmable Counter Array                                      |     |

| 27.1. PCA Counter/Timer                                             |     |

| 27.2. PCA0 Interrupt Sources                                        |     |

| 27.3. Capture/Compare Modules                                       |     |

| 27.3.1. Edge-triggered Capture Mode                                 |     |

| 27.3.2. Software Timer (Compare) Mode                               |     |

| 27.3.3. High-Speed Output Mode                                      |     |

| 27.3.4. Frequency Output Mode                                       |     |

| 27.3.5. 8-bit, 9-bit, 10-bit and 11-bit Pulse Width Modulator Modes |     |

| 27.3.5.1. 8-bit Pulse Width Modulator Mode                          |     |

| 27.3.5.2. 9/10/11-bit Pulse Width Modulator Mode                    |     |

| 27.3.6. 16-Bit Pulse Width Modulator Mode                           |     |

| 27.4. Watchdog Timer Mode                                           |     |

| 27.4.1. Watchdog Timer Operation                                    |     |

| 27.4.2. Watchdog Timer Usage                                        |     |

| 27.5. Register Descriptions for PCA0                                |     |

| 28. C2 Interface                                                    |     |

| 28.1. C2 Interface Registers                                        |     |

| 28.2. C2 Pin Sharing                                                |     |

| Document Change List                                                |     |

| Contact Information                                                 |     |

|                                                                     |     |

## 2. Ordering Information

The following features are common to all devices in this family:

- 50 MHz system clock and 50 MIPS throughput (peak)

- 4352 bytes of RAM (256 internal bytes and 4096 XRAM bytes)

- SMBus/I<sup>2</sup>C, Enhanced SPI, Enhanced UART

- Four Timers

- Six Programmable Counter Array channels

- Internal 24 MHz oscillator

- Internal Voltage Regulator

- 12-bit, 200 ksps ADC

- Internal Voltage Reference and Temperature Sensor

- Two Analog Comparators

Table 2.1 shows the feature that differentiate the devices in this family.

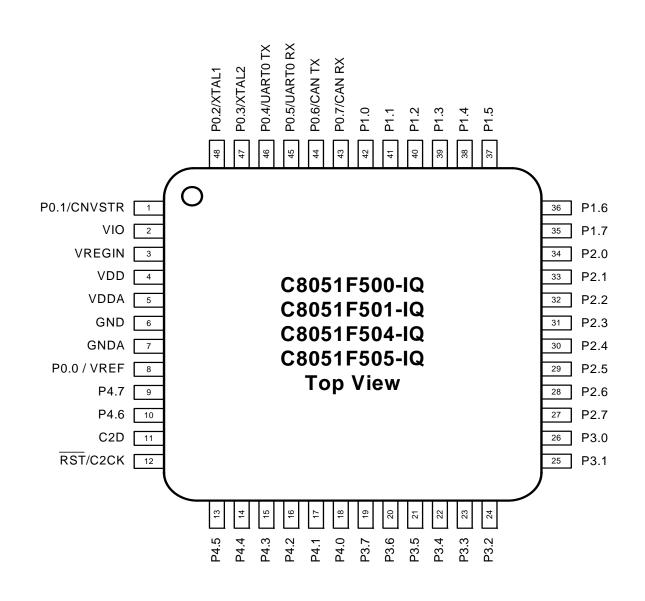

Figure 3.1. QFP-48 Pinout Diagram (Top View)

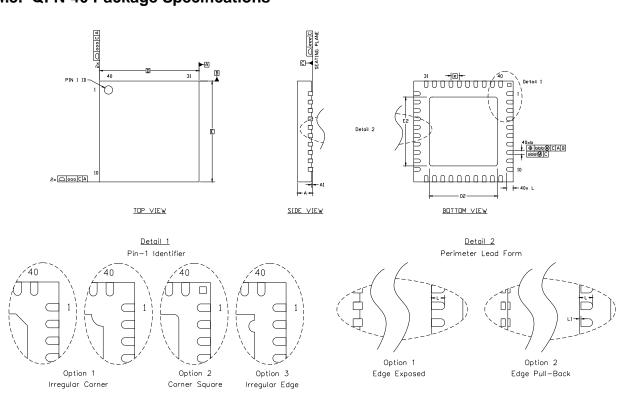

## 4.3. QFN-40 Package Specifications

Figure 4.5. Typical QFN-40 Package Drawing

| Dimension | Min      | Тур  | Max  | Dimension | Min  | Тур  | Мах  |

|-----------|----------|------|------|-----------|------|------|------|

| A         | 0.80     | 0.85 | 0.90 | E2        | 4.00 | 4.10 | 4.20 |

| A1        | 0.00     |      | 0.05 | L         | 0.35 | 0.40 | 0.45 |

| b         | 0.18     | 0.23 | 0.28 | L1        |      |      | 0.10 |

| D         | 6.00 BSC |      |      | aaa       |      |      | 0.10 |

| D2        | 4.00     | 4.10 | 4.20 | bbb       |      |      | 0.10 |

| е         | 0.50 BSC |      |      | ddd       |      |      | 0.05 |

| E         | 6.00 BSC |      |      | eee       |      |      | 0.08 |

### Table 4.5. QFN-40 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

**3.** This drawing conforms to JEDEC Solid State Outline MO-220, variation VJJD-5, except for features A, D2, and E2 which are toleranced per supplier designation.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

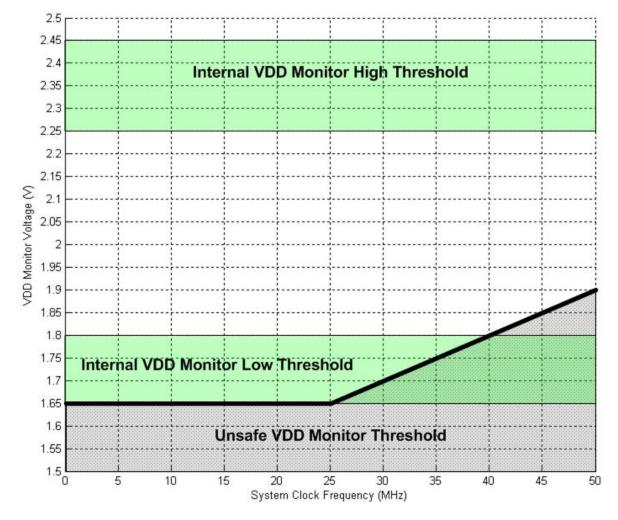

Figure 5.1. Minimum VDD Monitor Threshold vs. System Clock Frequency

**Note:** With system clock frequencies greater than 25 MHz, the VDD monitor level should be set to the high threshold (VDMLVL = 1b in SFR VDM0CN) to prevent undefined CPU operation. The high threshold should only be used with an external regulator powering VDD directly. See Figure 10.2 on page 85 for the recommended power supply connections.

## SFR Definition 9.2. CPT0MD: Comparator0 Mode Selection

| Bit   | 7 | 6 | 5      | 4      | 3 | 2 | 1    | 0       |

|-------|---|---|--------|--------|---|---|------|---------|

| Name  |   |   | CP0RIE | CP0FIE |   |   | CP0M | ID[1:0] |

| Туре  | R | R | R/W    | R/W    | R | R | R/W  |         |

| Reset | 0 | 0 | 0      | 0      | 0 | 0 | 1    | 0       |

### SFR Address = 0x9B; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                                                                                                                                            |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b, Write = Don't Care.                                                                                                                                                                                                                                     |

| 5   | CP0RIE     | Comparator0 Rising-Edge Interrupt Enable.<br>0: Comparator0 Rising-edge interrupt disabled.                                                                                                                                                                         |

|     |            | 1: Comparator0 Rising-edge interrupt enabled.                                                                                                                                                                                                                       |

| 4   | CP0FIE     | Comparator0 Falling-Edge Interrupt Enable.<br>0: Comparator0 Falling-edge interrupt disabled.<br>1: Comparator0 Falling-edge interrupt enabled.                                                                                                                     |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                                                                                                                                                                                                                     |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select.<br>These bits affect the response time and power consumption for Comparator0.<br>00: Mode 0 (Fastest Response Time, Highest Power Consumption)<br>01: Mode 1<br>10: Mode 2<br>11: Mode 3 (Slowest Response Time, Lowest Power Consumption) |

## SFR Definition 9.6. CPT1MX: Comparator1 MUX Selection

| Bit   | 7             | 6                                         | 5                | 4         | 3          | 2   | 1       | 0 |  |  |

|-------|---------------|-------------------------------------------|------------------|-----------|------------|-----|---------|---|--|--|

| Nam   | е             | CMX1                                      | N[3:0]           |           |            | CMX | 1P[3:0] | • |  |  |

| Туре  | e             | R/                                        | W                |           |            | R/W |         |   |  |  |

| Rese  | et 0          | 1                                         | 1                | 1         | 0          | 1   | 1       | 1 |  |  |

| SFR A | Address = 0x9 | <br>F: SER Page                           | - 0x00           |           |            |     |         |   |  |  |

| Bit   | Name          |                                           | - 0,00           |           | Function   |     |         |   |  |  |

| 7:4   | CMX1N[3:0]    | Comparator1 Negative Input MUX Selection. |                  |           |            |     |         |   |  |  |

|       |               | 0000:                                     | P0.1             | -         |            |     |         |   |  |  |

|       |               | 0001:                                     | P0.3             |           |            |     |         |   |  |  |

|       |               | 0010:                                     | P0.              |           |            |     |         |   |  |  |

|       |               | 0011:                                     | P0.1             |           |            |     |         |   |  |  |

|       |               | 0100:                                     | P1. <sup>-</sup> | 1         |            |     |         |   |  |  |

|       |               | 0101:                                     | P1.3             | 3         |            |     |         |   |  |  |

|       |               | 0110:                                     | P1.              | 5         |            |     |         |   |  |  |

|       |               | 0111:                                     | P1.              | 7         |            |     |         |   |  |  |

|       |               | 1000:                                     | P2.1             | 1         |            |     |         |   |  |  |

|       |               | 1001:                                     | P2.3             | 3         |            |     |         |   |  |  |

|       |               | 1010:                                     | P2.              | 5         |            |     |         |   |  |  |

|       |               | 1011:                                     | P2.1             |           |            |     |         |   |  |  |

|       |               | 1100–1111:                                | Nor              | ne        |            |     |         |   |  |  |

| 3:0   | CMX1P[3:0]    | Comparato                                 | r1 Positive      | Input MUX | Selection. |     |         |   |  |  |

|       |               | 0000:                                     | P0.0             | 0         |            |     |         |   |  |  |

|       |               | 0001:                                     | P0.2             | 2         |            |     |         |   |  |  |

|       |               | 0010:                                     | P0.4             | 4         |            |     |         |   |  |  |

|       |               | 0011:                                     | P0.0             |           |            |     |         |   |  |  |

|       |               | 0100:                                     | P1.0             |           |            |     |         |   |  |  |

|       |               | 0101:                                     | P1.2             |           |            |     |         |   |  |  |

|       |               | 0110:                                     | P1.4             |           |            |     |         |   |  |  |

|       |               | 0111:                                     | P1.0             |           |            |     |         |   |  |  |

|       |               | 1000:                                     | P2.0             |           |            |     |         |   |  |  |

|       |               | 1001:                                     | P2.2             |           |            |     |         |   |  |  |

|       |               | 1010:                                     | P2.4             |           |            |     |         |   |  |  |

|       |               | 1011:                                     | P2.0             |           |            |     |         |   |  |  |

|       |               | 1100–1111:                                | Nor              | ne        |            |     |         |   |  |  |

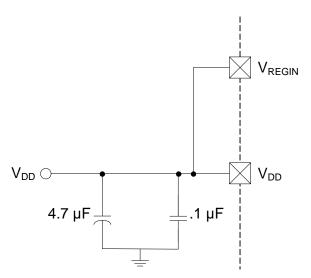

Figure 10.2. External Capacitors for Voltage Regulator Input/Output— Regulator Disabled

## SFR Definition 10.1. REG0CN: Regulator Control

| Bit   | 7      | 6        | 5 | 4      | 3 | 2 | 1 | 0       |

|-------|--------|----------|---|--------|---|---|---|---------|

| Name  | REGDIS | Reserved |   | REG0MD |   |   |   | DROPOUT |

| Туре  | R/W    | R/W      | R | R/W    | R | R | R | R       |

| Reset | 0      | 1        | 0 | 1      | 0 | 0 | 0 | 0       |

SFR Address = 0xC9; SFR Page = 0x00

| Bit | Name     | Function                                                      |  |  |  |  |

|-----|----------|---------------------------------------------------------------|--|--|--|--|

| 7   | REGDIS   | Voltage Regulator Disable Bit.                                |  |  |  |  |

|     |          | 0: Voltage Regulator Enabled<br>1: Voltage Regulator Disabled |  |  |  |  |

| 6   | Reserved | ead = 1b; Must Write 1b.                                      |  |  |  |  |

| 5   | Unused   | Read = 0b; Write = Don't Care.                                |  |  |  |  |

| 4   | REG0MD   | Voltage Regulator Mode Select Bit.                            |  |  |  |  |

|     |          | 0: Voltage Regulator Output is 2.1V.                          |  |  |  |  |

|     |          | 1: Voltage Regulator Output is 2.6V.                          |  |  |  |  |

| 3:1 | Unused   | Read = 000b. Write = Don't Care.                              |  |  |  |  |

| 0   | DROPOUT  | Voltage Regulator Dropout Indicator.                          |  |  |  |  |

|     |          | 0: Voltage Regulator is not in dropout                        |  |  |  |  |

|     |          | 1: Voltage Regulator is in or near dropout.                   |  |  |  |  |

## SFR Definition 11.3. SP: Stack Pointer

| Bit                                      | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------------------|---------|---|---|---|---|---|---|---|

| Name                                     | SP[7:0] |   |   |   |   |   |   |   |

| Туре                                     | R/W     |   |   |   |   |   |   |   |

| Reset                                    | 0       | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

| SFR Address = 0x81; SFR Page = All Pages |         |   |   |   |   |   |   |   |

| Bit | Name    | Function                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                                 |

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

## SFR Definition 11.4. ACC: Accumulator

| Bit    | 7           | 6           | 5             | 4            | 3        | 2 | 1 | 0 |  |

|--------|-------------|-------------|---------------|--------------|----------|---|---|---|--|

| Name   |             | ACC[7:0]    |               |              |          |   |   |   |  |

| Туре   |             | R/W         |               |              |          |   |   |   |  |

| Reset  | 0           | 0           | 0             | 0            | 0        | 0 | 0 | 0 |  |

| SFR Ad | dress = 0xE | 0; SFR Page | e = All Pages | ; Bit-Addres | sable    |   |   |   |  |

| Rit    | Name        |             |               |              | Function |   |   |   |  |

| Bit | Name     | Function                                                    |

|-----|----------|-------------------------------------------------------------|

| 7:0 | ACC[7:0] | Accumulator.                                                |

|     |          | This register is the accumulator for arithmetic operations. |

### SFR Definition 11.5. B: B Register

| Bit 7 6          | Э      | 4 | 3 | 2 | 1 | 0 |

|------------------|--------|---|---|---|---|---|

| Name             | B[7:0] |   |   |   |   |   |

| Туре             | R/W    |   |   |   |   |   |

| <b>Reset</b> 0 0 | 0      | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xF0; SFR Page = All Pages; Bit-Addressable

| Bit | Name   | Function                                                                        |

|-----|--------|---------------------------------------------------------------------------------|

| 7:0 | B[7:0] | B Register.                                                                     |

|     |        | This register serves as a second accumulator for certain arithmetic operations. |

## Table 13.3. Special Function Registers (Continued)

| SFRs are listed in alphabetical order. All undefined SFR locations are reserved |

|---------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------|

| Register | Address | Description                          | Page |  |

|----------|---------|--------------------------------------|------|--|

| IT01CF   | 0xE4    | INT0/INT1 Configuration              | 128  |  |

| LIN0ADR  | 0xD3    | LIN0 Address                         | 208  |  |

| LIN0CF   | 0xC9    | LIN0 Configuration                   | 208  |  |

| LIN0DAT  | 0xD2    | LIN0 Data                            | 209  |  |

| OSCICN   | 0xA1    | Internal Oscillator Control          | 168  |  |

| OSCICRS  | 0xA2    | Internal Oscillator Coarse Control   | 169  |  |

| OSCIFIN  | 0x9E    | Internal Oscillator Fine Calibration | 169  |  |

| OSCXCN   | 0x9F    | External Oscillator Control          | 173  |  |

| P0       | 0x80    | Port 0 Latch                         | 191  |  |

| POMASK   | 0xF2    | Port 0 Mask Configuration            | 187  |  |

| P0MAT    | 0xF1    | Port 0 Match Configuration           | 187  |  |

| POMDIN   | 0xF1    | Port 0 Input Mode Configuration      | 192  |  |

| P0MDOUT  | 0xA4    | Port 0 Output Mode Configuration     | 192  |  |

| P0SKIP   | 0xD4    | Port 0 Skip                          | 193  |  |

| P1       | 0x90    | Port 1 Latch                         | 193  |  |

| P1MASK   | 0xF4    | Port 1 Mask Configuration            | 188  |  |

| P1MAT    | 0xF3    | Port 1 Match Configuration           | 188  |  |

| P1MDIN   | 0xF2    | Port 1 Input Mode Configuration      | 194  |  |

| P1MDOUT  | 0xA5    | Port 1 Output Mode Configuration     | 194  |  |

| P1SKIP   | 0xD5    | Port 1 Skip                          | 195  |  |

| P2       | 0xA0    | Port 2 Latch                         | 195  |  |

| P2MASK   | 0xB2    | Port 2 Mask Configuration            | 189  |  |

| P2MAT    | 0xB1    | Port 2 Match Configuration           | 189  |  |

| P2MDIN   | 0xF3    | Port 2 Input Mode Configuration      | 196  |  |

| P2MDOUT  | 0xA6    | Port 2 Output Mode Configuration     | 196  |  |

| P2SKIP   | 0xD6    | Port 2 Skip                          | 197  |  |

| P3       | 0xB0    | Port 3 Latch                         | 197  |  |

| P3MASK   | 0xAF    | Port 3 Mask Configuration            | 190  |  |

| P3MAT    | 0xAE    | Port 3 Match Configuration           | 190  |  |

| P3MDIN   | 0xF4    | Port 3 Input Mode Configuration      | 198  |  |

| P3MDOUT  | 0xAE    | Port 3 Output Mode Configuration     |      |  |

| P3SKIP   | 0xD7    | Port 3 Skip                          | 199  |  |

| P4       | 0xB5    | Port 4 Latch                         | 199  |  |

| P4MDOUT  | 0xAF    | Port 4 Output Mode Configuration     | 200  |  |

| PCA0CN   | 0xD8    | PCA Control                          | 300  |  |

| PCA0CPH0 | 0xFC    | PCA Capture 0 High                   | 305  |  |

## SFR Definition 14.2. IP: Interrupt Priority

| Bit   | 7           | 6                                                                                                                                                                                                         | 5                                                                                                                                                                                                                                                               | 4                              | 3              | 2            | 1   | 0   |

|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|--------------|-----|-----|

| Nam   | e           | PSPI0                                                                                                                                                                                                     | PT2                                                                                                                                                                                                                                                             | PS0                            | PT1            | PX1          | PT0 | PX0 |

| Туре  | , R         | R/W                                                                                                                                                                                                       | R/W                                                                                                                                                                                                                                                             | R/W                            | R/W            | R/W          | R/W | R/W |

| Rese  | et 1        | 0                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                               | 0                              | 0              | 0            | 0   | 0   |

| SFR A | Address = 0 | xB8; Bit-Addres                                                                                                                                                                                           | sable; SFR                                                                                                                                                                                                                                                      | Page = All F                   | Pages          |              |     |     |

| Bit   | Name        |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                 |                                | Function       |              |     |     |

| 7     | Unused      | Read = 1b, W                                                                                                                                                                                              | rite = Don't (                                                                                                                                                                                                                                                  | Care.                          |                |              |     |     |

| 6     | PSPI0       | Serial Periph<br>This bit sets th<br>0: SPI0 interru<br>1: SPI0 interru                                                                                                                                   | ne priority of<br>opt set to low                                                                                                                                                                                                                                | the SPI0 int                   | errupt.<br>el. | ity Control. |     |     |

| 5     | PT2         | Timer 2 Intern<br>This bit sets th<br>0: Timer 2 inter<br>1: Timer 2 inter                                                                                                                                | ne priority of<br>errupt set to                                                                                                                                                                                                                                 | the Timer 2<br>low priority le | evel.          |              |     |     |

| 4     | PS0         | UART0 Interrupt Priority Control.<br>This bit sets the priority of the UART0 interrupt.<br>0: UART0 interrupt set to low priority level.<br>1: UART0 interrupt set to high priority level.                |                                                                                                                                                                                                                                                                 |                                |                |              |     |     |

| 3     | PT1         | This bit sets th<br>0: Timer 1 inte                                                                                                                                                                       | Timer 1 Interrupt Priority Control.This bit sets the priority of the Timer 1 interrupt.0: Timer 1 interrupt set to low priority level.1: Timer 1 interrupt set to high priority level.                                                                          |                                |                |              |     |     |

| 2     | PX1         | This bit sets th<br>0: External Int                                                                                                                                                                       | External Interrupt 1 Priority Control.<br>This bit sets the priority of the External Interrupt 1 interrupt.<br>0: External Interrupt 1 set to low priority level.<br>1: External Interrupt 1 set to high priority level.                                        |                                |                |              |     |     |

| 1     | PT0         | <b>Timer 0 Interrupt Priority Control.</b><br>This bit sets the priority of the Timer 0 interrupt.<br>0: Timer 0 interrupt set to low priority level.<br>1: Timer 0 interrupt set to high priority level. |                                                                                                                                                                                                                                                                 |                                |                |              |     |     |

| 0     | PX0         | This bit sets th<br>0: External Int                                                                                                                                                                       | : Timer 0 interrupt set to high priority level. External Interrupt 0 Priority Control. This bit sets the priority of the External Interrupt 0 interrupt. D: External Interrupt 0 set to low priority level. I: External Interrupt 0 set to high priority level. |                                |                |              |     |     |

#### 20.1.3. Interfacing Port I/O in a Multi-Voltage System

All Port I/O are capable of interfacing to digital logic operating at a supply voltage higher than VDD and less than 5.25 V. Connect the VIO pin to the voltage source of the interface logic.

### 20.2. Assigning Port I/O Pins to Analog and Digital Functions

Port I/O pins P0.0–P3.7 can be assigned to various analog, digital, and external interrupt functions. P4.0-P4.7 can be assigned to only digital functions. The Port pins assigned to analog functions should be configured for analog I/O, and Port pins assigned to digital or external interrupt functions should be configured for digital I/O.

#### 20.2.1. Assigning Port I/O Pins to Analog Functions

Table 20.1 shows all available analog functions that require Port I/O assignments. **Port pins selected for these analog functions should have their corresponding bit in PnSKIP set to 1.** This reserves the pin for use by the analog function and does not allow it to be claimed by the Crossbar. Table 20.1 shows the potential mapping of Port I/O to each analog function.

| Analog Function                                             | Potentially Assignable<br>Port Pins                                   | SFR(s) used for<br>Assignment |  |  |  |  |  |

|-------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------|--|--|--|--|--|

| ADC Input                                                   | P0.0–P3.7*                                                            | ADC0MX, PnSKIP                |  |  |  |  |  |

| Comparator0 or Compartor1 Input                             | P0.0-P2.7                                                             | CPT0MX, CPT1MX,<br>PnSKIP     |  |  |  |  |  |

| Voltage Reference (VREF0)                                   | P0.0                                                                  | REF0CN, PnSKIP                |  |  |  |  |  |

| External Oscillator in Crystal Mode (XTAL1)                 | P0.2                                                                  | OSCXCN, PnSKIP                |  |  |  |  |  |

| External Oscillator in RC, C, or Crystal Mode (XTAL2)       | P0.3                                                                  | OSCXCN, PnSKIP                |  |  |  |  |  |

| *Note: P3.1-P3.7 are only available on the 48-pin and 40-pi | *Note: P3.1–P3.7 are only available on the 48-pin and 40-pin packages |                               |  |  |  |  |  |

#### Table 20.1. Port I/O Assignment for Analog Functions

#### 20.2.2. Assigning Port I/O Pins to Digital Functions

Any Port pins not assigned to analog functions may be assigned to digital functions or used as GPIO. Most digital functions rely on the Crossbar for pin assignment; however, some digital functions bypass the Crossbar in a manner similar to the analog functions listed above. **Port pins used by these digital func-tions and any Port pins selected for use as GPIO should have their corresponding bit in PnSKIP set to 1.** Table 20.2 shows all available digital functions and the potential mapping of Port I/O to each digital function.

| Table 20.2. | Port I/O | Assignment | for Dig | gital Functions |

|-------------|----------|------------|---------|-----------------|

|-------------|----------|------------|---------|-----------------|

| Digital Function                                                                                        | Potentially Assignable Port Pins                                                                                                                                                                                                                                   | SFR(s) used for<br>Assignment     |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| UART0, SPI0, SMBus,<br>CAN0, LIN0, CP0, CP0A,<br>CP1, CP1A, SYSCLK, PCA0<br>(CEX0-5 and ECI), T0 or T1. | <ul> <li>Any Port pin available for assignment by the Crossbar. This includes P0.0–P4.7* pins which have their PnSKIP bit set to 0.</li> <li>Note: The Crossbar will always assign UART0 pins to P0.4 and P0.5 and always assign CAN0 to P0.6 and P0.7.</li> </ul> | XBR0, XBR1, XBR2                  |

| Any pin used for GPIO                                                                                   | P0.0–P4.7*                                                                                                                                                                                                                                                         | P0SKIP, P1SKIP,<br>P2SKIP, P3SKIP |

|                                                                                                         | only available on the 48-pin and 40pin packages. P4.1–l<br>o register is not available for P4.                                                                                                                                                                     | P4.7 are only available on        |

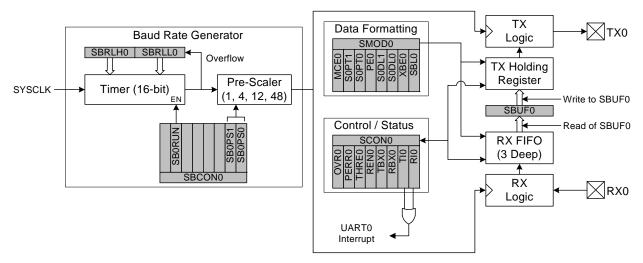

## 24. UART0

UART0 is an asynchronous, full duplex serial port offering a variety of data formatting options. A dedicated baud rate generator with a 16-bit timer and selectable prescaler is included, which can generate a wide range of baud rates (details in Section "24.1. Baud Rate Generator" on page 243). A received data FIFO allows UART0 to receive up to three data bytes before data is lost and an overflow occurs.

UART0 has six associated SFRs. Three are used for the Baud Rate Generator (SBCON0, SBRLH0, and SBRLL0), two are used for data formatting, control, and status functions (SCON0, SMOD0), and one is used to send and receive data (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Writes to SBUF0 always access the Transmit register. Reads of SBUF0 always access the buffered Receive register; it is not possible to read data from the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete). If additional bytes are available in the Receive FIFO, the RI0 bit cannot be cleared by software.

Figure 24.1. UART0 Block Diagram

### 24.1. Baud Rate Generator

The UART0 baud rate is generated by a dedicated 16-bit timer which runs from the controller's core clock (SYSCLK) and has prescaler options of 1, 4, 12, or 48. The timer and prescaler options combined allow for a wide selection of baud rates over many clock frequencies.

The baud rate generator is configured using three registers: SBCON0, SBRLH0, and SBRLL0. The UART0 Baud Rate Generator Control Register (SBCON0, SFR Definition 24.4) enables or disables the baud rate generator, selects the clock source for the baud rate generator, and selects the prescaler value for the timer. The baud rate generator must be enabled for UART0 to function. Registers SBRLH0 and SBRLL0 contain a 16-bit reload value for the dedicated 16-bit timer. The internal timer counts up from the reload value on every clock tick. On timer overflows (0xFFFF to 0x0000), the timer is reloaded. The baud rate for UART0 is defined in Equation 24.1, where "BRG Clock" is the baud rate generator's selected clock source. For reliable UART operation, it is recommended that the UART baud rate is not configured for baud rates faster than SYSCLK/16.

If the extra bit function is enabled (XBE0 = 1) and the parity function is disabled (PE0 = 0), the extra bit for the oldest byte in the FIFO can be read from the RBX0 bit (SCON0.2). If the extra bit function is not enabled, the value of the stop bit for the oldest FIFO byte will be presented in RBX0. When the parity function is enabled (PE0 = 1), hardware will check the received parity bit against the selected parity type (selected with S0PT[1:0]) when receiving data. If a byte with parity error is received, the PERR0 flag will be set to 1. This flag must be cleared by software. Note: when parity is enabled, the extra bit function is not available.

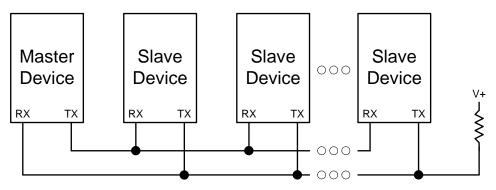

#### 24.3.3. Multiprocessor Communications

UART0 supports multiprocessor communication between a master processor and one or more slave processors by special use of the extra data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its extra bit is logic 1; in a data byte, the extra bit is always set to logic 0.

Setting the MCE0 bit (SMOD0.7) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the extra bit is logic 1 (RBX0 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned address. If the addresses match, the slave will clear its MCE0 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE0 bits set and do not generate interrupts on the reception of the following data byte(s) bits of the following data bytes, thereby ignoring the data. Once the entire message is received, the addressed slave resets its MCE0 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 24.6. UART Multi-Processor Mode Interconnect Diagram

## SFR Definition 24.3. SBUF0: Serial (UART0) Port Data Buffer

| Bit   | 7   | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|------------|---|---|---|---|---|---|

| Name  |     | SBUF0[7:0] |   |   |   |   |   |   |

| Туре  | R/W |            |   |   |   |   |   |   |

| Reset | 0   | 0          | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0x99; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                    |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SBUF0[7:0] | Serial Data Buffer Bits 7–0 (MSB–LSB).                                                                                                                                                                                                                                                                                      |

|     |            | This SFR accesses two registers; a transmit shift register and a receive latch register.<br>When data is written to SBUF0, it goes to the transmit shift register and is held for<br>serial transmission. Writing a byte to SBUF0 initiates the transmission. A read of<br>SBUF0 returns the contents of the receive latch. |

## SFR Definition 24.4. SBCON0: UART0 Baud Rate Generator Control

| Bit   | 7        | 6      | 5        | 4        | 3        | 2        | 1    | 0      |

|-------|----------|--------|----------|----------|----------|----------|------|--------|

| Name  | Reserved | SB0RUN | Reserved | Reserved | Reserved | Reserved | SB0P | S[1:0] |

| Туре  | R/W      | R/W    | R/W      | R/W      | R/W      | R/W      | R/   | W      |

| Reset | 0        | 0      | 0        | 0        | 0        | 0        | 0    | 0      |

SFR Address = 0xAB; SFR Page = 0x0F

| Bit | Name       | Function                                                                                     |

|-----|------------|----------------------------------------------------------------------------------------------|

| 7   | Reserved   | Read = 0b; Must Write 0b;                                                                    |

| 6   | SBORUN     | Baud Rate Generator Enable.                                                                  |

|     |            | 0: Baud Rate Generator disabled. UART0 will not function.<br>1: Baud Rate Generator enabled. |

| 5:2 | Reserved   | Read = 0000b; Must Write = 0000b;                                                            |

| 1:0 | SB0PS[1:0] |                                                                                              |

|     |            | 00: Prescaler = 12.<br>01: Prescaler = 4.<br>10: Prescaler = 48.<br>11: Prescaler = 1.       |

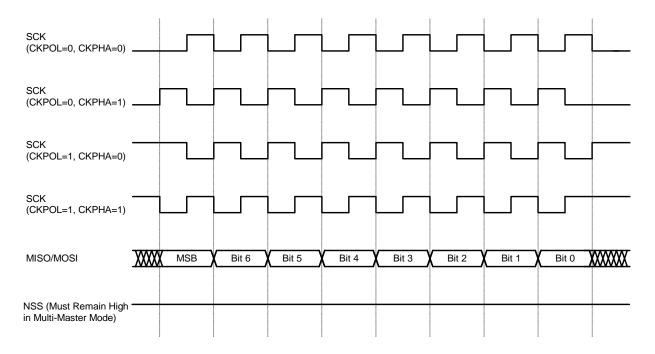

### 25.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 25.5. For slave mode, the clock and data relationships are shown in Figure 25.6 and Figure 25.7. CKPHA must be set to 0 on both the master and slave SPI when communicating between two of the following devices: C8051F04x, C8051F06x, C8051F12x, C8051F31x, C8051F32x, and C8051F33x.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 25.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

Figure 25.5. Master Mode Data/Clock Timing

| Parameter                | Description                                                   | Min                          | Max                     | Units |

|--------------------------|---------------------------------------------------------------|------------------------------|-------------------------|-------|

| Master Mod               | <b>e Timing</b> <sup>*</sup> (See Figure 25.8 and Figure 25.9 | ))                           | 1                       | 1     |

| т <sub>мскн</sub>        | SCK High Time                                                 | 1 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>MCKL</sub>        | SCK Low Time                                                  | 1 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>MIS</sub>         | MISO Valid to SCK Shift Edge                                  | 1 x T <sub>SYSCLK</sub> + 20 | —                       | ns    |

| Т <sub>МІН</sub>         | SCK Shift Edge to MISO Change                                 | 0                            | —                       | ns    |

| Slave Mode               | <b>Timing</b> <sup>*</sup> (See Figure 25.10 and Figure 25.1  | 1)                           |                         |       |

| T <sub>SE</sub>          | NSS Falling to First SCK Edge                                 | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SD</sub>          | Last SCK Edge to NSS Rising                                   | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SEZ</sub>         | NSS Falling to MISO Valid                                     | _                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SDZ</sub>         | NSS Rising to MISO High-Z                                     |                              | 4 x T <sub>SYSCLK</sub> | ns    |

| т <sub>скн</sub>         | SCK High Time                                                 | 5 x T <sub>SYSCLK</sub>      | —                       | ns    |

| Т <sub>СКL</sub>         | SCK Low Time                                                  | 5 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SIS</sub>         | MOSI Valid to SCK Sample Edge                                 | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SIH</sub>         | SCK Sample Edge to MOSI Change                                | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| т <sub>ѕон</sub>         | SCK Shift Edge to MISO Change                                 | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SLH</sub>         | Last SCK Edge to MISO Change<br>(CKPHA = 1 ONLY)              | 6 x T <sub>SYSCLK</sub>      | 8 x T <sub>SYSCLK</sub> | ns    |

| *Note: T <sub>SYSC</sub> | LK is equal to one period of the device system cl             | ock (SYSCLK).                |                         |       |

## Table 25.1. SPI Slave Timing Parameters

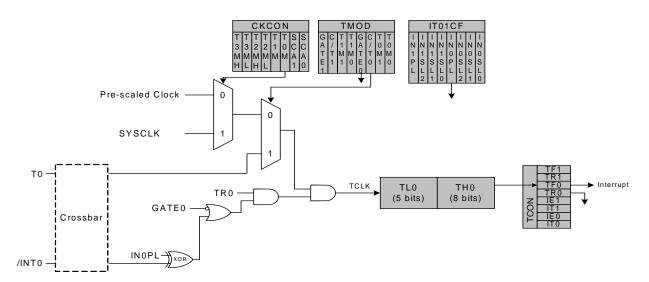

Figure 26.1. T0 Mode 0 Block Diagram

#### 26.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

#### 26.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal INT0 is active as defined by bit INOPL in register IT01CF (see Section "14.3. External Interrupts INT0 and INT1" on page 126 for details on the external input signals INT0 and INT1).

| T2MH | T2XCLK | TMR2H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK/12          |

| 0    | 1      | External Clock/8   |

| 1    | Х      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK/12          |

| 0    | 1      | External Clock/8   |

| 1    | Х      | SYSCLK             |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 26.5. Timer 2 8-Bit Mode Block Diagram

#### 26.2.3. External Oscillator Capture Mode

Capture Mode allows the external oscillator to be measured against the system clock. Timer 2 can be clocked from the system clock, or the system clock divided by 12, depending on the T2ML (CKCON.4), and T2XCLK bits. When a capture event is generated, the contents of Timer 2 (TMR2H:TMR2L) are loaded into the Timer 2 reload registers (TMR2RLH:TMR2RLL) and the TF2H flag is set. A capture event is generated by the falling edge of the clock source being measured, which is the external oscillator / 8. By recording the difference between two successive timer capture values, the external oscillator frequency can be determined with respect to the Timer 2 clock. The Timer 2 clock should be much faster than the capture clock to achieve an accurate reading. Timer 2 should be in 16-bit auto-reload mode when using Capture Mode.

For example, if T2ML = 1b and TF2CEN = 1b, Timer 2 will clock every SYSCLK and capture every external clock divided by 8. If the SYSCLK is 24 MHz and the difference between two successive captures is 5984, then the external clock frequency is as follows:

24 MHz/(5984/8) = 0.032086 MHz or 32.086 kHz

This mode allows software to determine the external oscillator frequency when an RC network or capacitor is used to generate the clock source.

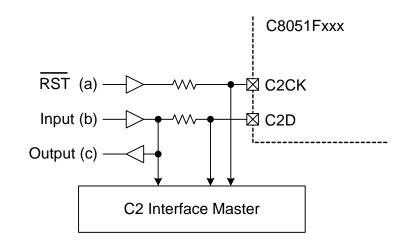

### 28.2. C2 Pin Sharing

The C2 protocol allows the C2 pins to be shared with user functions so that in-system debugging and Flash programming may be performed. This is possible because C2 communication is typically performed when the device is in the halt state, where all on-chip peripherals and user software are stalled. In this halted state, the C2 interface can safely 'borrow' the C2CK (RST) and C2D pins. In most applications, external resistors are required to isolate C2 interface traffic from the user application. A typical isolation configuration is shown in Figure 28.1.

Figure 28.1. Typical C2 Pin Sharing

The configuration in Figure 28.1 assumes the following:

- 1. The user input (b) cannot change state while the target device is halted.

- 2. The  $\overline{\text{RST}}$  pin on the target device is used as an input only.

Additional resistors may be necessary depending on the specific application.