Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 4.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 25x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f507-im |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5. Electrical Characteristics

## 5.1. Absolute Maximum Specifications

#### Table 5.1. Absolute Maximum Ratings

| Parameter                                                                                                                                                                                               | Conditions | Min  | Тур | Max                   | Units |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|-----|-----------------------|-------|--|

| Ambient Temperature under Bias                                                                                                                                                                          |            | -55  | _   | 135                   | °C    |  |

| Storage Temperature                                                                                                                                                                                     |            | -65  | _   | 150                   | °C    |  |

| Voltage on V <sub>REGIN</sub> with Respect to GND                                                                                                                                                       |            | -0.3 | _   | 5.5                   | V     |  |

| Voltage on V <sub>DD</sub> with Respect to GND                                                                                                                                                          |            | -0.3 |     | 2.8                   | V     |  |

| Voltage on VDDA with Respect to GND                                                                                                                                                                     |            | -0.3 |     | 2.8                   | V     |  |

| Voltage on V <sub>IO</sub> with Respect to GND                                                                                                                                                          |            | -0.3 |     | 5.5                   | V     |  |

| Voltage on any Port I/O Pin or $\overline{RST}$ with Respect to GND                                                                                                                                     |            | -0.3 | _   | V <sub>IO</sub> + 0.3 | V     |  |

| Maximum Total Current through V <sub>REGIN</sub> or GND                                                                                                                                                 |            |      | _   | 500                   | mA    |  |

| Maximum Output Current Sunk by $\overline{RST}$ or any Port Pin                                                                                                                                         |            | _    | _   | 100                   | mA    |  |

| Maximum Output Current Sourced by any Port Pin                                                                                                                                                          |            |      | _   | 100                   | mA    |  |

| Maximum Output Current Sourced by any Port Pin       —       —       100       mA         Note:       Stresses outside of the range of the "Absolute Maximum Ratings" may cause permanent damage to the |            |      |     |                       |       |  |

ote: Stresses outside of the range of the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

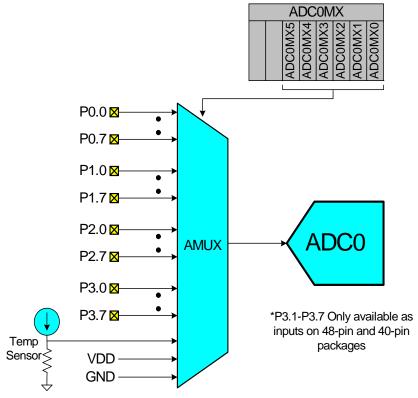

### 6.5. ADC0 Analog Multiplexer

ADC0 includes an analog multiplexer to enable multiple analog input sources. Any of the following may be selected as an input: P0.0–P3.7, the on-chip temperature sensor, the core power supply ( $V_{DD}$ ), or ground (GND). **ADC0 is single-ended and all signals measured are with respect to GND.** The ADC0 input channels are selected using the ADC0MX register as described in SFR Definition 6.13.

Figure 6.8. ADC0 Multiplexer Block Diagram

**Important Note About ADC0 Input Configuration:** Port pins selected as ADC0 inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set to 0 the corresponding bit in register PnMDIN. To force the Crossbar to skip a Port pin, set to 1 the corresponding bit in register PnSKIP. See Section "20. Port Input/Output" on page 177 for more Port I/O configuration details.

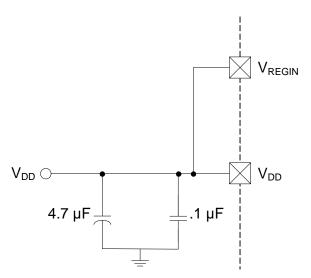

Figure 10.2. External Capacitors for Voltage Regulator Input/Output— Regulator Disabled

## SFR Definition 10.1. REG0CN: Regulator Control

| Bit   | 7      | 6        | 5 | 4      | 3 | 2 | 1 | 0       |

|-------|--------|----------|---|--------|---|---|---|---------|

| Name  | REGDIS | Reserved |   | REG0MD |   |   |   | DROPOUT |

| Туре  | R/W    | R/W      | R | R/W    | R | R | R | R       |

| Reset | 0      | 1        | 0 | 1      | 0 | 0 | 0 | 0       |

SFR Address = 0xC9; SFR Page = 0x00

| Bit | Name     | Function                                                      |

|-----|----------|---------------------------------------------------------------|

| 7   | REGDIS   | Voltage Regulator Disable Bit.                                |

|     |          | 0: Voltage Regulator Enabled<br>1: Voltage Regulator Disabled |

| 6   | Reserved | Read = 1b; Must Write 1b.                                     |

| 5   | Unused   | Read = 0b; Write = Don't Care.                                |

| 4   | REG0MD   | Voltage Regulator Mode Select Bit.                            |

|     |          | 0: Voltage Regulator Output is 2.1V.                          |

|     |          | 1: Voltage Regulator Output is 2.6V.                          |

| 3:1 | Unused   | Read = 000b. Write = Don't Care.                              |

| 0   | DROPOUT  | Voltage Regulator Dropout Indicator.                          |

|     |          | 0: Voltage Regulator is not in dropout                        |

|     |          | 1: Voltage Regulator is in or near dropout.                   |

## SFR Definition 11.6. PSW: Program Status Word

| Bit   | 7          | 6                                                            | 5                                                                                                                                                                                                         | 4               | 3             | 2             | 1              | 0             |

|-------|------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|---------------|----------------|---------------|

| Name  | e CY       | AC F0 RS[1:0] C                                              |                                                                                                                                                                                                           |                 | OV            | F1            | PARITY         |               |

| Туре  | R/W        | R/W R/W R/W                                                  |                                                                                                                                                                                                           |                 | W             | R/W           | R/W            | R             |

| Rese  | t 0        | 0 0 0 0 0 0                                                  |                                                                                                                                                                                                           |                 |               | 0             | 0              |               |

| SFR A | ddress = 0 | D0; SFR Page                                                 | e = All Pages                                                                                                                                                                                             | :<br>Bit-Addres | sable         |               |                |               |

| Bit   | Name       |                                                              |                                                                                                                                                                                                           |                 | Function      |               |                |               |

| 7     | CY         | Carry Flag.                                                  |                                                                                                                                                                                                           |                 |               |               |                |               |

|       |            | This bit is set row (subtraction                             |                                                                                                                                                                                                           |                 | •             |               |                | n) or a bor-  |

| 6     | AC         | Auxiliary Car                                                | ry Flag.                                                                                                                                                                                                  |                 |               |               |                |               |

|       |            | borrow from (s                                               | This bit is set when the last arithmetic operation resulted in a carry into (addition) or a porrow from (subtraction) the high order nibble. It is cleared to logic 0 by all other arithmetic operations. |                 |               |               |                |               |

| 5     | F0         | User Flag 0.                                                 | Jser Flag 0.                                                                                                                                                                                              |                 |               |               |                |               |

|       |            | This is a bit-ad                                             | This is a bit-addressable, general purpose flag for use under software control.                                                                                                                           |                 |               |               |                |               |

| 4:3   | RS[1:0]    | Register Ban                                                 | k Select.                                                                                                                                                                                                 |                 |               |               |                |               |

|       |            | These bits sel                                               |                                                                                                                                                                                                           | -               | s used durin  | g register ac | cesses.        |               |

|       |            | 00: Bank 0, A<br>01: Bank 1, A                               |                                                                                                                                                                                                           |                 |               |               |                |               |

|       |            | 10: Bank 2, A                                                |                                                                                                                                                                                                           |                 |               |               |                |               |

|       |            | 11: Bank 3, Ao                                               | ddresses 0x                                                                                                                                                                                               | 18-0x1F         |               |               |                |               |

| 2     | OV         | <b>Overflow Flag</b>                                         | g.                                                                                                                                                                                                        |                 |               |               |                |               |

|       |            | This bit is set                                              |                                                                                                                                                                                                           | -               |               |               |                |               |

|       |            | <ul> <li>An ADD, A</li> <li>A MUL ins<sup>-</sup></li> </ul> |                                                                                                                                                                                                           |                 |               |               |                |               |

|       |            | <ul> <li>A MOL INS</li> <li>A DIV instr</li> </ul>           |                                                                                                                                                                                                           |                 | ,             | •             | an 200).       |               |

|       |            | The OV bit is                                                |                                                                                                                                                                                                           |                 | •             |               | d DIV instruc  | ctions in all |

|       | -          | other cases.                                                 |                                                                                                                                                                                                           |                 |               |               |                |               |

| 1     | F1         | User Flag 1.                                                 |                                                                                                                                                                                                           |                 |               |               | 4              |               |

|       |            | This is a bit-ad                                             | Juressable, (                                                                                                                                                                                             | general purp    | use hag for   | use under so  | ntware contr   | 01.           |

| 0     | PARITY     | Parity Flag.                                                 |                                                                                                                                                                                                           |                 | oight hite in | the accurry   | lator is odd a | and closered  |

|       |            | This bit is set t<br>if the sum is e                         | -                                                                                                                                                                                                         |                 | eigni bits in | the accumu    | 18 000 8       |               |

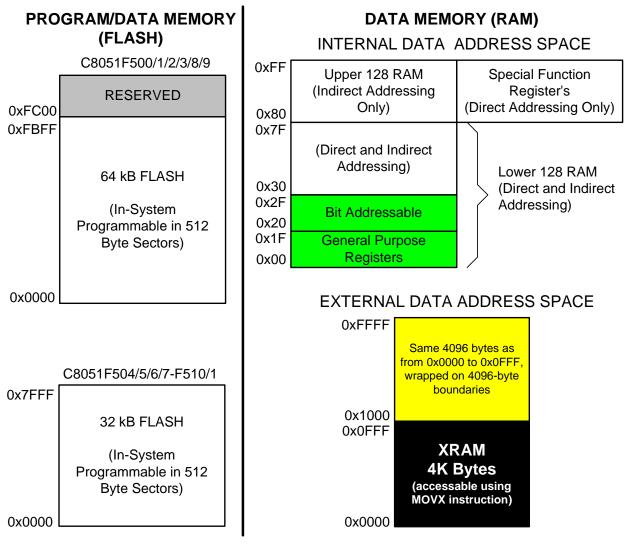

# 12. Memory Organization

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The memory organization is shown in Figure 12.1

Figure 12.1. C8051F50x/F51x Memory Map

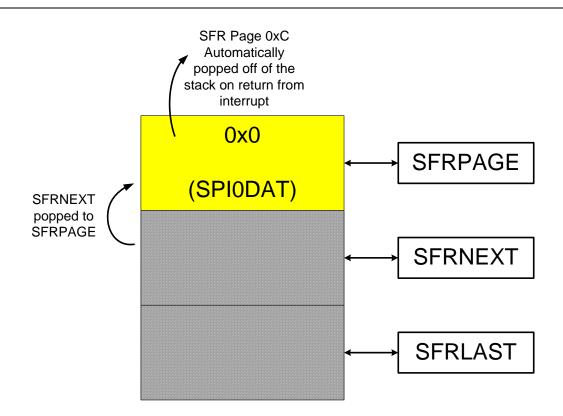

Figure 13.6. SFR Page Stack Upon Return From CAN0 Interrupt

In the example above, all three bytes in the SFR Page Stack are accessible via the SFRPAGE, SFRNEXT, and SFRLAST special function registers. If the stack is altered while servicing an interrupt, it is possible to return to a different SFR Page upon interrupt exit than selected prior to the interrupt call. Direct access to the SFR Page stack can be useful to enable real-time operating systems to control and manage context switching between multiple tasks.

Push operations on the SFR Page Stack only occur on interrupt service, and pop operations only occur on interrupt exit (execution on the RETI instruction). The automatic switching of the SFRPAGE and operation of the SFR Page Stack as described above can be disabled in software by clearing the SFR Automatic Page Enable Bit (SFRPGEN) in the SFR Page Control Register (SFR0CN). See SFR Definition 13.1.

### Table 14.1. Interrupt Summary

| Interrupt Source               | Interrupt<br>Vector | Priority<br>Order | Pending Flag                                                               | Bit addressable? | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|--------------------------------|---------------------|-------------------|----------------------------------------------------------------------------|------------------|----------------|--------------------|---------------------|

| Reset                          | 0x0000              | Тор               | None                                                                       | N/A              | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0<br>(INT0) | 0x0003              | 0                 | IE0 (TCON.1)                                                               | Y                | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow               | 0x000B              | 1                 | TF0 (TCON.5)                                                               | Y                | Y              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1<br>(INT1) | 0x0013              | 2                 | IE1 (TCON.3)                                                               | Y                | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow               | 0x001B              | 3                 | TF1 (TCON.7)                                                               | Y                | Y              | ET1 (IE.3)         | · · · ·             |

| UART0                          | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y                | N              | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow               | 0x002B              | 5                 | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y                | N              | ET2 (IE.5)         | PT2 (IP.5)          |

| SPIO                           | 0x0033              | 6                 | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y                | N              | ESPI0<br>(IE.6)    | PSPI0<br>(IP.6)     |

| SMB0                           | 0x003B              | 7                 | SI (SMB0CN.0)                                                              | Y                | N              | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| ADC0 Window Com-<br>pare       | 0x0043              | 8                 | AD0WINT<br>(ADC0CN.3)                                                      | Y                | N              | EWADC0<br>(EIE1.1) | PWADC0<br>(EIP1.1)  |

| ADC0 Conversion<br>Complete    | 0x004B              | 9                 | AD0INT (ADC0CN.5)                                                          | Y                | N              | EADC0<br>(EIE1.2)  | PADC0<br>(EIP1.2)   |

| Programmable<br>Counter Array  | 0x0053              | 10                | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)<br>COVF (PCA0PWM.6)                       | Y                | N              | EPCA0<br>(EIE1.3)  | PPCA0<br>(EIP1.3)   |

| Comparator0                    | 0x005B              | 11                | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | Ν                | N              | ECP0<br>(EIE1.4)   | PCP0<br>(EIP1.4)    |

| Comparator1                    | 0x0063              | 12                | CP1FIF (CPT1CN.4)<br>CP1RIF (CPT1CN.5)                                     | Ζ                | N              | ECP1<br>(EIE1.5)   | PCP1<br>(EIP1.5)    |

| Timer 3 Overflow               | 0x006B              | 13                | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | Ν                | Ν              | ET3<br>(EIE1.6)    | PT3<br>(EIP1.6)     |

| LINO                           | 0x0073              | 14                | LIN0INT (LINST.3)                                                          | Ν                | N*             | ELIN0<br>(EIE1.7)  | PLIN0<br>(EIP1.7)   |

| Voltage Regulator<br>Dropout   | 0x007B              | 15                | N/A                                                                        | N/A              | N/A            | EREG0<br>(EIE2.0)  | PREG0<br>(EIP2.0)   |

| CANO                           | 0x0083              | 16                | CAN0INT<br>(CAN0CN.7)                                                      | Ν                | Y              | ECAN0<br>(EIE2.1)  | PCAN0<br>(EIP2.1)   |

| Port Match                     | 0x008B              | 17                | None                                                                       | N/A              | N/A            | EMAT<br>(EIE2.2)   | PMAT<br>(EIP2.2)    |

## SFR Definition 14.7. IT01CF: INT0/INT1 Configuration

| Bit   | 7     | 6   | 5          | 4 | 3     | 2 | 1          | 0 |

|-------|-------|-----|------------|---|-------|---|------------|---|

| Name  | IN1PL |     | IN1SL[2:0] |   | IN0PL |   | IN0SL[2:0] |   |

| Туре  | R/W   | R/W |            |   | R/W   |   | R/W        |   |

| Reset | 0     | 0   | 0          | 0 | 0     | 0 | 0          | 0 |

#### SFR Address = 0xE4; SFR Page = 0x0F

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IN1PL      | INT1 Polarity.<br>0: INT1 input is active low.<br>1: INT1 input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6:4 | IN1SL[2:0] | INT1 Port Pin Selection Bits.<br>These bits select which Port pin is assigned to INT1. Note that this pin assignment is<br>independent of the Crossbar; INT1 will monitor the assigned Port pin without disturb-<br>ing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar<br>will not assign the Port pin to a peripheral if it is configured to skip the selected pin.<br>000: Select P1.0<br>001: Select P1.1<br>010: Select P1.2<br>011: Select P1.3<br>100: Select P1.4<br>101: Select P1.5<br>110: Select P1.6<br>111: Select P1.7 |

| 3   | IN0PL      | INTO Polarity.<br>0: INTO input is active low.<br>1: INTO input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2:0 | IN0SL[2:0] | <b>INTO</b> Port Pin Selection Bits.<br>These bits select which Port pin is assigned to INTO. Note that this pin assignment is independent of the Crossbar; INTO will monitor the assigned Port pin without disturbing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar will not assign the Port pin to a peripheral if it is configured to skip the selected pin.<br>000: Select P1.0<br>001: Select P1.1<br>010: Select P1.2<br>011: Select P1.3<br>100: Select P1.4<br>101: Select P1.5<br>110: Select P1.6<br>111: Select P1.7     |

| Multiplexed Mode |          |  |  |  |  |

|------------------|----------|--|--|--|--|

| Signal Name      | Port Pin |  |  |  |  |

| RD               | P1.6     |  |  |  |  |

| WR               | P1.7     |  |  |  |  |

| ALE              | P1.5     |  |  |  |  |

| D0/A0            | P4.0     |  |  |  |  |

| D1/A1            | P4.1     |  |  |  |  |

| D2/A2            | P4.2     |  |  |  |  |

| D3/A3            | P4.3     |  |  |  |  |

| D4/A4            | P4.4     |  |  |  |  |

| D5/A5            | P4.5     |  |  |  |  |

| D6/A6            | P4.6     |  |  |  |  |

| D7/A7            | P4.7     |  |  |  |  |

| A8               | P3.0     |  |  |  |  |

| A9               | P3.1     |  |  |  |  |

| A10              | P3.2     |  |  |  |  |

| A11              | P3.3     |  |  |  |  |

| A12              | P3.4     |  |  |  |  |

| A13              | P3.5     |  |  |  |  |

| A14              | P3.6     |  |  |  |  |

| A15              | P3.7     |  |  |  |  |

| —                | _        |  |  |  |  |

| —                | —        |  |  |  |  |

| —                | —        |  |  |  |  |

| —                | _        |  |  |  |  |

| —                | _        |  |  |  |  |

| —                | —        |  |  |  |  |

| —                | _        |  |  |  |  |

## Table 18.1. EMIF Pinout (C8051F500/1/4/5)

| Non Multiplexed Mode |          |  |  |  |  |

|----------------------|----------|--|--|--|--|

| Signal Name          | Port Pin |  |  |  |  |

| RD                   | P1.6     |  |  |  |  |

| WR                   | P1.7     |  |  |  |  |

| D0                   | P4.0     |  |  |  |  |

| D1                   | P4.1     |  |  |  |  |

| D2                   | P4.2     |  |  |  |  |

| D3                   | P4.3     |  |  |  |  |

| D4                   | P4.4     |  |  |  |  |

| D5                   | P4.5     |  |  |  |  |

| D6                   | P4.6     |  |  |  |  |

| D7                   | P4.7     |  |  |  |  |

| A0                   | P3.0     |  |  |  |  |

| A1                   | P3.1     |  |  |  |  |

| A2                   | P3.2     |  |  |  |  |

| A3                   | P3.3     |  |  |  |  |

| A4                   | P3.4     |  |  |  |  |

| A5                   | P3.5     |  |  |  |  |

| A6                   | P3.6     |  |  |  |  |

| A7                   | P3.7     |  |  |  |  |

| A8                   | P2.0     |  |  |  |  |

| A9                   | P2.1     |  |  |  |  |

| A10                  | P2.2     |  |  |  |  |

| A11                  | P2.3     |  |  |  |  |

| A12                  | P2.4     |  |  |  |  |

| A13                  | P2.5     |  |  |  |  |

| A14                  | P2.6     |  |  |  |  |

| A15                  | P2.7     |  |  |  |  |

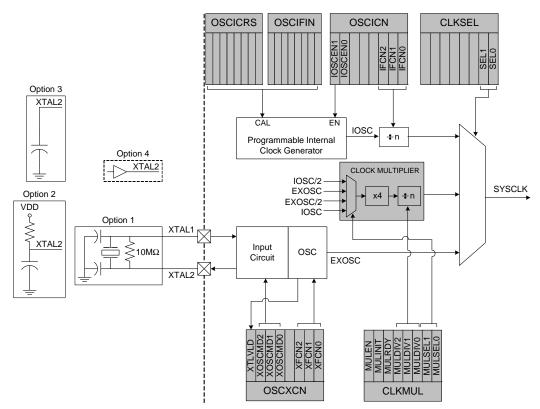

## **19. Oscillators and Clock Selection**

C8051F50x/F51x devices include a programmable internal high-frequency oscillator, an external oscillator drive circuit, and a clock multiplier. The internal oscillator can be enabled/disabled and calibrated using the OSCICN, OSCICRS, and OSCIFIN registers, as shown in Figure 19.1. The system clock can be sourced by the external oscillator circuit or the internal oscillator. The clock multiplier can produce three possible base outputs which can be scaled by a programmable factor of 1, 2/3, 2/4 (or 1/2), 2/5, 2/6 (or 1/3), or 2/7: Internal Oscillator x 2, Internal Oscillator x 4.

Figure 19.1. Oscillator Options

## 19.1. System Clock Selection

The CLKSL[1:0] bits in register CLKSEL select which oscillator source is used as the system clock. CLKSL[1:0] must be set to 01b for the system clock to run from the external oscillator; however the external oscillator may still clock certain peripherals (timers, PCA) when the internal oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal oscillator, external oscillator, and Clock Multiplier so long as the selected clock source is enabled and has settled.

The internal oscillator requires little start-up time and may be selected as the system clock immediately following the register write which enables the oscillator. The external RC and C modes also typically require no startup time.

External crystals and ceramic resonators however, typically require a start-up time before they are settled and ready for use. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to 1 by hardware when the external crystal or ceramic resonator is settled. In crystal mode, to avoid reading a false XTLVLD, software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD.

### **19.2.** Programmable Internal Oscillator

All C8051F50x/F51x devices include a programmable internal high-frequency oscillator that defaults as the system clock after a system reset. The internal oscillator period can be adjusted via the OSCICRS and OSCIFIN registers defined in SFR Definition 19.3 and SFR Definition 19.4. On C8051F50x/F51x devices, OSCICRS and OSCIFIN are factory calibrated to obtain a 24 MHz base frequency. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, 8, 16, 32, 64, or 128, as defined by the IFCN bits in register OSCICN. The divide value defaults to 128 following a reset.

#### 19.2.1. Internal Oscillator Suspend Mode

When software writes a logic 1 to SUSPEND (OSCICN.5), the internal oscillator is suspended. If the system clock is derived from the internal oscillator, the input clock to the peripheral or CIP-51 will be stopped until one of the following events occur:

- Port 0 Match Event.

- Port 1 Match Event.

- Port 2 Match Event.

- Port 3 Match Event.

- Comparator 0 enabled and output is logic 0.

When one of the oscillator awakening events occur, the internal oscillator, CIP-51, and affected peripherals resume normal operation, regardless of whether the event also causes an interrupt. The CPU resumes execution at the instruction following the write to SUSPEND.

Note: When entering suspend mode, firmware must set the ZTCEN bit in REF0CN (SFR Definition 8.1).

### 20.5. Port Match

Port match functionality allows system events to be triggered by a logic value change on P0, P1, P2 or P3. A software controlled value stored in the PnMATCH registers specifies the expected or normal logic values of P0, P1, P2, and P3. A Port mismatch event occurs if the logic levels of the Port's input pins no longer match the software controlled value. This allows Software to be notified if a certain change or pattern occurs on P0, P1, P2, or P3 input pins regardless of the XBRn settings.

The PnMASK registers can be used to individually select which of the port pins should be compared against the PnMATCH registers. A Port mismatch event is generated if (Pn & PnMASK) does not equal (PnMATCH & PnMASK), where n is 0, 1, 2 or 3

A Port mismatch event may be used to generate an interrupt or wake the device from a low power mode, such as IDLE or SUSPEND. See the Interrupts and Power Options chapters for more details on interrupt and wake-up sources.

| Bit   | 7              | 6           | 5                 | 4 | 3 | 2 | 1 | 0 |  |

|-------|----------------|-------------|-------------------|---|---|---|---|---|--|

| Nam   | e              | POMAŠK[7:0] |                   |   |   |   |   |   |  |

| Туре  | Type R/W       |             |                   |   |   |   |   |   |  |

| Rese  | et 0           | 0           | 0                 | 0 | 0 | 0 | 0 | 0 |  |

| SFR A | Address = 0xF2 | ; SFR Page  | $e = 0 \times 00$ |   |   |   |   |   |  |

| Bit   | Name           |             | Function          |   |   |   |   |   |  |

| 7:0   | P0MASK[7:0]    | Port 0 M    | ask Value.        |   |   |   |   |   |  |

#### SFR Definition 20.4. P0MASK: Port 0 Mask Register

| P0MASK[7:0] | Port 0 Mask Value.                                                         |

|-------------|----------------------------------------------------------------------------|

|             | Selects P0 pins to be compared to the corresponding bits in P0MAT.         |

|             | 0: P0.n pin logic value is ignored and cannot cause a Port Mismatch event. |

|             | 1: P0.n pin logic value is compared to P0MAT.n.                            |

### SFR Definition 20.5. P0MAT: Port 0 Match Register

| Bit   | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------------|---|---|---|---|---|---|---|

| Name  | POMAT[7:0]      |   |   |   |   |   |   |   |

| Туре  | R/W             |   |   |   |   |   |   |   |

| Reset | 1 1 1 1 1 1 1 1 |   |   |   |   |   |   |   |

SFR Address = 0xF1; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                                                                   |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MAT[7:0] | Port 0 Match Value.                                                                                                                                                                        |

|     |            | Match comparison value used on Port 0 for bits in P0MAT which are set to 1.<br>0: P0.n pin logic value is compared with logic LOW.<br>1: P0.n pin logic value is compared with logic HIGH. |

## SFR Definition 20.29. P4MDOUT: Port 4 Output Mode

| Bit      | 7                                                                    | 6                                                                                         | 5        | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|----------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------|---|---|---|---|---|--|--|--|--|

| Nam      | e                                                                    | P4MDOUT[7:0]                                                                              |          |   |   |   |   |   |  |  |  |  |

| Type R/W |                                                                      |                                                                                           |          |   |   |   |   |   |  |  |  |  |

| Rese     | et 0                                                                 | 0                                                                                         | 0        | 0 | 0 | 0 | 0 | 0 |  |  |  |  |

| SFR A    | Address = 0xA                                                        | F; SFR Page                                                                               | e = 0x0F |   |   |   |   |   |  |  |  |  |

| Bit      | Name                                                                 | e Function                                                                                |          |   |   |   |   |   |  |  |  |  |

| 7:0      | P4MDOUT[7:0] Output Configuration Bits for P4.7–P4.0 (respectively). |                                                                                           |          |   |   |   |   |   |  |  |  |  |

|          |                                                                      | 0: Corresponding P4.n Output is open-drain.<br>1: Corresponding P4.n Output is push-pull. |          |   |   |   |   |   |  |  |  |  |

**Note:** Port 4.0 is only available on the 48-pin and 40-pin packages. P4.1-P4.7 are only available on the 48-pin packages.

### LIN Register Definition 21.11. LIN0ID: LIN0 Identifier Register

| Bit   | 7                | 6 | 5 | 4   | 3    | 2    | 1 | 0 |  |  |

|-------|------------------|---|---|-----|------|------|---|---|--|--|

| Name  |                  |   |   |     | ID[: | 5:0] |   |   |  |  |

| Туре  | R                | R |   | R/W |      |      |   |   |  |  |

| Reset | et 0 0 0 0 0 0 0 |   |   |     | 0    |      |   |   |  |  |

Indirect Address = 0x0E

| Bit | Name    | Function                                                                                                                                              |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused  | Read = 00b; Write = Don't Care.                                                                                                                       |

| 5:0 | ID[5:0] | LIN Identifier Bits.<br>These bits form the data identifier.<br>If the LINSIZE bits (LIN0SIZE[3:0]) are 1111b, bits ID[5:4] are used to determine the |

|     |         | data size and are interpreted as follows:<br>00: 2 bytes<br>01: 2 bytes<br>10: 4 bytes<br>11: 8 bytes                                                 |

## SFR Definition 22.1. CAN0CFG: CAN Clock Configuration

| Bit   | 7      | 6      | 5      | 4      | 3      | 2      | 1           | 0 |  |

|-------|--------|--------|--------|--------|--------|--------|-------------|---|--|

| Name  | Unused | Unused | Unused | Unused | Unused | Unused | SYSDIV[1:0] |   |  |

| Туре  | R      | R      | R      | R      | R      | R      | R/          | W |  |

| Reset | 0      | 0      | 0      | 0      | 0      | 0      | 0           | 0 |  |

#### SFR Address = 0x92; SFR Page = 0x0C

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                      |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused      | Read = 000000b; Write = Don't Care.                                                                                                                                                                                                                                                                                           |

| 1:0 | SYSDIV[1:0] | CAN System Clock Divider Bits.                                                                                                                                                                                                                                                                                                |

|     |             | The CAN controller clock is derived from the CIP-51 system clock. The CAN control-<br>ler clock must be less than or equal to 25 MHz.<br>00: CAN controller clock = System Clock/1.<br>01: CAN controller clock = System Clock/2.<br>10: CAN controller clock = System Clock/4.<br>11: CAN controller clock = System Clock/8. |

|                     | Valu             | es F | Rea   | ad      |     | Current SMbus State                                                                         | Typical Response Options                                      | Va<br>Wr | lues<br>ite | sto | s<br>ected                     |

|---------------------|------------------|------|-------|---------|-----|---------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------|-------------|-----|--------------------------------|

| Mode                | Status<br>Vector |      | ACKKG | ARBLOST | ACK |                                                                                             |                                                               | STA      | STO         | ACK | Next Status<br>Vector Expected |

|                     | 0100             | 0    |       | 0       | 0   | A slave byte was transmitted;<br>NACK received.                                             | No action required (expecting STOP condition).                | 0        | 0           | Х   | 0001                           |

| ter                 |                  | 0    |       | 0       | 1   | A slave byte was transmitted;<br>ACK received.                                              | Load SMB0DAT with next data byte to transmit.                 | 0        | 0           | Х   | 0100                           |

| ansmitt             |                  | 0    |       | 1       | Х   | A Slave byte was transmitted; error detected.                                               | No action required (expecting Master to end transfer).        | 0        | 0           | Х   | 0001                           |

| Slave Transmitter   | 0101             | 0    |       | X       | Х   | An illegal STOP or bus error<br>was detected while a Slave<br>Transmission was in progress. | Clear STO.                                                    | 0        | 0           | Х   | —                              |

|                     | 0010             | 1    | (     | 0       | Х   | A slave address + R/W was received; ACK requested.                                          | If Write, Acknowledge received address                        | 0        | 0           | 1   | 0000                           |

|                     |                  |      |       |         |     |                                                                                             | If Read, Load SMB0DAT with data byte; ACK received address    | 0        | 0           | 1   | 0100                           |

|                     |                  |      |       |         |     |                                                                                             | NACK received address.                                        | 0        | 0           | 0   | —                              |

|                     |                  | 1    |       | 1       | Х   | Lost arbitration as master;<br>slave address + R/W received;                                | If Write, Acknowledge received address                        | 0        | 0           | 1   | 0000                           |

|                     |                  |      |       |         |     | ACK requested.                                                                              | If Read, Load SMB0DAT with<br>data byte; ACK received address | 0        | 0           | 1   | 0100                           |

|                     |                  |      |       |         |     |                                                                                             | NACK received address.                                        | 0        | 0           | 0   | —                              |

|                     |                  |      |       |         |     |                                                                                             | Reschedule failed transfer;<br>NACK received address.         | 1        | 0           | 0   | 1110                           |

|                     | 0001             | 0    |       | 0       | Х   | A STOP was detected while<br>addressed as a Slave Trans-<br>mitter or Slave Receiver.       | Clear STO.                                                    | 0        | 0           | Х   |                                |

| eiver               |                  | 1    |       | 1       | Х   | Lost arbitration while attempt-<br>ing a STOP.                                              | No action required (transfer complete/aborted).               | 0        | 0           | 0   | —                              |

| Slave Rece          | 0000             | 1    | (     | 0       | Х   | A slave byte was received;<br>ACK requested.                                                | Acknowledge received byte;<br>Read SMB0DAT.                   | 0        | 0           | 1   | 0000                           |

| Slav                |                  |      |       |         |     |                                                                                             | NACK received byte.                                           | 0        | 0           | 0   |                                |

|                     | 0010             | 0    | )     | 1       | Х   | Lost arbitration while attempt-                                                             | Abort failed transfer.                                        | 0        | 0           | Х   | —                              |

| ditic               |                  |      |       |         |     | ing a repeated START.                                                                       | Reschedule failed transfer.                                   | 1        | 0           | Х   | 1110                           |

| Con                 | 0001             | 0    | )     | 1       | Х   | Lost arbitration due to a                                                                   | Abort failed transfer.                                        | 0        | 0           | Х   | —                              |

| Bus Error Condition |                  |      |       |         |     | detected STOP.                                                                              | Reschedule failed transfer.                                   | 1        | 0           | Х   | 1110                           |

| sЦ                  | 0000             | 1    |       | 1       | Х   | Lost arbitration while transmit-                                                            | Abort failed transfer.                                        | 0        | 0           | 0   | —                              |

| Bu                  |                  |      |       |         |     | ting a data byte as master.                                                                 | Reschedule failed transfer.                                   | 1        | 0           | 0   | 1110                           |

## Table 23.4. SMBus Status Decoding

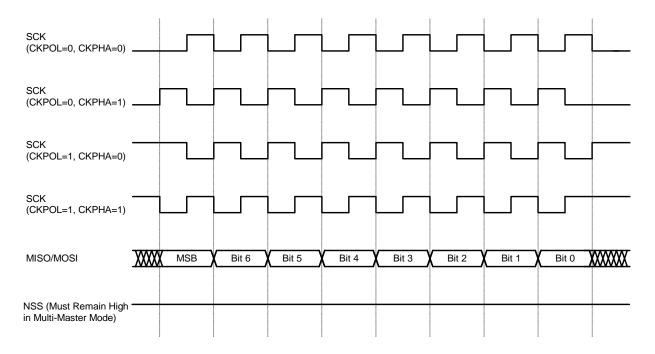

## 25.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 25.5. For slave mode, the clock and data relationships are shown in Figure 25.6 and Figure 25.7. CKPHA must be set to 0 on both the master and slave SPI when communicating between two of the following devices: C8051F04x, C8051F06x, C8051F12x, C8051F31x, C8051F32x, and C8051F33x.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 25.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

Figure 25.5. Master Mode Data/Clock Timing

## SFR Definition 26.1. CKCON: Clock Control

| Bit   | 7    | 6    | 5    | 4    | 3   | 2   | 1        | 0 |  |  |

|-------|------|------|------|------|-----|-----|----------|---|--|--|

| Name  | ТЗМН | T3ML | T2MH | T2ML | T1M | ТОМ | SCA[1:0] |   |  |  |

| Туре  | R/W  | R/W  | R/W  | R/W  | R/W | R/W | R/W      |   |  |  |

| Reset | 0    | 0    | 0    | 0    | 0   | 0   | 0        | 0 |  |  |

#### SFR Address = 0x8E; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                          |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ТЗМН     | Timer 3 High Byte Clock Select.                                                                                                                                                                                                                                                                                   |

|     |          | Selects the clock supplied to the Timer 3 high byte (split 8-bit timer mode only).<br>0: Timer 3 high byte uses the clock defined by the T3XCLK bit in TMR3CN.<br>1: Timer 3 high byte uses the system clock.                                                                                                     |

| 6   | T3ML     | Timer 3 Low Byte Clock Select.                                                                                                                                                                                                                                                                                    |

|     |          | <ul> <li>Selects the clock supplied to Timer 3. Selects the clock supplied to the lower 8-bit timer in split 8-bit timer mode.</li> <li>0: Timer 3 low byte uses the clock defined by the T3XCLK bit in TMR3CN.</li> <li>1: Timer 3 low byte uses the system clock.</li> </ul>                                    |

| 5   | T2MH     |                                                                                                                                                                                                                                                                                                                   |

| 5   | TZINIT   | <ul> <li>Timer 2 High Byte Clock Select.</li> <li>Selects the clock supplied to the Timer 2 high byte (split 8-bit timer mode only).</li> <li>0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 high byte uses the system clock.</li> </ul>                            |

| 4   | T2ML     | Timer 2 Low Byte Clock Select.                                                                                                                                                                                                                                                                                    |

|     |          | <ul> <li>Selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer mode, this bit selects the clock supplied to the lower 8-bit timer.</li> <li>0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 low byte uses the system clock.</li> </ul> |

| 3   | T1       | Timer 1 Clock Select.                                                                                                                                                                                                                                                                                             |

|     |          | Selects the clock source supplied to Timer 1. Ignored when C/T1 is set to 1.<br>0: Timer 1 uses the clock defined by the prescale bits SCA[1:0].<br>1: Timer 1 uses the system clock.                                                                                                                             |

| 2   | Т0       | Timer 0 Clock Select.                                                                                                                                                                                                                                                                                             |

|     |          | Selects the clock source supplied to Timer 0. Ignored when C/T0 is set to 1.<br>0: Counter/Timer 0 uses the clock defined by the prescale bits SCA[1:0].<br>1: Counter/Timer 0 uses the system clock.                                                                                                             |

| 1:0 | SCA[1:0] | Timer 0/1 Prescale Bits.                                                                                                                                                                                                                                                                                          |

|     |          | These bits control the Timer 0/1 Clock Prescaler:<br>00: System clock divided by 12<br>01: System clock divided by 4<br>10: System clock divided by 48<br>11: External clock divided by 8 (synchronized with the system clock)                                                                                    |

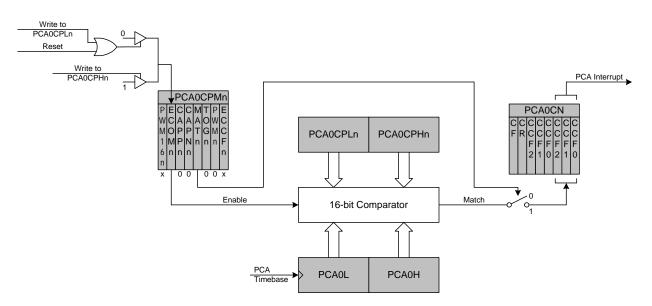

Figure 27.5. PCA Software Timer Mode Diagram

#### 27.3.3. High-Speed Output Mode

In High-Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode. If ECOMn is cleared, the associated pin will retain its state, and not toggle on the next match event.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

## 27.5. Register Descriptions for PCA0

Following are detailed descriptions of the special function registers related to the operation of the PCA.

## SFR Definition 27.1. PCA0CN: PCA Control

| Bit   | 7 6 |     | 5 4  |      | 3 2  |      | 1    | 0    |  |

|-------|-----|-----|------|------|------|------|------|------|--|

| Name  | CF  | CR  | CCF5 | CCF4 | CCF3 | CCF2 | CCF1 | CCF0 |  |

| Туре  | R/W | R/W | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |

| Reset | 0   | 0   | 0    | 0    | 0    | 0    | 0    | 0    |  |

SFR Address = 0xD8; Bit-Addressable; SFR Page = 0x00

| Bit | Name | Function                                                                                                                                                                                                                                                                                                           |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CF   | PCA Counter/Timer Overflow Flag.                                                                                                                                                                                                                                                                                   |

|     |      | Set by hardware when the PCA Counter/Timer overflows from 0xFFFF to 0x0000.<br>When the Counter/Timer Overflow (CF) interrupt is enabled, setting this bit causes the<br>CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared<br>by hardware and must be cleared by software. |

| 6   | CR   | PCA Counter/Timer Run Control.                                                                                                                                                                                                                                                                                     |

|     |      | This bit enables/disables the PCA Counter/Timer.<br>0: PCA Counter/Timer disabled.<br>1: PCA Counter/Timer enabled.                                                                                                                                                                                                |

| 5   | CCF5 | PCA Module 5 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |

|     |      | This bit is set by hardware when a match or capture occurs. When the CCF5 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.                                                 |

| 4   | CCF4 | PCA Module 4 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |

|     |      | This bit is set by hardware when a match or capture occurs. When the CCF4 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |

| 3   | CCF3 | PCA Module 3 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |

|     |      | This bit is set by hardware when a match or capture occurs. When the CCF3 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |

| 2   | CCF2 | PCA Module 2 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |

|     |      | This bit is set by hardware when a match or capture occurs. When the CCF2 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.                                                 |

| 1   | CCF1 | PCA Module 1 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |

|     |      | This bit is set by hardware when a match or capture occurs. When the CCF1 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.                                                 |

| 0   | CCF0 | PCA Module 0 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |

|     |      | This bit is set by hardware when a match or capture occurs. When the CCF0 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |