Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 4.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                    |

| Data Converters            | A/D 25x12b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                              |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 32-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f507-imr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2. Ordering Information

The following features are common to all devices in this family:

- 50 MHz system clock and 50 MIPS throughput (peak)

- 4352 bytes of RAM (256 internal bytes and 4096 XRAM bytes)

- SMBus/I<sup>2</sup>C, Enhanced SPI, Enhanced UART

- Four Timers

- Six Programmable Counter Array channels

- Internal 24 MHz oscillator

- Internal Voltage Regulator

- 12-bit, 200 ksps ADC

- Internal Voltage Reference and Temperature Sensor

- Two Analog Comparators

Table 2.1 shows the feature that differentiate the devices in this family.

| Name | Pin<br>'F500/1/4/5<br>(48-pin) | Pin<br>F508/9-<br>F510/1<br>(40-pin) | Pin<br>'F502/3/6/7<br>(32-pin) | Туре  | Description                                           |

|------|--------------------------------|--------------------------------------|--------------------------------|-------|-------------------------------------------------------|

| P3.7 | 19                             | 11                                   | —                              | D I/O | Port 3.7.                                             |

| P4.0 | 18                             | _                                    | —                              | D I/O | Port 4.0. See SFR Definition 20.28 for a description. |

| P4.1 | 17                             | _                                    | —                              | D I/O | Port 4.1.                                             |

| P4.2 | 16                             | _                                    | —                              | D I/O | Port 4.2.                                             |

| P4.3 | 15                             |                                      | —                              | D I/O | Port 4.3.                                             |

| P4.4 | 14                             |                                      | —                              | D I/O | Port 4.4.                                             |

| P4.5 | 13                             |                                      | —                              | D I/O | Port 4.5.                                             |

| P4.6 | 10                             | _                                    | —                              | D I/O | Port 4.6.                                             |

| P4.7 | 9                              |                                      | —                              | D I/O | Port 4.7.                                             |

Table 3.1. Pin Definitions for the C8051F50x/F51x(Continued)

# 4. Package Specifications

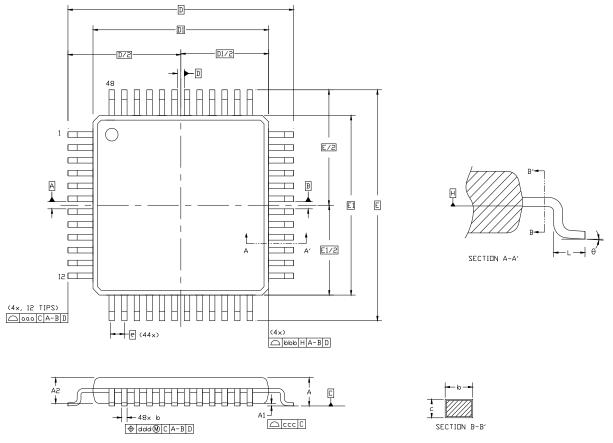

## 4.1. QFP-48 Package Specifications

#### Figure 4.1. QFP-48 Package Drawing

| Dimension | Min       | Тур       | Max  |  | Dimension | Min  | Тур       | Max  |  |

|-----------|-----------|-----------|------|--|-----------|------|-----------|------|--|

| A         | —         | —         | 1.20 |  | E         |      | 9.00 BSC. |      |  |

| A1        | 0.05      |           | 0.15 |  | E1        |      | 7.00 BSC. |      |  |

| A2        | 0.95      | 1.00      | 1.05 |  | L         | 0.45 | 0.60      | 0.75 |  |

| b         | 0.17      | 0.22      | 0.27 |  | aaa       | 0.20 |           |      |  |

| С         | 0.09      | _         | 0.20 |  | bbb       |      | 0.20      |      |  |

| D         |           | 9.00 BSC. |      |  | CCC       |      | 0.08      |      |  |

| D1        | 7.00 BSC. |           |      |  | ddd       |      | 0.08      |      |  |

| е         |           | 0.50 BSC. |      |  | θ         | 0°   | 3.5°      | 7°   |  |

#### Table 4.1. QFP-48 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC outline MS-026, variation ABC.

- Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

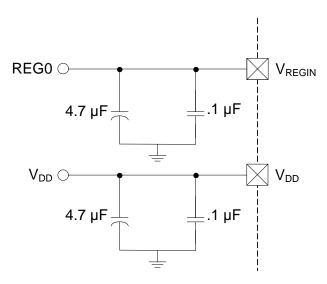

# 10. Voltage Regulator (REG0)

C8051F50x/F51x devices include an on-chip low dropout voltage regulator (REG0). The input to REG0 at the  $V_{REGIN}$  pin can be as high as 5.25 V. The output can be selected by software to 2.1 V or 2.6 V. When enabled, the output of REG0 appears on the  $V_{DD}$  pin, powers the microcontroller core, and can be used to power external devices. On reset, REG0 is enabled and can be disabled by software.

The Voltage regulator can generate an interrupt (if enabled by EREG0, EIE2.0) that is triggered whenever the  $V_{REGIN}$  input voltage drops below the dropout threshold voltage. This dropout interrupt has no pending flag and the recommended procedure to use it is as follows:

- 1. Wait enough time to ensure the  $V_{REGIN}$  input voltage is stable

- 2. Enable the dropout interrupt (EREG0, EIE2.0) and select the proper priority (PREG0, EIP2.0)

- 3. If triggered, inside the interrupt disable it (clear EREG0, EIE2.0), execute all procedures necessary to protect your application (put it in a safe mode and leave the interrupt now disabled.

- 4. In the main application, now running in the safe mode, regularly checks the DROPOUT bit (REG0CN.0). Once it is cleared by the regulator hardware the application can enable the interrupt again (EREG0, EIE1.6) and return to the normal mode operation.

The input (V<sub>REGIN</sub>) and output (V<sub>DD</sub>) of the voltage regulator should both be bypassed with a large capacitor (4.7  $\mu$ F + 0.1  $\mu$ F) to ground as shown in Figure 10.1 below. This capacitor will eliminate power spikes and provide any immediate power required by the microcontroller. The settling time associated with the voltage regulator is shown in Table X.

Figure 10.1. External Capacitors for Voltage Regulator Input/Output— Regulator Enabled

If the internal voltage regulator is not used, the VREGIN input should be tied to VDD, as shown in Figure 10.2.

## 14. Interrupts

The C8051F50x/F51x devices include an extended interrupt system supporting a total of 18 interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regard-less of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE, EIE1, or EIE2). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

**Note:** Any instruction that clears a bit to disable an interrupt should be immediately followed by an instruction that has two or more opcode bytes. Using EA (global interrupt enable) as an example:

// in 'C': EA = 0; // clear EA bit. EA = 0; // this is a dummy instruction with two-byte opcode. ; in assembly: CLR EA ; clear EA bit. CLR EA ; this is a dummy instruction with two-byte opcode.

For example, if an interrupt is posted during the execution phase of a "CLR EA" opcode (or any instruction which clears a bit to disable an interrupt source), and the instruction is followed by a single-cycle instruction, the interrupt may be taken. However, a read of the enable bit will return a 0 inside the interrupt service routine. When the bit-clearing opcode is followed by a multi-cycle instruction, the interrupt will not be taken.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

#### 14.1. MCU Interrupt Sources and Vectors

The C8051F50x/F51x MCUs support 18 interrupt sources. Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 14.1. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

#### 15.4. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of  $V_{DD}$ , system clock frequency, or temperature. This accidental execution of Flash modifying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

The following guidelines are recommended for any system which contains routines which write or erase Flash from code.

#### 15.4.1. $V_{\text{DD}}$ Maintenance and the $V_{\text{DD}}$ monitor

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- 2. The on-chip V<sub>DD</sub> monitor is turned on and enabled as a reset source by default by the hardware. If it is disabled by the firmware, use the following recommendations when re-enabling the V<sub>DD</sub> monitor. Turn on the V<sub>DD</sub> monitor and enable it as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For C-based systems, this will involve modifying the startup code added by the C compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the V<sub>DD</sub> monitor and enabling the V<sub>DD</sub> monitor as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware", available from the Silicon Laboratories web site.

- 3. As an added precaution, explicitly enable the V<sub>DD</sub> monitor and enable the V<sub>DD</sub> monitor as a reset source inside the functions that write and erase Flash memory. The V<sub>DD</sub> monitor enable instructions should be placed just after the instruction to set PSWE to a 1, but before the Flash write or erase operation instruction.

- 4. Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct. "RSTSRC |= 0x02" is incorrect.

- 5. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a 1. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

#### 15.4.2. PSWE Maintenance

- 1. Reduce the number of places in code where the PSWE bit (b0 in PSCTL) is set to a 1. There should be exactly one routine in code that sets PSWE to a 1 to write Flash bytes and one routine in code that sets PSWE and PSEE both to a 1 to erase Flash pages.

- Minimize the number of variable accesses while PSWE is set to a 1. Handle pointer address updates and loop variable maintenance outside the "PSWE = 1;... PSWE = 0;" area. Code examples showing this can be found in "AN201: Writing to Flash from Firmware" available from the Silicon Laboratories web site.

- 3. Disable interrupts prior to setting PSWE to a 1 and leave them disabled until after PSWE has been reset to '0'. Any interrupts posted during the Flash write or erase operation will be serviced in priority order after the Flash operation has been completed and interrupts have been re-enabled by software.

- Make certain that the Flash write and erase pointer variables are not located in XRAM. See your compiler documentation for instructions regarding how to explicitly locate variables in different memory areas.

- 5. Add address bounds checking to the routines that write or erase Flash memory to ensure that a routine called with an illegal address does not result in modification of the Flash.

## SFR Definition 15.3. FLSCL: Flash Scale

| Bit   | 7        | 6        | 5        | 4    | 3        | 2        | 1     | 0        |

|-------|----------|----------|----------|------|----------|----------|-------|----------|

| Name  | Reserved | Reserved | Reserved | FLRT | Reserved | Reserved | FLEWT | Reserved |

| Туре  | R/W      | R/W      | R/W      | R/W  | R/W      | R/W      | R/W   | R/W      |

| Reset | 0        | 0        | 0        | 0    | 0        | 0        | 0     | 0        |

\_\_\_\_\_

#### SFR Address = 0xB6; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                            |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Reserved | Must Write 000b.                                                                                                                                                                                                                                                    |

| 4   | FLRT     | Flash Read Time Control.                                                                                                                                                                                                                                            |

|     |          | <ul> <li>This bit should be programmed to the smallest allowed value, according to the system clock speed.</li> <li>0: SYSCLK ≤ 25 MHz (Flash read strobe is one system clock).</li> <li>1: SYSCLK &gt; 25 MHz (Flash read strobe is two system clocks).</li> </ul> |

| 3:2 | Reserved | Must Write 00b.                                                                                                                                                                                                                                                     |

| 1   | FLEWT    | Flash Erase Write Time Control.<br>This bit should be set to 1b before Writing or Erasing Flash.<br>0: Short Flash Erase / Write Timing.<br>1: Extended Flash Erase / Write Timing.                                                                                 |

| 0   | Reserved | Must Write 0b.                                                                                                                                                                                                                                                      |

## SFR Definition 17.1. VDM0CN: V<sub>DD</sub> Monitor Control

| Bit   | 7      | 6       | 5      | 4 | 3 | 2 | 1 | 0 |

|-------|--------|---------|--------|---|---|---|---|---|

| Name  | VDMEN  | VDDSTAT | VDMLVL |   |   |   |   |   |

| Туре  | R/W    | R       | R/W    | R | R | R | R | R |

| Reset | Varies | Varies  | 0      | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xFF; SFR Page = 0x00

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN   | V <sub>DD</sub> Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |         | This bit turns the V <sub>DD</sub> monitor circuit on/off. The V <sub>DD</sub> Monitor cannot generate system resets until it is also selected as a reset source in register RSTSRC (SFR Definition 17.2). Selecting the V <sub>DD</sub> monitor as a reset source before it has stabilized may generate a system reset. In systems where this reset would be undesirable, a delay should be introduced between enabling the V <sub>DD</sub> Monitor and selecting it as a reset source. See Table 5.4 for the minimum V <sub>DD</sub> Monitor turn-on time.<br>0: V <sub>DD</sub> Monitor Disabled.<br>1: V <sub>DD</sub> Monitor Enabled. |

| 6   | VDDSTAT | V <sub>DD</sub> Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |         | This bit indicates the current power supply status ( $V_{DD}$ Monitor output).<br>0: $V_{DD}$ is at or below the $V_{DD}$ monitor threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |         | 1: V <sub>DD</sub> is above the V <sub>DD</sub> monitor threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5   | VDMLVL  | V <sub>DD</sub> Monitor Level Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |         | 0: $V_{DD}$ Monitor Threshold is set to VRST-LOW<br>1: $V_{DD}$ Monitor Threshold is set to VRST-HIGH. This setting is required for any system includes code that writes to and/or erases Flash.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4:0 | Unused  | Read = 00000b; Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

### 17.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 5.4 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

### 17.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than the value specified in Table 5.4, "Reset Electrical Characteristics," on page 46, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

# C8051F50x/F51x

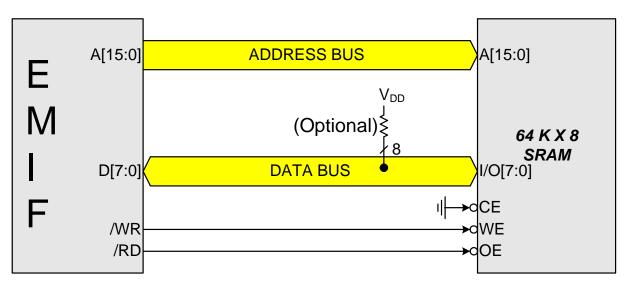

#### 18.4.2. Non-multiplexed Configuration

In Non-multiplexed mode, the Data Bus and the Address Bus pins are not shared. An example of a Nonmultiplexed Configuration is shown in Figure 18.2. See Section "18.6.1. Non-Multiplexed Mode" on page 158 for more information about Non-multiplexed operation.

Figure 18.2. Non-multiplexed Configuration Example

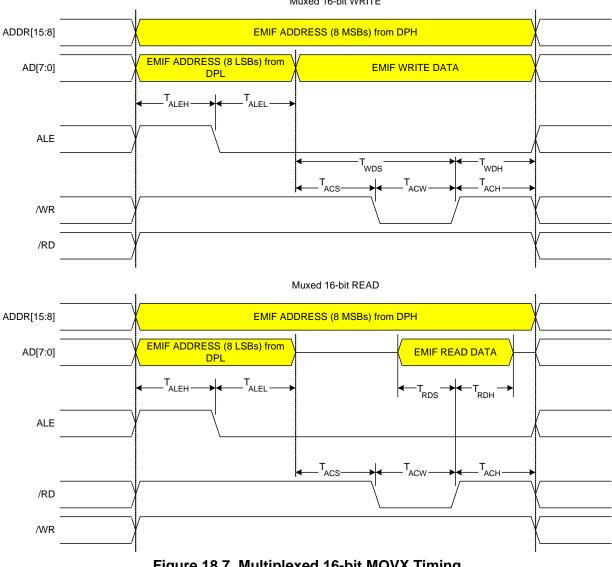

#### 18.6.2. Multiplexed Mode 18.6.2.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011

Muxed 16-bit WRITE

# C8051F50x/F51x

# SFR Definition 20.1. XBR0: Port I/O Crossbar Register 0

| Bit   | 7     | 6    | 5     | 4    | 3     | 2     | 1     | 0     |

|-------|-------|------|-------|------|-------|-------|-------|-------|

| Name  | CP1AE | CP1E | CP0AE | CP0E | SMB0E | SPI0E | CAN0E | URT0E |

| Туре  | R/W   | R/W  | R/W   | R/W  | R/W   | R/W   | R/W   | R/W   |

| Reset | 0     | 0    | 0     | 0    | 0     | 0     | 0     | 0     |

#### SFR Address = 0xE1; SFR Page = 0x0F

| Bit | Name   | Function                                                                                   |

|-----|--------|--------------------------------------------------------------------------------------------|

| 7   | CP1AE  | Comparator1 Asynchronous Output Enable.<br>0: Asynchronous CP1 unavailable at Port pin.    |

|     |        | 1: Asynchronous CP1 routed to Port pin.                                                    |

| 6   | CP1E   | Comparator1 Output Enable.                                                                 |

|     |        | 0: CP1 unavailable at Port pin.                                                            |

|     |        | 1: CP1 routed to Port pin.                                                                 |

| 5   | CP0AE  | Comparator0 Asynchronous Output Enable.                                                    |

|     |        | 0: Asynchronous CP0 unavailable at Port pin.<br>1: Asynchronous CP0 routed to Port pin.    |

|     | 0005   |                                                                                            |

| 4   | CP0E   | Comparator0 Output Enable.<br>0: CP0 unavailable at Port pin.                              |

|     |        | 1: CP0 routed to Port pin.                                                                 |

| 3   | SMB0E  | SMBus I/O Enable.                                                                          |

| Ŭ   | CINECE | 0: SMBus I/O unavailable at Port pins.                                                     |

|     |        | 1: SMBus I/O routed to Port pins.                                                          |

| 2   | SPI0E  | SPI I/O Enable.                                                                            |

|     |        | 0: SPI I/O unavailable at Port pins.                                                       |

|     |        | 1: SPI I/O routed to Port pins. Note that the SPI can be assigned either 3 or 4 GPIO pins. |

| 1   | CAN0E  | CAN I/O Output Enable.                                                                     |

|     |        | 0: CAN I/O unavailable at Port pins.                                                       |

|     |        | 1: CAN_TX, CAN_RX routed to Port pins P0.6 and P0.7.                                       |

| 0   | URT0E  | UART I/O Output Enable.                                                                    |

|     |        | 0: UART I/O unavailable at Port pin.                                                       |

|     |        | 1: UART TX0, RX0 routed to Port pins P0.4 and P0.5.                                        |

of setting the DTACK (LINOCTRL.4) bit. At that time, steps 2 through 5 can then be skipped. In this situation, the LIN controller stops the processing of LIN communication until the next SYNC BREAK is received.

4. Changing the configuration of the checksum during a transaction will cause the interface to reset and the transaction to be lost. To prevent this, the checksum should not be configured while a transaction is in progress. The same applies to changes in the LIN interface mode from slave mode to master mode and from master mode to slave mode.

#### 21.5. Sleep Mode and Wake-Up

To reduce the system's power consumption, the LIN Protocol Specification defines a Sleep Mode. The message used to broadcast a Sleep Mode request must be transmitted by the LIN master application in the same way as a normal transmit message. The LIN slave application must decode the Sleep Mode Frame from the Identifier and data bytes. After that, it has to put the LIN slave node into the Sleep Mode by setting the SLEEP bit (LIN0CTRL.6).

If the SLEEP bit (LIN0CTRL.6) of the LIN slave application is not set and there is no bus activity for four seconds (specified bus idle timeout), the IDLTOUT bit (LIN0ST.6) is set and an interrupt request is generated. After that the application may assume that the LIN bus is in Sleep Mode and set the SLEEP bit (LIN0CTRL.6).

Sending a wake-up signal from the master or any slave node terminates the Sleep Mode of the LIN bus. To send a wake-up signal, the application has to set the WUPREQ bit (LIN0CTRL.1). After successful transmission of the wake-up signal, the DONE bit (LIN0ST.0) of the master node is set and an interrupt request is generated. The LIN slave does not generate an interrupt request after successful transmission of the wake-up signal but it generates an interrupt request if the master does not respond to the wake-up signal within 150 milliseconds. In that case, the ERROR bit (LIN0ST.2) and TOUT bit (LIN0ERR.2) are set. The application then has to decide whether or not to transmit another wake-up signal.

All LIN nodes that detect a wake-up signal will set the WAKEUP (LIN0ST.1) and DONE bits (LIN0ST.0) and generate an interrupt request. After that, the application has to clear the SLEEP bit (LIN0CTRL.6) in the LIN slave.

#### 21.6. Error Detection and Handling

The LIN controller generates an interrupt request and stops the processing of the current frame if it detects an error. The application has to check the type of error by processing LIN0ERR. After that, it has to reset the error register and the ERROR bit (LIN0ST.2) by writing a 1 to the RSTERR bit (LIN0CTRL.2). Starting a new message with the LIN controller selected as master or sending a Wakeup signal with the LIN controller selected as a master or slave is possible only if the ERROR bit (LIN0ST.2) is set to 0.

#### LIN Register Definition 21.6. LIN0ST: LIN0 Status Register

| Bit   | 7      | 6       | 5     | 4     | 3      | 2     | 1      | 0    |

|-------|--------|---------|-------|-------|--------|-------|--------|------|

| Name  | ACTIVE | IDLTOUT | ABORT | DTREQ | LININT | ERROR | WAKEUP | DONE |

| Туре  | R      | R       | R     | R     | R      | R     | R      | R    |

| Reset | 0      | 0       | 0     | 0     | 0      | 0     | 0      | 0    |

Indirect Address = 0x09

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                          |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ACTIVE | LIN Active Indicator Bit.                                                                                                                                                                                                                                                                                         |

|     |        | 0: No transmission activity detected on the LIN bus.                                                                                                                                                                                                                                                              |

|     |        | 1: Transmission activity detected on the LIN bus.                                                                                                                                                                                                                                                                 |

| 6   | IDLT   | Bus Idle Timeout Bit. (slave mode only)                                                                                                                                                                                                                                                                           |

|     |        | 0: The bus has not been idle for four seconds.                                                                                                                                                                                                                                                                    |

|     |        | 1: No bus activity has been detected for four seconds, but the bus is not yet in Sleep mode.                                                                                                                                                                                                                      |

| 5   | ABORT  | Aborted Transmission Bit. (slave mode only)                                                                                                                                                                                                                                                                       |

|     |        | <ul> <li>0: The current transmission has not been interrupted or stopped. This bit is reset to 0 after receiving a SYNCH BREAK that does not interrupt a pending transmission.</li> <li>1: New SYNCH BREAK detected before the end of the last transmission or the STOP bit (LIN0CTRL.7) has been set.</li> </ul> |

| 4   | DTREQ  | Data Request Bit. (slave mode only)                                                                                                                                                                                                                                                                               |

|     |        | 0: Data identifier has not been received.                                                                                                                                                                                                                                                                         |

|     |        | 1: Data identifier has been received.                                                                                                                                                                                                                                                                             |

| 3   | LININT | Interrupt Request Bit.                                                                                                                                                                                                                                                                                            |

|     |        | <ul><li>0: An interrupt is not pending. This bit is cleared by setting RSTINT (LIN0CTRL.3)</li><li>1: There is a pending LIN0 interrupt.</li></ul>                                                                                                                                                                |

| 2   | ERROR  | Communication Error Bit.                                                                                                                                                                                                                                                                                          |

|     |        | 0: No error has been detected. This bit is cleared by setting RSTERR (LIN0CTRL.2) 1: An error has been detected.                                                                                                                                                                                                  |

| 1   | WAKEUP | Wakeup Bit.                                                                                                                                                                                                                                                                                                       |

|     |        | 0: A wakeup signal is not being transmitted and has not been received.                                                                                                                                                                                                                                            |

|     |        | 1: A wakeup signal is being transmitted or has been received                                                                                                                                                                                                                                                      |

| 0   | DONE   | Transmission Complete Bit.                                                                                                                                                                                                                                                                                        |

|     |        | 0: A transmission is not in progress or has not been started. This bit is cleared at the                                                                                                                                                                                                                          |

|     |        | start of a transmission.<br>1: The current transmission is complete.                                                                                                                                                                                                                                              |

|     |        |                                                                                                                                                                                                                                                                                                                   |

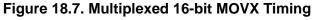

#### 23.5.4. Read Sequence (Slave)

During a read sequence, an SMBus master reads data from a slave device. The slave in this transfer will be a receiver during the address byte, and a transmitter during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode (to receive the slave address) when a START followed by a slave address and direction bit (READ in this case) is received. Upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. The interrupt will occur after the ACK cycle.

If the received slave address is ignored, slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are transmitted. If the received slave address is acknowledged, data should be written to SMB0DAT to be transmitted. The interface enters Slave Transmitter Mode, and transmits one or more bytes of data. After each byte is transmitted, the master sends an acknowledge bit; if the acknowledge bit is an ACK, SMB0DAT should be written with the next data byte. If the acknowledge bit is a NACK, SMB0DAT should not be written to before SI is cleared (Note: an error condition may be generated if SMB0DAT is written following a received NACK while in Slave Transmitter Mode). The interface exits Slave Transmitter Mode after receiving a STOP. Note that the interface will switch to Slave Receiver Mode if SMB0DAT is not written following a Slave Transmitter interrupt. Figure 23.8 shows a typical slave read sequence. Two transmitted data bytes are shown, though any number of bytes may be transmitted. Notice that all of the 'data byte transferred' interrupts occur **after** the ACK cycle in this mode.

#### 23.6. SMBus Status Decoding

The current SMBus status can be easily decoded using the SMB0CN register. In the tables, STATUS VECTOR refers to the four upper bits of SMB0CN: MASTER, TXMODE, STA, and STO. The shown response options are only the typical responses; application-specific procedures are allowed as long as they conform to the SMBus specification. Highlighted responses are allowed by hardware but do not conform to the SMBus specification.

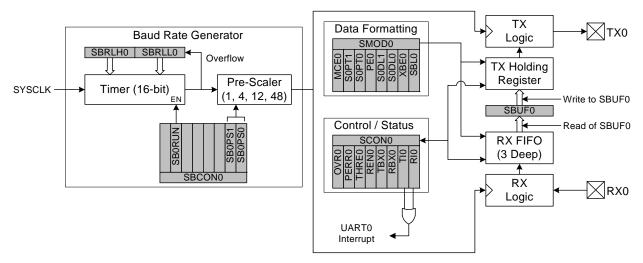

# 24. UART0

UART0 is an asynchronous, full duplex serial port offering a variety of data formatting options. A dedicated baud rate generator with a 16-bit timer and selectable prescaler is included, which can generate a wide range of baud rates (details in Section "24.1. Baud Rate Generator" on page 243). A received data FIFO allows UART0 to receive up to three data bytes before data is lost and an overflow occurs.

UART0 has six associated SFRs. Three are used for the Baud Rate Generator (SBCON0, SBRLH0, and SBRLL0), two are used for data formatting, control, and status functions (SCON0, SMOD0), and one is used to send and receive data (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Writes to SBUF0 always access the Transmit register. Reads of SBUF0 always access the buffered Receive register; it is not possible to read data from the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete). If additional bytes are available in the Receive FIFO, the RI0 bit cannot be cleared by software.

Figure 24.1. UART0 Block Diagram

### 24.1. Baud Rate Generator

The UART0 baud rate is generated by a dedicated 16-bit timer which runs from the controller's core clock (SYSCLK) and has prescaler options of 1, 4, 12, or 48. The timer and prescaler options combined allow for a wide selection of baud rates over many clock frequencies.

The baud rate generator is configured using three registers: SBCON0, SBRLH0, and SBRLL0. The UART0 Baud Rate Generator Control Register (SBCON0, SFR Definition 24.4) enables or disables the baud rate generator, selects the clock source for the baud rate generator, and selects the prescaler value for the timer. The baud rate generator must be enabled for UART0 to function. Registers SBRLH0 and SBRLL0 contain a 16-bit reload value for the dedicated 16-bit timer. The internal timer counts up from the reload value on every clock tick. On timer overflows (0xFFFF to 0x0000), the timer is reloaded. The baud rate for UART0 is defined in Equation 24.1, where "BRG Clock" is the baud rate generator's selected clock source. For reliable UART operation, it is recommended that the UART baud rate is not configured for baud rates faster than SYSCLK/16.

#### 24.3. Configuration and Operation

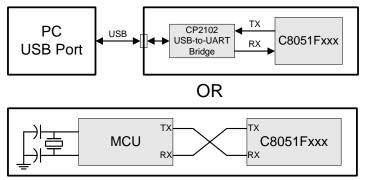

UART0 provides standard asynchronous, full duplex communication. It can operate in a point-to-point serial communications application, or as a node on a multi-processor serial interface. To operate in a point-to-point application, where there are only two devices on the serial bus, the MCE0 bit in SMOD0 should be cleared to 0. For operation as part of a multi-processor communications bus, the MCE0 and XBE0 bits should both be set to 1. In both types of applications, data is transmitted from the microcontroller on the TX0 pin, and received on the RX0 pin. The TX0 and RX0 pins are configured using the crossbar and the Port I/O registers, as detailed in Section "20. Port Input/Output" on page 177.

In typical UART communications, The transmit (TX) output of one device is connected to the receive (RX) input of the other device, either directly or through a bus transceiver, as shown in Figure 24.5.

Figure 24.5. Typical UART Interconnect Diagram

#### 24.3.1. Data Transmission

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) will be set at the end of any transmission (the beginning of the stop-bit time). If enabled, an interrupt will occur when TI0 is set.

If the extra bit function is enabled (XBE0 = 1) and the parity function is disabled (PE0 = 0), the value of the TBX0 (SCON0.3) bit will be sent in the extra bit position. When the parity function is enabled (PE0 = 1), hardware will generate the parity bit according to the selected parity type (selected with S0PT[1:0]), and append it to the data field. Note: when parity is enabled, the extra bit function is not available.

#### 24.3.2. Data Reception

Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be stored in the receive FIFO if the following conditions are met: the receive FIFO (3 bytes deep) must not be full, and the stop bit(s) must be logic 1. In the event that the receive FIFO is full, the incoming byte will be lost, and a Receive FIFO Overrun Error will be generated (OVR0 in register SCON0 will be set to logic 1). If the stop bit(s) were logic 0, the incoming data will not be stored in the receive FIFO. If the reception conditions are met, the data is stored in the receive FIFO, and the RI0 flag will be set. Note: when MCE0 = 1, RI0 will only be set if the extra bit was equal to 1. Data can be read from the receive FIFO by reading the SBUF0 register. The SBUF0 register represents the oldest byte in the FIFO. After SBUF0 is read, the next byte in the FIFO is immediately loaded into SBUF0, and space is made available in the FIFO for another incoming byte. If enabled, an interrupt will occur when RI0 is set.RI0 can only be cleared to 0 by software when there is no more information in the FIFO. The recommended procedure to empty the FIFO contents is:

- 1. Clear RI0 to 0.

- 2. Read SBUF0.

- 3. Check RI0, and repeat starting at step 1 if RI0 is set to 1.

## SFR Definition 26.1. CKCON: Clock Control

| Bit   | 7    | 6    | 5    | 4    | 3   | 2   | 1   | 0     |

|-------|------|------|------|------|-----|-----|-----|-------|

| Name  | ТЗМН | T3ML | T2MH | T2ML | T1M | ТОМ | SCA | [1:0] |

| Туре  | R/W  | R/W  | R/W  | R/W  | R/W | R/W | R/W |       |

| Reset | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0     |

#### SFR Address = 0x8E; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7   | ТЗМН     | Timer 3 High Byte Clock Select.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|     |          | Selects the clock supplied to the Timer 3 high byte (split 8-bit timer mode only).<br>0: Timer 3 high byte uses the clock defined by the T3XCLK bit in TMR3CN.<br>1: Timer 3 high byte uses the system clock.                                                                                                     |  |  |  |  |  |

| 6   | T3ML     | Timer 3 Low Byte Clock Select.                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|     |          | <ul> <li>Selects the clock supplied to Timer 3. Selects the clock supplied to the lower 8-bit timer in split 8-bit timer mode.</li> <li>0: Timer 3 low byte uses the clock defined by the T3XCLK bit in TMR3CN.</li> <li>1: Timer 3 low byte uses the system clock.</li> </ul>                                    |  |  |  |  |  |

| 5   | T2MH     |                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 5   | TZINIT   | <ul> <li>Timer 2 High Byte Clock Select.</li> <li>Selects the clock supplied to the Timer 2 high byte (split 8-bit timer mode only).</li> <li>0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 high byte uses the system clock.</li> </ul>                            |  |  |  |  |  |

| 4   | T2ML     | Timer 2 Low Byte Clock Select.                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|     |          | <ul> <li>Selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer mode, this bit selects the clock supplied to the lower 8-bit timer.</li> <li>0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 low byte uses the system clock.</li> </ul> |  |  |  |  |  |

| 3   | T1       | Timer 1 Clock Select.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|     |          | Selects the clock source supplied to Timer 1. Ignored when C/T1 is set to 1.<br>0: Timer 1 uses the clock defined by the prescale bits SCA[1:0].<br>1: Timer 1 uses the system clock.                                                                                                                             |  |  |  |  |  |

| 2   | Т0       | Timer 0 Clock Select.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|     |          | Selects the clock source supplied to Timer 0. Ignored when C/T0 is set to 1.                                                                                                                                                                                                                                      |  |  |  |  |  |

|     |          | <ul><li>0: Counter/Timer 0 uses the clock defined by the prescale bits SCA[1:0].</li><li>1: Counter/Timer 0 uses the system clock.</li></ul>                                                                                                                                                                      |  |  |  |  |  |

| 1:0 | SCA[1:0] | Timer 0/1 Prescale Bits.                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|     |          | These bits control the Timer 0/1 Clock Prescaler:                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|     |          | 00: System clock divided by 12<br>01: System clock divided by 4                                                                                                                                                                                                                                                   |  |  |  |  |  |

|     |          | 10: System clock divided by 4                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|     |          | 11: External clock divided by 8 (synchronized with the system clock)                                                                                                                                                                                                                                              |  |  |  |  |  |

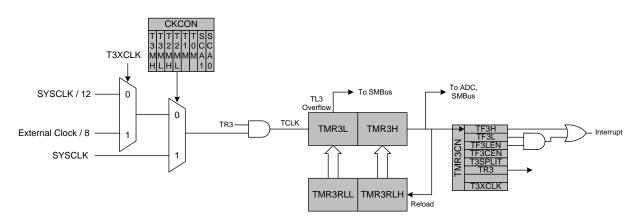

#### 26.3. Timer 3

Timer 3 is a 16-bit timer formed by two 8-bit SFRs: TMR3L (low byte) and TMR3H (high byte). Timer 3 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T3SPLIT bit (TMR3CN.3) defines the Timer 3 operation mode.

Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 3 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

#### 26.3.1. 16-bit Timer with Auto-Reload

When T3SPLIT (TMR3CN.3) is zero, Timer 3 operates as a 16-bit timer with auto-reload. Timer 3 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 3 reload registers (TMR3RLH and TMR3RLL) is loaded into the Timer 3 register as shown in Figure 26.7, and the Timer 3 High Byte Overflow Flag (TMR3CN.7) is set. If Timer 3 interrupts are enabled, an interrupt will be generated on each Timer 3 overflow. Additionally, if Timer 3 interrupts are enabled and the TF3LEN bit is set (TMR3CN.5), an interrupt will be generated each time the lower 8 bits (TMR3L) overflow from 0xFF to 0x000.

Figure 26.7. Timer 3 16-Bit Mode Block Diagram

#### 26.3.2. 8-bit Timers with Auto-Reload

When T3SPLIT is set, Timer 3 operates as two 8-bit timers (TMR3H and TMR3L). Both 8-bit timers operate in auto-reload mode as shown in Figure 26.8. TMR3RLL holds the reload value for TMR3L; TMR3RLH holds the reload value for TMR3H. The TR3 bit in TMR3CN handles the run control for TMR3H. TMR3L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 3 Clock Select bits (T3MH and T3ML in CKCON) select either SYSCLK or the clock defined by the Timer 3 External Clock Select bit (T3XCLK in TMR3CN), as follows:

## 27.5. Register Descriptions for PCA0

Following are detailed descriptions of the special function registers related to the operation of the PCA.

## SFR Definition 27.1. PCA0CN: PCA Control

| Bit   | 7   | 6   | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|-----|-----|------|------|------|------|------|------|

| Name  | CF  | CR  | CCF5 | CCF4 | CCF3 | CCF2 | CCF1 | CCF0 |

| Туре  | R/W | R/W | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset | 0   | 0   | 0    | 0    | 0    | 0    | 0    | 0    |

SFR Address = 0xD8; Bit-Addressable; SFR Page = 0x00

| Bit | Name | Function                                                                                                                                                                                                                                                                                                           |  |  |  |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | CF   | PCA Counter/Timer Overflow Flag.                                                                                                                                                                                                                                                                                   |  |  |  |

|     |      | Set by hardware when the PCA Counter/Timer overflows from 0xFFFF to 0x0000.<br>When the Counter/Timer Overflow (CF) interrupt is enabled, setting this bit causes the<br>CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared<br>by hardware and must be cleared by software. |  |  |  |

| 6   | CR   | PCA Counter/Timer Run Control.                                                                                                                                                                                                                                                                                     |  |  |  |

|     |      | This bit enables/disables the PCA Counter/Timer.<br>0: PCA Counter/Timer disabled.<br>1: PCA Counter/Timer enabled.                                                                                                                                                                                                |  |  |  |

| 5   | CCF5 | PCA Module 5 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |  |  |  |

|     |      | This bit is set by hardware when a match or capture occurs. When the CCF5 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |  |  |  |

| 4   | CCF4 | PCA Module 4 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |  |  |  |

|     |      | This bit is set by hardware when a match or capture occurs. When the CCF4 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |  |  |  |

| 3   | CCF3 | PCA Module 3 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |  |  |  |

|     |      | This bit is set by hardware when a match or capture occurs. When the CCF3 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |  |  |  |

| 2   | CCF2 | PCA Module 2 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |  |  |  |

|     |      | This bit is set by hardware when a match or capture occurs. When the CCF2 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |  |  |  |

| 1   | CCF1 | PCA Module 1 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |  |  |  |

|     |      | This bit is set by hardware when a match or capture occurs. When the CCF1 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |  |  |  |

| 0   | CCF0 | PCA Module 0 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |  |  |  |

|     |      | This bit is set by hardware when a match or capture occurs. When the CCF0 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |  |  |  |

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

## http://www.silabs.com