#### Silicon Labs - <u>C8051F511-IM Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART      |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 33                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                |                                                                |

| RAM Size                   | 4.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 32x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 40-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 40-QFN (6x6)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f511-im |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2. Ordering Information

The following features are common to all devices in this family:

- 50 MHz system clock and 50 MIPS throughput (peak)

- 4352 bytes of RAM (256 internal bytes and 4096 XRAM bytes)

- SMBus/I<sup>2</sup>C, Enhanced SPI, Enhanced UART

- Four Timers

- Six Programmable Counter Array channels

- Internal 24 MHz oscillator

- Internal Voltage Regulator

- 12-bit, 200 ksps ADC

- Internal Voltage Reference and Temperature Sensor

- Two Analog Comparators

Table 2.1 shows the feature that differentiate the devices in this family.

### 6.2. Output Code Formatting

The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code. When the repeat count is set to 1, conversion codes are represented in 12-bit unsigned integer format and the output conversion code is updated after each conversion. Inputs are measured from 0 to  $V_{REF} \times 4095/4096$ . Data can be right-justified or left-justified, depending on the setting of the AD0LJST bit (ADC0CN.2). Unused bits in the ADC0H and ADC0L registers are set to 0. Example codes are shown below for both right-justified and left-justified data.

| Input Voltage    | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|------------------|----------------------------------------------|---------------------------------------------|

| VREF x 4095/4096 | 0x0FFF                                       | 0xFFF0                                      |

| VREF x 2048/4096 | 0x0800                                       | 0x8000                                      |

| VREF x 2047/4096 | 0x07FF                                       | 0x7FF0                                      |

| 0                | 0x0000                                       | 0x0000                                      |

When the ADC0 Repeat Count is greater than 1, the output conversion code represents the accumulated result of the conversions performed and is updated after the last conversion in the series is finished. Sets of 4, 8, or 16 consecutive samples can be accumulated and represented in unsigned integer format. The repeat count can be selected using the AD0RPT bits in the ADC0CF register. The value must be right-justified (AD0LJST = 0), and unused bits in the ADC0H and ADC0L registers are set to 0. The following example shows right-justified codes for repeat counts greater than 1. Notice that accumulating  $2^n$  samples is equivalent to left-shifting by *n* bit positions when all samples returned from the ADC have the same value.

| Input Voltage                | Repeat Count = 4 | Repeat Count = 8 | Repeat Count = 16 |

|------------------------------|------------------|------------------|-------------------|

| V <sub>REF</sub> x 4095/4096 | 0x3FFC           | 0x7FF8           | 0xFFF0            |

| V <sub>REF</sub> x 2048/4096 | 0x2000           | 0x4000           | 0x8000            |

| V <sub>REF</sub> x 2047/4096 | 0x1FFC           | 0x3FF8           | 0x7FF0            |

| 0                            | 0x0000           | 0x0000           | 0x0000            |

#### 6.2.1. Settling Time Requirements

A minimum tracking time is required before an accurate conversion is performed. This tracking time is determined by any series impedance, including the AMUX0 resistance, the ADC0 sampling capacitance, and the accuracy required for the conversion.

Figure 6.5 shows the equivalent ADC0 input circuit. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 6.1. When measuring the Temperature Sensor output, use the settling time specified in Table 5.10 on page 50. When measuring V<sub>DD</sub> with respect to GND,  $R_{TO-TAL}$  reduces to  $R_{MUX}$ . See Table 5.9 for ADC0 minimum settling time requirements as well as the mux impedance and sampling capacitor values.

$$t = ln\left(\frac{2^{n}}{SA}\right) \times R_{TOTAL}C_{SAMPLE}$$

#### Equation 6.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance.

n is the ADC resolution in bits (10).

Note that false rising edges and falling edges can be detected when the comparator is first powered on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed.

#### SFR Definition 9.1. CPT0CN: Comparator0 Control

| Bit   | 7     | 6      | 5      | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|--------|--------|-------------|---|-------------|---|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0HYP[1:0] |   | CP0HYN[1:0] |   |

| Туре  | R/W   | R      | R/W    | R/W    | R/W         |   | R/          | W |

| Reset | 0     | 0      | 0      | 0      | 0           | 0 | 0           | 0 |

SFR Address = 0x9A; SFR Page = 0x00

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0                                                      |

|     |             | 1: Voltage on CP0+ > CP0                                                      |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3:2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP0HYN[1:0] |                                                                               |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

### SFR Definition 13.3. SFRNEXT: SFR Next

| Bit   | 7            | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------------|-----|---|---|---|---|---|---|--|

| Name  | SFRNEXT[7:0] |     |   |   |   |   |   |   |  |

| Туре  |              | R/W |   |   |   |   |   |   |  |

| Reset | 0            | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |

#### SFR Address = 0x85; SFR Page = All Pages

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SFRNEXT[7:0] | SFR Page Bits.                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |              | This is the value that will go to the SFR Page register upon a return from inter-<br>rupt.                                                                                                                                                                                                                                                                                                                          |

|     |              | Write: Sets the SFR Page contained in the second byte of the SFR Stack. This will cause the SFRPAGE SFR to have this SFR page value upon a return from interrupt.                                                                                                                                                                                                                                                   |

|     |              | Read: Returns the value of the SFR page contained in the second byte of the SFR stack.                                                                                                                                                                                                                                                                                                                              |

|     |              | SFR page context is retained upon interrupts/return from interrupts in a 3 byte<br>SFR Page Stack: SFRPAGE is the first entry, SFRNEXT is the second, and<br>SFRLAST is the third entry. The SFR stack bytes may be used alter the context<br>in the SFR Page Stack, and will not cause the stack to "push" or "pop". Only<br>interrupts and return from interrupts cause pushes and pops of the SFR Page<br>Stack. |

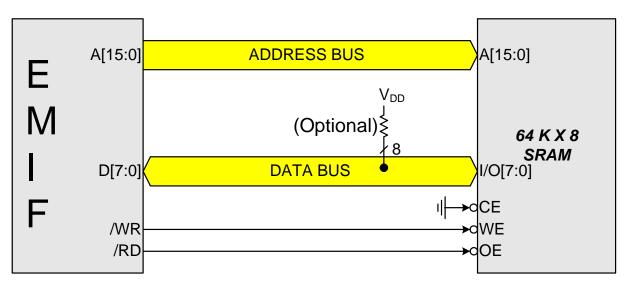

#### 18.4.2. Non-multiplexed Configuration

In Non-multiplexed mode, the Data Bus and the Address Bus pins are not shared. An example of a Nonmultiplexed Configuration is shown in Figure 18.2. See Section "18.6.1. Non-Multiplexed Mode" on page 158 for more information about Non-multiplexed operation.

Figure 18.2. Non-multiplexed Configuration Example

## SFR Definition 19.5. CLKMUL: Clock Multiplier

| Bit   | 7     | 6       | 5      | 4           | 3 | 2 | 1           | 0 |  |

|-------|-------|---------|--------|-------------|---|---|-------------|---|--|

| Name  | MULEN | MULINIT | MULRDY | MULDIV[2:0] |   |   | MULSEL[1:0] |   |  |

| Туре  | R/W   | R/W     | R      | R/W         |   |   | R/          | W |  |

| Reset | 0     | 0       | 0      | 0           | 0 | 0 | 0           | 0 |  |

#### SFR Address = 0x97; SFR Page = 0x0F;

| MULEN       | Clock Multiplier                                                                     | . En al-la                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|             | Clock Multiplier Enable.                                                             |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             |                                                                                      | 0: Clock Multiplier disabled.                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             | 1: Clock Multiplier enabled.                                                         |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| MULINIT     | <b>Clock Multiplier</b>                                                              | Clock Multiplier Initialize.                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             | bit will initialize th                                                               | This bit is 0 when the Clock Multiplier is enabled. Once enabled, writing a 1 to this bit will initialize the Clock Multiplier. The MULRDY bit reads 1 when the Clock Multiplier is stabilized. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| MULRDY      | <b>Clock Multiplier</b>                                                              | Clock Multiplier Ready.                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             | 0: Clock Multiplie                                                                   | er is not ready.                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             | 1: Clock Multiplier is ready (PLL is locked).                                        |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| MULDIV[2:0] | Clock Multiplier Output Scaling Factor.                                              |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             | 000: Clock Multiplier Output scaled by a factor of 1.                                |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             | 001: Clock Multiplier Output scaled by a factor of 1.                                |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             |                                                                                      |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             |                                                                                      |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             |                                                                                      |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             |                                                                                      |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             |                                                                                      |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             | * <b>Note:</b> The Clock Multiplier output duty cycle is not 50% for these settings. |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| MULSEL[1:0] | Clock Multiplier                                                                     | r Input Select.                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             | These bits select the clock supplied to the Clock Multiplier                         |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             | MULSEL[1:0]                                                                          | Selected Input Clock                                                                                                                                                                            | Clock Multiplier Output<br>for MULDIV[2:0] = 000b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|             | 00                                                                                   | Internal Oscillator                                                                                                                                                                             | Internal Oscillator x 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|             | 01 External Oscillator External                                                      |                                                                                                                                                                                                 | External Oscillator x 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|             | 10                                                                                   | Internal Oscillator                                                                                                                                                                             | Internal Oscillator x 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|             | 11                                                                                   | External Oscillator                                                                                                                                                                             | External Oscillator x 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|             | MULRDY                                                                               | MULINITClock Multiplier<br>This bit is 0 whe<br>bit will initialize t<br>tiplier is stabilizeMULRDYClock Multiplier<br>                                                                         | MULINITClock Multiplier Initialize.<br>This bit is 0 when the Clock Multiplier is enabled.<br>bit will initialize the Clock Multiplier. The MULRD<br>tiplier is stabilized.MULRDYClock Multiplier Ready.<br>0: Clock Multiplier is not ready.<br>1: Clock Multiplier Output Scaling Factor.<br>000: Clock Multiplier Output scaled by a factor of<br>001: Clock Multiplier Output scaled by a factor of<br>010: Clock Multiplier Output scaled by a factor of<br>100: Clock Multiplier Output scaled by a factor of<br>100: Clock Multiplier Output scaled by a factor of<br>100: Clock Multiplier Output scaled by a factor of<br>101: Clock Multiplier Output scaled by a factor of<br>101: Clock Multiplier Output scaled by a factor of<br>111: Clock Multiplier Output scaled by a factor of<br>111: Clock Multiplier Output scaled by a factor of<br>*Note: The Clock Multiplier output duty cycle is rMULSEL[1:0]Clock Multiplier Input Select.<br>These bits select the clock supplied to the Clock<br>00MULSEL[1:0]Selected Input Clock00Internal Oscillator01External Oscillator |  |  |  |  |  |  |

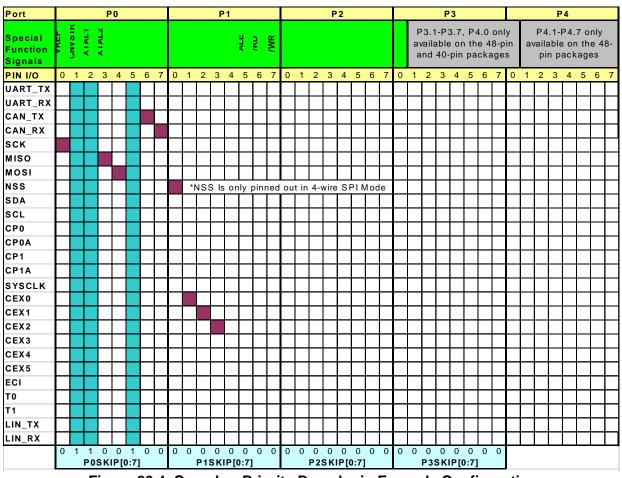

Figure 20.4. Crossbar Priority Decoder in Example Configuration

### 20.4. Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- 4. Assign Port pins to desired peripherals.

- 5. Enable the Crossbar (XBARE = 1).

All Port pins must be configured as either analog or digital inputs. Port 4 on the C8051F500/1/4/5 and C8051F508/9-F510/1 is a digital-only Port. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a 1 indicates a digital input, and a 0 indicates an analog input. All pins default to digital inputs on reset. See SFR Definition

## SFR Definition 20.3. XBR2: Port I/O Crossbar Register 1

| Bit   | 7       | 6     | 5   | 4        | 3   | 2 | 1   | 0   |

|-------|---------|-------|-----|----------|-----|---|-----|-----|

| Name  | WEAKPUD | XBARE |     | Reserved |     |   |     |     |

| Туре  | R/W     | R/W   | R/W | R/W      | R/W | R | R/W | R/W |

| Reset | 0       | 0     | 0   | 0        | 0   | 0 | 0   | 0   |

## SFR Address = 0xC7; SFR Page = 0x0F

| Bit | Name     | Function                                                                                                                                 |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | WEAKPUD  | Port I/O Weak Pullup Disable.                                                                                                            |

|     |          | <ul><li>0: Weak Pullups enabled (except for Ports whose I/O are configured for analog mode).</li><li>1: Weak Pullups disabled.</li></ul> |

| 6   | XBARE    | Crossbar Enable.                                                                                                                         |

|     |          | 0: Crossbar disabled.                                                                                                                    |

|     |          | 1: Crossbar enabled.                                                                                                                     |

| 5:1 | Reserved | Always Write to 00000b.                                                                                                                  |

| 0   | LIN0E    | LIN I/O Output Enable.                                                                                                                   |

|     |          | 0: LIN I/O unavailable at Port pin.                                                                                                      |

|     |          | 1: LIN_TX, LIN_RX routed to Port pins.                                                                                                   |

#### 20.6. Special Function Registers for Accessing and Configuring Port I/O

All Port I/O are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable, except for P4 which is only byte addressable. When writing to a Port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the Crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target a Port Latch register as the destination. The read-modify-write instructions when operating on a Port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a Port SFR. For these instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

Ports 0–3 have a corresponding PnSKIP register which allows its individual Port pins to be assigned to digital functions or skipped by the Crossbar. All Port pins used for analog functions, GPIO, or dedicated digital functions such as the EMIF should have their PnSKIP bit set to 1.

The Port input mode of the I/O pins is defined using the Port Input Mode registers (PnMDIN). Each Port cell can be configured for analog or digital I/O. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is P4, which can only be used for digital I/O.

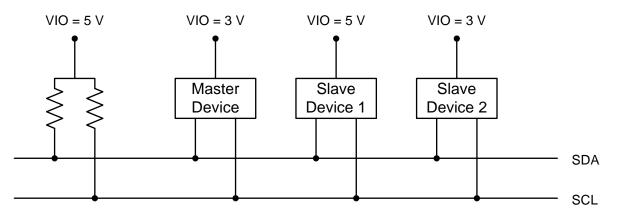

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings.

#### SFR Definition 20.12. P0: Port 0

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---------|---|---|---|---|---|---|---|--|

| Name  | P0[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W     |   |   |   |   |   |   |   |  |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |

SFR Address = 0x80; SFR Page = All Pages; Bit-Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P0[7:0] | <b>Port 0 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P0.n Port pin is logic<br>LOW.<br>1: P0.n Port pin is logic<br>HIGH. |

### SFR Definition 20.21. P2MDIN: Port 2 Input Mode

| Bit   | 7           | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|-------------|-----|---|---|---|---|---|---|--|--|--|--|

| Name  | P2MDIN[7:0] |     |   |   |   |   |   |   |  |  |  |  |

| Туре  |             | R/W |   |   |   |   |   |   |  |  |  |  |

| Reset | 1           | 1   | 1 | 1 | 1 | 1 | 1 | 1 |  |  |  |  |

#### SFR Address = 0xF3; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                  |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P2MDIN[7:0] | Analog Configuration Bits for P2.7–P2.0 (respectively).                                                                                                                                                                                                                                                                                                   |

|     |             | <ul> <li>Port pins configured for analog mode have their weak pull-up and digital receiver disabled. For analog mode, the pin also needs to be configured for open-drain mode in the P2MDOUT register.</li> <li>0: Corresponding P2.n pin is configured for analog mode.</li> <li>1: Corresponding P2.n pin is not configured for analog mode.</li> </ul> |

### SFR Definition 20.22. P2MDOUT: Port 2 Output Mode

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|---|-----------------|---|---|---|---|---|---|--|--|--|--|

| Name  |   | P2MDOUT[7:0]    |   |   |   |   |   |   |  |  |  |  |

| Туре  |   | R/W             |   |   |   |   |   |   |  |  |  |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |  |  |

#### SFR Address = 0xA6; SFR Page = 0x0F

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P2MDOUT[7:0] | Output Configuration Bits for P2.7–P2.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P2MDIN is logic 0.<br>0: Corresponding P2.n Output is open-drain.<br>1: Corresponding P2.n Output is push-pull. |

#### 21.1. Software Interface with the LIN Controller

The selection of the mode (Master or Slave) and the automatic baud rate feature are done though the LIN0 Control Mode (LIN0CF) register. The other LIN registers are accessed indirectly through the two SFRs LIN0 Address (LIN0ADR) and LIN0 Data (LIN0DAT). The LIN0ADR register selects which LIN register is targeted by reads/writes of the LIN0DAT register. The full list of indirectly-accessible LIN registers is given in Table 21.4 on page 210.

#### 21.2. LIN Interface Setup and Operation

The hardware based LIN controller allows for the implementation of both Master and Slave nodes with minimal firmware overhead and complete control of the interface status while allowing for interrupt and polled mode operation.

The first step to use the controller is to define the basic characteristics of the node:

Mode—Master or Slave

Baud Rate—Either defined manually or using the autobaud feature (slave mode only)

Checksum Type—Select between classic or enhanced checksum, both of which are implemented in hardware.

#### 21.2.1. Mode Definition

Following the LIN specification, the controller implements in hardware both the Slave and Master operating modes. The mode is configured using the MODE bit (LIN0CF.6).

#### 21.2.2. Baud Rate Options: Manual or Autobaud

The LIN controller can be selected to have its baud rate calculated manually or automatically. A master node must always have its baud rate set manually, but slave nodes can choose between a manual or automatic setup. The configuration is selected using the ABAUD bit (LIN0CF.5).

Both the manual and automatic baud rate configurations require additional setup. The following sections explain the different options available and their relation with the baud rate, along with the steps necessary to achieve the required baud rate.

#### 21.2.3. Baud Rate Calculations: Manual Mode

The baud rate used by the LIN controller is a function of the System Clock (SYSCLK) and the LIN timing registers according to the following equation:

baud\_rate =  $\frac{SYSCLK}{2^{(prescaler + 1)} \times divider \times (multiplier + 1)}}$

The prescaler, divider and multiplier factors are part of the LIN0DIV and LIN0MUL registers and can assume values in the following range:

| Factor     | Range  |  |  |  |

|------------|--------|--|--|--|

| prescaler  | 03     |  |  |  |

| multiplier | 031    |  |  |  |

| divider    | 200511 |  |  |  |

Table 21.1. Baud Rate Calculation Variable Ranges

Important Note: The minimum system clock (SYSCLK) to operate the LIN controller is 8 MHz.

- 1. Check the DONE bit (LIN0ST.0) and the ERROR bit (LIN0ST.2).

- 2. If performing a master receive operation and the transfer was successful, read the received data from the data buffer.

- 3. If the transfer was not successful, check the error register to determine the kind of error. Further error handling has to be done by the application.

- 4. Set the RSTINT (LIN0CTRL.3) and RSTERR bits (LIN0CTRL.2) to reset the interrupt request and the error flags.

#### 21.4. LIN Slave Mode Operation

When the device is configured for slave mode operation, it must wait for a command from a master node. Access from the firmware to the data buffer and ID registers of the LIN controller is only possible when a data request is pending (DTREQ bit (LINOST.4) is 1) and also when the LIN bus is not active (ACTIVE bit (LINOST.7) is set to 0).

The LIN controller in slave mode detects the header of the message frame sent by the LIN master. If slave synchronization is enabled (autobaud), the slave synchronizes its internal bit time to the master bit time.

The LIN controller configured for slave mode will generated an interrupt in one of three situations:

- 1. After the reception of the IDENTIFIER FIELD

- 2. When an error is detected

- 3. When the message transfer is completed.

The application should perform the following steps when an interrupt is detected:

- 1. Check the status of the DTREQ bit (LIN0ST.4). This bit is set when the IDENTIFIER FIELD has been received.

- 2. If DTREQ (LIN0ST.4) is set, read the identifier from LIN0ID and process it. If DTREQ (LIN0ST.4) is not set, continue to step 7.

- 3. Set the TXRX bit (LIN0CTRL.5) to 1 if the current frame is a transmit operation for the slave and set to 0 if the current frame is a receive operation for the slave.

- 4. Load the data length into LIN0SIZE.

- 5. For a slave transmit operation, load the data to transmit into the data buffer.

- 6. Set the DTACK bit (LIN0CTRL.4). Continue to step 10.

- 7. If DTREQ (LIN0ST.4) is not set, check the DONE bit (LIN0ST.0). The transmission was successful if the DONE bit is set.

- 8. If the transmission was successful and the current frame was a receive operation for the slave, load the received data bytes from the data buffer.

- 9. If the transmission was not successful, check LIN0ERR to determine the nature of the error. Further error handling has to be done by the application.

- 10.Set the RSTINT (LIN0CTRL.3) and RSTERR bits (LIN0CTRL.2) to reset the interrupt request and the error flags.

In addition to these steps, the application should be aware of the following:

- 1. If the current frame is a transmit operation for the slave, steps 1 through 5 must be completed during the IN-FRAME RESPONSE SPACE. If it is not completed in time, a timeout will be detected by the master.

- 2. If the current frame is a receive operation for the slave, steps 1 through 5 have to be finished until the reception of the first byte after the IDENTIFIER FIELD. Otherwise, the internal receive buffer of the LIN controller will be overwritten and a timeout error will be detected in the LIN controller.

- 3. The LIN controller does not directly support LIN Version 1.3 Extended Frames. If the application detects an unknown identifier (e.g. extended identifier), it has to write a 1 to the STOP bit (LIN0CTRL.7) instead

206

#### 21.7.2. LIN Indirect Access SFR Registers Definitions

Table 21.4 lists the 15 indirect registers used to configured and communicate with the LIN controller.

| Name       | Address       | Bit7                         | Bit6                    | Bit5         | Bit4         | Bit3         | Bit2         | Bit1         | Bit0          |  |  |

|------------|---------------|------------------------------|-------------------------|--------------|--------------|--------------|--------------|--------------|---------------|--|--|

| LIN0DT1    | 0x00          | DATA1[7:0]                   |                         |              |              |              |              |              |               |  |  |

| LIN0DT2    | 0x01          |                              | DATA2[7:0]              |              |              |              |              |              |               |  |  |

| LIN0DT3    | 0x02          |                              | DATA3[7:0]              |              |              |              |              |              |               |  |  |

| LIN0DT4    | 0x03          |                              | DATA4[7:0]              |              |              |              |              |              |               |  |  |

| LIN0DT5    | 0x04          |                              | DATA5[7:0]              |              |              |              |              |              |               |  |  |

| LIN0DT6    | 0x05          |                              | DATA67:0]               |              |              |              |              |              |               |  |  |

| LIN0DT7    | 0x06          | DATA7[7:0]                   |                         |              |              |              |              |              |               |  |  |

| LIN0DT8    | 0x07          |                              |                         |              | DATA8        | 8[7:0]       |              |              |               |  |  |

| LIN0CTRL   | 0x08          | STOP(s)                      | SLEEP(s)                | TXRX         | DTACK(s)     | RSTINT       | RSTERR       | WUPREQ       | STREQ(m)      |  |  |

| LIN0ST     | 0x09          | ACTIVE                       | IDLTOUT                 | ABORT(s)     | DTREQ(s)     | LININT       | ERROR        | WAKEUP       | DONE          |  |  |

| LIN0ERR    | 0x0A          |                              |                         |              | SYNCH(s)     | PRTY(s)      | TOUT         | СНК          | BITERR        |  |  |

| LIN0SIZE   | 0x0B          | ENHCHK                       |                         |              |              |              | LINS         | SIZE[3:0]    |               |  |  |

| LIN0DIV    | 0x0C          |                              |                         |              | DIVLSI       | B[7:0]       |              |              |               |  |  |

| LIN0MUL    | 0x0D          | PRESCL[1:0] LINMUL[4:0] DIV9 |                         |              |              |              |              |              |               |  |  |

| LIN0ID     | 0x0E          |                              | ID5 ID4 ID3 ID2 ID1 ID0 |              |              |              |              |              |               |  |  |

| Note: Thes | e registers a | are used in b                | oth master a            | and slave mo | de. The regi | ster bits ma | arked with ( | m) are acces | sible only in |  |  |

### Table 21.4. LIN Registers (Indirectly Addressable)

Note: These registers are used in both master and slave mode. The register bits marked with (m) are accessible only in Master mode while the register bits marked with (s) are accessible only in slave mode. All other registers are accessible in both modes.

#### LIN Register Definition 21.6. LIN0ST: LIN0 Status Register

| Bit   | 7      | 6       | 5     | 4     | 3      | 2     | 1      | 0    |

|-------|--------|---------|-------|-------|--------|-------|--------|------|

| Name  | ACTIVE | IDLTOUT | ABORT | DTREQ | LININT | ERROR | WAKEUP | DONE |

| Туре  | R      | R       | R     | R     | R      | R     | R      | R    |

| Reset | 0      | 0       | 0     | 0     | 0      | 0     | 0      | 0    |

Indirect Address = 0x09

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                          |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ACTIVE | LIN Active Indicator Bit.                                                                                                                                                                                                                                                                                         |

|     |        | 0: No transmission activity detected on the LIN bus.                                                                                                                                                                                                                                                              |

|     |        | 1: Transmission activity detected on the LIN bus.                                                                                                                                                                                                                                                                 |

| 6   | IDLT   | Bus Idle Timeout Bit. (slave mode only)                                                                                                                                                                                                                                                                           |