# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART       |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 33                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 4.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                    |

| Data Converters            | A/D 32x12b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                              |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 40-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 40-QFN (6x6)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f511-imr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 12.2.1.3. Stack                                       | . 99 |

|-------------------------------------------------------|------|

| 13. Special Function Registers                        |      |

| 13.1. SFR Paging                                      |      |

| 13.2. Interrupts and SFR Paging                       | 100  |

| 13.3. SFR Page Stack Example                          |      |

| 14. Interrupts                                        |      |

| 14.1. MCU Interrupt Sources and Vectors               |      |

| 14.1.1. Interrupt Priorities                          |      |

| 14.1.2. Interrupt Latency                             |      |

| 14.2. Interrupt Register <u>Descr</u> iption <u>s</u> |      |

| 14.3. External Interrupts INTO and INT1               | 126  |

| 15. Flash Memory                                      |      |

| 15.1. Programming the Flash Memory                    |      |

| 15.1.1. Flash Lock and Key Functions                  |      |

| 15.1.2. Flash Erase Procedure                         |      |

| 15.1.3. Flash Write Procedure                         |      |

| 15.1.4. Flash Write Optimization                      |      |

| 15.2. Non-volatile Data Storage                       |      |

| 15.3. Security Options                                |      |

| 15.4. Flash Write and Erase Guidelines                | 133  |

| 15.4.1. $V_{DD}$ Maintenance and the $V_{DD}$ monitor |      |

| 15.4.2. PSWE Maintenance                              | 133  |

| 15.4.3. System Clock                                  |      |

| 16. Power Management Modes                            |      |

| 16.1. Idle Mode                                       |      |

| 16.2. Stop Mode                                       |      |

| 16.3. Suspend Mode                                    |      |

| 17. Reset Sources                                     |      |

| 17.1. Power-On Reset                                  |      |

| 17.2. Power-Fail Reset/VDD Monitor                    |      |

| 17.3. External Reset                                  |      |

| 17.4. Missing Clock Detector Reset                    |      |

| 17.5. Comparator0 Reset                               |      |

| 17.6. PCA Watchdog Timer Reset                        |      |

| 17.7. Flash Error Reset                               |      |

| 17.8. Software Reset                                  |      |

| 18. External Data Memory Interface and On-Chip XRAM   |      |

| 18.1. Accessing XRAM                                  |      |

| 18.1.1. 16-Bit MOVX Example                           |      |

| 18.1.2. 8-Bit MOVX Example                            |      |

| 18.2. Configuring the External Memory Interface       | 148  |

| 18.3. Port Configuration                              |      |

| 18.4. Multiplexed and Non-multiplexed Selection       | 153  |

| 18.4.1. Multiplexed Configuration                     |      |

| 18.4.2. Non-multiplexed Configuration                 | 154  |

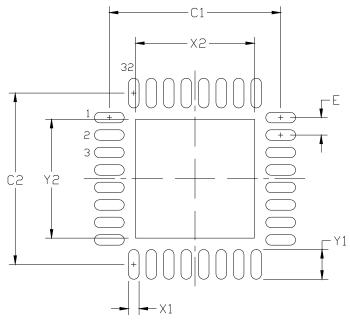

Figure 4.10. QFN-32 Package Drawing

| Dimension | Min      | Мах  | Dimension | Min  | Max  |

|-----------|----------|------|-----------|------|------|

| C1        | 4.80     | 4.90 | X2        | 3.20 | 3.40 |

| C2        | 4.80     | 4.90 | Y1        | 0.75 | 0.85 |

| е         | 0.50 BSC |      | Y2        | 3.20 | 3.40 |

| X1        | 0.20     | 0.30 |           |      |      |

Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

Solder Mask Design

**3.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60μm minimum, all the way around the pad.

Stencil Design

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- 7. A 3x3 array of 1.0 mm openings on a 1.20 mm pitch should be used for the center ground pad.

Card Assembly

- 8. A No-Clean, Type-3 solder paste is recommended.

- **9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### Table 5.2. Global Electrical Characteristics (Continued)

-40 to +125 °C, 24 MHz system clock unless otherwise specified.

| Parameter                                                     | Conditions                                                  | Min     | Тур    | Max    | Units  |

|---------------------------------------------------------------|-------------------------------------------------------------|---------|--------|--------|--------|

| Digital Supply Current—CPU                                    | Inactive (Idle Mode, not fetching inst                      | ructior | s from | Flash) |        |

| I <sub>DD</sub> <sup>4</sup>                                  | V <sub>DD</sub> = 2.1 V, F = 200 kHz                        | _       | 60     | —      | μA     |

|                                                               | V <sub>DD</sub> = 2.1 V, F = 1.5 MHz                        | —       | 460    | —      | μA     |

|                                                               | V <sub>DD</sub> = 2.1 V, F = 25 MHz                         | —       | 7.2    | 8.0    | mA     |

|                                                               | V <sub>DD</sub> = 2.1 V, F = 50 MHz                         | —       | 14     | 16     | mA     |

| I <sub>DD</sub> <sup>4</sup>                                  | V <sub>DD</sub> = 2.6 V, F = 200 kHz                        |         | 75     |        | μA     |

|                                                               | V <sub>DD</sub> = 2.6 V, F = 1.5 MHz                        | —       | 600    | —      | μA     |

|                                                               | V <sub>DD</sub> = 2.6 V, F = 25 MHz                         | —       | 9.3    | 15     | mA     |

|                                                               | V <sub>DD</sub> = 2.6 V, F = 50 MHz                         | —       | 19     | 25     | mA     |

| I <sub>DD</sub> Supply Sensitivity <sup>4</sup>               | F = 25 MHz                                                  | _       | 57     |        | %/V    |

|                                                               | F = 1 MHz                                                   | —       | 56     | —      | 70/ V  |

| I <sub>DD</sub> Frequency Sensitivity <sup>4.6</sup>          | $V_{DD}$ = 2.1V, F $\leq$ 12.5 MHz, T = 25 °C               | —       | 0.29   |        |        |

|                                                               | $V_{DD}$ = 2.1V, F > 12.5 MHz, T = 25 °C                    | —       | 0.29   | —      |        |

|                                                               | $V_{DD}$ = 2.6V, F $\leq$ 12.5 MHz, T = 25 °C               | —       | 0.38   | —      | mA/MHz |

|                                                               | V <sub>DD</sub> = 2.6V, F > 12.5 MHz, T = 25 °C             | —       | 0.38   | —      |        |

| Digital Supply Current <sup>4</sup><br>(Stop or Suspend Mode) | Oscillator not running,<br>V <sub>DD</sub> Monitor Disabled |         |        |        |        |

|                                                               | Temp = 25 °C                                                | —       | 2      | —      | μA     |

|                                                               | Temp = 60 °C                                                | —       | 10     | —      |        |

|                                                               | Temp= 125 °C                                                | —       | 120    | —      |        |

Notes:

1. Given in Table 5.4 on page 46.

2. V<sub>IO</sub> should not be lower than the V<sub>DD</sub> voltage.

3. SYSCLK must be at least 32 kHz to enable debugging.

- 4. Based on device characterization data; Not production tested. Does not include oscillator supply current.

- 5. IDD can be estimated for frequencies ≤ 12.5 MHz by simply multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate I<sub>DD</sub> for >12.5 MHz, the estimate should be the current at 50 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 2.6 V; F = 20 MHz, I<sub>DD</sub> = 26 mA (50 MHz 20 MHz) \* 0.48 mA/MHz = 11.6 mA.

- 6. Idle IDD can be estimated for frequencies ≤ 1 MHz by simply multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate Idle I<sub>DD</sub> for >1 MHz, the estimate should be the current at 50 MHz minus the difference in current indicated by the frequency sensitivity number.

For example:  $V_{DD}$  = 2.6 V; F = 5 MHz, Idle I<sub>DD</sub> = 21 mA – (50 MHz – 5 MHz) x 0.41 mA/MHz = 2.6 mA.

#### Table 5.6. Internal High-Frequency Oscillator Electrical Characteristics

V<sub>DD</sub> = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified; Using factory-calibrated settings.

| Parameter                                            | Conditions                                      | Min              | Тур             | Max       | Units               |

|------------------------------------------------------|-------------------------------------------------|------------------|-----------------|-----------|---------------------|

| Oscillator Frequency                                 | IFCN = 111b;<br>VDD $\geq$ VREGMIN <sup>1</sup> | 24 – 0.5%        | 24 <sup>2</sup> | 24 + 0.5% | MHz                 |

|                                                      | IFCN = 111b;<br>VDD < VREGMIN <sup>1</sup>      | 24 – 1.0%        | 24 <sup>2</sup> | 24 + 1.0% |                     |

| Oscillator Supply Current<br>(from V <sub>DD</sub> ) | Internal Oscillator On<br>OSCICN[7:6] = 11b     | _                | 830             | 1300      | μA                  |

| Internal Oscillator Suspend                          | Temp = 25 °C                                    | —                | 66              | _         | μA                  |

| OSCICN[7:6] = 00b                                    | Temp = 85 °C                                    | —                | 110             | —         |                     |

| ZTCEN = 1                                            | Temp = 125 °C                                   | —                | 190             | —         |                     |

| Wake-up Time From Suspend                            | OSCICN[7:6] = 00b                               | —                | 1               | —         | μs                  |

| Power Supply Sensitivity                             | Constant Temperature                            | —                | 0.10            | _         | %/V                 |

| Temperature Sensitivity <sup>3</sup>                 | Constant Supply                                 |                  |                 |           |                     |

|                                                      | TC <sub>1</sub>                                 | —                | 5.0             | —         | ppm/°C              |

|                                                      | TC <sub>2</sub>                                 | —                | -0.65           | —         | ppm/°C <sup>2</sup> |

| 1 VREGMIN is the minimum (                           | output of the voltage regulator for             | r its low settin | a (REGO         |           | = 0b) See           |

VREGMIN is the minimum output of the voltage regulator for its low setting (REG0CN: REG0MD = 0b). See Table 5.8, "Voltage Regulator Electrical Characteristics," on page 48.

2. This is the average frequency across the operating temperature range.

3. Use temperature coefficients TC<sub>1</sub> and TC<sub>2</sub> to calculate the new internal oscillator frequency using the following equation:

$f(T) = f0 x (1 + TC_1 x (T - T0) + TC_2 x (T - T0)^2)$

where f0 is the internal oscillator frequency at 25 °C and T0 is 25 °C.

### SFR Definition 6.5. ADC0H: ADC0 Data Word MSB

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------------|---|---|---|---|---|---|

| Name  |   | ADC0H[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W        |   |   |   |   |   |   |

| Reset | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xBE; SFR Page = 0x00

| Bit | Name       | Function                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------|

| 7:0 | ADC0H[7:0] | ADC0 Data Word High-Order Bits.                                                                        |

|     |            | For AD0LJST = 0 and AD0RPT as follows:                                                                 |

|     |            | 00: Bits 3–0 are the upper 4 bits of the 12-bit result. Bits 7–4 are 0000b.                            |

|     |            | 01: Bits 4–0 are the upper 5 bits of the 14-bit result. Bits 7–5 are 000b.                             |

|     |            | 10: Bits 5–0 are the upper 6 bits of the 15-bit result. Bits 7–6 are 00b.                              |

|     |            | 11: Bits 7–0 are the upper 8 bits of the 16-bit result.                                                |

|     |            | For AD0LJST = 1 (AD0RPT must be 00): Bits 7–0 are the most-significant bits of the ADC0 12-bit result. |

#### SFR Definition 6.6. ADC0L: ADC0 Data Word LSB

| Bit   | 7   | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|-----------------|---|---|---|---|---|---|

| Name  |     | ADC0L[7:0]      |   |   |   |   |   |   |

| Туре  | R/W |                 |   |   |   |   |   |   |

| Reset | 0   | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |

SFR Address = 0xBD; SFR Page = 0x00

| Bit | Name | Function                                                                                                                                                                                                                                     |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 |      | <b>ADC0 Data Word Low-Order Bits.</b><br>For AD0LJST = 0: Bits 7–0 are the lower 8 bits of the ADC0 Accumulated Result.<br>For AD0LJST = 1 (AD0RPT must be '00'): Bits 7–4 are the lower 4 bits of the 12-bit<br>result. Bits 3–0 are 0000b. |

### SFR Definition 9.4. CPT1MD: Comparator1 Mode Selection

| Bit   | 7 | 6 | 5      | 4      | 3 | 2 | 1    | 0      |

|-------|---|---|--------|--------|---|---|------|--------|

| Name  |   |   | CP1RIE | CP1FIE |   |   | CP1M | D[1:0] |

| Туре  | R | R | R/W    | R/W    | R | R | R/W  |        |

| Reset | 0 | 0 | 0      | 0      | 0 | 0 | 1    | 0      |

#### SFR Address = 0x9E; SFR Page = 0x00

| Bit | Name       | Function                                                                   |

|-----|------------|----------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b, Write = Don't Care.                                            |

| 5   | CP1RIE     | Comparator1 Rising-Edge Interrupt Enable.                                  |

|     |            | 0: Comparator1 Rising-edge interrupt disabled.                             |

|     |            | 1: Comparator1 Rising-edge interrupt enabled.                              |

| 4   | CP1FIE     | Comparator1 Falling-Edge Interrupt Enable.                                 |

|     |            | 0: Comparator1 Falling-edge interrupt disabled.                            |

|     |            | 1: Comparator1 Falling-edge interrupt enabled.                             |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                            |

| 1:0 | CP1MD[1:0] | Comparator1 Mode Select.                                                   |

|     |            | These bits affect the response time and power consumption for Comparator1. |

|     |            | 00: Mode 0 (Fastest Response Time, Highest Power Consumption)              |

|     |            | 01: Mode 1                                                                 |

|     |            | 10: Mode 2                                                                 |

|     |            | 11: Mode 3 (Slowest Response Time, Lowest Power Consumption)               |

### SFR Definition 9.6. CPT1MX: Comparator1 MUX Selection

| Bit   | 7             | 6               | 5                 | 4         | 3          | 2 | 1 | 0 |  |

|-------|---------------|-----------------|-------------------|-----------|------------|---|---|---|--|

| Nam   | е             | CMX1            | N[3:0] CMX1P[3:0] |           |            |   | • |   |  |

| Туре  | e             | R/              | W                 |           | R/W        |   |   |   |  |

| Rese  | et 0          | 1               | 1                 | 1         | 0          | 1 | 1 | 1 |  |

| SFR A | Address = 0x9 | <br>F: SER Page | - 0x00            |           |            |   |   |   |  |

| Bit   | Name          |                 | - 0,00            |           | Function   |   |   |   |  |

| 7:4   | CMX1N[3:0]    | Comparato       | r1 Negative       | Input MUX | Selection. |   |   |   |  |

|       |               | 0000:           | P0.1              | -         |            |   |   |   |  |

|       |               | 0001:           | P0.3              |           |            |   |   |   |  |

|       |               | 0010:           | P0.               |           |            |   |   |   |  |

|       |               | 0011:           | P0.1              |           |            |   |   |   |  |

|       |               | 0100:           | P1.1              | 1         |            |   |   |   |  |

|       |               | 0101:           | P1.3              | 3         |            |   |   |   |  |

|       |               | 0110:           | P1.               | 5         |            |   |   |   |  |

|       |               | 0111:           | P1.               | 7         |            |   |   |   |  |

|       |               | 1000:           | P2.1              | 1         |            |   |   |   |  |

|       |               | 1001:           | P2.3              | 3         |            |   |   |   |  |

|       |               | 1010:           | P2.               | 5         |            |   |   |   |  |

|       |               | 1011:           | P2.1              |           |            |   |   |   |  |

|       |               | 1100–1111:      | Nor               | ne        |            |   |   |   |  |

| 3:0   | CMX1P[3:0]    | Comparato       | r1 Positive       | Input MUX | Selection. |   |   |   |  |

|       |               | 0000:           | P0.0              | 0         |            |   |   |   |  |

|       |               | 0001:           | P0.2              | 2         |            |   |   |   |  |

|       |               | 0010:           | P0.4              | 4         |            |   |   |   |  |

|       |               | 0011:           | P0.0              |           |            |   |   |   |  |

|       |               | 0100:           | P1.0              |           |            |   |   |   |  |

|       |               | 0101:           | P1.2              |           |            |   |   |   |  |

|       |               | 0110:           | P1.4              |           |            |   |   |   |  |

|       |               | 0111:           | P1.0              |           |            |   |   |   |  |

|       |               | 1000:           | P2.0              |           |            |   |   |   |  |

|       |               | 1001:           | P2.2              |           |            |   |   |   |  |

|       |               | 1010:           | P2.4              |           |            |   |   |   |  |

|       |               | 1011:           | P2.0              |           |            |   |   |   |  |

|       |               | 1100–1111:      | Nor               | ne        |            |   |   |   |  |

### 11. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware (see description in Section 28), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 11.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 50 MIPS Peak Throughput with 50 MHz Clock

- 0 to 50 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

#### 11.1. Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

#### 11.2. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 11.2.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 11.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

### SFR Definition 11.3. SP: Stack Pointer

| Bit     | 7               | 6          | 5           | 4 | 3 | 2 | 1 | 0 |

|---------|-----------------|------------|-------------|---|---|---|---|---|

| Name    | SP[7:0]         |            |             |   |   |   |   |   |

| Туре    | R/W             |            |             |   |   |   |   |   |

| Reset   | 0 0 0 0 0 1 1 1 |            |             |   |   |   |   |   |

| SFR Add | dress = 0x81    | ; SFR Page | = All Pages |   |   |   |   |   |

| Bit | Name    | Function                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                                 |

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

#### SFR Definition 11.4. ACC: Accumulator

| Bit    | 7           | 6           | 5             | 4            | 3     | 2 | 1 | 0 |

|--------|-------------|-------------|---------------|--------------|-------|---|---|---|

| Name   |             | ACC[7:0]    |               |              |       |   |   |   |

| Туре   |             | R/W         |               |              |       |   |   |   |

| Reset  | 0           | 0           | 0             | 0            | 0     | 0 | 0 | 0 |

| SFR Ad | dress = 0xE | 0; SFR Page | e = All Pages | ; Bit-Addres | sable |   |   |   |

| Rit    | Name        |             |               |              |       |   |   |   |

| Bit | Name     | Function                                                    |

|-----|----------|-------------------------------------------------------------|

| 7:0 | ACC[7:0] | Accumulator.                                                |

|     |          | This register is the accumulator for arithmetic operations. |

#### SFR Definition 11.5. B: B Register

| Bit 7 6          | Э               | 4 | 3 | 2 | 1 | 0 |  |

|------------------|-----------------|---|---|---|---|---|--|

| Name             | B[7:0]          |   |   |   |   |   |  |

| Туре             | R/W             |   |   |   |   |   |  |

| <b>Reset</b> 0 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |  |

SFR Address = 0xF0; SFR Page = All Pages; Bit-Addressable

| Bit | Name   | Function                                                                        |

|-----|--------|---------------------------------------------------------------------------------|

| 7:0 | B[7:0] | B Register.                                                                     |

|     |        | This register serves as a second accumulator for certain arithmetic operations. |

#### 11.4. Serial Number Special Function Registers (SFRs)

The C8051F50x/F51x devices include four SFRs, SN0 through SN3, that are pre-programmed during production with a unique, 32-bit serial number. The serial number provides a unique identification number for each device and can be read from the application firmware. If the serial number is not used in the application, these four registers can be used as general purpose SFRs.

#### SFR Definition 11.7. SNn: Serial Number n

| Bit               | 7              | 6            | 5                          | 4             | 3            | 2            | 1            | 0        |  |

|-------------------|----------------|--------------|----------------------------|---------------|--------------|--------------|--------------|----------|--|

| Name SERNUMn[7:0] |                |              |                            |               |              |              |              |          |  |

| Тур               | e              | R/W          |                            |               |              |              |              |          |  |

| Rese              | et             |              | Varies—Unique 32-bit value |               |              |              |              |          |  |

| SFR /             | Addresses: SN0 | ) = 0xF9; SN | V1 = 0xFA;                 | SN2 = 0xFB;   | SN3 = 0xFC   | ; SFR Pag    | e = 0x0F;    |          |  |

| Bit               | Name           |              |                            |               | Function     |              |              |          |  |

| 7:0               | SERNUMn[7:0    | D] Serial N  | umber Bits                 | 5.            |              |              |              |          |  |

|                   |                | The four     | serial num                 | her registers | form a 32-bi | t serial num | ber, with SN | 3 as the |  |

|                   | -              |             | -           |             |               | -            |             |             |

|-------------------|----------------|-------------|-------------|-------------|---------------|--------------|-------------|-------------|

| SSS               | u 0(8)         | 1(9)        | 2(A)        | 3(B)        | 4(C)          | 5(D)         | 6(E)        | 7(F)        |

| ddres:            |                |             |             |             |               |              |             |             |

| Address           | <mark>л</mark> |             |             |             |               |              |             |             |

| F8 C              | SPI0CN         | PCA0L       | PCA0H       | PCA0CPL0    | PCA0CPH0      | PCACPL4      | PCACPH4     | VDM0CN      |

| F                 |                | SN0         | SN1         | SN2         | SN3           |              |             |             |

| F0 C              | B              | POMAT       | POMASK      | P1MAT       | P1MASK        |              | EIP1        | EIP2        |

|                   |                |             |             |             |               |              |             |             |

| L L               | (All Pages)    | POMDIN      | P1MDIN      | P2MDIN      | P3MDIN        |              | EIP1        | EIP2        |

| E8 <mark>0</mark> | ADC0CN         | PCA0CPL1    | PCA0CPH1    | PCA0CPL2    | PCA0CPH2      | PCA0CPL3     | PCA0CPL3    | RSTSRC      |

| F                 | -              |             |             |             |               |              |             |             |

| E0 C              | ACC            |             |             |             |               |              | EIE1        | EIE2        |

| F                 | (All Pages)    | XBR0        | XBR1        | CCH0CN      | IT01CF        |              | (All Pages) | (All Pages) |

|                   |                | PCA0MD      |             |             | PCA0CPM2      |              |             |             |

| D8 0              | PCAUCIN        |             | PCAUCPINIU  | PCAUCPINIT  | PCAUCPINZ     | PCAUCPINI3   | PCAUCPIN4   | PCAUCPIND   |

| L L               |                | PCA0PWM     |             |             |               |              |             |             |

| D0 <mark>0</mark> |                | REF0CN      | LIN0DATA    | LIN0ADDR    |               |              |             |             |

| F                 | (All Pages)    |             |             |             | P0SKIP        | P1SKIP       | P2SKIP      | P3SKIP      |

| C8                |                | REG0CN      | TMR2RLL     | TMR2RLH     | TMR2L         | TMR2H        | PCA0CPL5    | PCA0CPH5    |

| F                 |                | LIN0CF      |             |             |               |              |             |             |

|                   |                |             |             |             | ADC0GTH       | ADC0LTL      | ADC0LTH     |             |

|                   | SMB0CN         | SMB0CF      | SMB0DAT     | ADC0GTL     | ADCOGTH       | ADCULIL      | ADCULIH     | VDDA        |

| ŀ                 |                |             |             |             |               |              |             | XBR2        |

| B8 C              | IP             |             | ADC0TK      | ADC0MX      | ADC0CF        | ADC0L        | ADC0H       |             |

| F                 | (All Pages)    |             |             |             |               |              |             |             |

| B0 C              |                | P2MAT       | P2MASK      |             |               | P4           | FLSCL       | FLKEY       |

| F                 | (All Pages)    |             | EMIOCF      |             |               | (All Pages)  | (All Pages) | (All Pages) |

|                   |                |             |             |             |               | (All 1 ages) | , ,         |             |

| A8 <mark>C</mark> |                | SMOD0       | EMI0CN      | 000010      | 000110        | 0001110      | P3MAT       | P3MASK      |

| F                 | (All Pages)    |             | EMI0TC      | SBCON0      | SBRLL0        | SBRLH0       | P3MDOUT     | P4MDOUT     |

| A0 C              |                | SPI0CFG     | SPI0CKR     | SPI0DAT     |               |              |             | SFRPAGE     |

| F                 | (All Pages)    | OSCICN      | OSCICRS     |             | POMDOUT       | P1MDOUT      | P2MDOUT     | (All Pages) |

| 98 0              |                | SBUF0       | CPT0CN      | CPT0MD      | <b>CPT0MX</b> | CPT1CN       | CPT1MD      | CPT1MX      |

|                   |                | 02010       | 0           | or rome     | 0             | 0            | OSCIFIN     | OSCXCN      |

|                   | P1             | TMDOON      |             | TMDODULI    |               | TMDOLL       |             |             |

| 90 0              |                | TMR3CN      | TMR3RLL     | TMR3RLH     | TMR3L         | TMR3H        |             |             |

| ŀ                 | (All Pages)    |             |             |             |               |              |             | CLKMUL      |

| 88 <mark>0</mark> | TCON           | TMOD        | TL0         | TL1         | TH0           | TH1          | CKCON       | PSCTL       |

| F                 | (All Pages)    | (All Pages) | (All Pages) | (All Pages) | (All Pages)   | (All Pages)  | (All Pages) | CLKSEL      |

| 80 0              | _              | SP          | DPL         | DPH         | - /           | SFRNEXT      | SFRLAST     | PCON        |

| F                 | (All Pages)    | (All Pages) | (All Pages) | (All Pages) | SFR0CN        | (All Pages)  | (All Pages) | (All Pages) |

| Ľ                 | 0(8)           |             |             |             |               |              |             |             |

|                   | · · /          | 1(9)        | 2(A)        | 3(B)        | 4(C)          | 5(D)         | 6(E)        | 7(F)        |

|                   | (bit addres    | sable)      |             |             |               |              |             |             |

#### Table 13.1. Special Function Register (SFR) Memory Map for Pages 0x0 and 0xF

#### SFR Definition 14.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7     | 6   | 5    | 4    | 3     | 2     | 1      | 0     |

|-------|-------|-----|------|------|-------|-------|--------|-------|

| Name  | ELIN0 | ET3 | ECP1 | ECP0 | EPCA0 | EADC0 | EWADC0 | ESMB0 |

| Туре  | R/W   | R/W | R/W  | R/W  | R/W   | R/W   | R/W    | R/W   |

| Reset | 0     | 0   | 0    | 0    | 0     | 0     | 0      | 0     |

#### SFR Address = 0xE6; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                                                          |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ELIN0  | Enable LIN0 Interrupt.<br>This bit sets the masking of the LIN0 interrupt.<br>0: Disable LIN0 interrupts.<br>1: Enable interrupt requests generated by the LIN0INT flag.                                                                                                          |

| 6   | ET3    | <ul> <li>Enable Timer 3 Interrupt.</li> <li>This bit sets the masking of the Timer 3 interrupt.</li> <li>0: Disable Timer 3 interrupts.</li> <li>1: Enable interrupt requests generated by the TF3L or TF3H flags.</li> </ul>                                                     |

| 5   | ECP1   | <ul> <li>Enable Comparator1 (CP1) Interrupt.</li> <li>This bit sets the masking of the CP1 interrupt.</li> <li>0: Disable CP1 interrupts.</li> <li>1: Enable interrupt requests generated by the CP1RIF or CP1FIF flags.</li> </ul>                                               |

| 4   | ECP0   | <ul> <li>Enable Comparator0 (CP0) Interrupt.</li> <li>This bit sets the masking of the CP0 interrupt.</li> <li>0: Disable CP0 interrupts.</li> <li>1: Enable interrupt requests generated by the CP0RIF or CP0FIF flags.</li> </ul>                                               |

| 3   | EPCA0  | <ul> <li>Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> </ul>                                              |

| 2   | EADC0  | <ul> <li>Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> </ul>          |

| 1   | EWADC0 | <ul> <li>Enable Window Comparison ADC0 Interrupt.</li> <li>This bit sets the masking of ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).</li> </ul> |

| 0   | ESMB0  | Enable SMBus (SMB0) Interrupt.<br>This bit sets the masking of the SMB0 interrupt.<br>0: Disable all SMB0 interrupts.<br>1: Enable interrupt requests generated by SMB0.                                                                                                          |

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT1 external interrupts, respectively. If an INT0 or INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

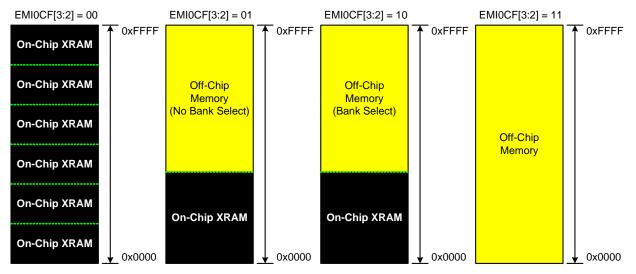

#### **18.5. Memory Mode Selection**

The external data memory space can be configured in one of four modes, shown in Figure 18.3, based on the EMIF Mode bits in the EMIOCF register (SFR Definition 18.2). These modes are summarized below. More information about the different modes can be found in Section "18.6. Timing" on page 156.

Figure 18.3. EMIF Operating Modes

#### 18.5.1. Internal XRAM Only

When bits EMI0CF[3:2] are set to 00, all MOVX instructions will target the internal XRAM space on the device. Memory accesses to addresses beyond the populated space will wrap on 4 kB boundaries. As an example, the addresses 0x1000 and 0x2000 both evaluate to address 0x0000 in on-chip XRAM space.

- 8-bit MOVX operations use the contents of EMI0CN to determine the high-byte of the effective address and R0 or R1 to determine the low-byte of the effective address.

- 16-bit MOVX operations use the contents of the 16-bit DPTR to determine the effective address.

#### 18.5.2. Split Mode without Bank Select

When bit EMI0CF.[3:2] are set to 01, the XRAM memory map is split into two areas, on-chip space and offchip space.

- Effective addresses below the internal XRAM size boundary will access on-chip XRAM space.

- Effective addresses above the internal XRAM size boundary will access off-chip space.

- 8-bit MOVX operations use the contents of EMI0CN to determine whether the memory access is onchip or off-chip. However, in the "No Bank Select" mode, an 8-bit MOVX operation will not drive the upper 8-bits A[15:8] of the Address Bus during an off-chip access. This allows the user to manipulate the upper address bits at will by setting the Port state directly via the port latches. This behavior is in contrast with "Split Mode with Bank Select" described below. The lower 8-bits of the Address Bus A[7:0] are driven, determined by R0 or R1.

- 16-bit MOVX operations use the contents of DPTR to determine whether the memory access is on-chip or off-chip, and unlike 8-bit MOVX operations, the full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

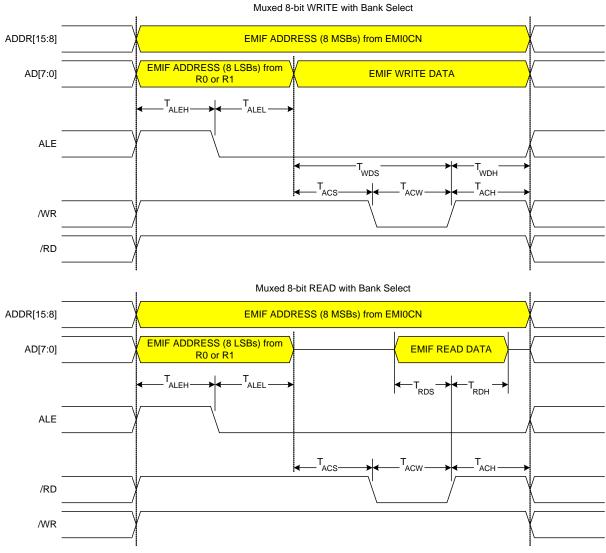

Figure 18.9. Multiplexed 8-bit MOVX with Bank Select Timing

#### 20.2.3. Assigning Port I/O Pins to External Digital Event Capture Functions

External digital event capture functions can be used to trigger an interrupt or wake the device from a low power mode when a transition occurs on a digital I/O pin. The digital event capture functions do not require dedicated pins and will function on both GPIO pins (PnSKIP = 1) and pins in use by the Crossbar (PnSKIP = 0). External digital event capture functions cannot be used on pins configured for analog I/O. Table 20.3 shows all available external digital event capture functions.

| Potentially Assignable Port Pins | SFR(s) used for<br>Assignment                                    |

|----------------------------------|------------------------------------------------------------------|

| P1.0–P1.7                        | IT01CF                                                           |

| P1.0–P1.7                        | IT01CF                                                           |

| P0.0–P3.7*                       | POMASK, POMAT<br>P1MASK, P1MAT<br>P2MASK, P2MAT<br>P3MASK, P3MAT |

|                                  | P1.0–P1.7<br>P1.0–P1.7                                           |

Table 20.3. Port I/O Assignment for External Digital Event Capture Functions

#### 20.3. Priority Crossbar Decoder

The Priority Crossbar Decoder (Figure 20.3) assigns a priority to each I/O function, starting at the top with UART0. When a digital resource is selected, the least-significant unassigned Port pin is assigned to that resource excluding UART0, which is always assigned to pins P0.4 and P0.5, and excluding CAN0 which is always assigned to pins P0.6 and P0.7. If a Port pin is assigned, the Crossbar skips that pin when assigning the next selected resource. Additionally, the Crossbar will skip Port pins whose associated bits in the PnSKIP registers are set. The PnSKIP registers allow software to skip Port pins that are to be used for analog input, dedicated functions, or GPIO.

Because of the nature of Priority Crossbar Decoder, not all peripherals can be located on all port pins. Figure 20.3 maps peripherals to the potential port pins on which the peripheral I/O can appear.

**Important Note on Crossbar Configuration:** If a Port pin is claimed by a peripheral without use of the Crossbar, its corresponding PnSKIP bit should be set. This applies to P0.0 if VREF is used, P0.1 if the ADC is configured to use the external conversion start signal (CNVSTR), P0.3 and/or P0.2 if the external oscillator circuit is enabled, and any selected ADC or Comparator inputs. The Crossbar skips selected pins as if they were already assigned, and moves to the next unassigned pin.

#### SFR Definition 20.23. P2SKIP: Port 2 Skip

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | P2SKIP[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xD6; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P2SKIP[7:0] | Port 2 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |

|     |             | <ul> <li>These bits select Port 2 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P2.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P2.n pin is skipped by the Crossbar.</li> </ul> |

#### SFR Definition 20.24. P3: Port 3

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| Name  | P3[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W     |   |   |   |   |   |   |   |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

#### SFR Address = 0xB0; SFR Page = All Pages; Bit-Addressable

| Bit   | Name                                                                       | Description                                                                                                                                   | Write                                                                         | Read                                                                    |  |  |  |  |

|-------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|

| 7:0   | P3[7:0]                                                                    | <b>Port 3 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P3.n Port pin is logic<br>LOW.<br>1: P3.n Port pin is logic<br>HIGH. |  |  |  |  |

| Note: | Note: Port P3.1–P3.7 are only available on the 48-pin and 40-pin packages. |                                                                                                                                               |                                                                               |                                                                         |  |  |  |  |

- 1. Check the DONE bit (LIN0ST.0) and the ERROR bit (LIN0ST.2).

- 2. If performing a master receive operation and the transfer was successful, read the received data from the data buffer.

- 3. If the transfer was not successful, check the error register to determine the kind of error. Further error handling has to be done by the application.

- 4. Set the RSTINT (LIN0CTRL.3) and RSTERR bits (LIN0CTRL.2) to reset the interrupt request and the error flags.

#### 21.4. LIN Slave Mode Operation

When the device is configured for slave mode operation, it must wait for a command from a master node. Access from the firmware to the data buffer and ID registers of the LIN controller is only possible when a data request is pending (DTREQ bit (LINOST.4) is 1) and also when the LIN bus is not active (ACTIVE bit (LINOST.7) is set to 0).

The LIN controller in slave mode detects the header of the message frame sent by the LIN master. If slave synchronization is enabled (autobaud), the slave synchronizes its internal bit time to the master bit time.

The LIN controller configured for slave mode will generated an interrupt in one of three situations:

- 1. After the reception of the IDENTIFIER FIELD

- 2. When an error is detected

- 3. When the message transfer is completed.

The application should perform the following steps when an interrupt is detected:

- 1. Check the status of the DTREQ bit (LIN0ST.4). This bit is set when the IDENTIFIER FIELD has been received.

- 2. If DTREQ (LIN0ST.4) is set, read the identifier from LIN0ID and process it. If DTREQ (LIN0ST.4) is not set, continue to step 7.

- 3. Set the TXRX bit (LIN0CTRL.5) to 1 if the current frame is a transmit operation for the slave and set to 0 if the current frame is a receive operation for the slave.

- 4. Load the data length into LIN0SIZE.

- 5. For a slave transmit operation, load the data to transmit into the data buffer.

- 6. Set the DTACK bit (LIN0CTRL.4). Continue to step 10.

- 7. If DTREQ (LIN0ST.4) is not set, check the DONE bit (LIN0ST.0). The transmission was successful if the DONE bit is set.

- 8. If the transmission was successful and the current frame was a receive operation for the slave, load the received data bytes from the data buffer.

- 9. If the transmission was not successful, check LIN0ERR to determine the nature of the error. Further error handling has to be done by the application.

- 10.Set the RSTINT (LIN0CTRL.3) and RSTERR bits (LIN0CTRL.2) to reset the interrupt request and the error flags.

In addition to these steps, the application should be aware of the following:

- 1. If the current frame is a transmit operation for the slave, steps 1 through 5 must be completed during the IN-FRAME RESPONSE SPACE. If it is not completed in time, a timeout will be detected by the master.

- 2. If the current frame is a receive operation for the slave, steps 1 through 5 have to be finished until the reception of the first byte after the IDENTIFIER FIELD. Otherwise, the internal receive buffer of the LIN controller will be overwritten and a timeout error will be detected in the LIN controller.

- 3. The LIN controller does not directly support LIN Version 1.3 Extended Frames. If the application detects an unknown identifier (e.g. extended identifier), it has to write a 1 to the STOP bit (LIN0CTRL.7) instead

206