Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | Coldfire V1                                                           |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 50MHz                                                                 |

| Connectivity               | Ethernet, I <sup>2</sup> C, SCI, SPI                                  |

| Peripherals                | LVD, PWM, WDT                                                         |

| Number of I/O              | 54                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 24K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 12x12b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcf51cn128clh |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Part Number   | Package Description | Original (gold wire) package document number | Current (copper wire) package document number |

|---------------|---------------------|----------------------------------------------|-----------------------------------------------|

| MC68HC908JW32 | 48 QFN              | 98ARH99048A                                  | 98ASA00466D                                   |

| MC9S08AC16    |                     |                                              |                                               |

| MC9S908AC60   |                     |                                              |                                               |

| MC9S08AC128   |                     |                                              |                                               |

| MC9S08AW60    |                     |                                              |                                               |

| MC9S08GB60A   |                     |                                              |                                               |

| MC9S08GT16A   |                     |                                              |                                               |

| MC9S08JM16    |                     |                                              |                                               |

| MC9S08JM60    |                     |                                              |                                               |

| MC9S08LL16    |                     |                                              |                                               |

| MC9S08QE128   |                     |                                              |                                               |

| MC9S08QE32    |                     |                                              |                                               |

| MC9S08RG60    |                     |                                              |                                               |

| MCF51CN128    |                     |                                              |                                               |

| MC9RS08LA8    | 48 QFN              | 98ARL10606D                                  | 98ASA00466D                                   |

| MC9S08GT16A   | 32 QFN              | 98ARH99035A                                  | 98ASA00473D                                   |

| MC9S908QE32   | 32 QFN              | 98ARE10566D                                  | 98ASA00473D                                   |

| MC9S908QE8    | 32 QFN              | 98ASA00071D                                  | 98ASA00736D                                   |

| MC9S08JS16    | 24 QFN              | 98ARL10608D                                  | 98ASA00734D                                   |

| MC9S08QB8     |                     |                                              |                                               |

| MC9S08QG8     | 24 QFN              | 98ARL10605D                                  | 98ASA00474D                                   |

| MC9S08SH8     | 24 QFN              | 98ARE10714D                                  | 98ASA00474D                                   |

| MC9RS08KB12   | 24 QFN              | 98ASA00087D                                  | 98ASA00602D                                   |

| MC9S08QG8     | 16 QFN              | 98ARE10614D                                  | 98ASA00671D                                   |

| MC9RS08KB12   | 8 DFN               | 98ARL10557D                                  | 98ASA00672D                                   |

| MC9S08QG8     |                     |                                              |                                               |

| MC9RS08KA2    | 6 DFN               | 98ARL10602D                                  | 98ASA00735D                                   |

## Freescale Semiconductor

Data Sheet: Technical Data

## Document Number: MCF51CN128

Rev. 4, 5/2009

# MCF51CN128 ColdFire Microcontroller Cover: MCF51CN128

The MCF51CN128 device is a low-cost, low-power, high-performance 32-bit ColdFire V1 microcontroller (MCU) featuring 10/100 BASE-T/TX fast ethernet controller (FEC), media independent interface (MII) to connect an external physical transceiver (PHY), and multi-function external bus interface.

MCF51CN128 also has multiple communication interfaces for various ethernet gateway applications. MCF51CN128 is the first ColdFire V1 device to incorporate ethernet and external bus interface along with new features to minimize power consumption and increase functionality in low-power modes.

The MCF51CN128 features the following functional units:

- 32-bit ColdFire V1 Central Processing Unit (CPU)

- Up to 50.33 MHz ColdFire CPU from 3.6 V to 3.0 V, up to 40 MHz CPU from 3.0 V to 2.1 V, and up to 20 MHz CPU from 2.1 V to 1.8 V across temperature range of -40 °C to 85 °C

- Provides 0.94 Dhrystone 2.1 MIPS per MHz performance when running from internal RAM (0.76 DMIPS/MHz from flash)

- ColdFire Instruction Set Revision C (ISA C)

- Support for up to 45 peripheral interrupt requests and 7 software interrupts

- · On-Chip Memory

- 128 KB Flash, 24 KB RAM

- Flash read/program/erase over full operating voltage and temperature

- On-chip memory aliased to create a contiguous memory space with off-chip memory

- Security circuitry to prevent unauthorized access to Peripherals, RAM, and flash contents

- Ethernet

- FEC—10/100 BASE-T/TX, bus-mastering fast ethernet controller with direct memory access (DMA); supports half or full duplex; operation is limited to 3.0 V to 3.6 V

# **MCF51CN128**

80 LQFP 14 mm × 14 mm

64 LQFP 10 mm × 10 mm

- MII—media independent interface to connect ethernet controller to external PHY; includes output clock for external PHY

- · External Bus

- Mini-FlexBus—Multi-function external bus interface; supports up to 1 MB memories, gate-array logic, simple slave device or glueless interfaces to standard chip-selected asynchronous memories

- Programmable options: access time per chip select, burst and burst-inhibited transfers per chip select, transfer direction, and address setup and hold times

- Power-Saving Modes

- Two low-power stop modes, one of which allows limited use of some peripherals (ADC, KBI, RTC)

- Reduced-power wait mode shuts off CPU and allows full use of all peripherals; FEC can remain active and conduct DMA transfers to RAM and assert an interrupt to wake up the CPU upon completion

- Low-power run and wait modes allow peripherals to run while the voltage regulator is in standby

- Peripheral clock enable register can disable clocks to unused modules, thereby reducing currents

- Low-power external oscillator that can be used in stop3 mode to provide accurate clock source to active peripherals

- Low-power real-time counter for use in run, wait, and stop modes with internal and external clock sources

- 6 μs typical wake-up time from stop3 mode

- Pins and clocks to peripherals not available in smaller packages are automatically disabled for reduced current consumption; no user interaction is needed

- Clock Source Options

- Oscillator (XOSC) Loop-control pierce oscillator; crystal or ceramic resonator range of 31.25 kHz to 38.4 kHz or 1 MHz to 25 MHz

- Multi-Purpose Clock Generator (MCG) Flexible clock source module with either frequency-locked-loop (FLL) or phase-lock loop (PLL) clock options. FLL can be controlled by internal or external reference and

Freescale reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

© Freescale Semiconductor, Inc., 2009. All rights reserved.

includes precision trimming of internal reference, allowing 0.2% resolution and 2% deviation over temperature and voltage. PLL derives a higher accuracy clock source derived by an external reference

## · System Protection

- Watchdog computer operating properly (COP) reset with option to run from dedicated 1-kHz internal clock source or bus clock

- Low-voltage detection with reset or interrupt; selectable trip points

- Illegal opcode and illegal address detection with programmable reset or exception response

- Flash block protection

## • Development Support

- Single-wire background debug module (BDM) interface; supports same electrical interface used by the S08, 9S12, and 9S12x families debug modules

- 4 PC plus 2 address (optional data) breakpoint registers with programmable 1- or 2-level trigger response

- 64-entry processor status and debug data trace buffer with programmable start/stop conditions

## Peripherals

- ADC—Up to 12 channel, 12-bit resolution; 2.5 μs conversion time; automatic compare function; 1.7 mV/°C temperature sensor; internal bandgap reference channel; operation in stop3; fully functional from 3.6 V to 1.8 V

- SCI—Three modules with optional 13-bit break

- SPI—Two interfaces with full-duplex or single-wire bi-directional; double-buffered transmit and receive; master or slave mode; MSB-first or LSB-first shifting

- IIC—Two IICs with up to 100 kbps with maxmimum bus loading; multi-master operation; programmable slave address; interrupt-driven byte-by-byte data transfer; supports broadcast mode and 11-bit addressing

- TPM—Two 3-channel, 16-bit resolution modules; selectable input capture, output compare, or buffered edge- or center-aligned PWM on each channel

- RTC—8-bit modulus counter with binary- or decimal-based prescaler; external clock source for precise time base, time-of-day, calendar- or task-scheduling functions; free-running on-chip low-power oscillator (1 kHz) for cyclic wake-up without external components; runs in all MCU modes

- MTIM—Two 8-bit resolution modulo timers with 8-bit prescaler

#### • Input/Output

- Up to 70 general-purpose input/output (GPIO) pins, all with pin mux controls to select alternate functions

- 16 keyboard interrupt (KBI) pins with selectable polarity

- Hysteresis and configurable pull-up device or input filtering on all input pins; configurable slew rate and drive strength on all output pins

- 16 Rapid GPIO pins connected to the CPU's high-speed local bus with set, clear, and toggle functionality (PTD and PTF)

Pin Assignments

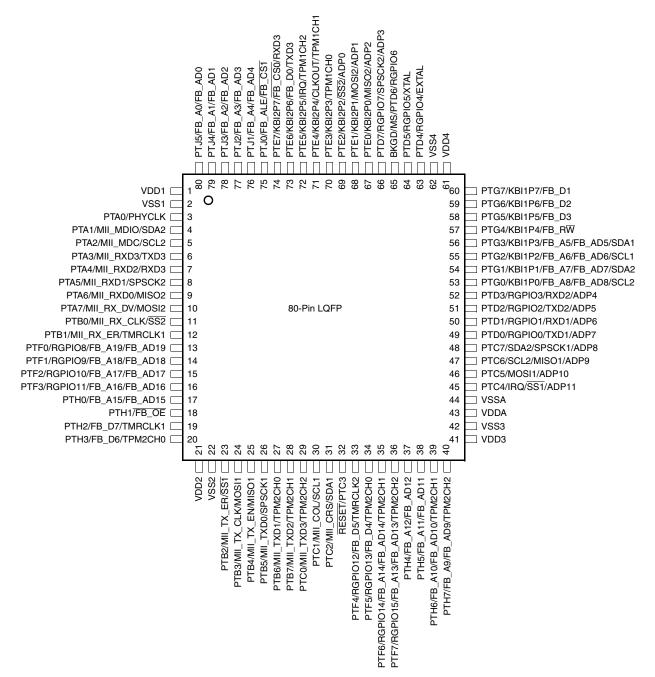

# 2 Pin Assignments

This section describes the pin assignments for the available packages. See for pin availability by package pin-count.

Figure 2. Pin Assignments in 80-Pin LQFP Package

## **Pin Assignments**

Figure 4. Pin Assignments in 48-Pin QFN Package

## **NOTE**

There is no electrical connection to the flag for 48-pin QFN packages.

**Table 2. Package Pin Assignments**

| 80-Pin | 64-Pin | 48-Pin | Default Function | Alt 1  | Alt 2 | Alt 3 | Comment |

|--------|--------|--------|------------------|--------|-------|-------|---------|

| 1      | 1      | 1      | VDD1             | _      | _     | _     | _       |

| 2      | 2      | 2      | VSS1             | _      | _     | _     | _       |

| 3      | 3      | 3      | PTA0             | PHYCLK | _     | _     | _       |

## MCF51CN128 ColdFire Microcontroller Data Sheet, Rev. 4

## 3.4 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and voltage regulator circuits, and it is user-determined rather than being controlled by the MCU design. To take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  will be very small.

|                                        | Rating                          | Symbol            | Value                                                                   | Unit |

|----------------------------------------|---------------------------------|-------------------|-------------------------------------------------------------------------|------|

| Operating temperature range (packaged) |                                 | T <sub>A</sub>    | T <sub>L</sub> to T <sub>H</sub><br>(-40 to 85 or 0 to 70) <sup>1</sup> | °C   |

| Maximu                                 | ım junction temperature         | $T_JM$            | 95                                                                      | °C   |

|                                        | ıl resistance<br>le-layer board |                   |                                                                         |      |

|                                        | 48-pin QFN                      |                   | 81                                                                      |      |

|                                        | 64-pin LQFP                     | $\theta_{\sf JA}$ | 69                                                                      | °C/W |

|                                        | 80-pin LQFP                     |                   | 60                                                                      |      |

|                                        | ll resistance<br>-layer board   |                   |                                                                         |      |

|                                        | 48-pin QFN                      |                   | 26                                                                      |      |

|                                        | 64-pin LQFP                     | $\theta_{\sf JA}$ | 50                                                                      | °C/W |

|                                        | 80-pin LQFP                     |                   | 47                                                                      |      |

**Table 5. Thermal Characteristics**

The average chip-junction temperature (T<sub>I</sub>) in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

Eqn. 1

where:

$T_A = Ambient temperature, °C$

$\theta_{JA}$  = Package thermal resistance, junction-to-ambient, °C/W

$$P_{D} = P_{int} + P_{I/O}$$

$P_{int} = I_{DD} \times V_{DD}$ , Watts — chip internal power

$P_{I/O}$  = Power dissipation on input and output pins — user determined

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_D = K \div (T_J + 273^{\circ}C)$$

Eqn. 2

Solving Equation 1 and Equation 2 for K gives:

$$K = P_D \times (T_A + 273^{\circ}C) + \theta_{JA} \times (P_D)^2$$

Eqn. 3

where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving Equation 1 and Equation 2 iteratively for any value of  $T_A$ .

## MCF51CN128 ColdFire Microcontroller Data Sheet, Rev. 4

Depending on device.

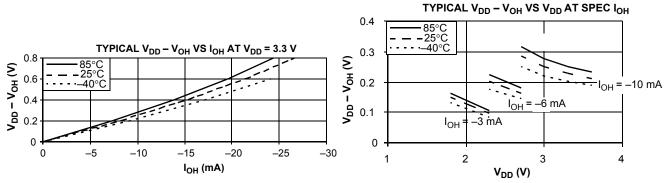

Figure 9. Typical High-Side (Source) Characteristics — High Drive (PTxDSn = 1)

# 3.7 Supply Current Characteristics

This section includes information about power supply current in various operating modes.

**Table 9. Supply Current Characteristics**

| Num | С | Parameter                                                            | Symbol            | Bus<br>Freq     | V <sub>DD</sub> (V)         | Typ <sup>1</sup> | Max  | Unit       | Temp<br>(°C) |             |

|-----|---|----------------------------------------------------------------------|-------------------|-----------------|-----------------------------|------------------|------|------------|--------------|-------------|

|     | Р | Run supply current                                                   |                   | 25 MHz          |                             | 60               | 75   |            |              |             |

| 1   | Т | FEI mode, all modules on                                             | DI                | 20 MHz          | 3.3                         | 49               | _    | mA         | –40 to 85 °C |             |

| '   | Т |                                                                      | טטייי י           | $RI_{DD}$       | 8 MHz                       | 3.3              | 21   |            | IIIA         | -40 to 65 C |

|     | Т |                                                                      |                   | 1 MHz           |                             | 4.6              | _    |            |              |             |

|     | С | Run supply current                                                   |                   | 25 MHz          | 3.3 44<br>36<br>15.5<br>3.9 | 47               |      |            |              |             |

| 2   | Т | FEI mode, all modules off                                            | Rlpp              | 20 MHz          |                             | 36               | _    | mA         | –40 to 85 °C |             |

|     | Т |                                                                      | ı ııDD            | 8 MHz           |                             | 15.5             | _    | 111/4      | -40 to 65 °C |             |

|     | Т |                                                                      |                   | 1 MHz           |                             | 3.9              | _    |            |              |             |

| 3   | Т | Run supply current<br>LPRS=0, all modules off                        | BI                | 16 kHz<br>FBILP | 3.3                         | 203              | _    | μΑ         | –40 to 85 °C |             |

|     | Т |                                                                      | RI <sub>DD</sub>  | 16 kHz<br>FBELP | 3.5                         | 154              | _    | μ.,        | -40 to 65 °C |             |

| 4   | Т | Run supply current<br>LPRS=1, all modules off, running from<br>Flash | RI <sub>DD</sub>  | 16 kHz<br>FBELP | 3.3                         | 50               | _    | μА         | –40 to 85 °C |             |

|     | С | Wait mode supply current                                             |                   | 25 MHz          |                             | 11               | 13.7 |            |              |             |

| 5   | Т | FEI mode, all modules off                                            | $WI_{DD}$         | 20 MHz          | 3.3                         | 4.57             |      | μΑ         | 40 to 85 °C  |             |

| 5   | Т |                                                                      | AAIDD             | 8 MHz           | 5.5                         | 2                | _    | μΑ         | 40 to 65 C   |             |

|     | Т |                                                                      |                   | 1 MHz           |                             | 0.73             | _    |            |              |             |

|     | С | Stop2 mode supply current                                            |                   | 3.3             | 0.35                        | 11               |      | 0 to 70 °C |              |             |

| 6   | Р |                                                                      | S2I <sub>DD</sub> | n/a             | 0.0                         | 0.00             | 45   | μΑ         | –40 to 85 °C |             |

|     | С |                                                                      | OZ'DD             | 11/4            | 1.8                         | 0.35             | 12   | μι         | 0 to 70 °C   |             |

|     | С |                                                                      |                   |                 | 1.0                         | 0.33             | 16.2 | 1          | –40 to 85 °C |             |

## MCF51CN128 ColdFire Microcontroller Data Sheet, Rev. 4

## 3.8 External Oscillator (XOSC) Characteristics

Reference Figure 11 and Figure 12 for crystal or resonator circuits.

Table 10. XOSC and ICS Specifications (Temperature Range = −40 to 85 °C Ambient)

| Num | С | Characteristic                                                                                                                                                                                                         | Symbol                                                | Min          | Typ <sup>1</sup>       | Max                    | Unit              |

|-----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------|------------------------|------------------------|-------------------|

| 1   | С | Oscillator crystal or resonator (EREFS = 1, ERCLKEN = 1) Low range (RANGE = 0) High range (RANGE = 1), high gain (HGO = 1) High range (RANGE = 1), low power (HGO = 0)                                                 | f <sub>lo</sub><br>f <sub>hi</sub><br>f <sub>hi</sub> | 32<br>1<br>1 | _<br>_<br>_            | 38.4<br>25<br>8        | kHz<br>MHz<br>MHz |

| 2   | D | Load capacitors Low range (RANGE=0), low power (HGO=0) Other oscillator settings                                                                                                                                       | nge (RANGE=0), low power (HGO=0) $C_{1,}C_{2}$        |              |                        |                        |                   |

| 3   | D | Feedback resistor Low range, low power (RANGE=0, HGO=0) <sup>2</sup> Low range, High Gain (RANGE=0, HGO=1) High range (RANGE=1, HGO=X)                                                                                 | R <sub>F</sub>                                        | _<br>_<br>_  | _<br>10<br>1           | _<br>_<br>_            | МΩ                |

| 4   | D | Series resistor — Low range, low power (RANGE = 0, HGO = 0) <sup>2</sup> Low range, high gain (RANGE = 0, HGO = 1) High range, low power (RANGE = 1, HGO = 0) High range, high gain (RANGE = 1, HGO = 1) ≥ 8 MHz 4 MHz | R <sub>S</sub>                                        |              | <br>0<br>100<br>0<br>0 | <br><br>0<br>10        | Ω                 |

| 5   | С | 1 MHz  Crystal start-up time <sup>4</sup> Low range, low power Low range, high power High range, low power High range, high power                                                                                      | t<br>CSTL<br>t<br>CSTH                                |              | 200<br>400<br>5<br>15  | 20<br>—<br>—<br>—<br>— | ms                |

| 6   | D | Square wave input clock frequency (EREFS = 0, ERCLKEN = 1) External with FLL / PLL enabled (FEE / PEE) External with bypass (FBE.FBELP,PBE, PBELP)                                                                     | f <sub>extal</sub>                                    | 0.03125      |                        | 50.33<br>50.33         | MHz<br>MHz        |

<sup>&</sup>lt;sup>1</sup> Data in Typical column was characterized at 3.3 V, 25 °C or is typical recommended value.

<sup>&</sup>lt;sup>2</sup> Load capacitors (C<sub>1</sub>,C<sub>2</sub>), feedback resistor (R<sub>F</sub>) and series resistor (R<sub>S</sub>) are incorporated internally when RANGE=HGO=0.

<sup>&</sup>lt;sup>3</sup> See crystal or resonator manufacturer's recommendation.

<sup>&</sup>lt;sup>4</sup> Proper PC board layout procedures must be followed to achieve specifications.

Table 11. MCG Frequency Specifications (continued)(Temperature Range = -40 to 125 °C Ambient)

| Num | С | Rating                                                                                                | Symbol                   | Min                      | Typical       | Max                                                           | Unit              |

|-----|---|-------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|---------------|---------------------------------------------------------------|-------------------|

| 8   | С | Resolution of trimmed DCO output frequency at fixed voltage and temperature (not using FTRIM)         | $\Delta f_{dco\_res\_t}$ | _                        | ± 0.2         | ± 0.4                                                         | %f <sub>dco</sub> |

| 9   | Р | Total deviation of trimmed DCO output frequency over voltage and temperature                          | $\Delta f_{dco\_t}$      | _                        | + 0.5<br>-1.0 | ± 2                                                           | %f <sub>dco</sub> |

| 10  | С | Total deviation of trimmed DCO output frequency over fixed voltage and temperature range of 0 - 70 °C | $\Delta f_{dco\_t}$      | _                        | ± 0.5         | ± 1                                                           | %f <sub>dco</sub> |

| 11  | С | FLL acquisition time <sup>2</sup>                                                                     | t <sub>fll_acquire</sub> | _                        | _             | 1                                                             | ms                |

| 12  | D | PLL acquisition time <sup>3</sup>                                                                     | t <sub>pll_acquire</sub> | _                        | _             | 1                                                             | ms                |

| 13  | С | Long term Jitter of DCO output clock (averaged over 2ms interval) <sup>4</sup>                        | C <sub>Jitter</sub>      | _                        | 0.02          | 0.2                                                           | %f <sub>dco</sub> |

| 14  | D | VCO operating frequency                                                                               | f <sub>vco</sub>         | 7.0                      | _             | 55.0                                                          | MHz               |

| 15  | D | Lock entry frequency tolerance <sup>5</sup>                                                           | D <sub>lock</sub>        | ± 1.49                   | _             | ± 2.98                                                        | %                 |

| 16  | D | Lock exit frequency tolerance <sup>6</sup>                                                            | D <sub>unl</sub>         | ± 4.47                   | _             | ± 5.97                                                        | %                 |

| 17  | D | Lock time - FLL                                                                                       | t <sub>fll_lock</sub>    | _                        | _             | t <sub>fll_acquire+</sub><br>1075(1/fint_t<br>)               | s                 |

| 18  | D | Lock time - PLL                                                                                       | <sup>t</sup> pll_lock    | _                        | _             | t <sub>pll_acquire+</sub><br>1075(1/f <sub>pll_r</sub><br>ef) | S                 |

| 19  | D | Loss of external clock minimum frequency - RANGE = 0                                                  | f <sub>loc_low</sub>     | (3/5) x f <sub>int</sub> | _             | _                                                             | kHz               |

<sup>&</sup>lt;sup>1</sup> TRIM register at default value (0x80) and FTRIM control bit at default value (0x0).

<sup>&</sup>lt;sup>2</sup> This specification applies to any time the FLL reference source or reference divider is changed, trim value changed or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>BUS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the FLL circuitry via V<sub>DD</sub> and V<sub>SS</sub> and variation in crystal oscillator frequency increase the C<sub>Jitter</sub> percentage for a given interval.

Below D<sub>lock</sub> minimum, the MCG is guaranteed to enter lock. Above D<sub>lock</sub> maximum, the MCG does not enter lock. But if the MCG is already in lock, then the MCG may stay in lock.

<sup>&</sup>lt;sup>6</sup> Below D<sub>IIII</sub> minimum, the MCG does not exit lock if already in lock. Above D<sub>IIII</sub> maximum, the MCG is guaranteed to exit lock.

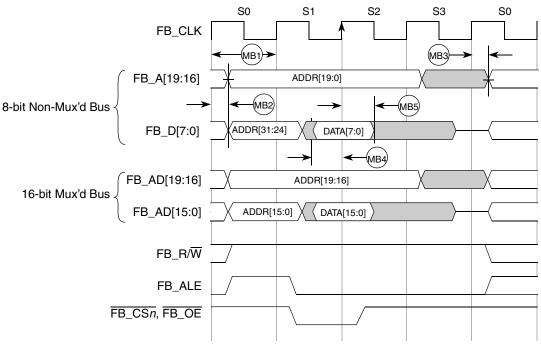

## 3.10 Mini-FlexBus Timing Specifications

A multi-function external bus interface called Mini-FlexBus is provided with basic functionality to interface to slave-only devices up to a maximum bus frequency of 25.1666 MHz. It can be directly connected to asynchronous or synchronous devices such as external boot ROMs, flash memories, gate-array logic, or other simple target (slave) devices with little or no additional circuitry. For asynchronous devices a simple chip-select based interface can be used.

All processor bus timings are synchronous; that is, input setup/hold and output delay are given in respect to the rising edge of a reference clock, MB CLK. The MB CLK frequency is half the internal system bus frequency.

The following timing numbers indicate when data is latched or driven onto the external bus, relative to the Mini-FlexBus output clock (MB\_CLK). All other timing relationships can be derived from these values.

| Num | С | Characteristic         | Min   | Max     | Unit | Notes |

|-----|---|------------------------|-------|---------|------|-------|

| _   | _ | Frequency of Operation | _     | 25.1666 | MHz  | _     |

| MB1 | D | Clock Period           | 39.73 | _       | ns   | _     |

| MB2 | Р | Output Valid           | _     | 20      | ns   | 1     |

| MB3 | D | Output Hold            | 1.0   | _       | ns   | 1     |

| MB4 | Р | Input Setup            | 22    | _       | ns   | 2     |

| MB5 | D | Input Hold             | 10    | _       | ns   | 2     |

**Table 12. Mini-FlexBus AC Timing Specifications**

<sup>&</sup>lt;sup>2</sup> Specification is valid for all MB\_D[7:0].

Figure 13. Mini-FlexBus Read Timing

<sup>&</sup>lt;sup>1</sup> Specification is valid for all MB\_A[19:0], MB\_D[7:0], MB\_CS[1:0], MB\_OE, MB\_R/W, and MB\_ALE.

# 3.12.3 SPI Timing

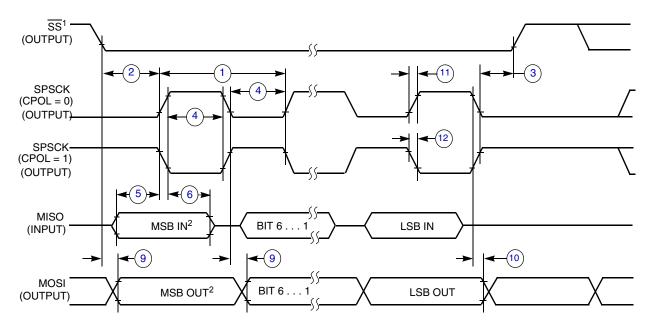

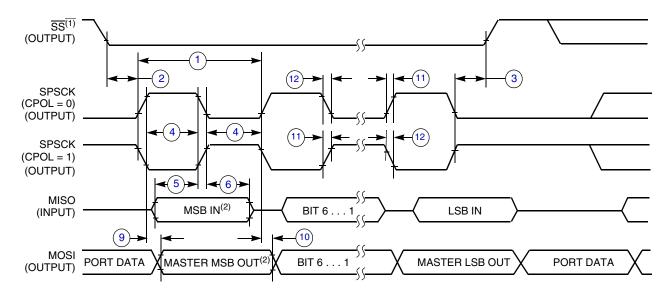

Table 19 and Figure 23 through Figure 26 describe the timing requirements for the SPI system.

## Table 19. SPI Timing

| No. | С | Function                                          | Symbol             | Min                                            | Max                                        | Unit                                 |

|-----|---|---------------------------------------------------|--------------------|------------------------------------------------|--------------------------------------------|--------------------------------------|

| _   | D | Operating frequency<br>Master<br>Slave            | f <sub>op</sub>    | f <sub>Bus</sub> /2048                         | f <sub>Bus</sub> /2<br>f <sub>Bus</sub> /4 | Hz<br>Hz                             |

| 1   | D | SPSCK period<br>Master<br>Slave                   | t <sub>SPSCK</sub> | 2<br>4                                         | 2048<br>—                                  | t <sub>cyc</sub><br>t <sub>cyc</sub> |

| 2   | D | Enable lead time<br>Master<br>Slave               | t <sub>Lead</sub>  | 1/2<br>1                                       |                                            | t <sub>SPSCK</sub>                   |

| 3   | D | Enable lag time<br>Master<br>Slave                | t <sub>Lag</sub>   | 1/2<br>1                                       |                                            | t <sub>SPSCK</sub>                   |

| 4   | D | Clock (SPSCK) high or low time<br>Master<br>Slave | twspsck            | t <sub>cyc</sub> - 30<br>t <sub>cyc</sub> - 30 | 1024 t <sub>cyc</sub>                      | ns<br>ns                             |

| 5   | D | Data setup time (inputs)<br>Master<br>Slave       | t <sub>SU</sub>    | 15<br>15                                       |                                            | ns<br>ns                             |

| 6   | D | Data hold time (inputs) Master Slave              | t <sub>HI</sub>    | 0<br>25                                        |                                            | ns<br>ns                             |

| 7   | D | Slave access time                                 | t <sub>a</sub>     | _                                              | 1                                          | t <sub>cyc</sub>                     |

| 8   | D | Slave MISO disable time                           | t <sub>dis</sub>   | _                                              | 1                                          | t <sub>cyc</sub>                     |

| 9   | D | Data valid (after SPSCK edge)<br>Master<br>Slave  | t <sub>v</sub>     | _                                              | 25<br>25                                   | ns<br>ns                             |

| 10  | D | Data hold time (outputs) Master Slave             | t <sub>HO</sub>    | 0<br>0                                         |                                            | ns<br>ns                             |

| 11  | D | Rise time<br>Input<br>Output                      | t <sub>RI</sub>    | _                                              | t <sub>cyc</sub> – 25<br>25                | ns<br>ns                             |

| 12  | D | Fall time<br>Input<br>Output                      | t <sub>FI</sub>    | _                                              | t <sub>cyc</sub> – 25<br>25                | ns<br>ns                             |

## NOTES:

- 1.  $\overline{SS}$  output mode (DDS7 = 1, SSOE = 1).

- 2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

Figure 23. SPI Master Timing (CPHA = 0)

## NOTES:

- 1.  $\overline{SS}$  output mode (DDS7 = 1, SSOE = 1).

- 2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

Figure 24. SPI Master Timing (CPHA =1)

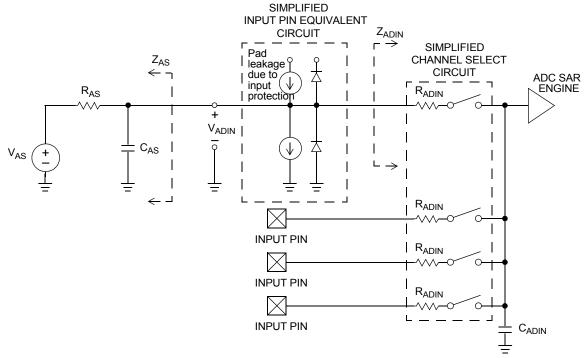

Figure 27. ADC Input Impedance Equivalency Diagram

Table 21. 12-bit ADC Characteristics ( $V_{REFH} = V_{DDAD}$ ,  $V_{REFL} = V_{SSAD}$ )

| Characteristic                                  | Conditions              | С | Symb               | Min  | Typ <sup>1</sup> | Max | Unit  | Comment                   |

|-------------------------------------------------|-------------------------|---|--------------------|------|------------------|-----|-------|---------------------------|

| Supply Current<br>ADLPC=1<br>ADLSMP=1<br>ADCO=1 |                         | Т | I <sub>DDAD</sub>  | _    | 120              | _   | μА    |                           |

| Supply Current<br>ADLPC=1<br>ADLSMP=0<br>ADCO=1 |                         | Т | I <sub>DDAD</sub>  | _    | 202              | _   | μА    |                           |

| Supply Current<br>ADLPC=0<br>ADLSMP=1<br>ADCO=1 |                         | Т | I <sub>DDAD</sub>  | _    | 288              | _   | μА    |                           |

| Supply Current<br>ADLPC=0<br>ADLSMP=0<br>ADCO=1 |                         | Т | I <sub>DDAD</sub>  | _    | 0.532            | 1   | mA    |                           |

| Supply Current                                  | Stop, Reset, Module Off | D | I <sub>DDAD</sub>  | _    | 0.007            | 0.8 | μΑ    |                           |

| ADC                                             | High Speed (ADLPC=0)    | Р | f <sub>ADACK</sub> | 2    | 3.3              | 5   | M1.1- | $t_{ADACK} = 1/f_{ADACK}$ |

| Asynchronous<br>Clock Source                    | Low Power (ADLPC=1)     | С |                    | 1.25 | 2                | 3.3 | MHz   |                           |

Table 21. 12-bit ADC Characteristics ( $V_{REFH} = V_{DDAD}$ ,  $V_{REFL} = V_{SSAD}$ ) (continued)

| Characteristic          | Conditions               | С | Symb                | Min | Typ <sup>1</sup> | Max  | Unit             | Comment                                |  |

|-------------------------|--------------------------|---|---------------------|-----|------------------|------|------------------|----------------------------------------|--|

|                         | Short Sample (ADLSMP=0)  | Р | t <sub>ADC</sub>    | _   | 20               | _    | ADCK             | See the ADC                            |  |

| (Including sample time) | Long Sample (ADLSMP=1)   | С |                     | _   | 40               | _    | cycles           | chapter in the MCF51CN128              |  |

| Sample Time             | Short Sample (ADLSMP=0)  | Р | t <sub>ADS</sub>    | _   | 3.5              | _    | ADCK             | Reference Manual for conversion time   |  |

|                         | Long Sample (ADLSMP=1)   | С |                     | _   | 23.5             | _    | cycles           | variances                              |  |

| Total Unadjusted        | 12 bit mode              | Т | E <sub>TUE</sub>    | _   | ±3.0             | _    | LSB <sup>2</sup> | Includes                               |  |

| Error                   | 10 bit mode              | Р |                     | _   | ±1               | ±2.5 |                  | Quantization                           |  |

|                         | 8 bit mode               | Т |                     | _   | ±0.5             | ±1.0 |                  |                                        |  |

| Differential            | 12 bit mode              | Т | DNL                 | _   | ±1.75            | _    | LSB <sup>2</sup> |                                        |  |

| Non-Linearity           | 10 bit mode <sup>3</sup> | Р |                     | _   | ±0.5             | ±1.0 |                  |                                        |  |

|                         | 8 bit mode <sup>3</sup>  | Т |                     | _   | ±0.3             | ±0.5 |                  |                                        |  |

| Integral                | 12 bit mode              | Т | INL                 | _   | ±1.5             | _    | LSB <sup>2</sup> |                                        |  |

| Non-Linearity           | 10 bit mode              | Р |                     | _   | ±0.5             | ±1.0 |                  |                                        |  |

|                         | 8 bit mode               | Т |                     | _   | ±0.3             | ±0.5 |                  |                                        |  |

| Zero-Scale Error        | 12 bit mode              | Т | E <sub>ZS</sub>     | _   | ±1.5             | _    | LSB <sup>2</sup> | $V_{ADIN} = V_{SSAD}$                  |  |

|                         | 10 bit mode              | Р |                     | _   | ±0.5             | ±1.5 | ]                |                                        |  |

|                         | 8 bit mode               | Т |                     | _   | ±0.5             | ±0.5 |                  |                                        |  |

| Full-Scale Error        | 12 bit mode              | Т | E <sub>FS</sub>     | _   | ±1.0             | _    | LSB <sup>2</sup> | $V_{ADIN} = V_{DDAD}$                  |  |

|                         | 10 bit mode              | Р |                     | _   | ±0.5             | ±1   |                  |                                        |  |

|                         | 8 bit mode               | Т |                     | _   | ±0.5             | ±0.5 |                  |                                        |  |

| Quantization            | 12 bit mode              | D | EQ                  | _   | -1 to 0          | _    | LSB <sup>2</sup> |                                        |  |

| Error                   | 10 bit mode              |   |                     | _   | _                | ±0.5 |                  |                                        |  |

|                         | 8 bit mode               |   |                     | _   | _                | ±0.5 |                  |                                        |  |

| Input Leakage           | 12 bit mode              | D | E <sub>IL</sub>     | _   | ±2               | _    | LSB <sup>2</sup> | Pad leakage <sup>4</sup> *             |  |

| Error                   | 10 bit mode              |   |                     | _   | ±0.2             | ±4   |                  | R <sub>AS{test=pad leakage</sub> test} |  |

|                         | 8 bit mode               |   |                     | _   | ±0.1             | ±1.2 | -                | testy                                  |  |

| Temp Sensor             | -40°C to 25°C            | D | m                   | _   | 1.646            | _    | mV/°C            |                                        |  |

| Slope                   | 25°C to 85°C             |   |                     | _   | 1.769            | _    |                  |                                        |  |

| Temp Sensor<br>Voltage  | 25°C                     | D | V <sub>TEMP25</sub> | _   | 701.2            | _    | mV               |                                        |  |

Typical values assume V<sub>DDAD</sub> = 3.3 V, Temp = 25 °C, f<sub>ADCK</sub>=1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

## MCF51CN128 ColdFire Microcontroller Data Sheet, Rev. 4

<sup>&</sup>lt;sup>2</sup> 1 LSB =  $(V_{REFH} - V_{REFL})/2^{N}$

<sup>&</sup>lt;sup>3</sup> Monotonicity and No-Missing-Codes guaranteed in 10 bit and 8 bit modes

<sup>&</sup>lt;sup>4</sup> Based on input pad leakage current. Refer to pad electricals.

#### **Ordering Information**

## 3.13.1 Radiated Emissions

Microcontroller radiated RF emissions are measured from 150 kHz to 1 GHz using the TEM/GTEM Cell method in accordance with the IEC 61967-2 and SAE J1752/3 standards. The measurement is performed with the microcontroller installed on a custom EMC evaluation board while running specialized EMC test software. The radiated emissions from the microcontroller are measured in a TEM cell in two package orientations (North and East). For more detailed information concerning the evaluation results, conditions and setup, please refer to the EMC Evaluation Report for this device.

# 4 Ordering Information

This section contains ordering information for MCF51CN128 devices.

**Table 23. Ordering Information**

| Freescale Part Number <sup>1</sup> | Men   | nory | Temperature Range | Package <sup>2</sup> |

|------------------------------------|-------|------|-------------------|----------------------|

| Freescale Fait Number              | Flash | RAM  | (°C)              | rackage              |

| MCF51CN128CLK                      | 128K  | 24K  | -40 to +85        | 80-pin LQFP          |

| MCF51CN128CLH                      | 128K  | 24K  | -40 to +85        | 64-pin LQFP          |

| MCF51CN128CGT                      | 128K  | 24K  | -40 to +85        | 48-pin QFN           |

See the MCF51CN128 Reference Manual (document MCF51CN128RM), for a complete description of modules included on each device.

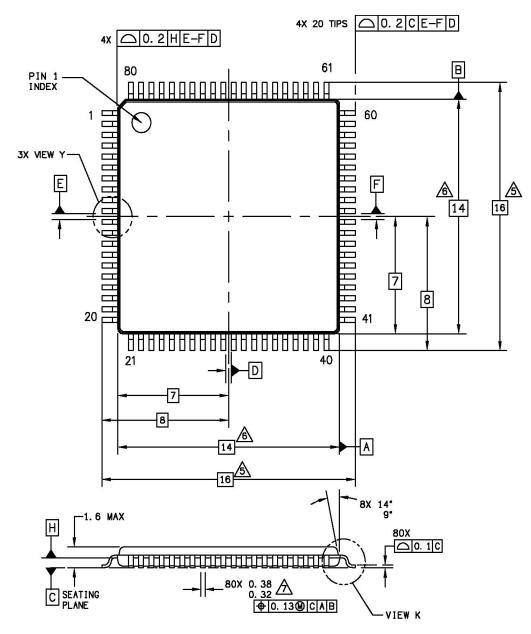

# 5 Package Information

**Table 24. Package Descriptions**

| Pin Count | Package Type          | Abbreviation | Designator | Case No. | Document No. |

|-----------|-----------------------|--------------|------------|----------|--------------|

| 80        | Low Quad Flat Package | LQFP         | LK         | 917A     | 98ASS23237W  |

| 64        | Low Quad Flat Package | LQFP         | LH         | 840F     | 98ASS23234W  |

| 48        | Quad Flat No-Leads    | QFN          | GT         | 1314     | 98ARH99048A  |

# 6 Mechanical Outline Drawings

The following pages are mechanical drawings for the packages described in Table 24. For the latest available drawings, visit freescale web site (http://www.freescale.com) and enter the package's document number into the keyword search box.

<sup>&</sup>lt;sup>2</sup> See Table 24 for package information.

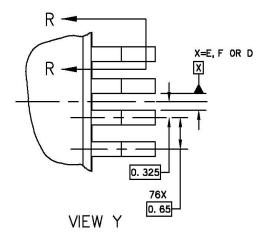

# 6.1 80-pin LQFP

| © FREESCALE SEMICONDUCTOR, INC.  ALL RIGHTS RESERVED.  MECHANIC | AL OUTLINE           | PRINT VERSION NOT TO SCALE |             |

|-----------------------------------------------------------------|----------------------|----------------------------|-------------|

| TITLE:                                                          | DOCUMENT NO          | ): 98ASS23237W             | REV: E      |

| 80 LD LQFP, 14 X 14 PKG,                                        | CASE NUMBER: 917A-03 |                            | 28 APR 2006 |

| 0.65 MM PITCH, 1.4 THICK                                        | STANDARD: NO         | N-JEDEC                    |             |

## **Mechanical Outline Drawings**

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | AL OUTLINE           | PRINT VERSION NOT TO SCALE |             |

|------------------------------------------------------|----------------------|----------------------------|-------------|

| TITLE:                                               | DOCUMENT NO          | ): 98ASS23237W             | REV: E      |

| 80 LD LQFP, 14 X 14 PKG,<br>0.65 MM PITCH, 1.4 THICK | CASE NUMBER: 917A-03 |                            | 28 APR 2006 |

| U. 65 MM PITCH, I. 4 THICK                           | STANDARD: NO         | N-JEDEC                    |             |

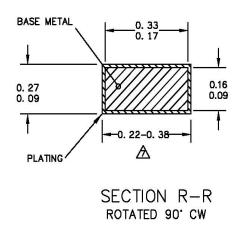

FREESCALE SEMICONDUCTOR, INC.

MECHANICAL OUTLINE

PRINT VERSION NOT TO SCALE

DOCUMENT NO: 98ASS23234W

REV: E

10 X 10 X 1. 4 PKG,

O. 5 PITCH, CASE OUTLINE

STANDARD: JEDEC MS-026 BCD

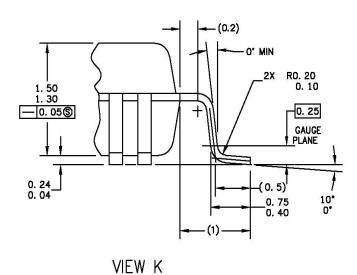

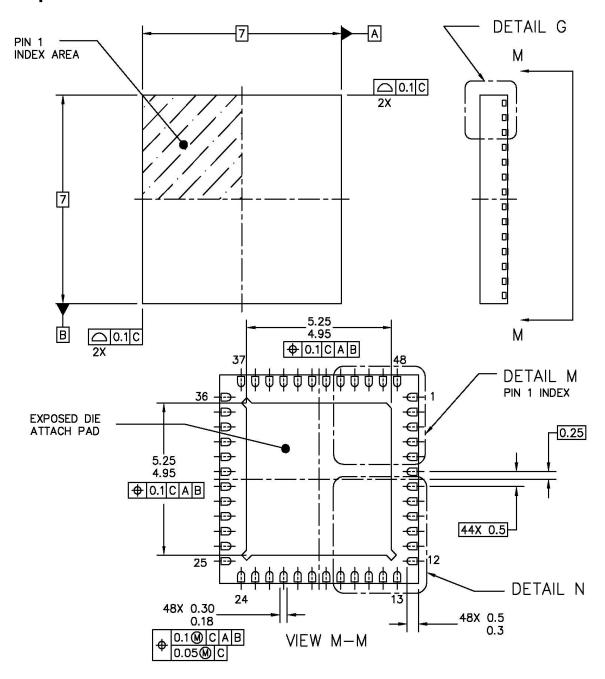

# 6.3 48-pin QFN

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.  MECHANICA |                          | L OUTLINE                     | PRINT VERSION NO | T TO SCALE |

|-----------------------------------------------------------------|--------------------------|-------------------------------|------------------|------------|

| TITLE: THERMALLY ENHANCED QUA                                   | DOCUMENT NO: 98ARH99048A |                               | REV: F           |            |

| FLAT NON-LEADED PACKAGE                                         | CASE NUMBER              | : 1314–05                     | 05 DEC 2005      |            |

| 48 TERMINAL, 0.5 PITCH (7 X 7 X 1)                              |                          | STANDARD: JEDEC-MO-220 VKKD-2 |                  |            |

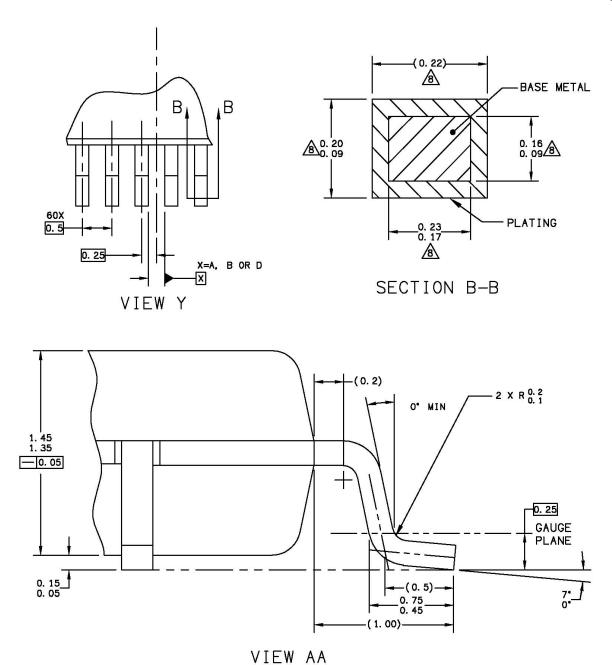

## **Mechanical Outline Drawings**

## NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- 3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HF-PQFN.

4. COPLANARITY APPLIES TO LEADS, CORNER LEADS, AND DIE ATTACH PAD.

5. MIN METAL GAP SHOULD BE 0.2MM.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. |                               | L OUTLINE | PRINT VERSION NO | T TO SCALE |

|------------------------------------------------------|-------------------------------|-----------|------------------|------------|

| TITLE: THERMALLY ENHANCED                            | DOCUMENT NO: 98ARH99048A      |           | REV: F           |            |

| FLAT NON-LEADED PACK                                 | CASE NUMBER: 1314-05          |           | 05 DEC 2005      |            |

| 48 TERMINAL, 0.5 PITCH (7                            | STANDARD: JEDEC-MO-220 VKKD-2 |           |                  |            |