Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2221-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 6.0 MEMORY ORGANIZATION

There are three types of memory in PIC18 Enhanced microcontroller devices:

- Program Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device, since it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Flash program memory is provided in Section 7.0 "Flash Program Memory". Data EEPROM is discussed separately in Section 8.0 "Data EEPROM Memory".

#### 6.1 Program Memory Organization

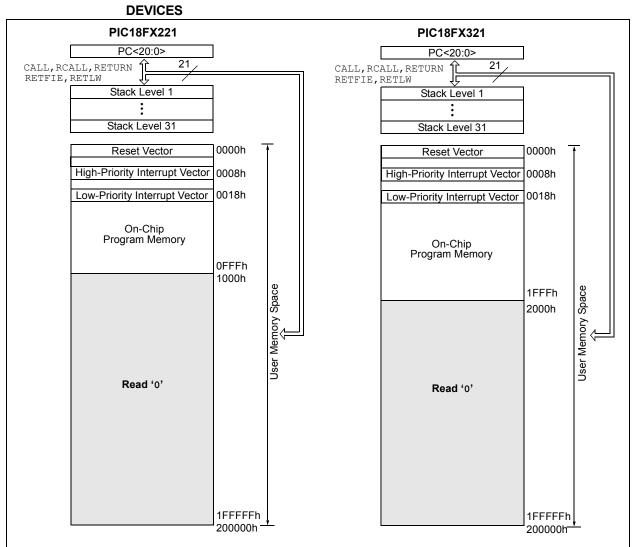

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

The PIC18F2221 and PIC18F4221 each have 4 Kbytes of Flash memory and can store up to 2048 single-word instructions. The PIC18F2321 and PIC18F4321 each have 8 Kbytes of Flash memory and can store up to 4096 single-word instructions.

PIC18 devices have two interrupt vectors. The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

The program memory maps for PIC18F2221/4221 and PIC18F2321/4321 devices are shown in Figure 6-1.

FIGURE 6-1: PROGRAM MEMORY MAP AND STACK FOR PIC18F2221/2321/4221/4321 FAMILY

#### 11.4 PORTD, TRISD and LATD Registers

| Note: | PORTD    | is | only | available | on | 40/44-pin |

|-------|----------|----|------|-----------|----|-----------|

|       | devices. |    |      |           |    |           |

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

Three of the PORTD pins are multiplexed with outputs P1B, P1C and P1D of the Enhanced CCP module. The operation of these additional PWM output pins is covered in greater detail in Section 17.0 "Enhanced Capture/Compare/PWM (ECCP) Module".

Note: On a Power-on Reset, these pins are configured as digital inputs. PORTD can also be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit, PSPMODE (TRISE<4>). In this mode, the input buffers are TTL. See **Section 11.6 "Parallel Slave Port"** for additional information on the Parallel Slave Port (PSP).

| Note: | When the Enhanced PWM mode is used        |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|

|       | with either dual or quad outputs, the PSP |  |  |  |  |  |  |  |  |

|       | functions of PORTD are automatically      |  |  |  |  |  |  |  |  |

|       | disabled.                                 |  |  |  |  |  |  |  |  |

#### EXAMPLE 11-4: INITIALIZING PORTD

| CLRF  | PORTD | ; Initialize PORTD by<br>; clearing output<br>: data latches |

|-------|-------|--------------------------------------------------------------|

| CLRF  | LATD  | ; Alternate method                                           |

|       |       | ; to clear output                                            |

|       |       | ; data latches                                               |

| MOVLW | OCFh  | ; Value used to                                              |

|       |       | ; initialize data                                            |

|       |       | ; direction                                                  |

| MOVWF | TRISD | ; Set RD<3:0> as inputs                                      |

|       |       | ; RD<5:4> as outputs                                         |

|       |       | ; RD<7:6> as inputs                                          |

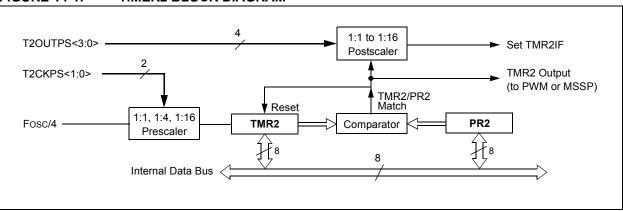

#### 14.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2 to PR2 match) provides the input for the 4-bit output counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF (PIR1<1>). The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE (PIE1<1>).

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0> (T2CON<6:3>).

#### 14.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 18.0 "Master Synchronous Serial Port (MSSP) Module".

### FIGURE 14-1: TIMER2 BLOCK DIAGRAM

#### TABLE 14-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name   | Bit 7                  | Bit 6     | Bit 5    | Bit 4         | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on page |

|--------|------------------------|-----------|----------|---------------|----------|--------|---------|---------|----------------------------|

| INTCON | GIE/GIEH               | PEIE/GIEL | TMR0IE   | <b>INTOIE</b> | RBIE     | TMR0IF | INT0IF  | RBIF    | 55                         |

| PIR1   | PSPIF <sup>(1)</sup>   | ADIF      | RCIF     | TXIF          | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 58                         |

| PIE1   | PSPIE <sup>(1)</sup>   | ADIE      | RCIE     | TXIE          | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 58                         |

| IPR1   | PSPIP <sup>(1)</sup>   | ADIP      | RCIP     | TXIP          | SSPIP    | CCP1IP | TMR2IP  | TMR1IP  | 58                         |

| TMR2   | Timer2 Register        |           |          |               |          |        |         |         |                            |

| T2CON  |                        | T2OUTPS3  | T2OUTPS2 | T2OUTPS1      | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 56                         |

| PR2    | Timer2 Period Register |           |          |               |          |        |         |         |                            |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

### 15.0 TIMER3 MODULE

The Timer3 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR3H and TMR3L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Module Reset on CCP Special Event Trigger

#### A simplified block diagram of the Timer3 module is shown in Figure 15-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 15-2.

The Timer3 module is controlled through the T3CON register (Register 15-1). It also selects the clock source options for the CCP modules (see **Section 16.1.1** "**CCP Modules and Timer Resources**" for more information).

#### REGISTER 15-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|--------|---------|---------|--------|--------|--------|--------|

| RD16  | T3CCP2 | T3CKPS1 | T3CKPS0 | T3CCP1 | T3SYNC | TMR3CS | TMR3ON |

| bit 7 |        |         |         |        |        |        | bit 0  |

- bit 7 RD16: 16-Bit Read/Write Mode Enable bit

- 1 = Enables register read/write of Timer3 in one 16-bit operation

- 0 = Enables register read/write of Timer3 in two 8-bit operations

- bit 6,3 T3CCP<2:1>: Timer3 and Timer1 to CCPx Enable bits

- 1x = Timer3 is the capture/compare clock source for the CCP modules

- 01 = Timer3 is the capture/compare clock source for CCP2; Timer1 is the capture/compare clock source for CCP1

- 00 = Timer1 is the capture/compare clock source for the CCP modules

- bit 5-4 T3CKPS<1:0>: Timer3 Input Clock Prescale Select bits

- 11 = 1:8 Prescale value

- 10 = 1:4 Prescale value

- 01 = 1:2 Prescale value

- 00 = 1:1 Prescale value

- bit 2 **T3SYNC:** Timer3 External Clock Input Synchronization Control bit (Not usable if the device clock comes from Timer1/Timer3.)

- $M_{\text{box}} = 1$

- When TMR3CS = 1:

- 1 = Do not synchronize external clock input

- 0 = Synchronize external clock input

- When TMR3CS = 0:

- This bit is ignored. Timer3 uses the internal clock when TMR3CS = 0.

- bit 1 TMR3CS: Timer3 Clock Source Select bit

- 1 = External clock input from Timer1 oscillator or T13CKI (on the rising edge after the first falling edge)

- 0 = Internal clock (Fosc/4)

- bit 0 **TMR3ON:** Timer3 On bit

- 1 = Enables Timer3

- 0 = Stops Timer3

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The CCPRxH register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the CCPRxH and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCPx pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

#### EQUATION 16-3:

PWM Resolution (max) =

$$\frac{\log(\frac{FOSC}{FPWM})}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the CCPx pin will not be cleared.

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8          | 7          | 6.58       |

#### 16.4.3 PWM AUTO-SHUTDOWN (CCP1 ONLY)

The PWM auto-shutdown features of the Enhanced CCP module are also available to CCP1 in 28-pin devices. The operation of this feature is discussed in detail in **Section 17.4.7 "Enhanced PWM Auto-Shutdown"**.

Auto-shutdown features are not available for CCP2.

#### 16.4.4 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPRxL register and CCPxCON<5:4> bits.

- 3. Make the CCPx pin an output by clearing the appropriate TRIS bit.

- 4. Set the TMR2 prescale value, then enable Timer2 by writing to T2CON.

- 5. Configure the CCPx module for PWM operation.

# PIC18F2221/2321/4221/4321 FAMILY

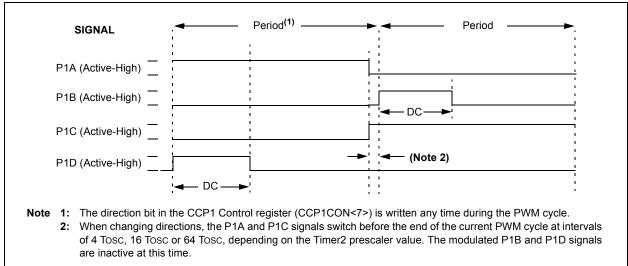

#### FIGURE 17-8: PWM DIRECTION CHANGE

|         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0          | R/W-0       | R/W-0        | =_,<br>R/W-0  | R/W-0         | R/W-0       |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|--------------|---------------|---------------|-------------|--|--|

|         | WCOL                                                                                                                                                                                                                                                                                                                                                                                                                      | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                               | SSPEN          | CKP         | SSPM3        | SSPM2         | SSPM1         | SSPM0       |  |  |

|         | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |             | I            | I             | 1             | bit 0       |  |  |

| bit 7   | 1 = The S                                                                                                                                                                                                                                                                                                                                                                                                                 | rite Collision<br>SPBUF regis<br>be cleared in<br>lision                                                                                                                                                                                                                                                                                                                                                                            | ter is written |             | • ·          | ng the previ  | ous word      |             |  |  |

| bit 6   | SPI Slave<br>1 = A new<br>of ove<br>must r<br>cleare                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>SSPOV: Receive Overflow Indicator bit</li> <li><u>SPI Slave mode:</u></li> <li>1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. The user must read the SSPBUF, even if only transmitting data, to avoid setting overflow (must be cleared in software).</li> <li>0 = No overflow</li> </ul> |                |             |              |               |               |             |  |  |

|         | Note:                                                                                                                                                                                                                                                                                                                                                                                                                     | In Master<br>transmissio                                                                                                                                                                                                                                                                                                                                                                                                            |                |             |              |               |               | eption (and |  |  |

| bit 5   | 1 = Enable                                                                                                                                                                                                                                                                                                                                                                                                                | ynchronous s<br>es serial port<br>es serial port                                                                                                                                                                                                                                                                                                                                                                                    | and configu    | res SCK, SE |              |               | al port pins  |             |  |  |

|         | Note:                                                                                                                                                                                                                                                                                                                                                                                                                     | When enab                                                                                                                                                                                                                                                                                                                                                                                                                           | led, these p   | ins must be | properly cor | nfigured as i | nput or outp  | out.        |  |  |

| bit 4   | 1 = Idle sta                                                                                                                                                                                                                                                                                                                                                                                                              | k Polarity Se<br>ate for clock i<br>ate for clock i                                                                                                                                                                                                                                                                                                                                                                                 | s a high leve  |             |              |               |               |             |  |  |

| bit 3-0 | SSPM<3:0>: Synchronous Serial Port Mode Select bits<br>0101 = SPI Slave mode, clock = SCK pin, <u>SS</u> pin control disabled, <u>SS</u> can be used as I/O pin<br>0100 = SPI Slave mode, clock = SCK pin, <u>SS</u> pin control enabled<br>0011 = SPI Master mode, clock = TMR2 output/2<br>0010 = SPI Master mode, clock = Fosc/64<br>0001 = SPI Master mode, clock = Fosc/16<br>0000 = SPI Master mode, clock = Fosc/4 |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |             |              |               |               |             |  |  |

|         | Note:                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |             |              |               |               |             |  |  |

|         | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |             |              |               |               |             |  |  |

|         | R = Reada                                                                                                                                                                                                                                                                                                                                                                                                                 | able bit                                                                                                                                                                                                                                                                                                                                                                                                                            | W = Writab     | le bit      | U = Unimp    | lemented bi   | t, read as '0 | ,           |  |  |

'1' = Bit is set

-n = Value at POR

#### REGISTER 18-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE)

'0' = Bit is cleared

x = Bit is unknown

|   |       |         |        |        | •      | ,      |        |       |

|---|-------|---------|--------|--------|--------|--------|--------|-------|

|   | R/W-0 | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 |

| ſ | GCEN  | ACKSTAT |        |        |        |        |        |       |

|   |       |         | ADMSK5 | ADMSK4 | ADMSK3 | ADMSK2 | ADMSK1 |       |

| _ | bit 7 |         |        |        |        |        |        | bit 0 |

#### REGISTER 18-5: SSPCON2: MSSP CONTROL REGISTER 2 (I<sup>2</sup>C<sup>™</sup> MODE) – CONTINUED

bit 0 SEN: Start Condition Enable/Stretch Enable bit<sup>(1)</sup>

In Master mode:

1 = Initiate Start condition on SDA and SCL pins. Automatically cleared by hardware.

0 = Start condition Idle

#### In Slave mode:

1 = Clock stretching is enabled for both slave transmit and slave receive (stretch enabled)

0 = Clock stretching is disabled

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is active, these bits may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### REGISTER 18-6: SSPADD: MSSP ADDRESS REGISTER<sup>(1)</sup>

|   | R/W-0 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

| ſ | ADD7  | ADD6  | ADD5  | ADD4  | ADD3  | ADD2  | ADD1  | ADD0  |

|   | bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7-0 ADD<7:0>: MSSP Address bits

**Note 1:** MSSP Address register in I<sup>2</sup>C Slave mode. MSSP Baud Rate register in I<sup>2</sup>C Master mode.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 18.4.3.2 Address Masking

Masking an address bit causes that bit to become a "don't care". When one address bit is masked, two addresses will be Acknowledged and cause an interrupt. It is possible to mask more than one address bit at a time, which makes it possible to Acknowledge up to 31 addresses in 7-Bit Addressing mode and up to 63 addresses in 10-Bit Addressing mode (see Example 18-2).

The  $l^2C$  slave behaves the same way whether address masking is used or not. However, when address masking is used, the  $l^2C$  slave can Acknowledge multiple addresses and cause interrupts. When this occurs, it is necessary to determine which address caused the interrupt by checking the SSPBUF register.

• 7-Bit Addressing mode

Address mask bits, ADMSK<5:1>, mask the corresponding address bits in the SSPADD register. For any ADMSK bits that are active (ADMSK<n> = 1), the corresponding address bit is ignored (ADD<n> = x). For the module to issue an address Acknowledge, it is sufficient to match only on addresses that do not have an active address mask.

#### • 10-Bit Addressing mode

Address mask bits, ADMSK<5:2>, mask the corresponding address bits in the SSPADD register. In addition, ADMSK<1> simultaneously masks the two LSBs of the address, ADD<1:0>. For any ADMSK bits that are active (ADMSK<n> = 1), the corresponding address bit is ignored (ADD<n> = x). Also note that although in 10-Bit Addressing mode, the upper address bits reuse part of the SSPADD register bits, the address mask bits do not interact with those bits. They only affect the lower address bits.

Note 1: ADMSK<1> masks the two Least Significant bits of the address.

2: The two Most Significant bits of the address are not affected by address masking.

#### EXAMPLE 18-2: ADDRESS MASKING

#### 7-Bit Addressing mode:

SSPADD<7:1> = 1010 0000

ADMSK<5:1> = 00 111

Addresses Acknowledged = 0xA0, 0xA2, 0xA4, 0xA6, 0xA8, 0xAA, 0xAC, 0xAE

#### 10-Bit Addressing mode:

SSPADD<7:0> = 1010 0000 (The two MSbs are ignored in this example since they are not affected)

ADMSK<5:1> = 00 111

Addresses Acknowledged = 0xA0, 0xA1, 0xA2, 0xA3, 0xA4, 0xA5, 0xA6, 0xA7, 0xA8, 0xA9, 0xAA, 0xAB, 0xAC, 0xAD, 0xAE, 0xAF

The upper two bits are not affected by the address masking.

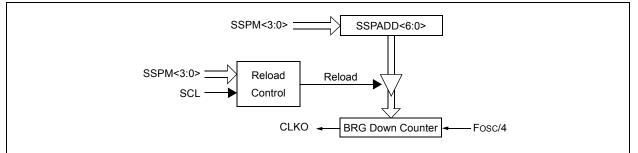

#### 18.4.7 BAUD RATE

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the lower 7 bits of the SSPADD register (Figure 18-19). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TcY) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state.

Table 18-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD.

#### FIGURE 18-19: BAUD RATE GENERATOR BLOCK DIAGRAM

#### TABLE 18-3: I<sup>2</sup>C<sup>™</sup> CLOCK RATE W/BRG

| Fosc   | Fcy    | Fcy * 2 | BRG Value | FscL<br>(2 Rollovers of BRG) |

|--------|--------|---------|-----------|------------------------------|

| 40 MHz | 10 MHz | 20 MHz  | 18h       | 400 kHz                      |

| 40 MHz | 10 MHz | 20 MHz  | 1Fh       | 312.5 kHz                    |

| 40 MHz | 10 MHz | 20 MHz  | 63h       | 100 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 09h       | 400 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 0Ch       | 308 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 27h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 02h       | 333 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 09h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 00h       | 1 MHz                        |

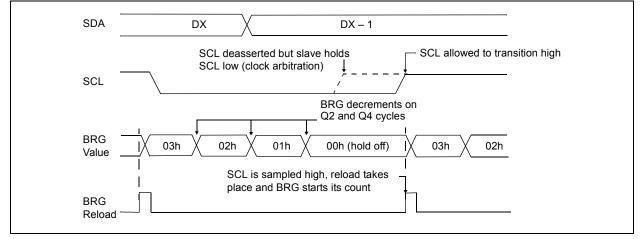

#### 18.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 18-20).

# PIC18F2221/2321/4221/4321 FAMILY

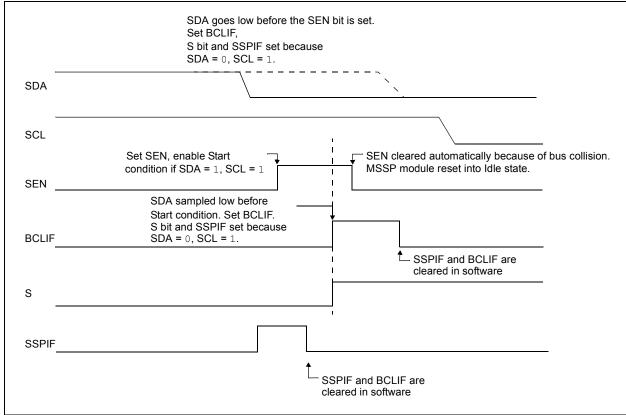

## 18.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 18-28).

- b) SCL is sampled low before SDA is asserted low (Figure 18-29).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 18-28).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 18-30). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 18-28: BUS COLLISION DURING START CONDITION (SDA ONLY)

|             |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |                   |                             |                       |                  |                             |                       |            |                             |  |  |

|-------------|-----------------------|-------------------------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|------------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|

| BAUD        | Fosc = 40.000 MHz     |                               | Fosc = 20.000 MHz           |                       | Fosc = 10.000 MHz |                             |                       | Fosc = 8.000 MHz |                             |                       |            |                             |  |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 0.3         | _                     |                               |                             |                       |                   |                             | _                     |                  | _                           |                       |            |                             |  |  |

| 1.2         | —                     | —                             | —                           | 1.221                 | 1.73              | 255                         | 1.202                 | 0.16             | 129                         | 1.201                 | -0.16      | 103                         |  |  |

| 2.4         | 2.441                 | 1.73                          | 255                         | 2.404                 | 0.16              | 129                         | 2.404                 | 0.16             | 64                          | 2.403                 | -0.16      | 51                          |  |  |

| 9.6         | 9.615                 | 0.16                          | 64                          | 9.766                 | 1.73              | 31                          | 9.766                 | 1.73             | 15                          | 9.615                 | -0.16      | 12                          |  |  |

| 19.2        | 19.531                | 1.73                          | 31                          | 19.531                | 1.73              | 15                          | 19.531                | 1.73             | 7                           | _                     | _          | _                           |  |  |

| 57.6        | 56.818                | -1.36                         | 10                          | 62.500                | 8.51              | 4                           | 52.083                | -9.58            | 2                           | _                     | _          | _                           |  |  |

| 115.2       | 125.000               | 8.51                          | 4                           | 104.167               | -9.58             | 2                           | 78.125                | -32.18           | 1                           | _                     | _          | _                           |  |  |

#### TABLE 19-3: BAUD RATES FOR ASYNCHRONOUS MODES

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |                  |                             |                       |                  |                             |  |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------------|-----------------------------|-----------------------|------------------|-----------------------------|--|--|--|

| BAUD<br>RATE | Fosc = 4.000 MHz      |                               |                             | Fos                   | Fosc = 2.000 MHz |                             |                       | Fosc = 1.000 MHz |                             |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3          | 0.300                 | 0.16                          | 207                         | 0.300                 | -0.16            | 103                         | 0.300                 | -0.16            | 51                          |  |  |  |

| 1.2          | 1.202                 | 0.16                          | 51                          | 1.201                 | -0.16            | 25                          | 1.201                 | -0.16            | 12                          |  |  |  |

| 2.4          | 2.404                 | 0.16                          | 25                          | 2.403                 | -0.16            | 12                          | _                     | _                | _                           |  |  |  |

| 9.6          | 8.929                 | -6.99                         | 6                           | —                     | _                | _                           | _                     | _                | _                           |  |  |  |

| 19.2         | 20.833                | 8.51                          | 2                           | —                     | _                | _                           | _                     | _                | _                           |  |  |  |

| 57.6         | 62.500                | 8.51                          | 0                           | —                     | _                | _                           | —                     | _                | _                           |  |  |  |

| 115.2        | 62.500                | -45.75                        | 0                           | _                     | —                | —                           | _                     | _                |                             |  |  |  |

|             |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |                       |            |                             |  |  |

|-------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|

| BAUD        | Fosc = 40.000 MHz     |                               |                             | Fosc = 20.000 MHz     |            | Fosc = 10.000 MHz           |                       |            | Fosc = 8.000 MHz            |                       |            |                             |  |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 0.3         | _                     |                               | _                           | —                     | _          | _                           |                       |            | _                           |                       | _          | _                           |  |  |

| 1.2         | —                     | _                             | _                           | —                     | _          | _                           | —                     | _          | _                           | —                     | _          | —                           |  |  |

| 2.4         | —                     | _                             | _                           | —                     | _          | _                           | 2.441                 | 1.73       | 255                         | 2.403                 | -0.16      | 207                         |  |  |

| 9.6         | 9.766                 | 1.73                          | 255                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |  |  |

| 19.2        | 19.231                | 0.16                          | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |  |  |

| 57.6        | 58.140                | 0.94                          | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |  |  |

| 115.2       | 113.636               | -1.36                         | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | —                     | _          | _                           |  |  |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |  |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|

| BAUD<br>RATE | Foso                  | = 4.000                       | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3          | _                     |                               | _                           |                       |            | _                           | 0.300                 | -0.16      | 207                         |  |  |  |

| 1.2          | 1.202                 | 0.16                          | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |  |  |

| 2.4          | 2.404                 | 0.16                          | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |  |  |

| 9.6          | 9.615                 | 0.16                          | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | _                           |  |  |  |

| 19.2         | 19.231                | 0.16                          | 12                          | _                     | _          | _                           | _                     | _          | _                           |  |  |  |

| 57.6         | 62.500                | 8.51                          | 3                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |

| 115.2        | 125.000               | 8.51                          | 1                           |                       | _          | —                           | _                     | _          | _                           |  |  |  |

© 2009 Microchip Technology Inc.

# PIC18F2221/2321/4221/4321 FAMILY

NOTES:

# PIC18F2221/2321/4221/4321 FAMILY

| ADDWF                                                          |                                                                                                   | ADD W to Indexed<br>(Indexed Literal Offset mode)                          |                                      |                        |  |  |  |  |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------|------------------------|--|--|--|--|

| Syntax:                                                        | ADDWF                                                                                             | [k] {,d}                                                                   |                                      |                        |  |  |  |  |

| Operands:                                                      | $\begin{array}{l} 0 \leq k \leq 95 \\ d  \in  [0,1] \end{array}$                                  |                                                                            |                                      |                        |  |  |  |  |

| Operation:                                                     | (W) + ((FSF                                                                                       | R2) + k) →                                                                 | dest                                 |                        |  |  |  |  |

| Status Affected:                                               | N, OV, C, D                                                                                       | N, OV, C, DC, Z                                                            |                                      |                        |  |  |  |  |

| Encoding:                                                      | 0010                                                                                              | 01d0                                                                       | kkkk                                 | kkkk                   |  |  |  |  |

| Description:                                                   | The content<br>contents of<br>FSR2, offse<br>If 'd' is '0', t<br>is '1', the re<br>register 'f' ( | the registent<br>the the value of the value of the the the tesult is store | er indica<br>alue 'k'.<br>s stored i | ted by<br>in W. If 'd' |  |  |  |  |

| Words:                                                         | 1                                                                                                 |                                                                            |                                      |                        |  |  |  |  |

| Cycles:                                                        | 1                                                                                                 |                                                                            |                                      |                        |  |  |  |  |

| Q Cycle Activity:                                              |                                                                                                   |                                                                            |                                      |                        |  |  |  |  |

| Q1                                                             | Q2                                                                                                | Q3                                                                         |                                      | Q4                     |  |  |  |  |

| Decode                                                         | Read 'k'                                                                                          | Proces<br>Data                                                             | -                                    | Write to<br>stination  |  |  |  |  |

| Example:                                                       | ADDWF                                                                                             | [OFST],                                                                    | 0                                    |                        |  |  |  |  |

| Before Instructi                                               | on                                                                                                |                                                                            |                                      |                        |  |  |  |  |

| W<br>OFST<br>FSR2<br>Contents<br>of 0A2Ch<br>After Instructior | =<br>=<br>=<br>1                                                                                  | 17h<br>2Ch<br>0A00h<br>20h                                                 |                                      |                        |  |  |  |  |

| W<br>Contents<br>of 0A2Ch                                      | =                                                                                                 | 37h<br>20h                                                                 |                                      |                        |  |  |  |  |

| BSF   |                                                            | =                                                                  | Bit Set Indexed<br>(Indexed Literal Offset mode)                   |                                                     |      |     |                       |  |  |

|-------|------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------|------|-----|-----------------------|--|--|

| Synta | ax:                                                        | BSF [k],                                                           | b                                                                  |                                                     |      |     |                       |  |  |

| Oper  | ands:                                                      | $\begin{array}{l} 0 \leq f \leq 95 \\ 0 \leq b \leq 7 \end{array}$ | $\begin{array}{l} 0 \leq f \leq 95 \\ 0 \leq b \leq 7 \end{array}$ |                                                     |      |     |                       |  |  |

| Oper  | ation:                                                     | $1 \rightarrow$ ((FS                                               | R2)                                                                | + k) <b< td=""><td>&gt;</td><td></td><td></td></b<> | >    |     |                       |  |  |

| Statu | s Affected:                                                | None                                                               |                                                                    |                                                     |      |     |                       |  |  |

| Enco  | ding:                                                      | 1000                                                               | b                                                                  | bb0                                                 | kk}  | ck  | kkkk                  |  |  |

| Desc  | ription:                                                   | Bit 'b' of th<br>offset by                                         |                                                                    | •                                                   |      |     | by FSR2,              |  |  |

| Word  | ls:                                                        | 1                                                                  |                                                                    |                                                     |      |     |                       |  |  |

| Cycle | es:                                                        | 1                                                                  |                                                                    |                                                     |      |     |                       |  |  |

| QC    | ycle Activity:                                             |                                                                    |                                                                    |                                                     |      |     |                       |  |  |

|       | Q1                                                         | Q2                                                                 |                                                                    | Q3                                                  |      | Q4  |                       |  |  |

|       | Decode                                                     | Read<br>register 'f'                                               |                                                                    | Proce<br>Data                                       |      |     | Vrite to<br>stination |  |  |

| Exam  | <u>nple:</u>                                               | BSF                                                                | [F]                                                                | LAG_O                                               | FST] | , 7 |                       |  |  |

|       | Before Instruct<br>FLAG_OI<br>FSR2<br>Contents<br>of 0A0Ah | =ST =<br>=                                                         | =<br>=                                                             | 0Ah<br>0A00h<br>55h                                 | 1    |     |                       |  |  |

|       | After Instructio<br>Contents<br>of 0A0Ah                   |                                                                    | =                                                                  | D5h                                                 |      |     |                       |  |  |

| SETF              |                    | Set Indexed<br>(Indexed Literal Offset mode)                                   |      |                  |  |  |  |  |  |

|-------------------|--------------------|--------------------------------------------------------------------------------|------|------------------|--|--|--|--|--|

| Syntax:           | SETF [k]           |                                                                                |      |                  |  |  |  |  |  |

| Operands:         | $0 \leq k \leq 95$ | $0 \leq k \leq 95$                                                             |      |                  |  |  |  |  |  |

| Operation:        | $FFh \to ((FS))$   | SR2) + k)                                                                      | 1    |                  |  |  |  |  |  |

| Status Affected:  | None               | None                                                                           |      |                  |  |  |  |  |  |

| Encoding:         | 0110               | 1000                                                                           | kkkk | kkkk             |  |  |  |  |  |

| Description:      |                    | The contents of the register indicated by FSR2, offset by 'k', are set to FFh. |      |                  |  |  |  |  |  |

| Words:            | 1                  | 1                                                                              |      |                  |  |  |  |  |  |

| Cycles:           | 1                  | 1                                                                              |      |                  |  |  |  |  |  |

| Q Cycle Activity: |                    |                                                                                |      |                  |  |  |  |  |  |

| Q1                | Q2                 | Q3                                                                             | 1    | Q4               |  |  |  |  |  |

| Decode            | Read 'k'           | Proce<br>Dat                                                                   |      | Write<br>egister |  |  |  |  |  |

|                   |                    |                                                                                |      |                  |  |  |  |  |  |

| Example:          | SETF               | [OFST]                                                                         |      |                  |  |  |  |  |  |

| Before Instruc    | Before Instruction |                                                                                |      |                  |  |  |  |  |  |

| = | 2Ch         |

|---|-------------|

| = | 0A00h       |

| = | 00h         |

|   |             |

| = | FFh         |

|   | =<br>=<br>= |

### 27.0 ELECTRICAL CHARACTERISTICS

### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                               | 40°C to +125°C       |

|--------------------------------------------------------------|----------------------|

| Storage temperature                                          | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD and MCLR) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                           | -0.3V to +7.5V       |

| Voltage on MCLR with respect to Vss (Note 2)                 | 0V to +13.25V        |

| Total power dissipation (Note 1)                             | 1.0W                 |

| Maximum current out of Vss pin                               |                      |

| Maximum current into VDD pin                                 | 250 mA               |

| Input clamp current, Iικ (Vι < 0 or Vι > VDD)                | ±20 mA               |

| Output clamp current, loк (Vo < 0 or Vo > VDD)               | ±20 mA               |

| Maximum output current sunk by any I/O pin                   | 25 mA                |

| Maximum output current sourced by any I/O pin                | 25 mA                |

| Maximum current sunk by all ports                            | 200 mA               |

| Maximum current sourced by all ports                         | 200 mA               |

- **Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD  $- \sum$  IOH} +  $\sum$  {(VDD - VOH) x IOH} +  $\sum$ (VOL x IOL)

- **2:** Voltage spikes below Vss at the MCLR/VPP/RE3 pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP/ RE3 pin, rather than pulling this pin directly to Vss.

**† NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

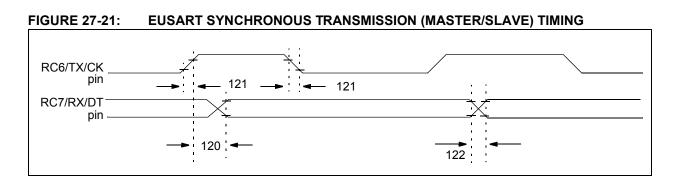

#### TABLE 27-22: EUSART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Symbol                           | Characteristic                                             |                      | Min | Мах | Units | Conditions |

|--------------|----------------------------------|------------------------------------------------------------|----------------------|-----|-----|-------|------------|

| 120          | TckH2dtV                         | SYNC XMIT (MASTER & SLAVE)<br>Clock High to Data Out Valid | PIC18 <b>F</b> XXXX  |     | 40  | ns    |            |

|              |                                  |                                                            | PIC18LFXXXX          |     | 100 | ns    | VDD = 2.0V |

|              | lock Out Rise Time and Fall Time | PIC18FXXXX                                                 |                      | 20  | ns  |       |            |

|              |                                  | (Master mode)                                              | PIC18 <b>LF</b> XXXX | _   | 50  | ns    | VDD = 2.0V |

| 122          | Tdtrf                            | Data Out Rise Time and Fall Time                           | PIC18FXXXX           | —   | 20  | ns    |            |

|              |                                  |                                                            | PIC18 <b>LF</b> XXXX | _   | 50  | ns    | VDD = 2.0V |

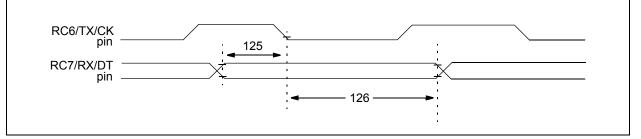

#### FIGURE 27-22: EUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 27-23: EUSART SYNCHRONOUS RECEIVE REQUIREMENTS

| Param.<br>No. | Symbol   | Characteristic                                                               | Min | Max | Units | Conditions |

|---------------|----------|------------------------------------------------------------------------------|-----|-----|-------|------------|

| 125           | TdtV2ckl | SYNC RCV (MASTER & SLAVE)<br>Data Hold before CK $\downarrow$ (DT hold time) | 10  |     | ns    |            |

| 126           | TckL2dtl | Data Hold after CK $\downarrow$ (DT hold time)                               | 15  |     | ns    |            |

|              |               | A/D CONVERTER CHARAC                              |                           |     | i          |          | i                                                           |

|--------------|---------------|---------------------------------------------------|---------------------------|-----|------------|----------|-------------------------------------------------------------|

| Param<br>No. | Symbol        | Characteristic                                    | Min                       | Тур | Мах        | Units    | Conditions                                                  |

| A01          | NR            | Resolution                                        | —                         |     | 10         | bit      | $\Delta \text{VREF} \geq 3.0 \text{V}$                      |

| A03          | EIL           | Integral Linearity Error                          | —                         | _   | <±1        | LSb      | $\Delta VREF \ge 3.0V$                                      |

| A04          | Edl           | Differential Linearity Error                      | —                         | _   | <±1        | LSb      | $\Delta VREF \ge 3.0V$                                      |

| A06          | EOFF          | Offset Error                                      | —                         | —   | <±2        | LSb      | $\Delta VREF \ge 3.0V$                                      |

| A07          | Egn           | Gain Error                                        | —                         | _   | <±1        | LSb      | $\Delta VREF \ge 3.0V$                                      |

| A10          | —             | Monotonicity                                      | Guaranteed <sup>(1)</sup> |     |            | _        | $VSS \leq VAIN \leq VREF$                                   |

| A20          | $\Delta VREF$ | Reference Voltage Range<br>(VREFH – VREFL)        | 1.8<br>3                  | _   |            | V<br>V   | $\begin{array}{l} VDD < 3.0V \\ VDD \geq 3.0V \end{array}$  |

| A21          | VREFH         | Reference Voltage High                            | —                         | _   | VDD + 3.0V | V        |                                                             |

| A22          | VREFL         | Reference Voltage Low                             | Vss – 0.3V                | _   |            | V        |                                                             |

| A25          | VAIN          | Analog Input Voltage                              | VREFL                     | _   | VREFH      | V        |                                                             |

| A30          | ZAIN          | Recommended Impedance of<br>Analog Voltage Source | —                         |     | 2.5        | kΩ       |                                                             |

| A50          | IREF          | VREF Input Current <sup>(2)</sup>                 |                           |     | 5<br>150   | μΑ<br>μΑ | During VAIN acquisition.<br>During A/D conversion<br>cycle. |

#### TABLE 27-24: A/D CONVERTER CHARACTERISTICS

Note 1: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

2: VREFH current is from RA3/AN3/VREF+ pin or VDD, whichever is selected as the VREFH source. VREFL current is from RA2/AN2/VREF-/CVREF pin or VSS, whichever is selected as the VREFL source.

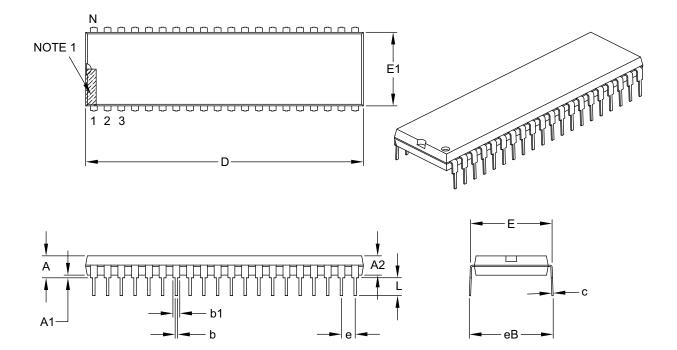

#### 40-Lead Plastic Dual In-Line (P) – 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       | INCHES   |       |

|----------------------------|------------------|-------|----------|-------|

|                            | Dimension Limits | MIN   | NOM      | MAX   |

| Number of Pins             | N                | 40    |          |       |

| Pitch                      | е                |       | .100 BSC |       |

| Top to Seating Plane       | А                | -     | -        | .250  |

| Molded Package Thickness   | A2               | .125  | -        | .195  |

| Base to Seating Plane      | A1               | .015  | -        | -     |

| Shoulder to Shoulder Width | E                | .590  | -        | .625  |

| Molded Package Width       | E1               | .485  | -        | .580  |

| Overall Length             | D                | 1.980 | -        | 2.095 |

| Tip to Seating Plane       | L                | .115  | -        | .200  |

| Lead Thickness             | С                | .008  | -        | .015  |

| Upper Lead Width           | b1               | .030  | -        | .070  |

| Lower Lead Width           | b                | .014  | -        | .023  |

| Overall Row Spacing §      | eB               | _     | -        | .700  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M. BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B

| Example Frequencies/Resolutions        | 151      |

|----------------------------------------|----------|

| Operation Setup                        | 151      |

| Period                                 | 150      |

| TMR2 to PR2 Match                      | 150, 155 |

| PWM (ECCP Module)                      | 155      |

| CCPR1H:CCPR1L Registers                |          |

| Duty Cycle                             | 156      |

| Effects of a Reset                     |          |

| Enhanced PWM Auto-Shutdown             |          |

| Example Frequencies/Resolutions        | 156      |

| Full-Bridge Application Example        |          |

| Full-Bridge Mode                       |          |

| Direction Change                       |          |

| Half-Bridge Mode                       |          |

| Half-Bridge Output Mode Applications   |          |

| Example                                |          |

| Operation in Power-Managed Modes       |          |

| Operation with Fail-Safe Clock Monitor |          |

| Output Configurations                  | 156      |

| Output Relationships (Active-High)     |          |

| Output Relationships (Active-Low)      |          |

| Period                                 | 155      |

| Programmable Dead-Band Delay           |          |

| Setup for PWM Operation                |          |

| Start-up Considerations                |          |

| Q                                      |          |

| Q Clock                                | 151. 156 |

|                                        |          |

### R

| ĸ                                     |       |

|---------------------------------------|-------|

| RAM. See Data Memory.                 |       |

| RC Oscillator                         |       |

| RCIO Oscillator Mode                  | 31    |

| RC_IDLE Mode                          |       |

| RC_RUN Mode                           | 41    |

| RCALL                                 | 309   |

| RCON Register                         |       |

| Bit Status During Initialization      | 54    |

| Reader Response                       | 400   |

| Register File                         | 67    |

| Register File Summary                 | 69–71 |

| Registers                             |       |

| ADCON0 (A/D Control 0)                | 233   |

| ADCON1 (A/D Control 1)                | 234   |

| ADCON2 (A/D Control 2)                | 235   |

| BAUDCON (Baud Rate Control)           | 214   |

| CCP1CON (Enhanced Capture/Compare/PWM |       |

| Control 1)                            | 153   |

| CCPxCON (CCPx Control)                | 145   |

| CMCON (Comparator Control)            |       |

| CONFIG1H (Configuration 1 High)       |       |

| CONFIG2H (Configuration 2 High)       |       |

| CONFIG2L (Configuration 2 Low)        |       |

| CONFIG3H (Configuration 3 High)       | 263   |

| CONFIG4L (Configuration 4 Low)        | 264   |

| CONFIG5H (Configuration 5 High)       | 265   |

| CONFIG5L (Configuration 5 Low)        | 265   |

| CONFIG6H (Configuration 6 High)       |       |

| CONFIG6L (Configuration 6 Low)        | 266   |

| CONFIG7H (Configuration 7 High)       | 267   |

| CONFIG7L (Configuration 7 Low)        | 267   |

| CVRCON (Comparator Voltage            |       |

| Reference Control)                    | 249   |

| DEVID1 (Device ID 1)                  | 268   |

| DEVID2 (Device ID 2)                  | 268   |

| ECCP1AS (ECCP Auto-Shutdown Control)  | 163   |

|                                       |       |

| ECCP1DEL (PWM Dead-Band Delay) 162                  |        |

|-----------------------------------------------------|--------|

| EECON1 (Data EEPROM Control 1) 81, 90               | С      |

| HLVDCON (High/Low-Voltage Detect Control) 253       | 3      |

| INTCON (Interrupt Control)                          | 9      |

| INTCON2 (Interrupt Control 2) 100                   | 0      |

| INTCON3 (Interrupt Control 3) 10                    |        |

| IPR1 (Peripheral Interrupt Priority 1) 106          |        |

| IPR2 (Peripheral Interrupt Priority 2)              |        |

| OSCCON (Oscillator Control)                         |        |

|                                                     |        |

| OSCTUNE (Oscillator Tuning)                         |        |

| PIE1 (Peripheral Interrupt Enable 1) 104            |        |

| PIE2 (Peripheral Interrupt Enable 2)                |        |

| PIR1 (Peripheral Interrupt Request (Flag) 1) 102    |        |

| PIR2 (Peripheral Interrupt Request (Flag) 2) 103    |        |

| RCON (Reset Control) 48, 108                        | 3      |

| RCSTA (Receive Status and Control) 213              | 3      |

| SSPADD(MSSP Address) 180                            | C      |

| SSPCON1 (MSSP Control 1, I <sup>2</sup> C Mode) 178 | 8      |

| SSPCON1 (MSSP Control 1, SPI Mode) 169              | 9      |

| SSPCON2 (MSSP Control 2, I <sup>2</sup> C Mode)     | à      |

| SSPSTAT (MSSP Status, I <sup>2</sup> C Mode)        |        |

| SSPSTAT (MSSP Status, TC Mode)                      | r<br>D |

|                                                     |        |