Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

|                            |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2221-e-ss |

#### 1.2 Other Special Features

- Memory Endurance: The Enhanced Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles – up to 100,000 for program memory and 1,000,000 for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

- Self-Programmability: These devices can write to their own program memory spaces under internal software control. By using a bootloader routine, located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

- Extended Instruction Set: The PIC18F2221/ 2321/4221/4321 family introduces an optional extension to the PIC18 instruction set, which adds 8 new instructions and an Indexed Addressing mode. This extension, enabled as a device configuration option, has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

- Enhanced CCP Module: In PWM mode, this

module provides 1, 2 or 4 modulated outputs for

controlling half-bridge and full-bridge drivers.

Other features include auto-shutdown, for

disabling PWM outputs on interrupt or other select

conditions and auto-restart, to reactivate outputs

once the condition has cleared.

- Enhanced Addressable USART: This serial communication module is capable of standard RS-232 operation and provides support for the LIN/J2602 bus protocol. Other enhancements include automatic baud rate detection and a 16-bit Baud Rate Generator for improved resolution. When the microcontroller is using the internal oscillator block, the EUSART provides stable operation for applications that talk to the outside world without using an external crystal (or its accompanying power requirement).

- 10-Bit A/D Converter: This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reducing code overhead.

- Extended Watchdog Timer (WDT): This

Enhanced version incorporates a 16-bit prescaler,

allowing an extended time-out range that is stable

across operating voltage and temperature. See

Section 27.0 "Electrical Characteristics" for

time-out periods.

### 1.3 Details on Individual Family Members

Devices in the PIC18F2221/2321/4221/4321 family are available in 28-pin and 40/44-pin packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2.

The devices are differentiated from each other in five ways:

- Flash program memory (4 Kbytes for PIC18F2221/4221 devices, 8 Kbytes for PIC18F2321/4321).

- 2. A/D channels (10 for 28-pin devices, 13 for 40/44-pin devices).

- 3. I/O ports (3 bidirectional ports on 28-pin devices, 5 bidirectional ports on 40/44-pin devices).

- 4. CCP and Enhanced CCP implementation (28-pin devices have 2 standard CCP modules, 40/44-pin devices have one standard CCP module and one ECCP module).

- Parallel Slave Port (present only on 40/44-pin devices).

All other features for devices in this family are identical. These are summarized in Table 1-1.

The pinouts for all devices are listed in Table 1-2 and Table 1-3.

Like all Microchip PIC18 devices, members of the PIC18F2221/2321/4221/4321 family are available as both standard and low-voltage devices. Standard devices with Enhanced Flash memory, designated with an "F" in the part number (such as PIC18F2321), accommodate an operating VDD range of 4.2V to 5.5V. Low-voltage parts, designated by "LF" (such as PIC18LF2321), function over an extended VDD range of 2.0V to 5.5V.

### 3.0 OSCILLATOR CONFIGURATIONS

### 3.1 Oscillator Types

The PIC18F2221/2321/4221/4321 family of devices can be operated in ten different oscillator modes. The user can program the Configuration bits, FOSC<3:0>, in Configuration Register 1H to select one of these ten modes:

| 1.  | LP     | Low-Power Crystal                                            |

|-----|--------|--------------------------------------------------------------|

| 2.  | XT     | Crystal/Resonator                                            |

| 3.  | HS     | High-Speed Crystal/Resonator                                 |

| 4.  | HSPLL  | High-Speed Crystal/Resonator with PLL enabled                |

| 5.  | RC     | External Resistor/Capacitor with Fosc/4 output on RA6        |

| 6.  | RCIO   | External Resistor/Capacitor with I/O on RA6                  |

| 7.  | INTIO1 | Internal Oscillator with Fosc/4 output on RA6 and I/O on RA7 |

| 8.  | INTIO2 | Internal Oscillator with I/O on RA6 and RA7                  |

| 9.  | EC     | External Clock with Fosc/4 output                            |

| 10. | ECIO   | External Clock with I/O on RA6                               |

### 3.2 Crystal Oscillator/Ceramic Resonators

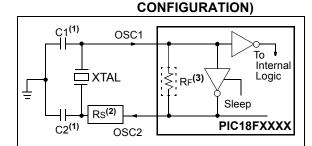

In XT, LP, HS or HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 3-1 shows the pin connections.

The oscillator design requires the use of a parallel cut crystal.

**Note:** Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications.

# FIGURE 3-1: CRYSTAL/CERAMIC RESONATOR OPERATION (XT, LP, HS OR HSPLL

Note 1: See Table 3-1 and Table 3-2 for initial values of C1 and C2.

- 2: A series resistor (Rs) may be required for AT strip cut crystals.

- 3: RF varies with the oscillator mode chosen.

### TABLE 3-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| Typical Capacitor Values Used: |          |       |       |  |  |

|--------------------------------|----------|-------|-------|--|--|

| Mode Freq OSC1 OSC2            |          |       |       |  |  |

| XT                             | 3.58 MHz | 22 pF | 22 pF |  |  |

#### Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application. Refer to the following application notes for oscillator specific information:

- AN588, "PIC® Microcontroller Oscillator Design Guide"

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC® and PIC® Devices"

- AN849, "Basic PIC® Oscillator Design"

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

See the notes following Table 3-2 for additional information.

Note: When using resonators with frequencies above 3.5 MHz, the use of HS mode, rather than XT mode, is recommended. HS mode may be used at any VDD for which the controller is rated. If HS is selected, it is possible that the gain of the oscillator will overdrive the resonator. Therefore, a series resistor may be placed between the OSC2 pin and the resonator. As a good starting point, the recommended value of Rs is  $330\Omega$ .

#### 6.0 MEMORY ORGANIZATION

There are three types of memory in PIC18 Enhanced microcontroller devices:

- Program Memory

- · Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device, since it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Flash program memory is provided in **Section 7.0 "Flash Program Memory"**. Data EEPROM is discussed separately in **Section 8.0 "Data EEPROM Memory"**.

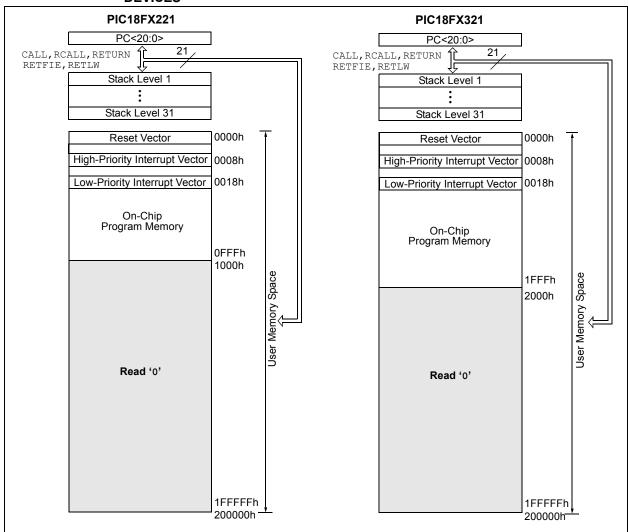

#### 6.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

The PIC18F2221 and PIC18F4221 each have 4 Kbytes of Flash memory and can store up to 2048 single-word instructions. The PIC18F2321 and PIC18F4321 each have 8 Kbytes of Flash memory and can store up to 4096 single-word instructions.

PIC18 devices have two interrupt vectors. The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

The program memory maps for PIC18F2221/4221 and PIC18F2321/4321 devices are shown in Figure 6-1.

FIGURE 6-1: PROGRAM MEMORY MAP AND STACK FOR PIC18F2221/2321/4221/4321 FAMILY DEVICES

#### 6.4 Data Addressing Modes

Note:

The execution of some instructions in the core PIC18 instruction set are changed when the PIC18 extended instruction set is enabled. See Section 6.5 "Data Memory and the Extended Instruction Set" for more information.

The data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- · Inherent

- Literal

- Direct

- · Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 6.5.1 "Indexed Addressing with Literal Offset"**.

### 6.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 6.4.2 DIRECT ADDRESSING

Direct addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byteoriented instructions use some version of direct addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (Section 6.3.3 "General Purpose Register File") or a location in the Access Bank (Section 6.3.2 "Access Bank") as the data source for the instruction. The Access RAM bit 'a' determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 6.3.1 "Bank Select Register (BSR)") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

#### 6.4.3 INDIRECT ADDRESSING

Indirect addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special Function Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory.

The registers for indirect addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code, using loops, such as the example of clearing an entire RAM bank in Example 6-5.

EXAMPLE 6-5: HOW TO CLEAR RAM

(BANK 1) USING

INDIRECT ADDRESSING

|          | LFSR  | FSR0, 100h | ; |                |

|----------|-------|------------|---|----------------|

| NEXT     | CLRF  | POSTINC0   | ; | Clear INDF     |

|          |       |            | ; | register then  |

|          |       |            | ; | inc pointer    |

|          | BTFSS | FSROH, 1   | ; | All done with  |

|          |       |            | ; | Bank1?         |

|          | BRA   | NEXT       | ; | NO, clear next |

| CONTINUE | €     |            | ; | YES, continue  |

#### 7.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

#### 7.1 **Table Reads and Table Writes**

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

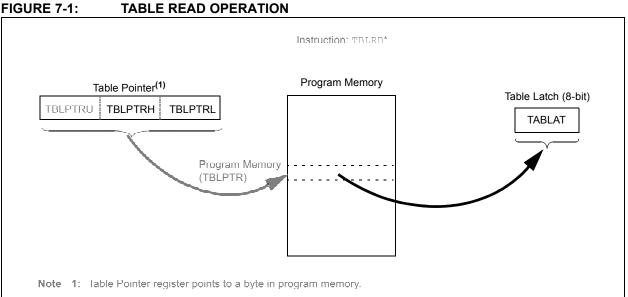

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 7-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in Section 7.5 "Writing to Flash Program Memory". Figure 7-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word-aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned.

FIGURE 7-1:

TABLE 11-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7                 | Bit 6                 | Bit 5    | Bit 4        | Bit 3       | Bit 2       | Bit 1       | Bit 0 | Reset<br>Values<br>on page |

|--------|-----------------------|-----------------------|----------|--------------|-------------|-------------|-------------|-------|----------------------------|

| PORTA  | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5      | RA4          | RA3         | RA2         | RA1         | RA0   | 58                         |

| LATA   | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | PORTA Da | ta Latch Re  | gister (Rea | d and Write | to Data Lat | ch)   | 58                         |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA Da | ta Direction | Register    |             |             |       | 58                         |

| ADCON1 | _                     | _                     | VCFG1    | VCFG0        | PCFG3       | PCFG2       | PCFG1       | PCFG0 | 57                         |

| CMCON  | C2OUT                 | C10UT                 | C2INV    | C1INV        | CIS         | CM2         | CM1         | CM0   | 57                         |

| CVRCON | CVREN                 | CVROE                 | CVRR     | CVRSS        | CVR3        | CVR2        | CVR1        | CVR0  | 57                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA<7:6> and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

### 11.2 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

#### **EXAMPLE 11-2: INITIALIZING PORTB**

| CLRF  | PORTB  | ; Initialize PORTB by     |

|-------|--------|---------------------------|

|       |        | ; clearing output         |

|       |        | ; data latches            |

| CLRF  | LATB   | ; Alternate method        |

|       |        | ; to clear output         |

|       |        | ; data latches            |

| MOVLW | 0Fh    | ; Set RB<4:0> as          |

| MOVWF | ADCON1 | ; digital I/O pins        |

|       |        | ; (required if config bit |

|       |        | ; PBADEN is set)          |

| MOVLW | 0CFh   | ; Value used to           |

|       |        | ; initialize data         |

|       |        | ; direction               |

| MOVWF | TRISB  | ; Set RB<3:0> as inputs   |

|       |        | ; RB<5:4> as outputs      |

|       |        | ; RB<7:6> as inputs       |

| 1     |        |                           |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit, RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Note: On a Power-on Reset, RB<4:0> are configured as analog inputs by default and read as '0'; RB<7:5> are configured as digital inputs.

By clearing the Configuration bit, PBADEN, RB<4:0> will alternatively be configured as digital inputs on POR.

Four of the PORTB pins (RB<7:4>) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep mode or any of the Idle modes. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the  ${\tt MOVFF}$  (ANY), PORTB instruction).

- b) 1 Tcy.

- c) Clear flag bit, RBIF.

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB and waiting 1 Tcy will end the mismatch condition and allow flag bit, RBIF, to be cleared. Also, if the port pin returns to its original state, the mismatch condition will be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB3 can be configured by the Configuration bit, CCP2MX, as the alternate peripheral pin for the CCP2 module (CCP2MX = 0).

### 11.4 PORTD, TRISD and LATD Registers

**Note:** PORTD is only available on 40/44-pin devices.

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

Three of the PORTD pins are multiplexed with outputs P1B, P1C and P1D of the Enhanced CCP module. The operation of these additional PWM output pins is covered in greater detail in **Section 17.0 "Enhanced Capture/Compare/PWM (ECCP) Module"**.

**Note:** On a Power-on Reset, these pins are configured as digital inputs.

PORTD can also be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit, PSPMODE (TRISE<4>). In this mode, the input buffers are TTL. See **Section 11.6 "Parallel Slave Port"** for additional information on the Parallel Slave Port (PSP).

Note: When the Enhanced PWM mode is used with either dual or quad outputs, the PSP functions of PORTD are automatically disabled.

#### **EXAMPLE 11-4: INITIALIZING PORTD**

| CLRF  | PORTD | ; Initialize PORTD by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATD  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0CFh  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISD | ; Set RD<3:0> as inputs |

|       |       | ; RD<5:4> as outputs    |

|       |       | ; RD<7:6> as inputs     |

|       |       |                         |

### 20.2 Selecting and Configuring Acquisition Time

The ADCON2 register allows the user to select an acquisition time that occurs each time the GO/DONE bit is set. It also gives users the option to use an automatically determined acquisition time.

Acquisition time may be set with the ACQT<2:0> bits (ADCON2<5:3>), which provides a range of 2 to 20 TAD. When the GO/DONE bit is set, the A/D module continues to sample the input for the selected acquisition time, then automatically begins a conversion. Since the acquisition time is programmed, there may be no need to wait for an acquisition time between selecting a channel and setting the GO/DONE bit.

Manual acquisition is selected when ACQT<2:0> = 000. When the GO/ $\overline{DONE}$  bit is set, sampling is stopped and a conversion begins. The user is responsible for ensuring the required acquisition time has passed between selecting the desired input channel and setting the  $\overline{GO/DONE}$  bit. This option is also the default Reset state of the ACQT<2:0> bits and is compatible with devices that do not offer programmable acquisition times.

In either case, when the conversion is completed, the GO/DONE bit is cleared, the ADIF flag is set and the A/D begins sampling the currently selected channel again. If an acquisition time is programmed, there is nothing to indicate if the acquisition time has ended or if the conversion has begun.

### 20.3 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 11 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. There are seven possible options for TAD:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal RC Oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be as short as possible, but greater than the minimum TAD (see parameter 130 for more information).

Table 20-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

TABLE 20-1: TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock So       | AD Clock Source (TAD) |                         | vice Frequency                  |

|-------------------|-----------------------|-------------------------|---------------------------------|

| Operation         | ADCS<2:0>             | PIC18F2X21/4X21         | PIC18LF2X21/4X21 <sup>(4)</sup> |

| 2 Tosc            | 000                   | 2.86 MHz                | 1.43 kHz                        |

| 4 Tosc            | 100                   | 5.71 MHz                | 2.86 MHz                        |

| 8 Tosc            | 001                   | 11.43 MHz               | 5.72 MHz                        |

| 16 Tosc           | 101                   | 22.86 MHz               | 11.43 MHz                       |

| 32 Tosc           | 010                   | 40.0 MHz                | 22.86 MHz                       |

| 64 Tosc           | 110                   | 40.0 MHz                | 22.86 MHz                       |

| RC <sup>(3)</sup> | x11                   | 1.00 MHz <sup>(1)</sup> | 1.00 MHz <sup>(2)</sup>         |

- **Note 1:** The RC source has a typical TAD time of 1.2  $\mu$ s.

- 2: The RC source has a typical TAD time of 2.5  $\mu$ s.

- **3:** For device frequencies above 1 MHz, the device must be in Sleep for the entire conversion or the A/D accuracy may be out of specification.

- 4: Low-power (PIC18LFXXXX) devices only.

TBLRD Table Read

Syntax: TBLRD ( \*; \*+; \*-; +\*)

Operands: None

Operation: if TBLRD \*,

$(\mathsf{Prog}\;\mathsf{Mem}\;(\mathsf{TBLPTR})) \to \mathsf{TABLAT},$

TBLPTR - No Change;

if TBLRD \*+,

$(\mathsf{Prog}\;\mathsf{Mem}\;(\mathsf{TBLPTR})) \to \mathsf{TABLAT},$

(TBLPTR) +  $1 \rightarrow$  TBLPTR;

if TBLRD \*-,

(Prog Mem (TBLPTR)) → TABLAT,

$(TBLPTR) - 1 \rightarrow TBLPTR;$

if TBLRD +\*,

(TBLPTR) +  $1 \rightarrow$  TBLPTR,

$(\mathsf{Prog}\;\mathsf{Mem}\;(\mathsf{TBLPTR})) \to \mathsf{TABLAT}$

Status Affected: None

Encoding:

| 0000 | 0000 | 0000 | 10nn |     |

|------|------|------|------|-----|

|      |      |      | nn=0 | *   |

|      |      |      | =1   | *+  |

|      |      |      | =2   | * – |

|      |      |      | =3 - | +*  |

Description:

This instruction is used to read the contents of Program Memory (P.M.). To address the program memory, a pointer called Table

Pointer (TBLPTR) is used.

The TBLPTR (a 21-bit pointer) points to each byte in the program memory. TBLPTR

has a 2-Mbyte address range.

TBLPTR[0] = 0: Least Significant Byte of

Program Memory Word

TBLPTR[0] = 1: Most Significant Byte of Program Memory Word

The TBLRD instruction can modify the value

of TBLPTR as follows:

no change

post-increment

post-decrement

pre-increment

Words: 1

Cycles: 2

Q Cycle Activity:

| Q1           | Q1 Q2                      |              | Q4                     |

|--------------|----------------------------|--------------|------------------------|

| Decode       | Decode No                  |              | No                     |

|              | operation                  |              | operation              |

| No operation | No operation (Read Program | No operation | No operation<br>(Write |

| '            | ` Memory)                  |              | TÀBLAT)                |

| TBLRD                                                                                   | Table Read             | (Co              | ontinued)                               |

|-----------------------------------------------------------------------------------------|------------------------|------------------|-----------------------------------------|

| Example 1:                                                                              | TBLRD *+               | ;                |                                         |

| Before Instructi<br>TABLAT<br>TBLPTR<br>MEMORY<br>After Instruction<br>TABLAT<br>TBLPTR | (00A356h)              | = = = =          | 55h<br>00A356h<br>34h<br>34h<br>00A357h |

| Example 2:                                                                              | TBLRD +*               | ;                |                                         |

| MEMORY                                                                                  | (01A357h)<br>(01A358h) | =<br>=<br>=<br>= | AAh<br>01A357h<br>12h<br>34h            |

| After Instruction<br>TABLAT<br>TBLPTR                                                   | 1                      | =                | 34h<br>01A358h                          |

# 26.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit™ 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit™ 2 enables in-circuit debugging on most PIC® microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 26.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

### 26.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>TM</sup> and dsPICDEM<sup>TM</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, Keeloq® security ICs, CAN, IrDA®, PowerSmart battery management, Seevaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

27.1 DC Characteristics: Supply Voltage

PIC18F2221/2321/4221/4321 (Industrial) PIC18LF2221/2321/4221/4321 (Industrial)

| PIC18LF2221/2321/4221/4321<br>(Industrial)          |      |                                                                  | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for industrial                                                                           |      |            |       |                                           |

|-----------------------------------------------------|------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|-------|-------------------------------------------|

| PIC18F2221/2321/4221/4321<br>(Industrial, Extended) |      |                                                                  | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |      |            |       |                                           |

| Param No. Symbol Characteristic                     |      |                                                                  | Min                                                                                                                                                                                                                                | Тур  | Max        | Units | Conditions                                |

| D001                                                | VDD  | Supply Voltage                                                   |                                                                                                                                                                                                                                    |      |            |       |                                           |

|                                                     |      | PIC18LF2X21/4X21                                                 | 2.0                                                                                                                                                                                                                                | _    | 5.5        | V     |                                           |

|                                                     |      | PIC18F2X21/4X21                                                  | 4.2                                                                                                                                                                                                                                | 1    | 5.5        | V     |                                           |

| D001C                                               | AVDD | Analog Supply Voltage                                            | VDD - 0.3V                                                                                                                                                                                                                         | _    | VDD + 0.3V | V     |                                           |

| D001D                                               | AVss | Analog Ground Voltage                                            | Vss - 0.3V                                                                                                                                                                                                                         | _    | Vss + 0.3V | V     |                                           |

| D002                                                | VDR  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5                                                                                                                                                                                                                                | _    | _          | V     |                                           |

| D003                                                | VPOR | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal | _                                                                                                                                                                                                                                  | _    | 0.7        | V     | See section on Power-on Reset for details |

| D004                                                | SVDD | VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal     | 0.05                                                                                                                                                                                                                               | _    | _          | V/ms  | See section on Power-on Reset for details |

|                                                     | VBOR | Brown-out Reset Voltag                                           | е                                                                                                                                                                                                                                  |      |            |       |                                           |

| D005                                                |      | PIC18LF2X21/4X21                                                 |                                                                                                                                                                                                                                    |      |            |       |                                           |

|                                                     |      | BORV<1:0> = 11                                                   | 2.00                                                                                                                                                                                                                               | 2.11 | 2.22       | V     |                                           |

|                                                     |      | BORV<1:0> = 10                                                   | 2.65                                                                                                                                                                                                                               | 2.79 | 2.93       | V     |                                           |

| D005                                                |      | All devices                                                      |                                                                                                                                                                                                                                    |      |            |       |                                           |

|                                                     |      | BORV<1:0> = 01 <sup>(2)</sup>                                    | 4.11                                                                                                                                                                                                                               | 4.33 | 4.55       | V     |                                           |

|                                                     |      | BORV<1:0> = 00                                                   | 4.36                                                                                                                                                                                                                               | 4.59 | 4.82       | V     |                                           |

**Legend:** Shading of rows is to assist in readability of the table.

Note 1: This is the limit to which VDD can be lowered in Sleep mode, or during a device Reset, without losing RAM data.

<sup>2:</sup> With BOR enabled, full-speed operation (Fosc = 40 MHz) is supported until a BOR occurs. This is valid although VDD may be below the minimum voltage for this frequency.

## 27.3 DC Characteristics: PIC18F2221/2321/4221/4321 (Industrial) PIC18LF2221/2321/4221/4321 (Industrial)

|              |        | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                             |          |       |                                                           |

|--------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------|-------|-----------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                                                                                                                                                                           | Min                         | Max      | Units | Conditions                                                |

|              | VIL    | Input Low Voltage                                                                                                                                                                        |                             |          |       |                                                           |

|              |        | I/O Ports:                                                                                                                                                                               |                             |          |       |                                                           |

| D030         |        | with TTL Buffer                                                                                                                                                                          | Vss                         | 0.15 VDD | V     | VDD < 4.5V                                                |

| D030A        |        |                                                                                                                                                                                          | _                           | 0.8      | V     | $4.5V \le VDD \le 5.5V$                                   |

| D031         |        | with Schmitt Trigger Buffer                                                                                                                                                              | Vss                         | 0.2 VDD  | V     |                                                           |

| D031A        |        | RC3 and RC4                                                                                                                                                                              | Vss                         | 0.3 VDD  | V     | I <sup>2</sup> C™ enabled                                 |

| D031B        |        |                                                                                                                                                                                          | Vss                         | 0.8      | V     | SMBus enabled                                             |

| D032         |        | MCLR                                                                                                                                                                                     | Vss                         | 0.2 VDD  | V     |                                                           |

| D033         |        | OSC1                                                                                                                                                                                     | Vss                         | 0.3 VDD  | V     | HS, HSPLL modes                                           |

| D033A        |        | OSC1                                                                                                                                                                                     | Vss                         | 0.2 VDD  | V     | RC, EC modes <sup>(1)</sup>                               |

| D033B        |        | OSC1                                                                                                                                                                                     | Vss                         | 0.3      | V     | XT, LP modes                                              |

| D034         |        | T13CKI                                                                                                                                                                                   | Vss                         | 0.3      | V     |                                                           |

|              | VIH    | Input High Voltage                                                                                                                                                                       |                             |          |       |                                                           |

|              |        | I/O Ports:                                                                                                                                                                               |                             |          |       |                                                           |

| D040         |        | with TTL Buffer                                                                                                                                                                          | 0.25 V <sub>DD</sub> + 0.8V | VDD      | V     | VDD < 4.5V                                                |

| D040A        |        |                                                                                                                                                                                          | 2.0                         | VDD      | V     | $4.5V \le VDD \le 5.5V$                                   |

| D041         |        | with Schmitt Trigger Buffer                                                                                                                                                              | 0.8 VDD                     | VDD      | V     |                                                           |

| D041A        |        | RC3 and RC4                                                                                                                                                                              | 0.7 VDD                     | VDD      | V     | I <sup>2</sup> C™ enabled                                 |

| D041B        |        |                                                                                                                                                                                          | 2.1                         | VDD      | V     | SMBus enabled,<br>Vss ≥ 3V                                |

| D042         |        | MCLR                                                                                                                                                                                     | 0.8 VDD                     | VDD      | V     |                                                           |

| D043         |        | OSC1                                                                                                                                                                                     | 0.7 VDD                     | VDD      | V     | HS, HSPLL modes                                           |

| D043A        |        | OSC1                                                                                                                                                                                     | 0.8 VDD                     | VDD      | V     | EC mode                                                   |

| D043B        |        | OSC1                                                                                                                                                                                     | 0.9 VDD                     | Vdd      | V     | RC mode <sup>(1)</sup>                                    |

| D043C        |        | OSC1                                                                                                                                                                                     | 1.6                         | VDD      | V     | XT, LP modes                                              |

| D044         |        | T13CKI                                                                                                                                                                                   | 1.6                         | VDD      | V     |                                                           |

|              | lı∟    | Input Leakage Current <sup>(2,3)</sup>                                                                                                                                                   |                             |          |       |                                                           |

| D060         |        | I/O Ports                                                                                                                                                                                | _                           | ±200     | nA    | VDD < 5.5V,<br>VSS ≤ VPIN ≤ VDD,<br>Pin at High-Impedance |

|              |        |                                                                                                                                                                                          | _                           | ±50      | nA    | VDD < 3V,<br>VSS ≤ VPIN ≤ VDD,<br>Pin at High-Impedance   |

| D061         |        | MCLR                                                                                                                                                                                     | _                           | ±1       | μΑ    | $Vss \le VPIN \le VDD$                                    |

| D063         |        | OSC1                                                                                                                                                                                     | _                           | ±1       | μΑ    | $Vss \le VPIN \le VDD$                                    |

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC<sup>®</sup> device be driven with an external clock while in RC mode.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as current sourced by the pin.

Note:

#### 27.4.2 TIMING CONDITIONS

**AC CHARACTERISTICS**

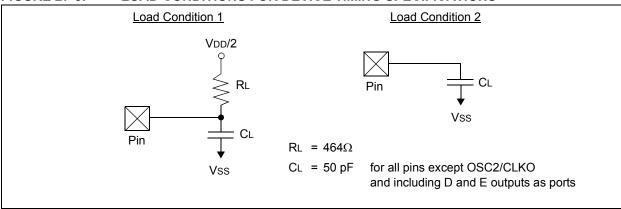

The temperature and voltages specified in Table 27-5 apply to all timing specifications unless otherwise noted. Figure 27-5 specifies the load conditions for the timing specifications.

Because of space limitations, the generic terms "PIC18FXXXX" and "PIC18LFXXXX" are used throughout this section to refer to the PIC18F2221/2321/4221/4321 and PIC18LF2221/2321/4221/4321 families of devices specifically and only those devices.

TABLE 27-5: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  for industrial  $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$  for extended

Operating voltage VDD range as described in DC spec Section 27.1 and Section 27.3.

FIGURE 27-5: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

LF parts operate for industrial temperatures only.

**TABLE 27-24: A/D CONVERTER CHARACTERISTICS**

| Param<br>No. | Symbol         | Characteristic                                    | Min                       | Тур    | Max         | Units                    | Conditions                                                  |

|--------------|----------------|---------------------------------------------------|---------------------------|--------|-------------|--------------------------|-------------------------------------------------------------|

| A01          | NR             | Resolution                                        | _                         | _      | 10          | bit                      | $\Delta VREF \ge 3.0V$                                      |

| A03          | EIL            | Integral Linearity Error                          | _                         | _      | <±1         | LSb                      | $\Delta V$ REF $\geq 3.0V$                                  |

| A04          | EDL            | Differential Linearity Error                      | _                         | _      | <±1         | LSb                      | $\Delta V$ REF $\geq 3.0V$                                  |

| A06          | Eoff           | Offset Error                                      | _                         | _      | < <u>±2</u> | LSb                      | $\Delta VREF \ge 3.0V$                                      |

| A07          | Egn            | Gain Error                                        | _                         | _      | <±1         | LSb                      | $\Delta V$ REF $\geq 3.0V$                                  |

| A10          | _              | Monotonicity                                      | Guaranteed <sup>(1)</sup> |        |             | _                        | $Vss \leq Vain \leq Vref$                                   |

| A20          | $\Delta V$ REF | Reference Voltage Range<br>(VREFH – VREFL)        | 1.8<br>3                  | _      |             | V                        | VDD < 3.0V<br>$VDD \ge 3.0V$                                |

| A21          | VREFH          | Reference Voltage High                            | _                         | _      | VDD + 3.0V  | V                        |                                                             |

| A22          | VREFL          | Reference Voltage Low                             | Vss - 0.3V                | _      | _           | V                        |                                                             |

| A25          | VAIN           | Analog Input Voltage                              | VREFL                     | _      | VREFH       | V                        |                                                             |

| A30          | ZAIN           | Recommended Impedance of<br>Analog Voltage Source | _                         | _      | 2.5         | kΩ                       |                                                             |

| A50          | IREF           | VREF Input Current <sup>(2)</sup>                 |                           | _<br>_ | 5<br>150    | μ <b>Α</b><br>μ <b>Α</b> | During VAIN acquisition.<br>During A/D conversion<br>cycle. |

**Note 1:** The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

**<sup>2:</sup>** VREFH current is from RA3/AN3/VREF+ pin or VDD, whichever is selected as the VREFH source. VREFL current is from RA2/AN2/VREF-/CVREF pin or VSS, whichever is selected as the VREFL source.

| C                                                     |     | Effects of a Reset                       |          |

|-------------------------------------------------------|-----|------------------------------------------|----------|

| C Compilers                                           |     | Interrupts                               |          |

| MPLAB C18                                             | 330 | Operation                                |          |

| MPLAB C30                                             |     | Operation During Sleep                   |          |

| CALL                                                  |     | Outputs                                  |          |

| CALLW                                                 |     | Reference                                |          |

| Capture (CCP Module)                                  |     | External Signal                          |          |

| Associated Registers                                  |     | Internal Signal                          |          |

| CCP Pin Configuration                                 |     | Response Time                            |          |

| CCPRxH:CCPRxL Registers                               |     | Comparator Specifications                |          |

| Prescaler                                             |     | Comparator Voltage Reference             |          |

| Software Interrupt                                    |     | Accuracy and Error                       |          |

| Timer1/Timer3 Mode Selection                          |     | Associated Registers                     |          |

| Capture (ECCP Module)                                 |     | Configuring                              |          |

| Capture/Compare/PWM (CCP)                             |     | Connection Considerations                | 250      |

| Capture Mode. See Capture.                            |     | Effects of a Reset                       | 250      |

| CCPRxH Register                                       | 146 | Operation During Sleep                   | 250      |

| CCPRxL Register                                       |     | Compare (CCP Module)                     | 148      |

| Compare Mode. See Compare.                            |     | CCPRx Register                           |          |

| Interaction of Two CCP Modules                        | 146 | Pin Configuration                        | 148      |

| Module Configuration                                  |     | Software Interrupt                       | 148      |

| Pin Assignment                                        |     | Special Event Trigger 143,               | 148, 242 |

| Timer Resources                                       |     | Timer1/Timer3 Mode Selection             | 148      |

| Clock Sources                                         |     | Compare (ECCP Module)                    | 154      |

| Selecting the 31 kHz Source                           |     | Special Event Trigger                    | 154      |

| Selection Using OSCCON Register                       |     | Computed GOTO                            | 62       |

| CLRF                                                  |     | Configuration Bits                       | 259      |

| CLRWDT                                                |     | Context Saving During Interrupts         |          |

| Code Examples                                         | 293 | Conversion Considerations                | 387      |

| 16 x 16 Signed Multiply Routine                       | 06  | CPFSEQ                                   | 296      |

|                                                       |     | CPFSGT                                   | 297      |

| 16 x 16 Unsigned Multiply Routine                     |     | CPFSLT                                   | 297      |

| 8 x 8 Signed Multiply Routine                         |     | Crystal Oscillator/Ceramic Resonator     | 29       |

| 8 x 8 Unsigned Multiply Routine                       |     | Customer Change Notification Service     |          |

| Address Masking Changing Potygon Capture Proceeding   |     | Customer Notification Service            |          |

| Changing Between Capture Prescalers                   |     | Customer Support                         | 399      |

| Computed GOTO Using an Offset Value  Data EEPROM Read |     | _                                        |          |

| Data EEPROM Refresh Routine                           |     | D                                        |          |

| Data EEPROM Write                                     |     | Data Addressing Modes                    | 73       |

| Erasing a Flash Program Memory Row                    |     | Comparing Options with the Extended      |          |

| Fast Register Stack                                   |     | Instruction Set Enabled                  | 76       |

| How to Clear RAM (Bank 1) Using Indirect              | 02  | Direct                                   | 73       |

| Addressing                                            | 73  | Indexed Literal Offset                   | 75       |

| <u> </u>                                              | 13  | Instructions Affected                    | 75       |

| Implementing a Real-Time Clock Using a                | 127 | Indirect                                 | 73       |

| Timer1 Interrupt Service                              |     | Inherent and Literal                     | 73       |

| Initializing PORTA                                    |     | Data EEPROM Memory                       | 89       |

| Initializing PORTS                                    |     | Associated Registers                     | 93       |

| Initializing PORTC                                    |     | EEADR Register                           | 89       |

| Initializing PORTD                                    |     | EECON1 Register                          | 89       |

| Initializing PORTE                                    |     | EECON2 Register                          | 89       |

| Loading the SSPBUF (SSPSR) Register                   |     | EEDATA Register                          |          |

| Reading a Flash Program Memory Word                   | 83  | Operation During Code-Protect            | 92       |

| Saving STATUS, WREG and BSR                           | 400 | Protection Against Spurious Write        |          |

| Registers in RAM                                      |     | Reading                                  |          |

| Writing to Flash Program Memory                       |     | Using                                    |          |

| Code Protection                                       |     | Write Verify                             |          |

| Associated Registers                                  |     | Writing                                  |          |

| Configuration Register Protection                     |     | Data Memory                              |          |

| Data EEPROM                                           |     | Access Bank                              |          |

| Program Memory                                        |     | and the Extended Instruction Set         |          |

| COMF                                                  |     | Bank Select Register (BSR)               |          |

| Comparator                                            |     | General Purpose Registers                |          |

| Analog Input Connection Considerations                |     | Map for PIC18F2221/2321/4221/4321 Family |          |

| Associated Registers                                  |     | Special Function Registers               |          |

| Configuration                                         | 244 | •                                        |          |

| High/Low-Voltage Detect                     | 253   | Instruction Cycle                     | 6               |

|---------------------------------------------|-------|---------------------------------------|-----------------|

| Applications                                | 256   | Clocking Scheme                       |                 |

| Associated Registers                        |       | Instruction Flow/Pipelining           |                 |

| Characteristics                             |       | Instruction Set                       |                 |

| Current Consumption                         |       | ADDLW                                 |                 |

| Effects of a Reset                          |       | ADDWF                                 | 28              |

| Operation                                   |       | ADDWF (Indexed Literal Offset Mode)   | 32              |

| During Sleep                                |       | ADDWFC                                |                 |

| Setup                                       |       | ANDLW                                 |                 |

| Start-up Time                               |       | ANDWF                                 |                 |

| Typical Application                         |       | BC                                    |                 |

| HLVD. See High/Low-Voltage Detect.          |       | BCF                                   |                 |

| TIEVE. Occ Trigit/Low Voltage Detect        | 200   | BN                                    |                 |

| 1                                           |       | BNC                                   |                 |

| I/O Ports                                   | 111   | BNN                                   |                 |

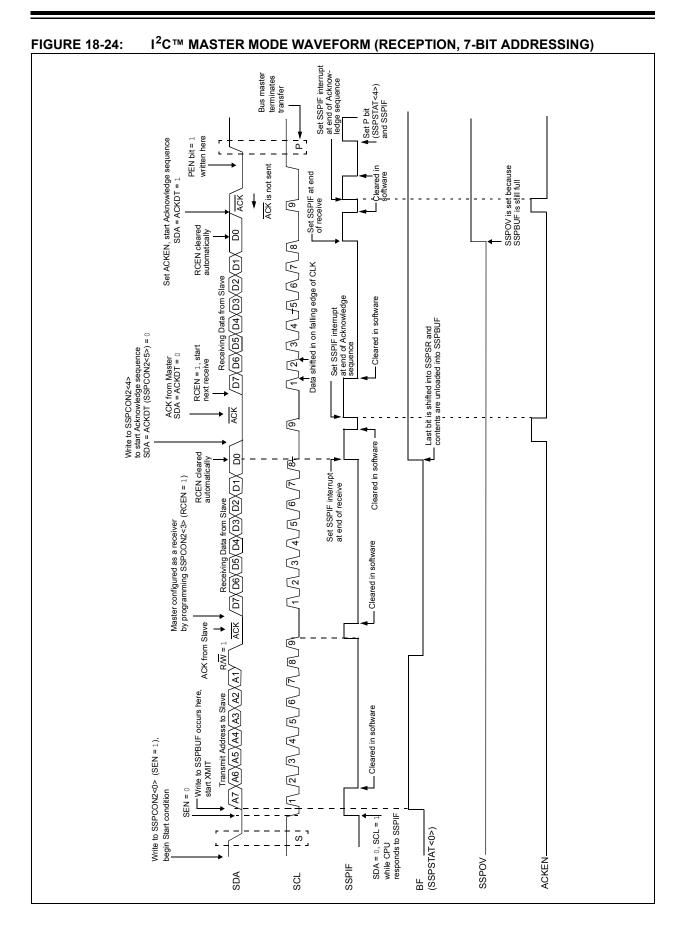

| I <sup>2</sup> C Mode (MSSP)                |       | BNOV                                  |                 |

| Acknowledge Sequence Timing                 | 204   | BNZ                                   |                 |

| Associated Registers                        |       | BOV                                   |                 |

| Baud Rate Generator                         |       | BRA                                   |                 |

| Bus Collision                               |       | BSF                                   |                 |

| During a Repeated Start Condition           | 208   | BSF (Indexed Literal Offset Mode)     |                 |

| During a Start Condition                    |       | · · · · · · · · · · · · · · · · · · · |                 |

| During a Start Condition                    |       | BTFSC                                 |                 |

| Clock Arbitration                           |       | BTFSS                                 |                 |

|                                             |       | BTG                                   |                 |

| Clock Stretching                            |       | BZ                                    |                 |

| 10-Bit Slave Receive Mode (SEN = 1)         |       | CALL                                  |                 |

| 10-Bit Slave Transmit Mode                  |       | CLRF                                  |                 |

| 7-Bit Slave Receive Mode (SEN = 1) .        |       | CLRWDT                                |                 |

| 7-Bit Slave Transmit Mode                   |       | COMF                                  |                 |

| Clock Synchronization and the CKP Bit       |       | CPFSEQ                                |                 |

| Effects of a Reset                          |       | CPFSGT                                |                 |

| General Call Address Support                |       | CPFSLT                                | 29              |

| I <sup>2</sup> C Clock Rate w/BRG           |       | DAW                                   | 298             |

| Master Mode                                 | 195   | DCFSNZ                                | 299             |

| Operation                                   | 196   | DECF                                  | 298             |

| Reception                                   |       | DECFSZ                                | 299             |

| Repeated Start Condition Timing             | 200   | Extended Instruction Set              | 32 <sup>-</sup> |

| Start Condition Timing                      | 199   | General Format                        | 28              |

| Transmission                                | 201   | GOTO                                  | 300             |

| Multi-Master Communication, Bus Collision   |       | INCF                                  | 300             |

| and Arbitration                             | 205   | INCFSZ                                | 30              |

| Multi-Master Mode                           | 205   | INFSNZ                                | 30              |

| Operation                                   | 181   | IORLW                                 | 302             |

| Read/Write Bit Information (R/W Bit)        | 181   | IORWF                                 | 302             |

| Read/Write Bit Information (R/W Bit)        | 183   | LFSR                                  | 303             |

| Registers                                   | 176   | MOVF                                  | 30              |

| Serial Clock (RC3/SCK/SCL)                  | 183   | MOVFF                                 |                 |

| Slave Mode                                  |       | MOVLB                                 |                 |

| Address Masking                             |       | MOVLW                                 |                 |

| Addressing                                  |       | MOVWF                                 |                 |

| Reception                                   |       | MULLW                                 |                 |

| Transmission                                |       | MULWF                                 |                 |

| Sleep Operation                             |       | NEGF                                  |                 |

| Stop Condition Timing                       |       | NOP                                   |                 |

| ID Locations                                |       |                                       |                 |

| INCF                                        |       | Opcode Field Descriptions             |                 |

|                                             |       | POP                                   |                 |

| INCFSZ                                      |       | PUSH                                  |                 |

| In-Circuit Debugger                         |       | RCALL                                 |                 |

| In-Circuit Serial Programming (ICSP)        |       | RESET                                 |                 |

| Single-Supply                               | 277   | RETFIE                                |                 |

| Indexed Literal Offset Addressing           |       | RETLW                                 |                 |

| and Standard PIC18 Instructions             |       | RETURN                                |                 |

| Indexed Literal Offset Mode                 |       | RLCF                                  |                 |

| Indirect Addressing                         |       | RLNCF                                 |                 |

| INFSNZ                                      |       | RRCF                                  | 312             |

| Initialization Conditions for all Registers | 55–58 |                                       |                 |

| Software Simulator (MPLAB SIM)                    | 330 | TMR1L Register                                                           | . 133 |

|---------------------------------------------------|-----|--------------------------------------------------------------------------|-------|

| Special Event Trigger. See Compare (CCP Mode).    |     | Use as a Real-Time Clock                                                 |       |

| Special Event Trigger. See Compare (ECCP Module). |     | Timer2                                                                   |       |

| Special Features of the CPU                       | 259 | Associated Registers                                                     | 140   |

| Special Function Registers                        | 68  | Interrupt                                                                | 140   |

| Map                                               | 68  | Operation                                                                | 139   |

| SPI Mode (MSSP)                                   |     | Output                                                                   |       |

| Associated Registers                              | 175 | PR2 Register150,                                                         | 155   |

| Bus Mode Compatibility                            | 175 | TMR2 to PR2 Match Interrupt                                              | . 155 |