Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

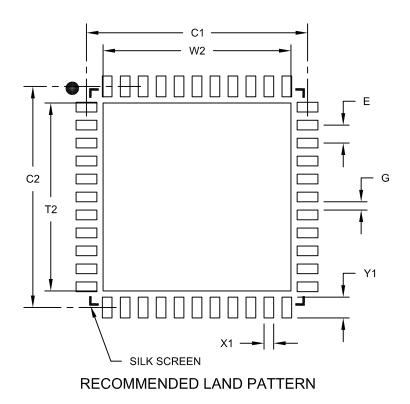

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2221-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F2221 PIC18LF2221

- PIC18F2321 PIC18LF2321

- PIC18F4221 PIC18LF4221

- PIC18F4321 PIC18LF4321

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of highendurance, Enhanced Flash program memory. On top of these features, the PIC18F2221/2321/4221/4321 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

## 1.1 New Core Features

#### 1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F2221/2321/4221/4321 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- **Multiple Idle Modes:** The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- On-the-Fly Mode Switching: The power-managed modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 27.0 "Electrical Characteristics" for values.

## 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F2221/2321/4221/4321 family offer ten different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators.

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O).

- Two External RC Oscillator modes with the same pin options as the External Clock modes.

- Two Internal Oscillator modes which provide an 8 MHz clock and an INTRC source (approximately 31 kHz), as well as a range of 6 user-selectable clock frequencies, between 125 kHz to 4 MHz, for a total of 8 clock frequencies. One or both of the oscillator pins can be used for general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both the high-speed crystal and internal oscillator modes, which allows clock speeds of up to 40 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 32 MHz – all without using an external crystal or clock circuit.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

# 3.4 RC Oscillator

For timing insensitive applications, the RC and RCIO Oscillator modes offer additional cost savings. The actual oscillator frequency is a function of several factors:

- supply voltage

- values of the external resistor (REXT) and capacitor (CEXT)

- · operating temperature

Given the same device, operating voltage, temperature and component values, there will also be unit-to-unit frequency variations. These are due to factors such as:

- normal manufacturing variation

- difference in lead frame capacitance between package types (especially for low CEXT values)

- variations within the tolerance of limits of  $\ensuremath{\mathsf{REXT}}$  and  $\ensuremath{\mathsf{CEXT}}$

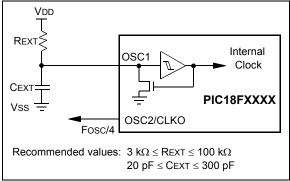

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 3-5 shows how the R/C combination is connected.

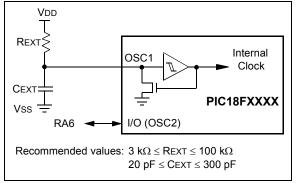

The RCIO Oscillator mode (Figure 3-6) functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

# 3.5 PLL Frequency Multiplier

A Phase Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency oscillator circuit or to clock the device up to its highest rated frequency from a crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals or users who require higher clock speeds from an internal oscillator.

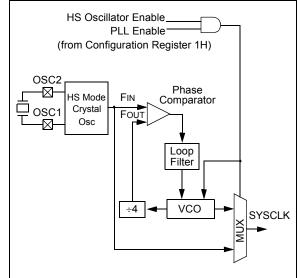

### 3.5.1 HSPLL OSCILLATOR MODE

The HSPLL mode makes use of the HS mode oscillator for frequencies up to 10 MHz. A PLL then multiplies the oscillator output frequency by 4 to produce an internal clock frequency up to 40 MHz. The PLLEN bit is not available when this mode is configured as the primary clock source.

The PLL is only available to the crystal oscillator when the FOSC<3:0> Configuration bits are programmed for HSPLL mode (= 0110).

# 3.5.2 PLL AND INTOSC

The PLL is also available to the internal oscillator block when the internal oscillator block is configured as the primary clock source. In this configuration, the PLL is enabled in software and generates a clock output of up to 32 MHz. The operation of INTOSC with the PLL is described in **Section 3.6.4 "PLL in INTOSC Modes"**.

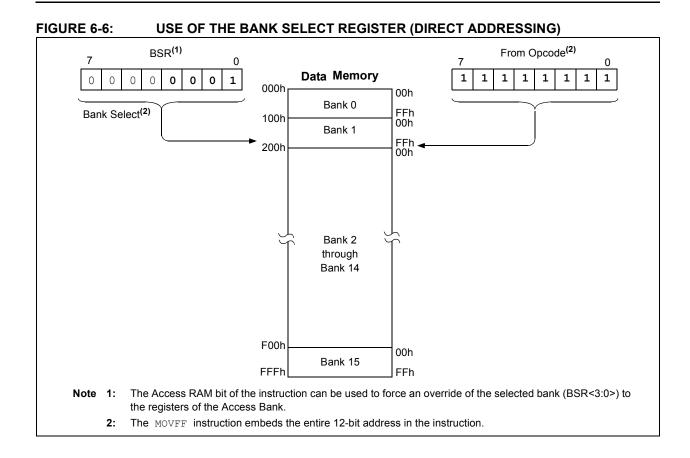

# 6.3.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 128 bytes of memory (00h-7Fh) in Bank 0 and the last 128 bytes of memory (80h-FFh) in Block 15. The lower half is known as the "Access RAM" and is composed of GPRs. This upper half is also where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 6-5).

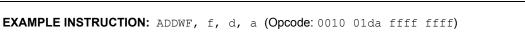

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0',

however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle, without updating the BSR first. For 8-bit addresses of 80h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 80h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 6.5.3 "Mapping the Access Bank in Indexed Literal Offset Addressing Mode".

#### 6.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

### FIGURE 6-8: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

#### When 'a' = 0 and 'f' $\geq$ 60h:

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and 0FFh. This is the same as locations 060h to 07Fh (Bank 0) and F80h to FFFh (Bank 15) of data memory.

Locations below 60h are not available in this addressing mode.

#### When 'a' = 0 and 'f' $\leq$ 5Fh:

The instruction executes in Indexed Literal Offset mode. 'f' is interpreted as an offset to the address value in FSR2. The two are added together to obtain the address of the target register for the instruction. The address can be anywhere in the data memory space.

Note that in this mode, the correct syntax is now: ADDWF [k], d where 'k' is the same as 'f'.

#### When 'a' = 1 (all values of 'f'):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 16 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

| INTCON3:                 | INTERRU                      | PICONII         | ROL REGI    | SIER 3       |              |        |        |

|--------------------------|------------------------------|-----------------|-------------|--------------|--------------|--------|--------|

| R/W-1                    | R/W-1                        | U-0             | R/W-0       | R/W-0        | U-0          | R/W-0  | R/W-0  |

| INT2IP                   | INT1IP                       | —               | INT2IE      | INT1IE       | —            | INT2IF | INT1IF |

| bit 7                    |                              |                 |             |              |              |        | bit 0  |

| INT2IP: IN               | T2 External                  | nterrupt Pri    | ority bit   |              |              |        |        |

| 1 = High p<br>0 = Low pr | •                            |                 |             |              |              |        |        |

| INT1IP: IN               | T1 External                  | nterrupt Pri    | ority bit   |              |              |        |        |

| 1 = High p<br>0 = Low pr |                              |                 |             |              |              |        |        |

| Unimplem                 | ented: Read                  | <b>l as</b> '0' |             |              |              |        |        |

| INT2IE: IN               | T2 External                  | nterrupt En     | able bit    |              |              |        |        |

|                          | es the INT2 e                |                 | •           |              |              |        |        |

|                          | es the INT2                  |                 | •           |              |              |        |        |

|                          | T1 External                  | •               |             |              |              |        |        |

|                          | es the INT1 e<br>es the INT1 |                 | •           |              |              |        |        |

| Unimplem                 | ented: Read                  | <b>l as</b> '0' |             |              |              |        |        |

| INT2IF: IN               | T2 External I                | nterrupt Fla    | ıg bit      |              |              |        |        |

|                          | IT2 external                 | •               | •           | t be cleared | in software) | )      |        |

| 0 = The IN               | IT2 external                 | interrupt dic   | d not occur |              |              |        |        |

|                          | T1 External I                | •               | •           |              |              |        |        |

|                          | IT1 external                 |                 | · ·         | t be cleared | in software) | )      |        |

| 0 = 1  ne IN             | IT1 external                 | interrupt aic   | not occur   |              |              |        |        |

#### REGISTER 10-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

### 10.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable registers (PIE1 and PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

### REGISTER 10-6: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

|       | R/W-0                     | R/W-0                        | R/W-0                          | R/W-0          | R/W-0         | R/W-0          | R/W-0          | R/W-0  |

|-------|---------------------------|------------------------------|--------------------------------|----------------|---------------|----------------|----------------|--------|

|       | PSPIE <sup>(1)</sup>      | ADIE                         | RCIE                           | TXIE           | SSPIE         | CCP1IE         | TMR2IE         | TMR1IE |

|       | bit 7                     |                              |                                | •              | •             | •              |                | bit 0  |

|       |                           |                              |                                |                |               | (4)            |                |        |

| bit 7 |                           |                              | Port Read/W                    | -              | ot Enable bit | (1)            |                |        |

|       |                           |                              | ead/write int<br>read/write in |                |               |                |                |        |

|       | Note 1:                   | This bit is u                | unimplement                    | ted on 28-pi   | n devices ar  | nd will read a | <b>as</b> '0'. |        |

| bit 6 | ADIE: A/D                 | Converter I                  | nterrupt Ena                   | ble bit        |               |                |                |        |

|       | 1 = Enable<br>0 = Disable | s the A/D in<br>s the A/D ir |                                |                |               |                |                |        |

| bit 5 | RCIE: EUS                 | ART Recei                    | ve Interrupt                   | Enable bit     |               |                |                |        |

|       |                           |                              | RT receive i<br>ART receive    |                |               |                |                |        |

| bit 4 | TXIE: EUS                 | ART Transr                   | nit Interrupt                  | Enable bit     |               |                |                |        |

|       |                           |                              | RT transmit                    |                |               |                |                |        |

|       | 0 = Disable               | es the EUSA                  | ART transmit                   | interrupt      |               |                |                |        |

| bit 3 |                           |                              | onous Seria                    | I Port Interru | ipt Enable b  | pit            |                |        |

|       | 1 = Enable<br>0 = Disable | s the MSSF<br>s the MSSF     |                                |                |               |                |                |        |

| bit 2 | CCP1IE: C                 | CP1 Interru                  | pt Enable bi                   | t              |               |                |                |        |

|       | 1 = Enable<br>0 = Disable |                              |                                |                |               |                |                |        |

| bit 1 | <b>TMR2IE:</b> ⊤          | MR2 to PR2                   | 2 Match Inte                   | rrupt Enable   | bit           |                |                |        |

|       |                           |                              | to PR2 mat                     | •              |               |                |                |        |

|       |                           |                              | 2 to PR2 ma                    | •              |               |                |                |        |

| bit 0 |                           |                              | ow Interrupt                   |                |               |                |                |        |

|       |                           |                              | overflow int                   |                |               |                |                |        |

|       |                           |                              | l overflow in                  | terrupt        |               |                |                |        |

|       | Legend:                   |                              |                                |                |               |                |                |        |

|       | R = Readal                | ble bit                      | W = Wr                         | itable bit     | U = Unim      | plemented b    | oit. read as ' | 0'     |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

NOTES:

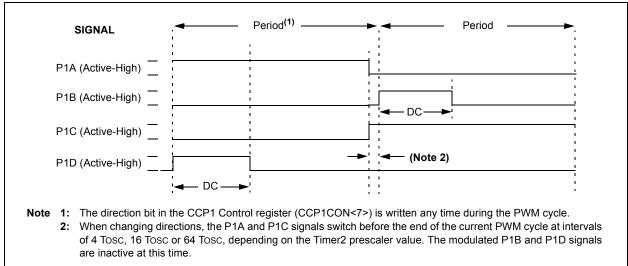

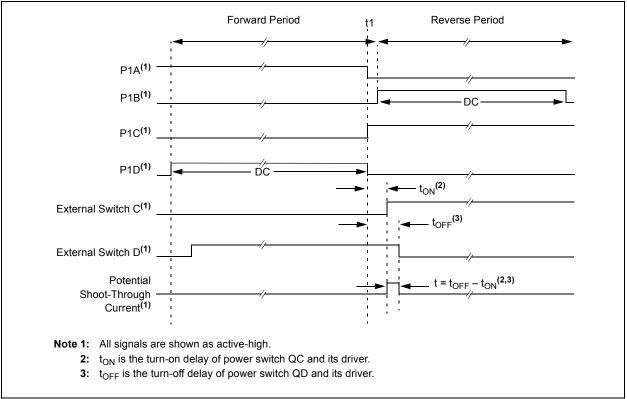

#### FIGURE 17-8: PWM DIRECTION CHANGE

# 18.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

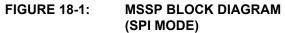

### 18.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with address masking for both 10-bit and 7-bit addressing)

The  $\mathrm{I}^2\mathrm{C}$  interface supports the following modes in hardware:

- · Master mode

- Multi-Master mode

- Slave mode

# 18.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON1 and SSPCON2). The use of these registers and their individual Configuration bits differ significantly depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections.

### 18.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four SPI modes are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) SDO

- Serial Data In (SDI) SDI/SDA

- Serial Clock (SCK) SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

• Slave Select (SS)

Figure 18-1 shows the block diagram of the MSSP module when operating in SPI mode.

# 19.1 Baud Rate Generator (BRG)

The BRG is a dedicated 8-bit or 16-bit generator that supports both the Asynchronous and Synchronous modes of the EUSART. By default, the BRG operates in 8-bit mode; setting the BRG16 bit (BAUDCON<3>) selects 16-bit mode.

The SPBRGH:SPBRG register pair controls the period of a free running timer. In Asynchronous mode, bits BRGH (TXSTA<2>) and BRG16 (BAUDCON<3>) also control the baud rate. In Synchronous mode, BRGH is ignored. Table 19-1 shows the formula for computation of the baud rate for different EUSART modes which only apply in Master mode (internally generated clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRGH:SPBRG registers can be calculated using the formulas in Table 19-1. From this, the error in baud rate can be determined. An example calculation is shown in Example 19-1. Typical baud rates and error values for the various Asynchronous modes are shown in Table 19-2. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG to reduce the baud rate error, or achieve a slow baud rate for a fast oscillator frequency.

Writing a new value to the SPBRGH:SPBRG registers causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

| <b>Note:</b> A BRG value of 0 is not supported. |  |

|-------------------------------------------------|--|

|-------------------------------------------------|--|

#### 19.1.1 OPERATION IN POWER-MANAGED MODES

The device clock is used to generate the desired baud rate. When one of the power-managed modes is entered, the new clock source may be operating at a different frequency. This may require an adjustment to the value in the SPBRG register pair.

#### 19.1.2 SAMPLING

The data on the RX pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin when SYNC is clear or when BRG16 and BRGH are both not set. The data on the RX pin is sampled once when SYNC is set or when BRGH16 and BRGH are both set.

| Configuration Bits |       | its  |                     | Poud Poto Formula |  |

|--------------------|-------|------|---------------------|-------------------|--|

| SYNC               | BRG16 | BRGH | BRG/EUSART Mode     | Baud Rate Formula |  |

| 0                  | 0     | 0    | 8-bit/Asynchronous  | Fosc/[64 (n + 1)] |  |

| 0                  | 0     | 1    | 8-bit/Asynchronous  |                   |  |

| 0                  | 1     | 0    | 16-bit/Asynchronous | Fosc/[16 (n + 1)] |  |

| 0                  | 1     | 1    | 16-bit/Asynchronous |                   |  |

| 1                  | 0     | х    | 8-bit/Synchronous   | Fosc/[4 (n + 1)]  |  |

| 1                  | 1     | х    | 16-bit/Synchronous  |                   |  |

#### TABLE 19-1: BAUD RATE FORMULAS

**Legend:** x = Don't care, n = value of SPBRGH:SPBRG register pair

### 19.4 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTA<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any power-managed mode.

### 19.4.1 EUSART SYNCHRONOUS SLAVE TRANSMISSION

The operation of the Synchronous Master and Slave modes are identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREG register.

- c) Flag bit, TXIF, will not be set.

- When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit, TXIF, will now be set.

- e) If enable bit, TXIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If the signal from the CK pin is to be inverted, set the TXCKP bit.

- 5. If 9-bit transmission is desired, set bit, TX9.

- 6. Enable the transmission by setting enable bit, TXEN.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 8. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| TABLE 13-5. REGISTERS ASSOCIATED WITH STREEMONDOUS SERVE MANSMISSION |                                               |                                              |        |        |       |        |        |        |                            |

|----------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------|--------|--------|-------|--------|--------|--------|----------------------------|

| Name                                                                 | Bit 7                                         | Bit 6                                        | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

| INTCON                                                               | GIE/GIEH                                      | PEIE/GIEL                                    | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1                                                                 | PSPIF <sup>(1)</sup>                          | ADIF                                         | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1                                                                 | PSPIE <sup>(1)</sup>                          | ADIE                                         | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1                                                                 | PSPIP <sup>(1)</sup>                          | ADIP                                         | RCIP   | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                         |

| RCSTA                                                                | SPEN                                          | RX9                                          | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 57                         |

| TXREG                                                                | EUSART T                                      | EUSART Transmit Register                     |        |        |       |        |        |        |                            |

| TXSTA                                                                | CSRC                                          | TX9                                          | TXEN   | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 57                         |

| BAUDCON                                                              | ABDOVF                                        | RCIDL                                        | RXDTP  | TXCKP  | BRG16 | —      | WUE    | ABDEN  | 57                         |

| SPBRGH                                                               | EUSART Baud Rate Generator Register High Byte |                                              |        |        |       |        |        | 57     |                            |

| SPBRG                                                                | EUSART E                                      | EUSART Baud Rate Generator Register Low Byte |        |        |       |        |        |        |                            |

|                                                                      |                                               |                                              |        |        |       |        |        |        |                            |

# TABLE 19-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

## 20.2 Selecting and Configuring Acquisition Time

The ADCON2 register allows the user to select an acquisition time that occurs each time the GO/DONE bit is set. It also gives users the option to use an automatically determined acquisition time.

Acquisition time may be set with the ACQT<2:0> bits (ADCON2<5:3>), which provides a range of 2 to 20 TAD. When the GO/DONE bit is set, the A/D module continues to sample the input for the selected acquisition time, then automatically begins a conversion. Since the acquisition time is programmed, there may be no need to wait for an acquisition time between selecting a channel and setting the GO/DONE bit.

Manual acquisition is selected when ACQT<2:0> = 000. When the GO/DONE bit is set, sampling is stopped and a conversion begins. The user is responsible for ensuring the required acquisition time has passed between selecting the desired input channel and setting the GO/DONE bit. This option is also the default Reset state of the ACQT<2:0> bits and is compatible with devices that do not offer programmable acquisition times.

In either case, when the conversion is completed, the GO/DONE bit is cleared, the ADIF flag is set and the A/D begins sampling the currently selected channel again. If an acquisition time is programmed, there is nothing to indicate if the acquisition time has ended or if the conversion has begun.

# 20.3 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 11 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. There are seven possible options for TAD:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal RC Oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be as short as possible, but greater than the minimum TAD (see parameter 130 for more information).

Table 20-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

| AD Clock Sc       | ource (TAD) | Maximum Device Frequency |                                 |  |  |

|-------------------|-------------|--------------------------|---------------------------------|--|--|

| Operation         | ADCS<2:0>   | PIC18F2X21/4X21          | PIC18LF2X21/4X21 <sup>(4)</sup> |  |  |

| 2 Tosc            | 000         | 2.86 MHz                 | 1.43 kHz                        |  |  |

| 4 Tosc            | 100         | 5.71 MHz                 | 2.86 MHz                        |  |  |

| 8 Tosc            | 001         | 11.43 MHz                | 5.72 MHz                        |  |  |

| 16 Tosc           | 101         | 22.86 MHz                | 11.43 MHz                       |  |  |

| 32 Tosc           | 010         | 40.0 MHz                 | 22.86 MHz                       |  |  |

| 64 Tosc           | 110         | 40.0 MHz                 | 22.86 MHz                       |  |  |

| RC <sup>(3)</sup> | x11         | 1.00 MHz <sup>(1)</sup>  | 1.00 MHz <sup>(2)</sup>         |  |  |

### TABLE 20-1: TAD VS. DEVICE OPERATING FREQUENCIES

**Note 1:** The RC source has a typical TAD time of  $1.2 \ \mu$ s.

**2:** The RC source has a typical TAD time of 2.5  $\mu$ s.

- **3:** For device frequencies above 1 MHz, the device must be in Sleep for the entire conversion or the A/D accuracy may be out of specification.

- 4: Low-power (PIC18LFXXXX) devices only.

| RRNCF Rotate Right f (No Carry)                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |                |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------|--|--|

| Syntax:                                                                                                                          | RRNCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | f {,d {,a}}                                                     |                |  |  |

| Operands:                                                                                                                        | $0 \le f \le 255$<br>$d \in [0, 1]$<br>$a \in [0, 1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                 |                |  |  |

| Operation:                                                                                                                       | $(f < n >) \rightarrow c$<br>$(f < 0 >) \rightarrow c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | lest <n 1="" –="">,<br/>lest&lt;7&gt;</n>                       |                |  |  |

| Status Affected:                                                                                                                 | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                 |                |  |  |

| Encoding:                                                                                                                        | 0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 00da f                                                          | fff ffff       |  |  |

| Description:                                                                                                                     | The contents of register 'f' are rotated<br>one bit to the right. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If 'a' is '0', the Access Bank will be<br>selected, overriding the BSR value. If 'a'<br>is '1', then the bank will be selected as<br>per the BSR value (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                                                 |                |  |  |

|                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>regist</li> </ul>                                      | ter f          |  |  |

| Words:                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | regist                                                          | ter f          |  |  |

| Words:<br>Cvcles:                                                                                                                | 1<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ► regist                                                        | ter f          |  |  |

| Cycles:                                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ► regist                                                        | ler f          |  |  |

|                                                                                                                                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ► regist                                                        | ter f          |  |  |

| Cycles:<br>Q Cycle Activity:                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                 |                |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1                                                                                               | 1<br>Q2<br>Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q3<br>Process                                                   | Q4<br>Write to |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode                                                                                     | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Q3<br>Process<br>Data<br>REG, 1, 0<br>0111                      | Q4<br>Write to |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example 1:<br>Before Instruct<br>REG<br>After Instruction<br>REG                 | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101<br>on<br>= 1110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Q3<br>Process<br>Data<br>REG, 1, 0<br>0111<br>1011              | Q4<br>Write to |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example 1:<br>Before Instructor<br>REG<br>After Instruction<br>REG<br>Example 2: | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101<br>on<br>= 1110<br>RRNCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Q3<br>Process<br>Data<br>REG, 1, 0<br>0111<br>1011              | Q4<br>Write to |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example 1:<br>Before Instruct<br>REG<br>After Instruction<br>REG                 | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101<br>m<br>= 1110<br>RRNCF<br>tion<br>= ?<br>= 1101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Q3<br>Process<br>Data<br>REG, 1, 0<br>0111<br>1011<br>REG, 0, 0 | Q4<br>Write to |  |  |

| SETF                              | Set f                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                     |  |  |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|--|--|--|

| Syntax:                           | SETF f{,                                                                                                                                                   | a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                     |  |  |  |

| Operands:                         | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                     |  |  |  |

| Operation:                        | $FFh\tof$                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                     |  |  |  |

| Status Affected:                  | None                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                     |  |  |  |

| Encoding:                         | 0110                                                                                                                                                       | 100a :                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ffff | ffff                |  |  |  |

| Description:                      | are set to F<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank<br>If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode wher<br>Section 25<br>Bit-Oriente | The contents of the specified register<br>are set to FFh.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |      |                     |  |  |  |

| Words:                            | 1                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                     |  |  |  |

| Cycles:                           | 1                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                     |  |  |  |

| Q Cycle Activity:                 |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                     |  |  |  |

| Q1                                | Q2                                                                                                                                                         | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | Q4                  |  |  |  |

| Decode                            | Read<br>register 'f'                                                                                                                                       | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | Write<br>gister 'f' |  |  |  |

| Example:<br>Before Instruc<br>REG | SETF<br>tion<br>= 5A                                                                                                                                       | REG,                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1    |                     |  |  |  |

| REG               | = | 5Ah |

|-------------------|---|-----|

| After Instruction |   |     |

| REG               | = | FFh |

| SLE                                           | EP             | Enter Sle                                                                                                                 | ep mode                                                                                                  |                                          | SU                         | BFWB                                          | Subtract                                                                       | f from W w                                               | ith Borrow                                                       |

|-----------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------|-----------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------|

| Synta                                         | ax:            | SLEEP                                                                                                                     |                                                                                                          |                                          | Syr                        | ntax:                                         | SUBFWB                                                                         | f {,d {,a}}                                              |                                                                  |

| Oper                                          | ands:          | None                                                                                                                      |                                                                                                          |                                          | Op                         | erands:                                       | $0 \le f \le 255$                                                              | i                                                        |                                                                  |

| Oper                                          | ation:         | $00h \rightarrow WE$                                                                                                      | DT,                                                                                                      |                                          |                            |                                               | d ∈ [0,1]<br>a ∈ [0,1]                                                         |                                                          |                                                                  |

|                                               |                | $0 \rightarrow \frac{\text{WDT}}{\text{TO}}$ , postscaler,<br>$1 \rightarrow \overline{\text{TO}}$ ,                      |                                                                                                          | On                                       | eration:                   | $(W) - (f) - (\overline{C}) \rightarrow dest$ |                                                                                |                                                          |                                                                  |

|                                               |                | $\begin{array}{c} 1 \rightarrow \overline{PD} \\ 0 \rightarrow \overline{PD} \\ \overline{TO}, \overline{PD} \end{array}$ |                                                                                                          |                                          | tus Affected:              | N, OV, C, DC, Z                               |                                                                                |                                                          |                                                                  |

| Statu                                         | s Affected:    |                                                                                                                           |                                                                                                          |                                          | Encoding:                  |                                               | 01da ff                                                                        | ff ffff                                                  |                                                                  |

| Enco                                          | ding:          | 0000 0000 0000 0011                                                                                                       |                                                                                                          |                                          | scription:                 | 0101<br>Subtract re                           | egister 'f' and C                                                              |                                                          |                                                                  |

| Description:                                  |                | cleared. T<br>is set. Wat<br>postscaler<br>The proce                                                                      | r-Down status<br>he Time-out st<br>chdog Timer a<br>are cleared.<br>ssor is put into<br>scillator stoppe | atus bit (TO)<br>and its<br>o Sleep mode | De                         | сприон.                                       | (borrow) fr<br>method). If<br>in W. If 'd'<br>register 'f'<br>If 'a' is '0', ' | om W (2's com<br>'d' is '0', the re<br>is '1', the resul | nplement<br>esult is stored<br>t is stored in<br>nk is selected. |

| Word                                          | ls:            | 1                                                                                                                         |                                                                                                          |                                          |                            |                                               | GPR bank                                                                       | (default).<br>and the extend                             | ad instruction                                                   |

| Cycles: 1                                     |                |                                                                                                                           |                                                                                                          |                                          | led, this instru           |                                               |                                                                                |                                                          |                                                                  |

| QC                                            | ycle Activity: |                                                                                                                           |                                                                                                          |                                          |                            |                                               | in Indexed                                                                     | Literal Offset A                                         | Addressing                                                       |

|                                               | Q1             | Q2                                                                                                                        | Q3                                                                                                       | Q4                                       |                            |                                               |                                                                                | never f ≤ 95 (5<br>5.2.3 "Byte-Or                        | ,                                                                |

|                                               | Decode         | No<br>operation                                                                                                           | Process<br>Data                                                                                          | Go to<br>Sleep                           |                            |                                               | Bit-Orient                                                                     | ed Instruction<br>set Mode" for                          | is in Indexed                                                    |

| _                                             |                |                                                                                                                           |                                                                                                          |                                          | Wo                         | rds:                                          | 1                                                                              |                                                          |                                                                  |

| Example: SLEEP                                |                | Сус                                                                                                                       | cles:                                                                                                    | 1                                        |                            |                                               |                                                                                |                                                          |                                                                  |

| Before Instruction<br>$\overline{TO} = ?$     |                |                                                                                                                           | Q                                                                                                        | Cycle Activity:                          |                            |                                               |                                                                                |                                                          |                                                                  |

| $\frac{10}{PD} = ?$                           |                |                                                                                                                           | Q1                                                                                                       | Q2                                       | Q3                         | Q4                                            |                                                                                |                                                          |                                                                  |

| After Instruction                             |                |                                                                                                                           |                                                                                                          | Decode                                   | Read                       | Process                                       | Write to                                                                       |                                                          |                                                                  |

| $\frac{\overline{TO}}{PD} = 0$                |                |                                                                                                                           |                                                                                                          |                                          | register 'f'               | Data                                          | destination                                                                    |                                                          |                                                                  |

|                                               |                |                                                                                                                           |                                                                                                          |                                          | Exa                        | ample 1:<br>Defens lastru                     | SUBFWB                                                                         | REG, 1, 0                                                |                                                                  |

| † If WDT causes wake-up, this bit is cleared. |                |                                                                                                                           |                                                                                                          | Before Instruc<br>REG<br>W<br>C          | ction<br>= 3<br>= 2<br>= 1 |                                               |                                                                                |                                                          |                                                                  |

After Instruction

REG

**Before Instruction** REG W

W

C Z N

С

After Instruction

REG W C Z N

**Before Instruction** REG W

After Instruction REG = W = C = Z = N =

С

Example 2:

Example 3:

FF 2 0

0 1 = =

2 5 = = 1

2 3 1 = = = = 0 = 0

SUBFWB

1 2 0

SUBFWB

; result is negative

; result is positive

; result is zero

REG, 1, 0

REG, 0, 0

=

=

=

=

= =

=

| ADDWF                                                          | ADD W to<br>(Indexed                                                                                                                                                                                                  |                            |   | ode)                  |  |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---|-----------------------|--|

| Syntax:                                                        | ADDWF                                                                                                                                                                                                                 | [k] {,d}                   |   |                       |  |

| Operands:                                                      | $\begin{array}{l} 0 \leq k \leq 95 \\ d  \in  [0,1] \end{array}$                                                                                                                                                      |                            |   |                       |  |

| Operation:                                                     | (W) + ((FSR2) + k) $\rightarrow$ dest                                                                                                                                                                                 |                            |   |                       |  |