### Microchip Technology - PIC18F2221-I/SO Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2221-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

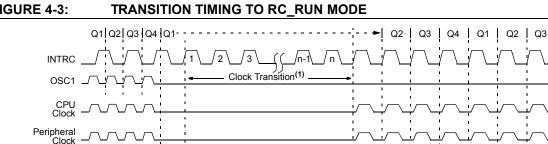

#### 4.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator block using the INTOSC multiplexer. In this mode, the primary clock is shut down. When using the INTRC source, this mode provides the best power conservation of all the Run modes, while still executing code. It works well for user applications which are not highly timing sensitive or do not require high-speed clocks at all times.

If the primary clock source is the internal oscillator block (either INTRC or INTOSC), there are no distinguishable differences between PRI\_RUN and RC\_RUN modes during execution. However, a clock switch delay will occur during entry to and exit from RC\_RUN mode. Therefore, if the primary clock source is the internal oscillator block, the use of RC\_RUN mode is not recommended. This mode is entered by setting the SCS1 bit to '1'. Although it is ignored, it is recommended that the SCS0 bit also be cleared; this is to maintain software compatibility with future devices. When the clock source is switched to the INTOSC multiplexer (see Figure 4-3), the primary oscillator is shut down and the OSTS bit is cleared. The IRCF bits may be modified at any time to immediately change the clock speed.

| Note: | Caution should be used when modifying a        |  |  |  |  |  |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | single IRCF bit. If VDD is less than 3V, it is |  |  |  |  |  |  |  |  |  |  |

|       | possible to select a higher clock speed        |  |  |  |  |  |  |  |  |  |  |

|       | than is supported by the low VDD.              |  |  |  |  |  |  |  |  |  |  |

|       | Improper device operation may result if        |  |  |  |  |  |  |  |  |  |  |

|       | the VDD/FOSC specifications are violated.      |  |  |  |  |  |  |  |  |  |  |

© 2009 Microchip Technology Inc.

If the IRCF bits and the INTSRC bit are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear; there will be no indication of the current clock source. The INTRC source is providing the device clocks.

If the IRCF bits are changed from all clear (thus, enabling the INTOSC output) or if INTSRC is set, the IOFS bit becomes set after the INTOSC output becomes stable. Clocks to the device continue while the INTOSC source stabilizes after an interval of TIOBST (parameter 39, Table 27-10).

If the IRCF bits were previously at a non-zero value, or if INTSRC was set before setting SCS1 and the INTOSC source was already stable, the IOFS bit will remain set.

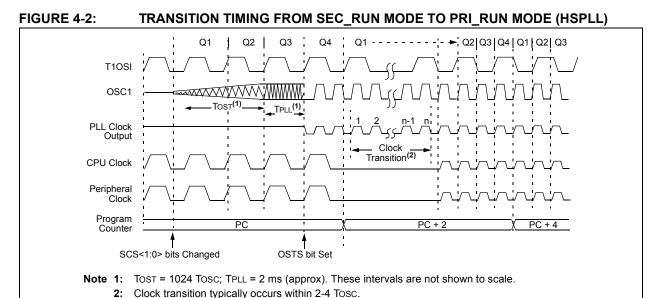

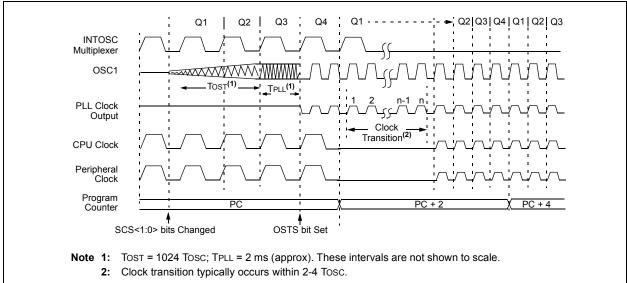

On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

PC + 4

#### FIGURE 4-3:

Note 1: Clock transition typically occurs within 2-4 Tosc.

Program Counter

PC

#### FIGURE 4-4: TRANSITION TIMING FROM RC RUN MODE TO PRI RUN MODE

PC + 2

| <b>REGISTER 7-1:</b> | EECON1:                                                                                                                                                                                                                                                                                                            | DATA EEF                     | ROM CO                      | NTROL RE                                      | GISTER 1      |               |              |            |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------|-----------------------------------------------|---------------|---------------|--------------|------------|--|

|                      | R/W-x                                                                                                                                                                                                                                                                                                              | R/W-x                        | U-0                         | R/W-0                                         | R/W-x         | R/W-0         | R/S-0        | R/S-0      |  |

|                      | EEPGD                                                                                                                                                                                                                                                                                                              | CFGS                         | —                           | FREE                                          | WRERR         | WREN          | WR           | RD         |  |

|                      | bit 7                                                                                                                                                                                                                                                                                                              |                              |                             |                                               | · · · · ·     |               |              | bit 0      |  |

| bit 7                | EEPGD: FI                                                                                                                                                                                                                                                                                                          | lash Prograr                 | n or Data E                 | EPROM Mei                                     | mory Select   | bit           |              |            |  |

|                      | 1 = Access                                                                                                                                                                                                                                                                                                         | s Flash prog<br>s data EEPF  | ram memor                   | тy                                            | 2             |               |              |            |  |

| bit 6                | CFGS: Flag                                                                                                                                                                                                                                                                                                         | sh Program/                  | Data EEPR                   | OM or Confi                                   | iguration Sel | lect bit      |              |            |  |

|                      |                                                                                                                                                                                                                                                                                                                    | s Configurat<br>s Flash prog | •                           | s<br>I EEPROM n                               | nemory        |               |              |            |  |

| bit 5                | Unimplem                                                                                                                                                                                                                                                                                                           | ented: Read                  | <b>d as</b> '0'             |                                               |               |               |              |            |  |

| bit 4                | <ul> <li>FREE: Flash Row Erase Enable bit</li> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command (cleared by completion of erase operation)</li> <li>0 = Perform write-only</li> </ul>                                                                                               |                              |                             |                                               |               |               |              |            |  |

| bit 3                | 1 = A write<br>normal                                                                                                                                                                                                                                                                                              | e operation i                | s premature<br>or an improj | PROM Error<br>ely terminate<br>per write atte | d (any Rese   | t during selt | f-timed prog | ramming in |  |

|                      | Note:                                                                                                                                                                                                                                                                                                              |                              |                             | rs, the EEPO<br>he error con                  |               | S bits are n  | ot cleared.  |            |  |

| bit 2                | 1 = Allows                                                                                                                                                                                                                                                                                                         | write cycles                 | s to Flash pr               | ROM Write E<br>rogram/data<br>rogram/data     | EEPROM        |               |              |            |  |

| bit 1                | WR: Write                                                                                                                                                                                                                                                                                                          | Control bit                  |                             |                                               |               |               |              |            |  |

|                      | <ul> <li>1 = Initiates a data EEPROM erase/write cycle or a program memory erase/write cycle.<br/>(The operation is self-timed and the bit is cleared by hardware once write is complete.<br/>The WR bit can only be set (not cleared) in software.)</li> <li>0 = Write cycle to the EEPROM is complete</li> </ul> |                              |                             |                                               |               |               |              |            |  |

| bit 0                | RD: Read (                                                                                                                                                                                                                                                                                                         | Control bit                  |                             |                                               |               |               |              |            |  |

|                      | <ul> <li>1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only be set (not cleared) in software. RD bit cannot be set when EEPGD = 1 or CFGS = 1.)</li> <li>0 = Does not initiate an EEPROM read</li> </ul>                                                           |                              |                             |                                               |               |               |              |            |  |

|                      | Legend:                                                                                                                                                                                                                                                                                                            |                              |                             |                                               |               |               |              |            |  |

|                      | R = Reada                                                                                                                                                                                                                                                                                                          | ble bit                      | W = M                       | /ritable bit                                  |               |               |              |            |  |

|                      |                                                                                                                                                                                                                                                                                                                    |                              |                             | not cleared                                   | U = Unim      | plemented     | bit, read as | ʻ0'        |  |

|                      |                                                                                                                                                                                                                                                                                                                    |                              |                             |                                               |               |               | ,            |            |  |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

### 8.5 Operation During Code-Protect

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

The microcontroller itself can both read and write to the internal data EEPROM, regardless of the state of the code-protect Configuration bit. Refer to Section 24.0 "Special Features of the CPU" for additional information.

### 8.6 Protection Against Spurious Write

To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT, parameter 33).

The write initiate sequence and the WREN bit together help prevent an accidental write during Brown-out Reset, power glitch or software malfunction.

### 8.7 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing data. Such data is typically updated at least one time within the number of writes defined by specification, D124. If any location storing data is not written at least this often, the data EEPROM array must be refreshed. For this reason, values that change infrequently, or not at all, should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 8-3.

**Note:** If data EEPROM is only used to store constants and/or data that changes often, an array refresh is likely not required. See specification, D124.

| EXAMPLE 8-3: | DATA EEPROM REFRESH ROUTINE |

|--------------|-----------------------------|

|--------------|-----------------------------|

|      |        | DATA EEL KG   |                              |

|------|--------|---------------|------------------------------|

|      | CLRF   | EEADR         | ; Start at address 0         |

|      | BCF    | EECON1, CFGS  | ; Set for memory             |

|      | BCF    | EECON1, EEPGD | ; Set for Data EEPROM        |

|      | BCF    | INTCON, GIE   | ; Disable interrupts         |

|      | BSF    | EECON1, WREN  | ; Enable writes              |

| LOOP |        |               | ; Loop to refresh array      |

|      | BSF    | EECON1, RD    | ; Read current address       |

|      | MOVLW  | 55h           | ;                            |

|      | MOVWF  | EECON2        | ; Write 55h                  |

|      | MOVLW  | 0AAh          | ;                            |

|      | MOVWF  | EECON2        | ; Write OAAh                 |

|      | BSF    | EECON1, WR    | ; Set WR bit to begin write  |

|      | BTFSC  | EECON1, WR    | ; Wait for write to complete |

|      | BRA    | \$-2          |                              |

|      | INCFSZ | EEADR, F      | ; Increment address          |

|      | BRA    | LOOP          | ; Not zero, do it again      |

|      | BCF    | EECON1, WREN  | ; Disable writes             |

|      | BSF    | INTCON, GIE   | ; Enable interrupts          |

| 1    |        |               |                              |

### 12.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

#### 12.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

### 12.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name   | Bit 7                                                         | Bit 6                    | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on page |  |  |  |

|--------|---------------------------------------------------------------|--------------------------|--------|--------|-------|--------|--------|-------|----------------------------|--|--|--|

| TMR0L  | Timer0 Reg                                                    | Timer0 Register Low Byte |        |        |       |        |        |       |                            |  |  |  |

| TMR0H  | Timer0 Reg                                                    | ister High By            | /te    |        |       |        |        |       | 56                         |  |  |  |

| INTCON | GIE/GIEH                                                      | PEIE/GIEL                | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 55                         |  |  |  |

| TOCON  | TMR0ON T08BIT T0CS T0SE PSA T0PS2 T0PS1 T0PS0                 |                          |        |        |       |        |        |       |                            |  |  |  |

| TRISA  | RA7 <sup>(1)</sup> RA6 <sup>(1)</sup> RA5 RA4 RA3 RA2 RA1 RA0 |                          |        |        |       |        |        |       | 58                         |  |  |  |

TABLE 12-1:

REGISTERS ASSOCIATED WITH TIMER0

Legend: Shaded cells are not used by Timer0.

**Note 1:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

NOTES:

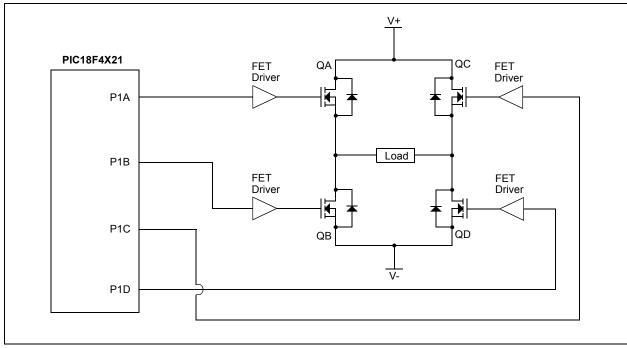

### FIGURE 17-7: EXAMPLE OF FULL-BRIDGE APPLICATION

### 17.4.5.1 Direction Change in Full-Bridge Mode

In the Full-Bridge Output mode, the P1M1 bit in the CCP1CON register allows user to control the forward/ reverse direction. When the application firmware changes this direction control bit, the module will assume the new direction on the next PWM cycle.

Just before the end of the current PWM period, the modulated outputs (P1B and P1D) are placed in their inactive state, while the unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction. This occurs in a time interval of 4 Tosc \* (Timer2 Prescale Value) before the next PWM period begins. The Timer2 prescaler will be either 1, 4 or 16, depending on the value of the T2CKPS<1:0> bits (T2CON<1:0>). During the interval from the switch of the unmodulated outputs to the beginning of the next period, the modulated outputs (P1B and P1D) remain inactive. This relationship is shown in Figure 17-8.

Note that in the Full-Bridge Output mode, the ECCP1 module does not provide any dead-band delay. In general, since only one output is modulated at all times, dead-band delay is not required. However, there is a situation where a dead-band delay might be required. This situation occurs when both of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

Figure 17-9 shows an example where the PWM direction changes from forward to reverse at a near 100% duty cycle. At time t1, the outputs P1A and P1D become inactive, while output P1C becomes active. In this example, since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current may flow through power devices, QC and QD (see Figure 17-7), for the duration of 't'. The same phenomenon will occur to power devices, QA and QB, for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, one of the following requirements must be met:

- 1. Reduce PWM for a PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

### 17.4.9 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP module for PWM operation:

- 1. Configure the PWM pins, P1A and P1B (and P1C and P1D, if used), as inputs by setting the corresponding TRIS bits.

- 2. Set the PWM period by loading the PR2 register.

- 3. If auto-shutdown is required, do the following:

- Disable auto-shutdown (ECCPASE = 0)

- Configure source (FLT0, Comparator 1 or Comparator 2)

- Wait for non-shutdown condition

- Configure the ECCP module for the desired PWM mode and configuration by loading the CCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the P1M<1:0 bits.

- Select the polarities of the PWM output signals with the CCP1M<3:0> bits.

- 5. Set the PWM duty cycle by loading the CCPR1L register and CCP1CON<5:4> bits.

- 6. For Half-Bridge Output mode, set the deadband delay by loading ECCP1DEL<6:0> with the appropriate value.

- 7. If auto-shutdown operation is required, load the ECCP1AS register:

- Select the auto-shutdown sources using the ECCPAS<2:0> bits.

- Select the shutdown states of the PWM output pins using the PSSAC<1:0> and PSSBD<1:0> bits.

- Set the ECCPASE bit (ECCP1AS<7>).

- Configure the comparators using the CMCON register.

- Configure the comparator inputs as analog inputs.

- 8. If auto-restart operation is required, set the PRSEN bit (ECCP1DEL<7>).

- 9. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit (PIR1<1>).

- Set the TMR2 prescale value by loading the T2CKPS bits (T2CON<1:0>).

- Enable Timer2 by setting the TMR2ON bit (T2CON<2>).

- 10. Enable PWM outputs after a new PWM cycle has started:

- Wait until TMRx overflows (TMRxIF bit is set).

- Enable the CCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- Clear the ECCPASE bit (ECCP1AS<7>).

### 17.4.10 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the ECCP pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from INTOSC and the postscaler may not be stable immediately.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCP module without change. In all other power-managed modes, the selected power-managed mode clock will clock Timer2. Other power-managed mode clocks will most likely be different than the primary clock frequency.

#### 17.4.10.1 Operation with Fail-Safe Clock Monitor

If the Fail-Safe Clock Monitor is enabled, a clock failure will force the device into the power-managed RC\_RUN mode and the OSCFIF bit (PIR2<7>) will be set. The ECCP will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

See the previous section for additional details.

### 17.4.11 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the CCP registers to their Reset states.

This forces the Enhanced CCP module to reset to a state compatible with the standard CCP module.

| FIGURE 18-5:                                                      | SPI N                 | IODE W      | /AVEFO                                       | RM (SL                | AVE MC                | DE WIT      | H CKE :               | = 0)                                          |   |                                  |            |

|-------------------------------------------------------------------|-----------------------|-------------|----------------------------------------------|-----------------------|-----------------------|-------------|-----------------------|-----------------------------------------------|---|----------------------------------|------------|

| -<br>SS<br>Opäend                                                 | •<br>•<br>•           |             |                                              |                       |                       |             |                       |                                               |   |                                  | <br>       |

| 90X<br>(CRP = 0<br>(CRS = 0)                                      |                       |             |                                              |                       |                       |             |                       |                                               |   |                                  |            |

| 497°Z                                                             | :<br>4                |             | ·<br>·<br>·                                  | ·<br>·<br>·           |                       | ·<br>·      |                       | ·<br>:<br>: ······                            |   |                                  | 3<br>3<br> |

| (CR49 + 1<br>CY48 + 0)                                            | :<br>:<br>:           |             |                                              |                       |                       |             |                       |                                               |   |                                  |            |

| VARA IN<br>SSPRUF                                                 |                       | •           | 2<br>2<br>2<br>2                             | :<br>:<br>:<br>:      | e<br>Garana<br>E<br>E | •           | 2<br>2<br>2           | ·<br>                                         | ( |                                  | *<br>      |

| 9870                                                              |                       | K 158 V     | <br>X                                        | X 58.6                |                       | ×68.3       | X 68.0                |                                               |   | <u>(3</u> 3-6)                   |            |

| 809<br>(9849 = 0)                                                 | ·<br>·<br>·<br>·<br>· |             |                                              | dijijijijiji          |                       |             |                       |                                               |   |                                  | *<br>1<br> |

| inguja<br>Samagoiae                                               | -<br>-<br>-<br>       |             | ,<br>, , , , , , , , , , , , , , , , , , ,   | . 49.                 |                       |             |                       |                                               |   | <i>a</i> .                       |            |

| (53492 == 0)<br>(5359292<br>============<br>===================== | :<br>:<br>:           |             | -<br>5<br>5<br>5<br>5                        | e<br>•<br>•<br>•<br>• | -<br>5<br>5<br>6<br>6 | :<br>:      | ·<br>5<br>5<br>5<br>5 | ,<br>,<br>;<br>;                              |   | Next ()                          |            |

| SSPSR 5<br>SSPSRF                                                 | ,<br>,<br>6           | •<br>•<br>• | )<br>)<br>////////////////////////////////// | :<br>:<br>            | t<br>t<br>5           | •<br>•<br>• | )<br>;<br>,           | :<br>:<br>· · · · · · · · · · · · · · · · · · |   | 2002 (22<br>2022 (22<br>2023 (22 |            |

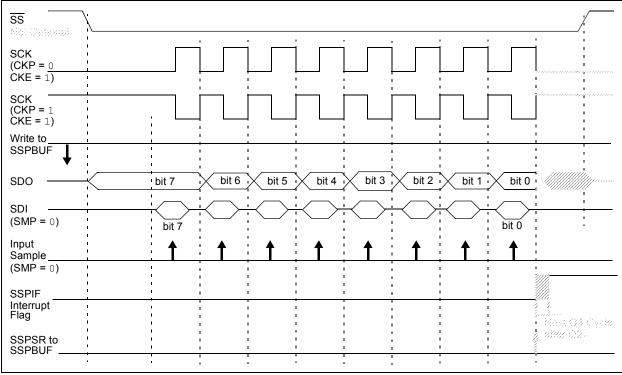

### FIGURE 18-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

| REGISTER 20-3: | ADCON2:                                                                                                      | A/D CONT                                                                                  | ROL REG                                    | ISTER 2     |                                                           |              |                |            |

|----------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------|-------------|-----------------------------------------------------------|--------------|----------------|------------|

|                | R/W-0                                                                                                        | U-0                                                                                       | R/W-0                                      | R/W-0       | R/W-0                                                     | R/W-0        | R/W-0          | R/W-0      |

|                | ADFM                                                                                                         | _                                                                                         | ACQT2                                      | ACQT1       | ACQT0                                                     | ADCS2        | ADCS1          | ADCS0      |

|                | bit 7                                                                                                        |                                                                                           |                                            |             |                                                           |              |                | bit 0      |

| bit 7          | ADFM: A/D                                                                                                    | Result For                                                                                | mat Select b                               | bit         |                                                           |              |                |            |

|                | 1 = Right ju<br>0 = Left jus                                                                                 |                                                                                           |                                            |             |                                                           |              |                |            |

| bit 6          | Unimplem                                                                                                     | ented: Read                                                                               | <b>d as</b> '0'                            |             |                                                           |              |                |            |

| bit 5-3        | ACQT<2:0                                                                                                     | >: A/D Acqu                                                                               | isition Time                               | Select bits |                                                           |              |                |            |

|                | 111 = 20 T<br>110 = 16 T<br>101 = 12 T<br>100 = 8 TA<br>011 = 6 TA<br>010 = 4 TA<br>001 = 2 TA<br>000 = 0 TA | AD<br>AD<br>D<br>D<br>D<br>D                                                              |                                            |             |                                                           |              |                |            |

| bit 2-0        | 111 = FRC<br>110 = FOS<br>101 = FOS<br>010 = FOS<br>011 = FRC<br>010 = FOS<br>001 = FOS                      | (clock deriv<br>c/64<br>c/16<br>c/4<br>(clock deriv<br>c/32<br>c/8<br>c/2<br>If the A/D I | ed from A/D<br>ed from A/D<br>FRC clock so |             | or) <sup>(1)</sup><br>or) <sup>(1)</sup><br>ected, a dela |              | CY (instructio |            |

|                | Lagand                                                                                                       |                                                                                           | re the A/D c<br>ting a conve               |             | his allows th                                             | ne SLEEP in: | struction to b | e executed |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The value in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see **Section 20.1 "A/D Acquisition Requirements"**. After this acquisition time has elapsed, the A/D conversion can be started. An acquisition time can be programmed to occur between setting the GO/DONE bit and the actual start of the conversion.

The following steps should be followed to perform an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins, voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D acquisition time (ADCON2)

- Select A/D conversion clock (ADCON2)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set GIE bit

- 3. Wait the required acquisition time (if required).

- 4. Start conversion:

- Set GO/DONE bit (ADCON0 register)

5. Wait for A/D conversion to complete, by either:

### • Polling for the GO/DONE bit to be cleared OR

• Waiting for the A/D interrupt

- 6. Read A/D Result registers (ADRESH:ADRESL); clear bit ADIF, if required.

- 7. For next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before the next acquisition starts.

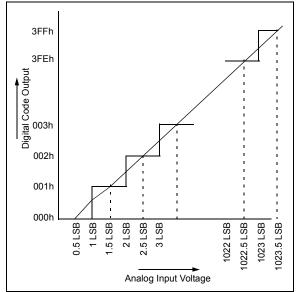

#### FIGURE 20-2: A/D TRANSFER FUNCTION

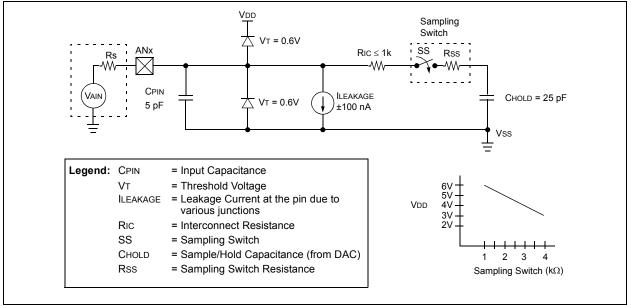

### FIGURE 20-3: ANALOG INPUT MODEL

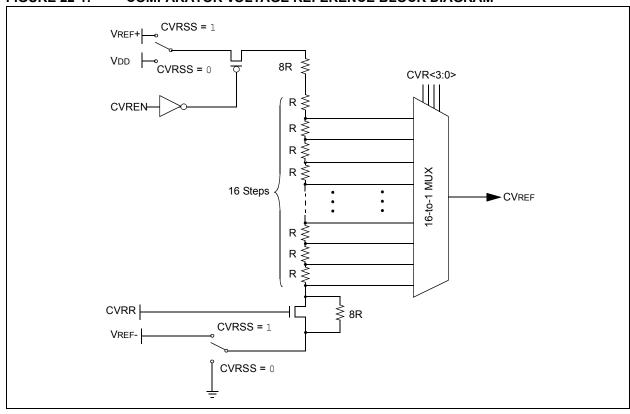

### FIGURE 22-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

### 22.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 22-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in **Section 27.0 "Electrical Characteristics"**.

### 22.3 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

### 22.4 Effects of a Reset

A device Reset disables the voltage reference by clearing bit, CVREN (CVRCON<7>). This Reset also disconnects the reference from the RA2 pin by clearing bit, CVROE (CVRCON<6>) and selects the high-voltage range by clearing bit, CVRR (CVRCON<5>). The CVR value select bits are also cleared.

### 22.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the CVROE bit is set. Enabling the voltage reference output onto RA2 when it is configured as a digital input will increase current consumption. Connecting RA2 as a digital output with CVRSS enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. Figure 22-2 shows an example buffering technique.

| CLRF                                                | Clear f                                                               |                           |                                    | CLRWDT          | Clear Wat                                                    | tchdog Time                         | er          |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------|---------------------------|------------------------------------|-----------------|--------------------------------------------------------------|-------------------------------------|-------------|--|--|--|--|

| Syntax:                                             | CLRF f{,a                                                             | }                         |                                    | Syntax:         | Syntax: CLRWDT                                               |                                     |             |  |  |  |  |

| Operands:                                           | $0 \leq f \leq 255$                                                   |                           |                                    | Operands:       | None                                                         | None                                |             |  |  |  |  |

|                                                     | <b>a</b> ∈[0,1]                                                       |                           |                                    | Operation:      | $000h \rightarrow Wl$                                        | ,                                   |             |  |  |  |  |

| Operation:                                          | $\begin{array}{l} 000h \rightarrow f, \\ 1 \rightarrow Z \end{array}$ |                           |                                    |                 | $000h \rightarrow WI$ $1 \rightarrow TO,$ $1 \rightarrow PD$ | OT postscaler,                      |             |  |  |  |  |

| Status Affected:                                    | Z                                                                     |                           |                                    | Status Affected |                                                              |                                     |             |  |  |  |  |

| Encoding:                                           | 0110                                                                  | 101a fff                  | ff ffff                            |                 |                                                              |                                     | 0.0 0.1 0.0 |  |  |  |  |

| Description:                                        |                                                                       | ontents of the            | specified                          | Encoding:       | 0000                                                         | 0000 00                             |             |  |  |  |  |

|                                                     | lf 'a' is '1', th<br>GPR bank (o                                      | e BSR is use<br>default). | nk is selected.<br>d to select the | Description:    |                                                              | on resets the<br>It also resets the |             |  |  |  |  |

|                                                     |                                                                       | d the extende             |                                    | Words:          | 1                                                            |                                     |             |  |  |  |  |

|                                                     |                                                                       | iteral Offset A           | tion operates                      | Cycles:         | 1                                                            |                                     |             |  |  |  |  |

|                                                     |                                                                       | ever f ≤ 95 (5F           | 0                                  | Q Cycle Activit | v:                                                           |                                     |             |  |  |  |  |

|                                                     |                                                                       | 2.3 "Byte-Ori             |                                    | Q1              | Q2                                                           | Q3                                  | Q4          |  |  |  |  |

|                                                     |                                                                       | et Mode" for              |                                    | Decode          |                                                              | Process                             | No          |  |  |  |  |

| Words:                                              | 1                                                                     |                           |                                    |                 | operation                                                    | Data                                | operation   |  |  |  |  |

| Cycles:                                             | 1                                                                     |                           |                                    | Example:        | CLRWDT                                                       |                                     |             |  |  |  |  |

| Q Cycle Activity:                                   |                                                                       |                           |                                    | Before Ins      |                                                              |                                     |             |  |  |  |  |

| Q1                                                  | Q2                                                                    | Q3                        | Q4                                 |                 | Counter =                                                    | ?                                   |             |  |  |  |  |

| Decode                                              | Read<br>register 'f'                                                  | Process<br>Data           | Write<br>register 'f'              |                 | uction<br>Counter =<br>Postscaler =                          | 00h<br>0                            |             |  |  |  |  |

| Example:                                            | CLRF                                                                  | FLAG_REG,                 | 1                                  | TO<br>PD        | =                                                            | 1<br>1                              |             |  |  |  |  |

| Before Instru<br>FLAG_F<br>After Instruct<br>FLAG_F | REG = 5Ah<br>on                                                       |                           |                                    |                 |                                                              |                                     |             |  |  |  |  |

| SLE                                                                                                                                                                                                                                                                    | EP                             | Enter Sle                                                         | ep mode         |                | SU           | BFWB                                                                           | Subtract                                                 | f from W w                                                       | ith Borrow     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------|-----------------|----------------|--------------|--------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------|----------------|

| Synta                                                                                                                                                                                                                                                                  | ax:                            | SLEEP                                                             |                 |                | Syr          | ntax:                                                                          | SUBFWB                                                   | f {,d {,a}}                                                      |                |

| Oper                                                                                                                                                                                                                                                                   | ands:                          | None                                                              |                 |                | Op           | erands:                                                                        | $0 \le f \le 255$                                        | i                                                                |                |

| Oper                                                                                                                                                                                                                                                                   | ation: $00h \rightarrow WDT$ , |                                                                   |                 |                |              |                                                                                | d ∈ [0,1]<br>a ∈ [0,1]                                   |                                                                  |                |

|                                                                                                                                                                                                                                                                        |                                | $0 \rightarrow \underline{WDT}$<br>$1 \rightarrow \overline{TO},$ | postscaler,     |                | On           | eration:                                                                       |                                                          | $(\overline{C}) \rightarrow dest$                                |                |

|                                                                                                                                                                                                                                                                        |                                | $1 \rightarrow \frac{10}{PD}$                                     |                 |                |              | tus Affected:                                                                  | (W) = (I) =<br>N, OV, C,                                 |                                                                  |                |

| Statu                                                                                                                                                                                                                                                                  | s Affected:                    | TO, PD                                                            |                 |                |              | coding:                                                                        | 0101                                                     | 01da ff                                                          | ff ffff        |

| Enco                                                                                                                                                                                                                                                                   | ding:                          | 0000                                                              | 0000 000        | 0 0011         |              | scription:                                                                     |                                                          | egister 'f' and C                                                |                |

| Encoding:       0000       0000       0011         Description:       The Power-Down status bit (PD) is cleared. The Time-out status bit (TO) is set. Watchdog Timer and its postscaler are cleared. The processor is put into Sleep mode with the oscillator stopped. |                                |                                                                   |                 | De             | сприон.      | (borrow) fr<br>method). If<br>in W. If 'd'<br>register 'f'<br>If 'a' is '0', ' | om W (2's com<br>'d' is '0', the re<br>is '1', the resul | nplement<br>esult is stored<br>t is stored in<br>nk is selected. |                |

| Word                                                                                                                                                                                                                                                                   | ls:                            | 1                                                                 |                 |                |              |                                                                                | GPR bank                                                 | (default).<br>and the extend                                     | ad instruction |

| Cycle                                                                                                                                                                                                                                                                  | es:                            | 1                                                                 |                 |                |              |                                                                                |                                                          | led, this instru                                                 |                |

| QC                                                                                                                                                                                                                                                                     | ycle Activity:                 |                                                                   |                 |                |              |                                                                                | in Indexed                                               | Literal Offset A                                                 | Addressing     |

|                                                                                                                                                                                                                                                                        | Q1                             | Q2                                                                | Q3              | Q4             |              |                                                                                |                                                          | never f ≤ 95 (5<br>5.2.3 "Byte-Or                                | ,              |

|                                                                                                                                                                                                                                                                        | Decode                         | No<br>operation                                                   | Process<br>Data | Go to<br>Sleep |              |                                                                                | Bit-Orient                                               | ed Instruction<br>set Mode" for                                  | is in Indexed  |

| _                                                                                                                                                                                                                                                                      |                                |                                                                   |                 |                | Wo           | rds:                                                                           | 1                                                        |                                                                  |                |

| Exan                                                                                                                                                                                                                                                                   |                                | SLEEP                                                             |                 |                | Сус          | cles:                                                                          | 1                                                        |                                                                  |                |

|                                                                                                                                                                                                                                                                        | Before Instruc<br>TO =         | tion<br>?                                                         |                 |                | Q            | Cycle Activity:                                                                |                                                          |                                                                  |                |

|                                                                                                                                                                                                                                                                        | $\frac{10}{PD} =$              | ?                                                                 |                 |                |              | Q1                                                                             | Q2                                                       | Q3                                                               | Q4             |

|                                                                                                                                                                                                                                                                        | After Instruction              |                                                                   |                 |                |              | Decode                                                                         | Read                                                     | Process                                                          | Write to       |

|                                                                                                                                                                                                                                                                        | $\frac{TO}{PD} = 0$            |                                                                   |                 |                | register 'f' | Data                                                                           | destination                                              |                                                                  |                |

|                                                                                                                                                                                                                                                                        |                                | U U                                                               |                 |                | Exa          | ample 1:<br>Defens lastru                                                      | SUBFWB                                                   | REG, 1, 0                                                        |                |

| † If                                                                                                                                                                                                                                                                   | WDT causes v                   | wake-up, this t                                                   | bit is cleared. |                |              | Before Instruc<br>REG<br>W<br>C                                                | ction<br>= 3<br>= 2<br>= 1                               |                                                                  |                |

After Instruction

REG

**Before Instruction** REG W

W

C Z N

С

After Instruction

REG W C Z N

**Before Instruction** REG W

After Instruction REG = W = C = Z = N =

С

Example 2:

Example 3:

FF 2 0

0 1 = =

2 5 = = 1

2 3 1 = = = = 0 = 0

SUBFWB

1 2 0

SUBFWB

; result is negative

; result is positive

; result is zero

REG, 1, 0

REG, 0, 0

=

=

=

=

= =

=

### 25.2 Extended Instruction Set

In addition to the standard 75 instructions of the PIC18 instruction set, PIC18F2221/2321/4221/4321 family devices also provide an optional extension to the core CPU functionality. The added features include eight additional instructions that augment indirect and indexed addressing operations and the implementation of Indexed Literal Offset Addressing mode for many of the standard PIC18 instructions.

The additional features of the extended instruction set are disabled by default. To enable them, users must set the XINST Configuration bit.

The instructions in the extended set (with the exception of CALLW, MOVSF and MOVSS) can all be classified as literal operations, which either manipulate the File Select Registers, or use them for indexed addressing. Two of the instructions, ADDFSR and SUBFSR, each have an additional special instantiation for using FSR2. These versions (ADDULNK and SUBULNK) allow for automatic return after execution.

The extended instructions are specifically implemented to optimize re-entrant program code (that is, code that is recursive or that uses a software stack) written in high-level languages, particularly C. Among other things, they allow users working in high-level languages to perform certain operations on data structures more efficiently. These include:

- Dynamic allocation and deallocation of software stack space when entering and leaving subroutines

- Function Pointer invocation

- Software Stack Pointer manipulation

- Manipulation of variables located in a software stack

A summary of the instructions in the extended instruction set is provided in Table 25-3. Detailed descriptions are provided in **Section 25.2.2** "**Extended Instruction Set**". The opcode field descriptions in Table 25-1 (page 280) apply to both the standard and extended PIC18 instruction sets.

Note: The instruction set extension and the Indexed Literal Offset Addressing mode were designed for optimizing applications written in C; the user may likely never use these instructions directly in the assembler. The syntax for these commands is provided as a reference for users who may be reviewing code that has been generated by a compiler.

### 25.2.1 EXTENDED INSTRUCTION SYNTAX

Most of the extended instructions use indexed arguments, using one of the File Select Registers and some offset to specify a source or destination register. When an argument for an instruction serves as part of indexed addressing, it is enclosed in square brackets ("[]"). This is done to indicate that the argument is used as an index or offset. The MPASM<sup>™</sup> Assembler will flag an error if it determines that an index or offset value is not bracketed.

When the extended instruction set is enabled, brackets are also used to indicate index arguments in byteoriented and bit-oriented instructions. This is in addition to other changes in their syntax. For more details, see Section 25.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands".

Note: In the past, square brackets have been used to denote optional arguments in the PIC18 and earlier instruction sets. In this text and going forward, optional arguments are denoted by braces ("{ }").

| Mnemo   | onic,                           | Description                              | Cycles | 16-E | Bit Instru | uction W | /ord | Status   |

|---------|---------------------------------|------------------------------------------|--------|------|------------|----------|------|----------|

| Opera   | nds                             | Description                              | Cycles | MSb  |            |          | LSb  | Affected |

| ADDFSR  | f, k                            | Add Literal to FSR                       | 1      | 1110 | 1000       | ffkk     | kkkk | None     |

| ADDULNK | k                               | Add Literal to FSR2 and Return           | 2      | 1110 | 1000       | 11kk     | kkkk | None     |

| CALLW   |                                 | Call Subroutine using WREG               | 2      | 0000 | 0000       | 0001     | 0100 | None     |

| MOVSF   | z <sub>s</sub> , f <sub>d</sub> | Move z <sub>s</sub> (source) to 1st Word | 2      | 1110 | 1011       | 0 z z z  | ZZZZ | None     |

|         |                                 | f <sub>d</sub> (destination) 2nd Word    |        | 1111 | ffff       | ffff     | ffff |          |

| MOVSS   | z <sub>s</sub> , z <sub>d</sub> | Move z <sub>s</sub> (source) to 1st word | 2      | 1110 | 1011       | 1zzz     | ZZZZ | None     |

|         |                                 | z <sub>d</sub> (destination) 2nd Word    |        | 1111 | XXXX       | XZZZ     | ZZZZ |          |

| PUSHL   | k                               | Store Literal at FSR2,                   | 1      | 1110 | 1010       | kkkk     | kkkk | None     |

|         |                                 | Decrement FSR2                           |        |      |            |          |      |          |

| SUBFSR  | f, k                            | Subtract Literal from FSR                | 1      | 1110 | 1001       | ffkk     | kkkk | None     |

| SUBULNK | k                               | Subtract Literal from FSR2 and           | 2      | 1110 | 1001       | 11kk     | kkkk | None     |

|         |                                 | Return                                   |        |      |            |          |      |          |

### TABLE 25-3: EXTENSIONS TO THE PIC18 INSTRUCTION SET

### 27.2 DC Characteristics:

### Power-Down and Supply Current PIC18F2221/2321/4221/4321 (Industrial) PIC18LF2221/2321/4221/4321 (Industrial) (Continued)

| PIC18LF2        | <b>221/2321/4221/4321</b><br>:rial)   |     | ird Ope | -     | <b>Conditions (unles</b><br>$e -40^{\circ}C \le TA$ | ss otherwise sta<br>≤ +85°C for indu                                                 |                                          |  |

|-----------------|---------------------------------------|-----|---------|-------|-----------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------|--|

|                 | 21/2321/4221/4321<br>trial, Extended) |     | ing tem | •     |                                                     | ss otherwise sta<br>$\leq +85^{\circ}$ C for indus<br>$\leq +125^{\circ}$ C for exte | strial                                   |  |

| Param<br>No.    | Device                                | Тур | Max     | Units |                                                     | Conditio                                                                             | ns                                       |  |

| D025            | Timer1 Oscillator                     | 2.1 | 4.5     | μA    | -40°C <sup>(5)</sup>                                |                                                                                      |                                          |  |

| (∆IOSCB)        |                                       |     | 4.5     | μΑ    | -10°C                                               | VDD = 2.0V                                                                           |                                          |  |

|                 |                                       | 1.8 | 4.5     | μA    | +25°C                                               | VDD - 2.0V                                                                           |                                          |  |

|                 |                                       | 2.1 | 4.5     | μA    | +85°C                                               |                                                                                      | 32 kHz Tuning Fork,<br>Crystal on Timer1 |  |

|                 |                                       | 2.2 | 6.0     | μA    | -40°C <sup>(5)</sup>                                |                                                                                      |                                          |  |

|                 |                                       | —   | 6       | μA    | -10°C                                               | VDD = 3.0V                                                                           |                                          |  |

|                 |                                       | 2.6 | 6.0     | μA    | +25°C                                               | VDD - 5.0V                                                                           | Oscillator <sup>(3)</sup>                |  |

|                 |                                       | 2.9 | 6.0     | μA    | +85°C                                               |                                                                                      |                                          |  |

|                 |                                       | 3.0 | 8.0     | μA    | -40°C <sup>(5)</sup>                                |                                                                                      |                                          |  |

|                 |                                       | _   | 8       | μA    | -10°C                                               | VDD = 5.0V                                                                           |                                          |  |

|                 |                                       | 3.2 | 8.0     | μA    | +25°C                                               | VDD - 5.0V                                                                           |                                          |  |

|                 |                                       | 3.4 | 8.0     | μA    | +85°C                                               |                                                                                      |                                          |  |

| D026            | A/D Converter                         | 1.0 | 2.0     | μA    | -40°C to +85°C                                      | VDD = 2.0V                                                                           |                                          |  |

| $(\Delta   AD)$ |                                       | 1.0 | 2.0     | μA    | -40°C to +85°C                                      | VDD = 3.0V                                                                           | A/D on, Not Converting                   |  |

|                 |                                       | 1.0 | 2.0     | μA    | -40°C to +85°C                                      | VDD = 5.0V                                                                           | Arb on, Not Converting                   |  |

|                 |                                       | 2.0 | 8.0     | μA    | -40°C to +125°C                                     | v DD = 3.0V                                                                          |                                          |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss, and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD or VSS;

MCLR = VDD; WDT enabled/disabled as specified.

3: Low-power, Timer1 oscillator is selected unless otherwise indicated, where LPT1OSC (CONFIG3H<2>) = 1.

4: BOR and HLVD enable internal band gap reference. With both modules enabled, current consumption will be less than the sum of both specifications.

5: When operation below -10°C is expected, use T1OSC High-Power mode, where LPT1OSC (CONFIG3H<2>) = 0.

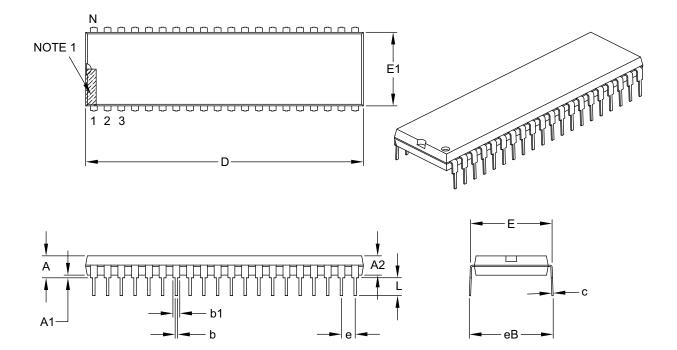

### 40-Lead Plastic Dual In-Line (P) – 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       | INCHES   |       |

|----------------------------|------------------|-------|----------|-------|

|                            | Dimension Limits | MIN   | NOM      | MAX   |

| Number of Pins             | N                |       | 40       | •     |

| Pitch                      | e                |       | .100 BSC |       |

| Top to Seating Plane       | A                | -     | -        | .250  |

| Molded Package Thickness   | A2               | .125  | -        | .195  |

| Base to Seating Plane      | A1               | .015  | -        | -     |