Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

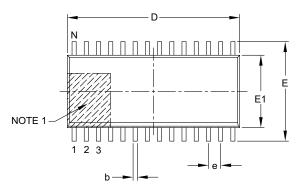

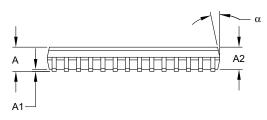

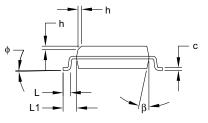

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2221-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din Nome                                                           | Pin Number |     |      | Pin Buff           | Buffer                              | Description                                                                                                          |

|--------------------------------------------------------------------|------------|-----|------|--------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                           | PDIP       | QFN | TQFP | Туре Туре          |                                     | Description                                                                                                          |

|                                                                    |            |     |      |                    |                                     | PORTA is a bidirectional I/O port.                                                                                   |

| RA0/AN0<br>RA0<br>AN0                                              | 2          | 19  | 19   | I/O<br>I           | TTL<br>Analog                       | Digital I/O.<br>Analog Input 0.                                                                                      |

| RA1/AN1<br>RA1<br>AN1                                              | 3          | 20  | 20   | I/O<br>I           | TTL<br>Analog                       | Digital I/O.<br>Analog Input 1.                                                                                      |

| RA2/AN2/VREF-/CVREF<br>RA2<br>AN2<br>VREF-<br>CVREF                | 4          | 21  | 21   | I/O<br>I<br>I<br>O | TTL<br>Analog<br>Analog<br>Analog   | Digital I/O.<br>Analog Input 2.<br>A/D reference voltage (low) input.<br>Comparator reference voltage output.        |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+                               | 5          | 22  | 22   | I/O<br>I<br>I      | TTL<br>Analog<br>Analog             | Digital I/O.<br>Analog Input 3.<br>A/D reference voltage (high) input.                                               |

| RA4/T0CKI/C1OUT<br>RA4<br>T0CKI<br>C1OUT                           | 6          | 23  | 23   | I/O<br>I<br>O      | ST<br>ST                            | Digital I/O.<br>Timer0 external clock input.<br>Comparator 1 output.                                                 |

| RA5/AN4/SS/HLVDIN/<br>C2OUT<br>RA5<br>AN4<br>SS<br>HLVDIN<br>C2OUT | 7          | 24  | 24   | I/O<br>I<br>I<br>O | TTL<br>Analog<br>TTL<br>Analog<br>— | Digital I/O.<br>Analog Input 4.<br>SPI slave select input.<br>High/Low-Voltage Detect input.<br>Comparator 2 output. |

| RA6                                                                |            |     |      |                    |                                     | See the OSC2/CLKO/RA6 pin.                                                                                           |

| RA7                                                                |            |     |      |                    |                                     | See the OSC1/CLKI/RA7 pin.                                                                                           |

### TABLE 1-3: PIC18F4221/4321 PINOUT I/O DESCRIPTIONS (CONTINUED)

$I^2C = ST$  with  $I^2C^{TM}$  or SMB levels

O = Output

**Note 1:** Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

**2**: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

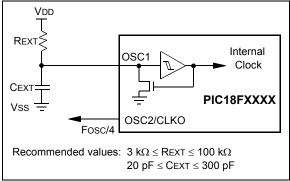

# 3.4 RC Oscillator

For timing insensitive applications, the RC and RCIO Oscillator modes offer additional cost savings. The actual oscillator frequency is a function of several factors:

- supply voltage

- values of the external resistor (REXT) and capacitor (CEXT)

- · operating temperature

Given the same device, operating voltage, temperature and component values, there will also be unit-to-unit frequency variations. These are due to factors such as:

- normal manufacturing variation

- difference in lead frame capacitance between package types (especially for low CEXT values)

- variations within the tolerance of limits of  $\ensuremath{\mathsf{REXT}}$  and  $\ensuremath{\mathsf{CEXT}}$

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 3-5 shows how the R/C combination is connected.

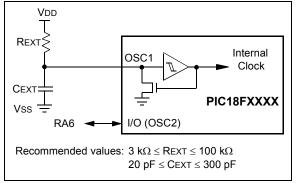

The RCIO Oscillator mode (Figure 3-6) functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

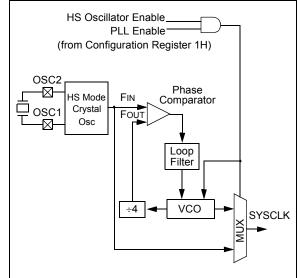

# 3.5 PLL Frequency Multiplier

A Phase Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency oscillator circuit or to clock the device up to its highest rated frequency from a crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals or users who require higher clock speeds from an internal oscillator.

### 3.5.1 HSPLL OSCILLATOR MODE

The HSPLL mode makes use of the HS mode oscillator for frequencies up to 10 MHz. A PLL then multiplies the oscillator output frequency by 4 to produce an internal clock frequency up to 40 MHz. The PLLEN bit is not available when this mode is configured as the primary clock source.

The PLL is only available to the crystal oscillator when the FOSC<3:0> Configuration bits are programmed for HSPLL mode (= 0110).

## 3.5.2 PLL AND INTOSC

The PLL is also available to the internal oscillator block when the internal oscillator block is configured as the primary clock source. In this configuration, the PLL is enabled in software and generates a clock output of up to 32 MHz. The operation of INTOSC with the PLL is described in **Section 3.6.4 "PLL in INTOSC Modes"**.

### 6.1.1 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU register are performed through the PCLATH register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 6.1.4.1 "Computed GOTO"**).

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

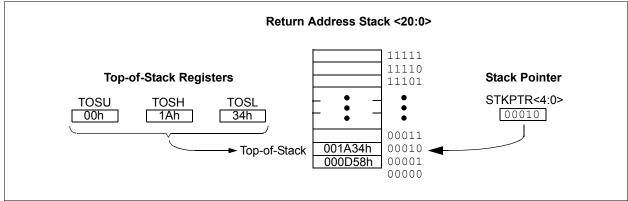

### 6.1.2 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack Special Function Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack; the Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack; the contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full or has overflowed or has underflowed.

### 6.1.2.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 6-2). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

## FIGURE 6-2: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

## 7.4 Erasing Flash Program Memory

The minimum erase block is 32 words or 64 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. TBLPTR<5:0> are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

### 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer register with address of row being erased.

- 2. Set the EECON1 register for the erase operation:

- set EEPGD bit to point to program memory;

- · clear the CFGS bit to access program memory;

- set WREN bit to enable writes;

- set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit. This will begin the row erase cycle.

- 7. The CPU will stall for duration of the erase (about 2 ms using internal timer).

- 8. Re-enable interrupts.

|                      | MOVLW<br>MOVWF<br>MOVWF<br>MOVLW<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL | ; load TBLPTR with the base<br>; address of the memory block                                                                                                        |

|----------------------|-------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ERASE_ROW            | MOVWP                                     | IDLFIKL                                                                             |                                                                                                                                                                     |

|                      | BSF<br>BCF<br>BSF<br>BSF<br>BCF           | EECON1, EEPGD<br>EECON1, CFGS<br>EECON1, WREN<br>EECON1, FREE<br>INTCON, GIE        | <pre>; point to Flash program memory<br/>; access Flash program memory<br/>; enable write to memory<br/>; enable Row Erase operation<br/>; disable interrupts</pre> |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF   | 55h<br>EECON2<br>0AAh<br>EECON2<br>EECON2<br>EECON1, WR                             | <pre>; write 55h ; write 0AAh ; start erase (CPU stall)</pre>                                                                                                       |

|                      | BSF                                       | INTCON, GIE                                                                         | ; re-enable interrupts                                                                                                                                              |

### EXAMPLE 7-2: ERASING A FLASH PROGRAM MEMORY ROW

### EXAMPLE 7-3: WRITING TO FLASH PROGRAM MEMORY (CONTINUED)

| PROGRAM_MEMORY |              |                             |

|----------------|--------------|-----------------------------|

| BCF            | INTCON, GIE  | ; disable interrupts        |

| MOVLW          | 55h          | ; required sequence         |

| MOVWF          | EECON2       | ; write 55h                 |

| MOVLW          | 0AAh         |                             |

| MOVWF          | EECON2       | ; write AAh                 |

| BSF            | EECON1, WR   | ; start program (CPU stall) |

| NOP            |              |                             |

| BSF            | INTCON, GIE  | ; re-enable interrupts      |

| DECFSZ         | COUNTER_HI   | ; loop until done           |

| GOTO           | PROGRAM_LOOP |                             |

| BCF            | EECON1, WREN | ; disable write to memory   |

|                |              |                             |

### 7.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

# 7.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

### 7.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See Section 24.0 "Special Features of the CPU" for more detail.

### 7.6 Flash Program Operation During Code Protection

See Section 24.5 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7      | Bit 6         | Bit 5       | Bit 4          | Bit 3         | Bit 2        | Bit 1         | Bit 0      | Reset<br>Values on<br>page |

|---------|------------|---------------|-------------|----------------|---------------|--------------|---------------|------------|----------------------------|

| TBLPTRU | _          |               | bit 21      | Program Me     | emory Table F | Pointer Uppe | r Byte (TBLP  | TR<20:16>) | 55                         |

| TBPLTRH | Program Me | emory Table   | Pointer H   | ligh Byte (TE  | BLPTR<15:8    | >)           |               |            | 55                         |

| TBLPTRL | Program Me | emory Table   | Pointer L   | ow Byte (TB.   | LPTR<7:0>     | )            |               |            | 55                         |

| TABLAT  | Program Me | emory Table   | Latch       |                |               |              |               |            | 55                         |

| INTCON  | GIE/GIEH   | PEIE/GIEL     | TMR0IE      | INT0IE         | RBIE          | TMR0IF       | <b>INT0IF</b> | RBIF       | 55                         |

| EECON2  | EEPROM C   | Control Regis | ster 2 (not | t a physical r | egister)      |              |               |            | 57                         |

| EECON1  | EEPGD      | CFGS          | _           | FREE           | WRERR         | WREN         | WR            | RD         | 57                         |

| IPR2    | OSCFIP     | CMIP          | _           | EEIP           | BCLIP         | HLVDIP       | TMR3IP        | CCP2IP     | 58                         |

| PIR2    | OSCFIF     | CMIF          |             | EEIF           | BCLIF         | HLVDIF       | TMR3IF        | CCP2IF     | 58                         |

| PIE2    | OSCFIE     | CMIE          |             | EEIE           | BCLIE         | HLVDIE       | TMR3IE        | CCP2IE     | 58                         |

TABLE 7-2:

REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

| Name   | Bit 7    | Bit 6                | Bit 5        | Bit 4        | Bit 3    | Bit 2  | Bit 1         | Bit 0  | Reset<br>Values<br>on page |  |

|--------|----------|----------------------|--------------|--------------|----------|--------|---------------|--------|----------------------------|--|

| INTCON | GIE/GIEH | PEIE/GIEL            | TMR0IE       | INT0IE       | RBIE     | TMR0IF | <b>INT0IF</b> | RBIF   | 55                         |  |

| EEADR  | EEPROM A | Address Regi         | ster         |              |          |        |               |        | 57                         |  |

| EEDATA | EEPROM [ | EEPROM Data Register |              |              |          |        |               |        |                            |  |

| EECON2 | EEPROM ( | Control Regis        | ter 2 (not a | n physical r | egister) |        |               |        | 57                         |  |

| EECON1 | EEPGD    | CFGS                 | —            | FREE         | WRERR    | WREN   | WR            | RD     | 57                         |  |

| IPR2   | OSCFIP   | CMIP                 | —            | EEIP         | BCLIP    | HLVDIP | TMR3IP        | CCP2IP | 58                         |  |

| PIR2   | OSCFIF   | CMIF                 | _            | EEIF         | BCLIF    | HLVDIF | TMR3IF        | CCP2IF | 58                         |  |

| PIE2   | OSCFIE   | CMIE                 | —            | EEIE         | BCLIE    | HLVDIE | TMR3IE        | CCP2IE | 58                         |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

| R/V        |                  | R/W-0                          | U-0                    | R/W-0                       | EST (FLAG<br>R/W-0           | R/W-0         | R/W-0         | R/W-0       |

|------------|------------------|--------------------------------|------------------------|-----------------------------|------------------------------|---------------|---------------|-------------|

| 050        |                  | CMIF                           | <u> </u>               | EEIF                        | BCLIF                        | HLVDIF        | TMR3IF        | CCP2IF      |

| bit 7      |                  |                                |                        |                             | DOLI                         |               |               | bit 0       |

|            |                  | scillator Fail                 | •                      | •                           |                              |               |               |             |

|            |                  | oscillator fa<br>clock opera   |                        | nput has cha                | anged to INT                 | OSC (must     | be cleared i  | n software) |

|            |                  | parator Inte                   |                        |                             |                              |               |               |             |

|            |                  | rator input h<br>rator input h |                        |                             | leared in sof                | tware)        |               |             |

| Unim       | pleme            | ented: Read                    | <b>l as</b> '0'        |                             |                              |               |               |             |

| EEIF:      | Data             | EEPROM/F                       | lash Write (           | Operation In                | terrupt Flag                 | bit           |               |             |

|            |                  |                                |                        |                             | leared in so<br>not been sta |               |               |             |

| BCLI       | F: Bus           | Collision In                   | iterrupt Flag          | bit                         |                              |               |               |             |

|            |                  | collision occ                  |                        | be cleared i                | n software)                  |               |               |             |

| HLVC       | IF: Hi           | gh/Low-Volt                    | age Detect             | Interrupt Fla               | g bit                        |               |               |             |

|            |                  | low-voltage<br>CON<7>)         | condition of           | ccurred; dire               | ction determ                 | nined by VD   | IRMAG bit     |             |

|            | •                | •                              |                        | as not occur                | red                          |               |               |             |

|            |                  | MR3 Overflo                    | •                      | •                           |                              |               |               |             |

|            |                  | register over<br>register did  |                        |                             | d in software                | e)            |               |             |

| CCP2       | 2 <b>IF</b> : C0 | CP2 Interrup                   | ot Flag bit            |                             |                              |               |               |             |

| 1 = A      |                  |                                |                        |                             | e cleared in                 | software)     |               |             |

| 1 = A      |                  | 1 register co                  |                        | ch occurred<br>atch occurre | (must be cle                 | eared in soft | ware)         |             |

| <u>PWM</u> | mode             | •                              | ·                      |                             |                              |               |               |             |

| Lege       |                  | ble bit                        | $\Delta A = \Delta A $ | itable bit                  |                              | plemented I   | pit read as " | <b>`</b>    |

'1' = Bit is set

'0' = Bit is cleared

# REGISTER 10-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

-n = Value at POR

x = Bit is unknown

# 11.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 11-5). The pins have Schmitt Trigger input buffers. RC1 is normally configured by Configuration bit, CCP2MX, as the default peripheral pin of the CCP2 module (default/erased state, CCP2MX = 1).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for additional information. Note: On a Power-on Reset, these pins are configured as digital inputs.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

### EXAMPLE 11-3: INITIALIZING PORTC

| CLRF  | PORTC | ; Initialize PORTC by<br>; clearing output<br>: data latches |

|-------|-------|--------------------------------------------------------------|

|       |       | ,                                                            |

| CLRF  | LATC  | ; Alternate method                                           |

|       |       | ; to clear output                                            |

|       |       | ; data latches                                               |

| MOVLW | OCFh  | ; Value used to                                              |

|       |       | ; initialize data                                            |

|       |       | ; direction                                                  |

| MOVWF | TRISC | ; Set RC<3:0> as inputs                                      |

|       |       | ; RC<5:4> as outputs                                         |

|       |       | ; RC<7:6> as inputs                                          |

|       |       | *                                                            |

|       | R/W-0                                      | R/W-0                                                     | R-0                            | R-0          | R-0         | R-0                               | R-0           | R-0        |

|-------|--------------------------------------------|-----------------------------------------------------------|--------------------------------|--------------|-------------|-----------------------------------|---------------|------------|

|       | SMP                                        | CKE                                                       | D/A                            | Р            | S           | R/W                               | UA            | BF         |

|       | bit 7                                      |                                                           |                                |              |             |                                   |               | bit 0      |

| bit 7 |                                            | v Rate Contr                                              |                                |              |             |                                   |               |            |

|       | 1 = Slew rate                              |                                                           |                                |              |             | 100 kHz and<br>(Hz)               | 1 MHz)        |            |

| bit 6 | In Master of 1 = Enable                    | Bus Select bi<br>or Slave mod<br>SMBus spe<br>e SMBus spe | de:<br>ecific inputs           |              |             |                                   |               |            |

| bit 5 | D/A: Data/                                 | Address bit                                               |                                |              |             |                                   |               |            |

|       | <u>In Master r</u><br>Reserved.            | <u>mode:</u>                                              |                                |              |             |                                   |               |            |

|       |                                            | es that the la                                            | ast byte rece                  |              |             |                                   |               |            |

| bit 4 | 0 = Indicat<br>P: Stop bit                 |                                                           | ast byte rece                  | ived or tran | smitted was | s address                         |               |            |

| bit i | 1 = Indicat                                |                                                           | op bit has be<br>etected last  | en detected  | last        |                                   |               |            |

|       | Note:                                      |                                                           | leared on R                    | eset and wh  | nen SSPEN   | is cleared.                       |               |            |

| bit 3 | S: Start bit                               |                                                           |                                |              |             |                                   |               |            |

|       |                                            | it was not de                                             |                                |              |             |                                   |               |            |

|       | Note:                                      | This bit is c                                             | cleared on Re                  | eset and wh  | nen SSPEN   | is cleared.                       |               |            |

| bit 2 |                                            |                                                           | mation bit (I <sup>2</sup>     | C™ mode o    | only)       |                                   |               |            |

|       | <u>In Slave m</u><br>1 = Read<br>0 = Write | iode:                                                     |                                |              |             |                                   |               |            |

|       | Note:                                      |                                                           |                                |              |             | g the last ado<br>Start bit, Stop |               |            |

|       |                                            | <u>mode:</u><br>nit is in prog<br>nit is not in p         |                                |              |             |                                   |               |            |

|       | Note:                                      | ORing this<br>in Active m                                 |                                | , RSEN, PE   | N, RCEN o   | r ACKEN will                      | indicate if t | he MSSP is |

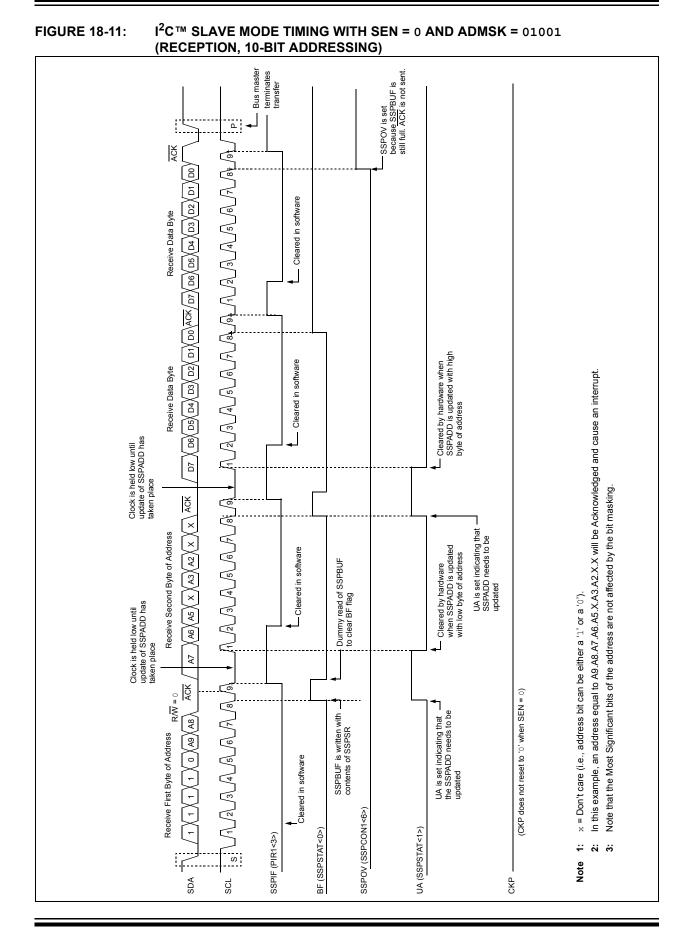

| bit 1 | UA: Updat                                  | e Address b                                               | it (10-bit Sla                 | ve mode on   | ly)         |                                   |               |            |

|       | 1 = Indicat                                | es that the u                                             | -                              | update the   | • ·         | the SSPADE                        | ) register    |            |

| bit 0 |                                            | Full Status b                                             | -                              |              |             |                                   |               |            |

|       | In Transmi                                 |                                                           |                                |              |             |                                   |               |            |

|       | 1 = SSPBU                                  |                                                           |                                |              |             |                                   |               |            |

|       | In Receive                                 | JF is empty                                               |                                |              |             |                                   |               |            |

|       | 1 = SSPBU                                  | JF is full (do                                            | es not includ<br>(does not inc |              |             |                                   |               |            |

|       | Legend:                                    |                                                           |                                |              |             |                                   |               |            |

|       | R = Reada                                  | hle hit                                                   | W = Writab                     | lo hit       | II – Unimr  | plemented bit                     | read as '0'   |            |

|       | IX - IXCaua                                |                                                           | vv – vviitab                   |              | 0 - 011111  | Jemenieu bit                      | , icuu us o   |            |

## RE

© 2009 Microchip Technology Inc.

| REGISTER 19-2: | RCSTA: R                        |                                                        | TATUS AN       |                |              | TER           |              |              |

|----------------|---------------------------------|--------------------------------------------------------|----------------|----------------|--------------|---------------|--------------|--------------|

|                | R/W-0                           | R/W-0                                                  | R/W-0          | R/W-0          | R/W-0        | R-0           | R-0          | R-x          |

|                | SPEN                            | RX9                                                    | SREN           | CREN           | ADDEN        | FERR          | OERR         | RX9D         |

|                | bit 7                           |                                                        |                |                |              |               |              | bit 0        |

| bit 7          |                                 | ial Dart Enal                                          | bla bit        |                |              |               |              |              |

| bit 7          |                                 | ial Port Enal                                          |                | DV/DT and      | TV/CK pipe   | an aprial pa  | rt nina)     |              |

|                |                                 | oort disabled                                          |                |                | TX/CK pins   | as senai po   | it pins)     |              |

| bit 6          | <b>RX9:</b> 9-bit               | Receive Ena                                            | able bit       |                |              |               |              |              |

|                |                                 | <ul> <li>9-bit recept</li> <li>8-bit recept</li> </ul> |                |                |              |               |              |              |

| bit 5          | SREN: Sin                       | gle Receive                                            | Enable bit     |                |              |               |              |              |

|                | <u>Asynchron</u><br>Don't care. |                                                        |                |                |              |               |              |              |

|                | Synchrono                       | us mode – N                                            | /laster:       |                |              |               |              |              |

|                |                                 | s single rece                                          |                |                |              |               |              |              |

|                |                                 | es single rec                                          |                |                |              |               |              |              |

|                |                                 | leared after                                           | -              | complete.      |              |               |              |              |

|                | Don't care.                     | <u>us mode – S</u>                                     | <u>blave:</u>  |                |              |               |              |              |

| bit 4          |                                 | ntinuous Re                                            | ceive Enable   | e bit          |              |               |              |              |

|                | Asynchron                       |                                                        |                |                |              |               |              |              |

|                | 1 = Enable                      |                                                        |                |                |              |               |              |              |

|                | 0 = Disable                     | es receiver                                            |                |                |              |               |              |              |

|                | Synchrono                       |                                                        | · · · ·        |                | ODEN         |               |              |              |

|                |                                 | s continuous<br>es continuou                           |                | til enable bit | CREN is cle  | eared (CREI   | N overrides  | SREN)        |

| bit 3          |                                 | ddress Dete                                            |                | t              |              |               |              |              |

| bit o          |                                 | ous mode 9-                                            |                |                |              |               |              |              |

|                |                                 |                                                        |                |                | upt and load | s the receiv  | e buffer whe | en RSR<8>    |

|                | 0 = Disabl                      | es address o                                           | detection, all | bytes are r    | eceived and  | ninth bit car | n be used as | s parity bit |

|                |                                 | ous mode 9-                                            | bit (RX9 = c   | ) <u>):</u>    |              |               |              |              |

|                | Don't care.                     |                                                        |                |                |              |               |              |              |

| bit 2          |                                 | ming Error b                                           |                |                |              |               |              |              |

|                | 1 = Framin<br>0 = No fran       |                                                        | be updated     | by reading     | RCREG regi   | ister and rec | eiving next  | valid byte)  |

| bit 1          | OERR: OV                        | errun Error b                                          | pit            |                |              |               |              |              |

|                |                                 | n error (can                                           | be cleared b   | by clearing b  | oit CREN)    |               |              |              |

|                | 0 = No ove                      |                                                        |                |                |              |               |              |              |

| bit 0          |                                 | bit of Receiv                                          |                |                |              |               | <b>C</b>     | _            |

|                | I his can be                    | e address/da                                           | ata bit or a p | arity bit and  | must be cal  | culated by u  | ser tirmware | 9.           |

|                | Legend:                         |                                                        |                |                |              |               |              |              |

|                | R = Reada                       | ble bit                                                | W = W          | /ritable bit   | U = Unin     | nplemented    | bit, read as | ʻ0'          |

|                | -n = Value                      |                                                        | '1' = B        | it is set      |              | s cleared     | x = Bit is u |              |

|                |                                 |                                                        | i – D          |                |              |               |              |              |

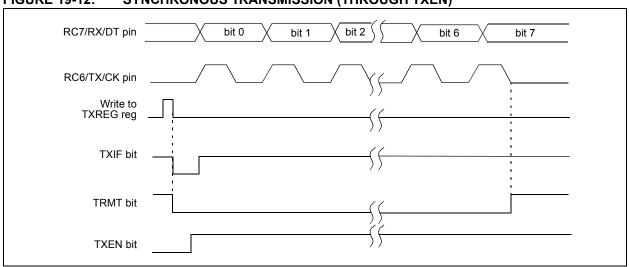

### FIGURE 19-12: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

### TABLE 19-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7                | Bit 6       | Bit 5       | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------|-------------|-------------|-------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL   | TMR0IE      | INT0IE      | RBIE  | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF        | RCIF        | TXIF        | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE        | RCIE        | TXIE        | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP        | RCIP        | TXIP        | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                         |

| RCSTA   | SPEN                 | RX9         | SREN        | CREN        | ADDEN | FERR   | OERR   | RX9D   | 57                         |

| TXREG   | EUSART T             | ransmit Reg | ister       |             |       |        |        |        | 57                         |

| TXSTA   | CSRC                 | TX9         | TXEN        | SYNC        | SENDB | BRGH   | TRMT   | TX9D   | 57                         |

| BAUDCON | ABDOVF               | RCIDL       | RXDTP       | TXCKP       | BRG16 | —      | WUE    | ABDEN  | 57                         |

| SPBRGH  | EUSART E             | Baud Rate G | enerator Re | gister High | Byte  |        |        |        | 57                         |

| SPBRG   | EUSART E             | Baud Rate G | enerator Re | gister Low  | Byte  |        |        |        | 57                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

**Note 1:** These bits are unimplemented on 28-pin devices and read as '0'.

| REGISTER 20-3: | ADCON2:                                                                                                         | A/D CONT                                                                                                  | ROL REG                                                                | ISTER 2        |                                                           |       |                      |       |

|----------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------|-----------------------------------------------------------|-------|----------------------|-------|

|                | R/W-0                                                                                                           | U-0                                                                                                       | R/W-0                                                                  | R/W-0          | R/W-0                                                     | R/W-0 | R/W-0                | R/W-0 |

|                | ADFM                                                                                                            | _                                                                                                         | ACQT2                                                                  | ACQT1          | ACQT0                                                     | ADCS2 | ADCS1                | ADCS0 |

|                | bit 7                                                                                                           |                                                                                                           |                                                                        |                |                                                           |       |                      | bit 0 |

| bit 7          | ADFM: A/D                                                                                                       | Result For                                                                                                | mat Select b                                                           | bit            |                                                           |       |                      |       |

|                | 1 = Right ju<br>0 = Left jus                                                                                    |                                                                                                           |                                                                        |                |                                                           |       |                      |       |

| bit 6          | Unimplem                                                                                                        | ented: Read                                                                                               | <b>d as</b> '0'                                                        |                |                                                           |       |                      |       |

| bit 5-3        | ACQT<2:0                                                                                                        | >: A/D Acqu                                                                                               | isition Time                                                           | Select bits    |                                                           |       |                      |       |

|                | 111 = 20 T.<br>110 = 16 T.<br>101 = 12 T.<br>100 = 8 TA<br>011 = 6 TA<br>010 = 4 TA<br>001 = 2 TA<br>000 = 0 TA | AD<br>AD<br>D<br>D<br>D<br>D                                                                              |                                                                        |                |                                                           |       |                      |       |

| bit 2-0        | 111 = FRC<br>110 = FOS<br>101 = FOS<br>010 = FOS<br>011 = FRC<br>010 = FOS<br>001 = FOS                         | (clock derive<br>c/64<br>c/16<br>c/4<br>(clock derive<br>c/32<br>c/8<br>c/2<br>If the A/D I<br>added befo | ed from A/D<br>ed from A/D<br><sup>=</sup> RC clock so<br>re the A/D c | lock starts. T | or) <sup>(1)</sup><br>or) <sup>(1)</sup><br>ected, a dela | •     | CY (instruction to b | • •   |

|                |                                                                                                                 | before star                                                                                               | ting a conve                                                           | rsion.         |                                                           |       |                      |       |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

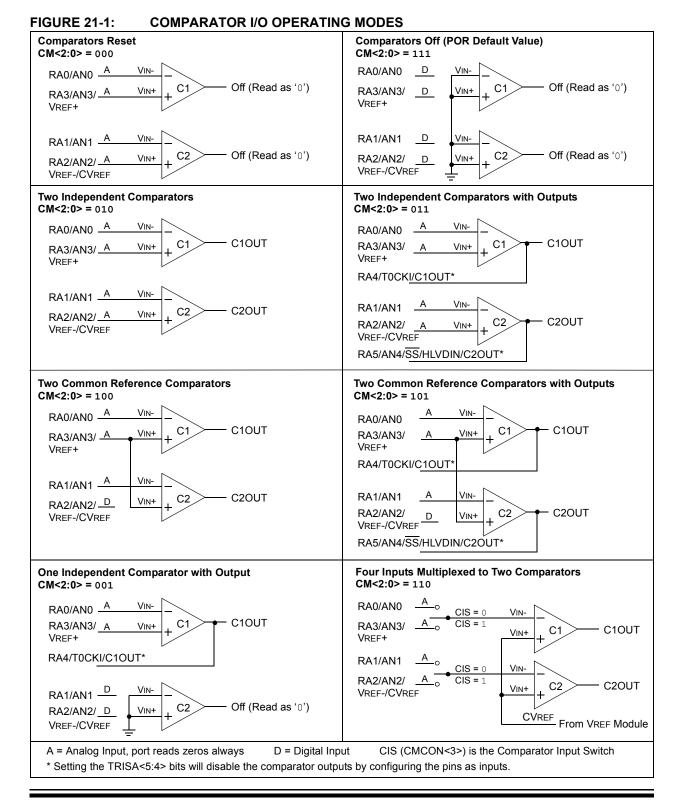

## 21.1 Comparator Configuration

There are eight modes of operation for the comparators, shown in Figure 21-1. Bits CM<2:0> of the CMCON register are used to select these modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the

comparator output level may not be valid for the specified mode change delay shown in **Section 27.0 "Electrical Characteristics"**.

Note: Comparator interrupts should be disabled during a Comparator mode change; otherwise, a false interrupt may occur.

| CPF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SGT              | Compare                     | f with W, Sk                               | ip if f > W |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------|--------------------------------------------|-------------|--|--|--|--|

| Synta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ax:              | CPFSGT                      | f {,a}                                     |             |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ands:            |                             | 0 ≤ f ≤ 255                                |             |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  | a ∈ [0,1]                   |                                            |             |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ation:           | (f) - (W),                  |                                            |             |  |  |  |  |

| opor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  | skip if (f) >               | (W)                                        |             |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  | • • • •                     | omparison)                                 |             |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | s Affected:      | None                        |                                            |             |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  | 0110                        | 010a fff                                   | f ffff      |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                |                             |                                            |             |  |  |  |  |

| Description:Compares the contents of data mem<br>location 'f' to the contents of the W b<br>performing an unsigned subtraction.<br>If the contents of 'f' are greater than<br>contents of WREG, then the fetched<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>two-cycle instruction.<br>If 'a' is '0', the Access Bank is select<br>If 'a' is '1', the BSR is used to select<br>GPR bank (default).<br>If 'a' is '0' and the extended instructi<br>set is enabled, this instruction opera<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Index<br>Literal Offset Mode" for details.Words:1 |                  |                             |                                            |             |  |  |  |  |

| Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  | 1(2)                        |                                            |             |  |  |  |  |

| Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55.              | • •                         | <b>Note:</b> 3 cycles if skip and followed |             |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  | ,                           | 2-word instru                              |             |  |  |  |  |

| 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ycle Activity:   | 5                           |                                            |             |  |  |  |  |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q1               | Q2                          | Q3                                         | Q4          |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Decode           | Read                        | Process                                    | No          |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  | register 'f'                | Data                                       | operation   |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ip:              |                             | •                                          |             |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Q1               | Q2                          | Q3                                         | Q4          |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No               | No                          | No                                         | No          |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | operation        | operation                   | operation                                  | operation   |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ip and followe   | d by 2-word in              | struction:                                 |             |  |  |  |  |

| i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Q1               | Q2                          | Q3                                         | Q4          |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No               | No                          | No                                         | No          |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | operation        | operation                   | operation                                  | operation   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No               | No                          | No                                         | No          |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | operation        | operation                   | operation                                  | operation   |  |  |  |  |

| <u>Example:</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  | HERE<br>NGREATER<br>GREATER | NGREATER :                                 |             |  |  |  |  |