Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2221t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

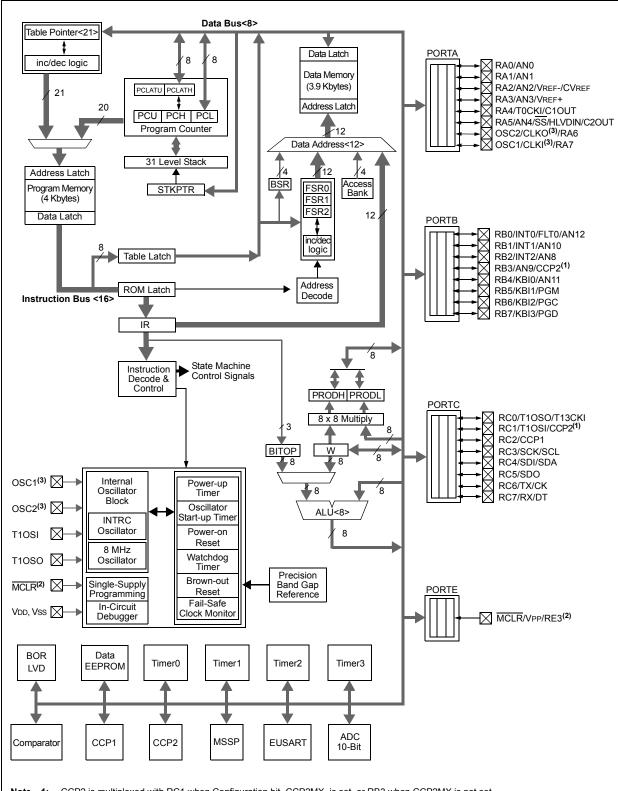

# FIGURE 1-1: PIC18F2221/2321 (28-PIN) BLOCK DIAGRAM

Note 1: CCP2 is multiplexed with RC1 when Configuration bit, CCP2MX, is set, or RB3 when CCP2MX is not set.

**2**: RE3 is only available when  $\overline{\text{MCLR}}$  functionality is disabled.

3: OSC1/CLKI and OSC2/CLKO are only available in select oscillator modes and when these pins are not being used as digital I/O. Refer to Section 3.0 "Oscillator Configurations" for additional information.

# 3.6 Internal Oscillator Block

The PIC18F2221/2321/4221/4321 family of devices includes an internal oscillator block which generates two different clock signals; either can be used as the microcontroller's clock source. This may eliminate the need for external oscillator circuits on the OSC1 and/or OSC2 pins.

The main output (INTOSC) is an 8 MHz clock source, which can be used to directly drive the device clock. It also drives a postscaler, which can provide a range of clock frequencies from 31 kHz to 4 MHz. The INTOSC output is enabled when a clock frequency from 125 kHz to 8 MHz is selected. The INTOSC output can also be enabled when 31 kHz is selected, depending on the INTSRC bit (OSCTUNE<7>).

The other clock source is the internal RC oscillator (INTRC), which provides a nominal 31 kHz output. INTRC is enabled if it is selected as the device clock source; it is also enabled automatically when any of the following are enabled:

- Power-up Timer

- · Fail-Safe Clock Monitor

- · Watchdog Timer

- Two-Speed Start-up

These features are discussed in greater detail in Section 24.0 "Special Features of the CPU".

The clock source frequency (INTOSC direct, INTRC direct or INTOSC postscaler) is selected by configuring the IRCF bits of the OSCCON register (page 37).

#### 3.6.1 INTIO MODES

Using the internal oscillator as the clock source eliminates the need for up to two external oscillator pins, which can then be used for digital I/O. Two distinct configurations are available:

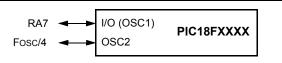

- In INTIO1 mode, the OSC2 pin outputs Fosc/4, while OSC1 functions as RA7 (see Figure 3-8) for digital input and output.

- In INTIO2 mode, OSC1 functions as RA7 and OSC2 functions as RA6 (see Figure 3-9), both for digital input and output.

#### FIGURE 3-8: INTIO1 OSCILLATOR MODE

| FIGURE 3-9: | INTIO2 OSCILLATOR MODE |

|-------------|------------------------|

|             |                        |

| RA7 🛶 🕨 | I/O (OSC1) | PIC18FXXXX |  |

|---------|------------|------------|--|

| RA6 🔶   | I/O (OSC2) |            |  |

#### 3.6.2 INTOSC OUTPUT FREQUENCY

The internal oscillator block is calibrated at the factory to produce an INTOSC output frequency of 8 MHz.

The INTRC oscillator operates independently of the INTOSC source. Any changes in INTOSC across voltage and temperature are not necessarily reflected by changes in INTRC or vice versa.

#### 3.6.3 OSCTUNE REGISTER

The INTOSC output has been calibrated at the factory but can be adjusted in the user's application. This is done by writing to TUN<4:0> (OSCTUNE<4:0>) in the OSCTUNE register (Register 3-1).

When the OSCTUNE register is modified, the INTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred. The INTRC is not affected by OSCTUNE.

The OSCTUNE register also implements the INTSRC (OSCTUNE<7>) and PLLEN (OSCTUNE<6>) bits, which control certain features of the internal oscillator block. The INTSRC bit allows users to select which internal oscillator provides the clock source when the 31 kHz frequency option is selected. This is covered in greater detail in **Section 3.7.1** "Oscillator Control **Register**".

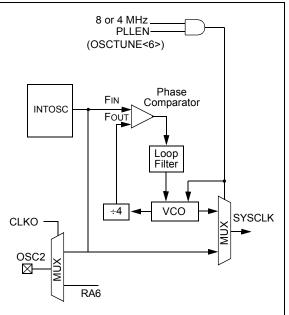

The PLLEN bit controls the operation of the Phase Locked Loop (PLL) in Internal Oscillator modes (see Figure 3-10).

#### FIGURE 3-10: INTOSC AND PLL BLOCK DIAGRAM

## 3.8 Effects of Power-Managed Modes on the Various Clock Sources

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin in Crystal Oscillator modes) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the Timer1 oscillator is operating and providing the device clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1 or Timer3.

In internal oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator block provides the device clock source. The 31 kHz INTRC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the powermanaged mode (see Section 24.2 "Watchdog Timer (WDT)", Section 24.3 "Two-Speed Start-up" and Section 24.4 "Fail-Safe Clock Monitor" for more information). The INTOSC output at 8 MHz may be used directly to clock the device or may be divided down by the postscaler. The INTOSC output is disabled if the clock is provided directly from the INTRC output. The INTOSC output is also enabled for Two-Speed Start-up at 1 MHz after a Reset.

If the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a Real-Time Clock. Other features may be operating that do not require a device clock source (i.e., MSSP slave, PSP, INTx pins and others). Peripherals that may add significant current consumption are listed in **Section 27.2 "DC Characteristics".**

# 3.9 Power-up Delays

Power-up delays are controlled by two or three timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 5.5 "Device Reset Timers"**.

The first timer is the Power-up Timer (PWRT) which provides a fixed delay on power-up (parameter 33, Table 27-10). It is enabled by clearing (= 0) the PWRTEN Configuration bit (CONFIG2L<0>).

#### 3.9.1 DELAYS FOR POWER-UP AND RETURN TO PRIMARY CLOCK

The second timer is the Oscillator Start-up Timer (OST), intended to delay execution until the crystal oscillator is stable (LP, XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the HSPLL Oscillator mode is selected, a third timer delays execution for an additional 2 ms following the HS mode OST delay, so the PLL can lock to the incoming clock frequency. At the end of these delays, the OSTS bit (OSCCON<3>) is set.

There is a delay of interval TCSD (parameter 38, Table 27-10), once execution is allowed to start, when the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC, RC or INTIO modes are used as the primary clock source.

| OSC Mode      | OSC1 Pin                                                                       | OSC2 Pin                                              |

|---------------|--------------------------------------------------------------------------------|-------------------------------------------------------|

| RC, INTIO1    | RC, INTIO1 Floating, external resistor pulls high At logic low (clock/4 output |                                                       |

| RCIO          | Floating, external resistor pulls high                                         | Configured as PORTA, bit 6                            |

| INTIO2        | Configured as PORTA, bit 7                                                     | Configured as PORTA, bit 6                            |

| ECIO          | Floating, driven by external clock                                             | Configured as PORTA, bit 6                            |

| EC            | Floating, driven by external clock                                             | At logic low (clock/4 output)                         |

| LP, XT and HS | Feedback inverter disabled at quiescent voltage level                          | Feedback inverter disabled at quiescent voltage level |

TABLE 3-3:OSC1 AND OSC2 PIN STATES IN SLEEP MODE

**Note:** See Table 5-2 in **Section 5.0 "Reset"** for time-outs due to Sleep and MCLR Reset.

## 4.4.1 PRI\_IDLE MODE

This mode is unique among the three low-power Idle modes, in that it does not disable the primary device clock. For timing sensitive applications, this allows for the fastest resumption of device operation with its more accurate primary clock source, since the clock source does not have to "warm-up" or transition from another oscillator.

PRI\_IDLE mode is entered from PRI\_RUN mode by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set IDLEN first, then clear the SCS bits and execute SLEEP. Although the CPU is disabled, the peripherals continue to be clocked from the primary clock source specified by the FOSC<3:0> Configuration bits. The OSTS bit remains set (see Figure 4-7).

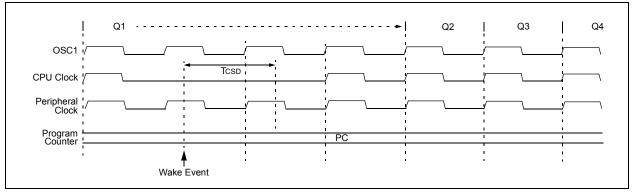

When a wake event occurs, the CPU is clocked from the primary clock source. A delay of interval TCSD (parameter 38, Table 27-10) is required between the wake event and when code execution starts. This is required to allow the CPU to become ready to execute instructions. After the wake-up, the OSTS bit remains set. The IDLEN and SCS bits are not affected by the wake-up (see Figure 4-8).

# 4.4.2 SEC\_IDLE MODE

In SEC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the Timer1 oscillator. This mode is entered from SEC\_RUN by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set the IDLEN bit first, then set the SCS<1:0> bits to '01' and execute SLEEP. When the clock source is switched to the Timer1 oscillator, the primary oscillator is shut down, the OSTS bit is cleared and the T1RUN bit is set.

When a wake event occurs, the peripherals continue to be clocked from the Timer1 oscillator. After an interval of TCSD following the wake event, the CPU begins executing code being clocked by the Timer1 oscillator. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run (see Figure 4-8).

Note: The Timer1 oscillator should already be running prior to entering SEC\_IDLE mode. If the T1OSCEN bit is not set when writing the SCS<1:0> bits, entry to SEC\_IDLE mode will not occur. If the Timer1 oscillator is enabled but not yet running, peripheral clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result.

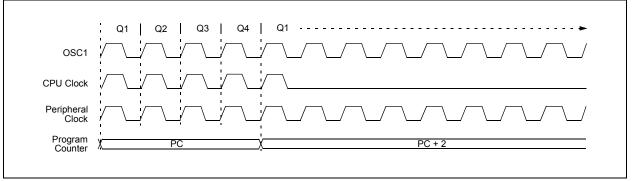

#### FIGURE 4-7: TRANSITION TIMING FOR ENTRY TO IDLE MODE

#### FIGURE 4-8: TRANSITION TIMING FOR WAKE FROM IDLE TO RUN MODE

#### 4.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped; and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval TCSD following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

# TABLE 4-2:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Clock Source<br>before Wake-up | Clock Source<br>after Wake-up | Exit Delay                            | Clock Ready Status<br>Bit (OSCCON) |

|--------------------------------|-------------------------------|---------------------------------------|------------------------------------|

|                                | LP, XT, HS                    |                                       |                                    |

| Primary Device Clock           | HSPLL                         | TCSD <sup>(1)</sup>                   | OSTS                               |

| (PRI_IDLE mode)                | EC, RC                        |                                       |                                    |

|                                | INTOSC <sup>(2)</sup>         |                                       | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |

| 11050                          | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |

| T1OSC                          | EC, RC                        | TCSD <sup>(1)</sup>                   |                                    |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                 | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |

| INTOSC <sup>(3)</sup>          | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |

|                                | EC, RC                        | Tcsd <sup>(1)</sup>                   |                                    |

|                                | INTOSC <sup>(2)</sup>         | None                                  | IOFS                               |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |

| None                           | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |

| (Sleep mode)                   | EC, RC                        | TCSD <sup>(1)</sup>                   |                                    |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                 | IOFS                               |

**Note 1:** TCSD (parameter 38) is a required delay when waking from Sleep and all Idle modes and runs concurrently with any other required delays (see **Section 4.4 "Idle Modes**"). On Reset, INTOSC defaults to 1 MHz.

2: Includes both the INTOSC 8 MHz source and postscaler derived frequencies.

**3:** TOST is the Oscillator Start-up Timer (parameter 32). t<sub>rc</sub> is the PLL Lock-out Timer (parameter F12); it is also designated as TPLL.

4: Execution continues during TIOBST (parameter 39), the INTOSC stabilization period.

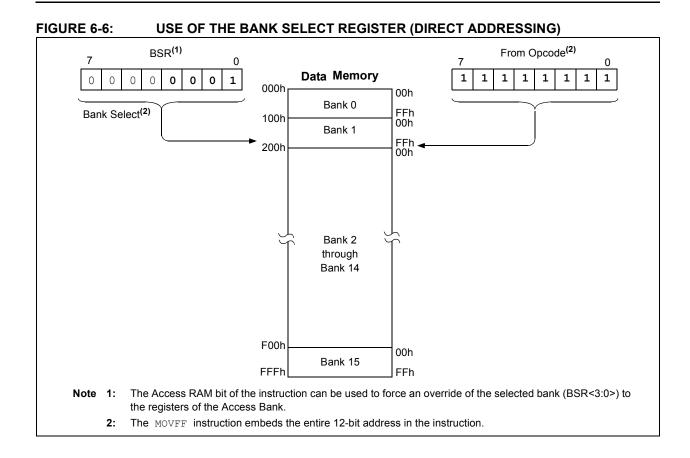

# 6.3.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 128 bytes of memory (00h-7Fh) in Bank 0 and the last 128 bytes of memory (80h-FFh) in Block 15. The lower half is known as the "Access RAM" and is composed of GPRs. This upper half is also where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 6-5).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0',

however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle, without updating the BSR first. For 8-bit addresses of 80h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 80h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 6.5.3 "Mapping the Access Bank in Indexed Literal Offset Addressing Mode".

#### 6.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

| Name   | Bit 7                                                 | Bit 6     | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1         | Bit 0  | Reset<br>Values<br>on page |

|--------|-------------------------------------------------------|-----------|--------|--------|-------|--------|---------------|--------|----------------------------|

| INTCON | GIE/GIEH                                              | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | <b>INT0IF</b> | RBIF   | 55                         |

| EEADR  | EEPROM Address Register                               |           |        |        |       |        | 57            |        |                            |

| EEDATA | EEPROM Data Register                                  |           |        |        |       |        | 57            |        |                            |

| EECON2 | 2 EEPROM Control Register 2 (not a physical register) |           |        |        |       | 57     |               |        |                            |

| EECON1 | EEPGD                                                 | CFGS      | —      | FREE   | WRERR | WREN   | WR            | RD     | 57                         |

| IPR2   | OSCFIP                                                | CMIP      | —      | EEIP   | BCLIP | HLVDIP | TMR3IP        | CCP2IP | 58                         |

| PIR2   | OSCFIF                                                | CMIF      | _      | EEIF   | BCLIF | HLVDIF | TMR3IF        | CCP2IF | 58                         |

| PIE2   | OSCFIE                                                | CMIE      | —      | EEIE   | BCLIE | HLVDIE | TMR3IE        | CCP2IE | 58                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

# 11.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 11-5). The pins have Schmitt Trigger input buffers. RC1 is normally configured by Configuration bit, CCP2MX, as the default peripheral pin of the CCP2 module (default/erased state, CCP2MX = 1).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for additional information. Note: On a Power-on Reset, these pins are configured as digital inputs.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

#### EXAMPLE 11-3: INITIALIZING PORTC

| CLRF  | PORTC | ; Initialize PORTC by<br>; clearing output<br>: data latches |

|-------|-------|--------------------------------------------------------------|

|       |       | ,                                                            |

| CLRF  | LATC  | ; Alternate method                                           |

|       |       | ; to clear output                                            |

|       |       | ; data latches                                               |

| MOVLW | OCFh  | ; Value used to                                              |

|       |       | ; initialize data                                            |

|       |       | ; direction                                                  |

| MOVWF | TRISC | ; Set RC<3:0> as inputs                                      |

|       |       | ; RC<5:4> as outputs                                         |

|       |       | ; RC<7:6> as inputs                                          |

|       |       | *                                                            |

# 12.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

#### 12.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

# 12.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name                           | Bit 7                     | Bit 6              | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on page |

|--------------------------------|---------------------------|--------------------|--------|--------|-------|--------|--------|-------|----------------------------|

| TMR0L Timer0 Register Low Byte |                           |                    |        |        |       |        | 56     |       |                            |

| TMR0H                          | Timer0 Register High Byte |                    |        |        |       | 56     |        |       |                            |

| INTCON                         | GIE/GIEH                  | PEIE/GIEL          | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 55                         |

| TOCON                          | TMR0ON                    | T08BIT             | TOCS   | TOSE   | PSA   | T0PS2  | T0PS1  | T0PS0 | 56                         |

| TRISA                          | RA7 <sup>(1)</sup>        | RA6 <sup>(1)</sup> | RA5    | RA4    | RA3   | RA2    | RA1    | RA0   | 58                         |

TABLE 12-1:

REGISTERS ASSOCIATED WITH TIMER0

Legend: Shaded cells are not used by Timer0.

**Note 1:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

# 13.2 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes (see Figure 13-2). When the RD16 control bit (T1CON<7>) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L will load the contents of the high byte of Timer1 into the Timer1 high byte buffer. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. The Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits to both the high and low bytes of Timer1 at once.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

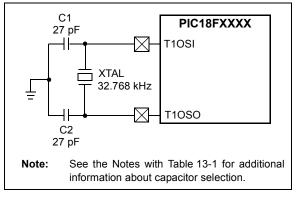

# 13.3 Timer1 Oscillator

An on-chip crystal oscillator circuit is incorporated between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting the Timer1 Oscillator Enable bit, T1OSCEN (T1CON<3>). The oscillator is a low-power circuit rated for 32 kHz crystals. It will continue to run during all power-managed modes. The circuit for a typical LP oscillator is shown in Figure 13-3. Table 13-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper start-up of the Timer1 oscillator.

#### FIGURE 13-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

# TABLE 13-1:CAPACITOR SELECTION FOR<br/>THE TIMER OSCILLATOR

| Osc Type                                                                                                 | Freq                                                                                                                                                                | C1                   | C2                   |  |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|--|--|--|

| LP                                                                                                       | 32 kHz                                                                                                                                                              | 27 pF <sup>(1)</sup> | 27 pF <sup>(1)</sup> |  |  |  |

| <b>Note 1:</b> Microchip suggests these values as a starting point in validating the oscillator circuit. |                                                                                                                                                                     |                      |                      |  |  |  |

| 2:                                                                                                       | Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time.                                                            |                      |                      |  |  |  |

|                                                                                                          | Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components. |                      |                      |  |  |  |

| 4:                                                                                                       | Capacitor values are for design guidance only.                                                                                                                      |                      |                      |  |  |  |

#### 13.3.1 USING TIMER1 AS A CLOCK SOURCE

The Timer1 oscillator is also available as a clock source in power-managed modes. By setting the clock select bits, SCS<1:0> (OSCCON<1:0>), to '01', the device switches to SEC\_RUN mode; both the CPU and peripherals are clocked from the Timer1 oscillator. If the IDLEN bit (OSCCON<7>) is cleared and a SLEEP instruction is executed, the device enters SEC\_IDLE mode. Additional details are available in **Section 4.0 "Power-Managed Modes"**.

Whenever the Timer1 oscillator is providing the clock source, the Timer1 system clock status flag, T1RUN (T1CON<6>), is set. This can be used to determine the controller's current clocking mode. It can also indicate the clock source being currently used by the Fail-Safe Clock Monitor. If the Clock Monitor is enabled and the Timer1 oscillator fails while providing the clock, polling the T1RUN bit will indicate whether the clock is being provided by the Timer1 oscillator or another source.

# 13.3.2 LOW-POWER TIMER1 OPTION

The Timer1 oscillator can operate at two distinct levels of power consumption based on device configuration. When the LPT1OSC Configuration bit is set, the Timer1 oscillator operates in a low-power mode. When LPT1OSC is not set, Timer1 operates at a higher power level. Power consumption for a particular mode is relatively constant, regardless of the device's operating mode. The default Timer1 configuration is the higher power mode.

As the low-power Timer1 mode tends to be more sensitive to interference, high noise environments may cause some oscillator instability. The low-power option is, therefore, best suited for low noise applications where power conservation is an important design consideration.

# 16.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

#### 16.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers 1, 2 or 3, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode.

# TABLE 16-1:CCP MODE – TIMER<br/>RESOURCES

| CCP/ECCP Mode | Timer Resource   |

|---------------|------------------|

| Capture       | Timer1 or Timer3 |

| Compare       | Timer1 or Timer3 |

| PWM           | Timer2           |

The assignment of a particular timer to a module is determined by the Timer to CCP enable bits in the T3CON register (Register 15-1). Both modules may be active at any given time and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time. The interactions between the two modules are summarized in Figure 16-1 and Figure 16-2. In Timer1 in Asynchronous Counter mode, the capture operation will not work.

## 16.1.2 CCP2 PIN ASSIGNMENT

The pin assignment for CCP2 (Capture input, Compare and PWM output) can change, based on device configuration. The CCP2MX Configuration bit determines which pin CCP2 is multiplexed to. By default, it is assigned to RC1 (CCP2MX = 1). If the Configuration bit is cleared, CCP2 is multiplexed with RB3.

Changing the pin assignment of CCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for CCP2 operation, regardless of where it is located.

| CCP1 Mode          | CCP2 Mode          | Interaction                                                                                                                                                                                                                                                         |

|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capture            | Capture            | Each module can use TMR1 or TMR3 as the time base. The time base can be different for each CCP.                                                                                                                                                                     |

| Capture            | Compare            | CCP2 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Automatic A/D conversions on trigger event can also be done. Operation of CCP1 could be affected if it is using the same timer as a time base. |

| Compare            | Capture            | CCP1 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Operation of CCP2 could be affected if it is using the same timer as a time base.                                                              |

| Compare            | Compare            | Either module can be configured for the Special Event Trigger to reset the time base.<br>Automatic A/D conversions on CCP2 trigger event can be done. Conflicts may occur if<br>both modules are using the same time base.                                          |

| Capture            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| Compare            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Capture            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Compare            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | PWM                | Both PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                                                                                                                                            |

# TABLE 16-2: INTERACTIONS BETWEEN CCP1 AND CCP2 FOR TIMER RESOURCES

**Note 1:** Includes standard and Enhanced PWM operation.

# 17.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The PWM duty cycle is calculated by the following equation.

#### EQUATION 17-2:

| PWM Duty Cycle = | (CCPR1L:CCP1CON<5:4>) •      |

|------------------|------------------------------|

|                  | Tosc • (TMR2 Prescale Value) |

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not copied into CCPR1H until a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation. When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or two bits of the TMR2 prescaler, the CCP1 pin is cleared. The maximum PWM resolution (bits) for a given PWM frequency is given by the following equation.

#### **EQUATION 17-3:**

PWM Resolution (max) =

$$\frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

# 17.4.3 PWM OUTPUT CONFIGURATIONS

The P1M<1:0> bits in the CCP1CON register allow one of four configurations:

- Single Output

- Half-Bridge Output

- Full-Bridge Output, Forward mode

- Full-Bridge Output, Reverse mode

The Single Output mode is the standard PWM mode discussed in **Section 17.4 "Enhanced PWM Mode"**. The Half-Bridge and Full-Bridge Output modes are covered in detail in the sections that follow.

The general relationship of the outputs in all configurations is summarized in Figure 17-2.

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8          | 7          | 6.58       |

TABLE 17-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

|       | R/W-0                            |                                                                                    |                            |                                  |                                 |                                |                                 |                    |

|-------|----------------------------------|------------------------------------------------------------------------------------|----------------------------|----------------------------------|---------------------------------|--------------------------------|---------------------------------|--------------------|

|       | 10110                            | R/W-0                                                                              | R/W-0                      | R/W-0                            | R/W-0                           | R/W-0                          | R/W-0                           | R/W-0              |

|       | GCEN                             | ACKSTAT                                                                            | ACKDT/<br>ADMSK5           | ACKEN <sup>(1)</sup> /<br>ADMSK4 | RCEN <sup>(1)</sup> /<br>ADMSK3 | PEN <sup>(1)</sup> /<br>ADMSK2 | RSEN <sup>(1)</sup> /<br>ADMSK1 | SEN <sup>(1)</sup> |

|       | bit 7                            |                                                                                    |                            |                                  |                                 |                                |                                 | bit 0              |

| bit 7 | 1 = Enable                       | eneral Call Er<br>e interrupt wh<br>al call addres                                 | en a general               |                                  |                                 | received in                    | the SSPSR                       |                    |

| bit 6 | 1 = Ackno                        | : Acknowledg<br>wledge was r<br>wledge was r                                       | not received               | from slave                       | smit mode (                     | only)                          |                                 |                    |

| bit 5 | In Master                        | <b>DMSK5:</b> Ack<br><u>Receive mod</u><br>knowledge<br>wledge                     | -                          | ata bit                          |                                 |                                |                                 |                    |

|       | Note:                            | Value that v<br>the end of a                                                       |                            | nitted when th                   | ne user initia                  | ates an Ack                    | nowledge s                      | equence at         |

|       |                                  | <u>iode:</u><br>ss masking o<br>ss masking o                                       |                            |                                  |                                 |                                |                                 |                    |

| bit 4 | ACKEN/A                          | DMSK4: Ack                                                                         | nowledge Se                | equence Ena                      | ble bit                         |                                |                                 |                    |

|       | 1 = Initiate<br>Auton            | Receive mod<br>e Acknowled<br>natically clear<br>owledge sequ                      | ge sequence<br>ed by hardw |                                  | nd SCL pir                      | ns and tran                    | smit ACKD                       | T data bit.        |

|       | In Slave m                       |                                                                                    | f ADD4 enab                |                                  |                                 |                                |                                 |                    |

| bit 3 |                                  | MSK3: Rece                                                                         |                            | it                               |                                 |                                |                                 |                    |

|       |                                  | <u>Receive mod</u><br>es Receive m<br>/e Idle                                      |                            |                                  |                                 |                                |                                 |                    |

|       |                                  | <u>iode:</u><br>ss masking o<br>ss masking o                                       |                            |                                  |                                 |                                |                                 |                    |

| bit 2 | PEN/ADM                          | SK2: Stop Co                                                                       | ondition Ena               | ble bit                          |                                 |                                |                                 |                    |

|       |                                  | <u>mode:</u> ( <sup>1)</sup><br>Stop condition<br>ondition Idle                    | on on SDA a                | nd SCL pins.                     | Automatica                      | ally cleared                   | by hardwar                      | e.                 |

|       |                                  | <u>iode:</u><br>ss masking o<br>ss masking o                                       |                            |                                  |                                 |                                |                                 |                    |

| bit 1 | <u>In Master</u><br>1 = Initiate | <b>MSK1:</b> Repe<br><u>mode:</u> <sup>(1)</sup><br>e Repeated S<br>ated Start cor | tart condition             |                                  |                                 | utomaticall                    | y cleared by                    | hardware.          |

|       | 1 = Addres                       | node (7-Bit Ac<br>ss masking o<br>ss masking o                                     | f ADD1 enab                | oled                             |                                 |                                |                                 |                    |

#### REGISTER 18-5: SSPCON2: MSSP CONTROL REGISTER 2 (I<sup>2</sup>C<sup>™</sup> MODE)

In Slave mode (10-Bit Addressing mode):

0 = Address masking of ADD1 and ADD0 disabled

# PIC18F2221/2321/4221/4321 FAMILY

# 22.0 COMPARATOR VOLTAGE REFERENCE MODULE

The comparator voltage reference is a 16-tap resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it may also be used independently of them.

A block diagram of the module is shown in Figure 22-1. The resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference.

## 22.1 Configuring the Comparator Voltage Reference

The voltage reference module is controlled through the CVRCON register (Register 22-1). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The range to be

used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF selection bits (CVR<3:0>), with one range offering finer resolution. The equations used to calculate the output of the comparator voltage reference are as follows:

<u>If CVRR = 1:</u> CVREF = ((CVR<3:0>)/24) x CVRSRC <u>If CVRR = 0:</u> CVREF = (CVRSRC x 1/4) + (((CVR<3:0>)/32) x CVRSRC)

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF- that are multiplexed with RA2 and RA3. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 27-3 in **Section 27.0 "Electrical Characteristics"**).

#### **REGISTER 22-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER**

|         | R/W-0                                                       | R/W-0                                          | R/W-0       | R/W-0                    | R/W-0                  | R/W-0       | R/W-0          | R/W-0  |  |  |  |

|---------|-------------------------------------------------------------|------------------------------------------------|-------------|--------------------------|------------------------|-------------|----------------|--------|--|--|--|

|         | CVREN                                                       | CVROE <sup>(1)</sup>                           | CVRR        | CVRSS                    | CVR3                   | CVR2        | CVR1           | CVR0   |  |  |  |

|         | bit 7                                                       |                                                |             |                          |                        |             |                | bit 0  |  |  |  |

|         |                                                             |                                                |             |                          |                        |             |                |        |  |  |  |

| bit 7   |                                                             | CVREN: Comparator Voltage Reference Enable bit |             |                          |                        |             |                |        |  |  |  |

|         |                                                             | F circuit powe<br>F circuit powe               |             |                          |                        |             |                |        |  |  |  |

| bit 6   | CVROE: C                                                    | Comparator V                                   | REF Output  | Enable bit <sup>(1</sup> | )                      |             |                |        |  |  |  |

|         |                                                             | F voltage leve                                 |             |                          |                        |             |                |        |  |  |  |

|         |                                                             | F voltage is d                                 |             |                          |                        | EF-/CVREF p | in             |        |  |  |  |

|         | Note 1:                                                     | CVROE ove                                      | errides the | TRISA<2> b               | it setting.            |             |                |        |  |  |  |

| bit 5   | CVRR: Co                                                    | mparator VR                                    | EF Range S  | election bit             |                        |             |                |        |  |  |  |

|         |                                                             | CVRSRC to 0.0<br>CVRSRC to 0.3                 |             | •                        |                        | · ·         | 0,             |        |  |  |  |

| bit 4   | CVRSS: C                                                    | comparator V                                   | REF Source  | Selection b              | it                     |             |                |        |  |  |  |

|         |                                                             | arator refere<br>arator refere                 |             |                          | . , .                  | /REF-)      |                |        |  |  |  |

| bit 3-0 | CVR<3:0>                                                    | : Comparato                                    | r VREF Valu | e Selection              | bits ( $0 \le (C^{1})$ | √R<3:0>) ≤  | 15)            |        |  |  |  |

|         | <u>When CVRR = 1:</u><br>CVREF = ((CVR<3:0>)/24) ● (CVRSRC) |                                                |             |                          |                        |             |                |        |  |  |  |

|         | When CVRR = 0:                                              |                                                |             |                          |                        |             |                |        |  |  |  |

|         | $CVREF = (CVRSRC/4) + ((CVR<3:0>)/32) \bullet (CVRSRC)$     |                                                |             |                          |                        |             |                |        |  |  |  |

|         | <b></b>                                                     |                                                |             |                          |                        |             |                |        |  |  |  |

|         | Legend:                                                     |                                                |             |                          |                        |             |                |        |  |  |  |

|         | R = Reada                                                   |                                                |             | ritable bit              |                        |             | bit, read as ' |        |  |  |  |

|         | -n = Value                                                  | at POR                                         | '1' = B     | it is set                | '0' = Bit i            | s cleared   | x = Bit is ur  | nknown |  |  |  |

# 24.0 SPECIAL FEATURES OF THE CPU

PIC18F2221/2321/4221/4321 family devices include several features intended to maximize reliability and minimize cost through elimination of external components. These are:

- Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- · Fail-Safe Clock Monitor

- · Two-Speed Start-up

- Code Protection

- ID Locations

- · In-Circuit Serial Programming

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in **Section 3.0 "Oscillator Configurations"**.

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, PIC18F2221/2321/4221/ 4321 family devices have a Watchdog Timer, which is either permanently enabled via the Configuration bits or software controlled (if configured as disabled). The inclusion of an internal RC oscillator also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

# 24.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFFh), which can only be accessed using table reads and table writes.

Programming the Configuration registers is done in a manner similar to programming the Flash memory. The WR bit in the EECON1 register starts a self-timed write to the Configuration register. In normal operation mode, a TBLWT instruction with the TBLPTR pointing to the Configuration register sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 7.5 "Writing to Flash Program Memory".

|         |                       |       |       |        |        | •      |         |        | 1      |                                   |

|---------|-----------------------|-------|-------|--------|--------|--------|---------|--------|--------|-----------------------------------|

| File    | Name                  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value |

| 300001h | CONFIG1H              | IESO  | FCMEN | —      | —      | FOSC3  | FOSC2   | FOSC1  | FOSC0  | 00 0111                           |

| 300002h | CONFIG2L              | —     | -     | _      | BORV1  | BORV0  | BOREN1  | BOREN0 | PWRTEN | 1 1111                            |

| 300003h | CONFIG2H              | —     |       |        | WDTPS3 | WDTPS2 | WDTPS1  | WDTPS0 | WDTEN  | 1 1111                            |

| 300005h | CONFIG3H              | MCLRE |       |        |        |        | LPT10SC | PBADEN | CCP2MX | 1011                              |

| 300006h | CONFIG4L              | DEBUG | XINST | BBSIZ1 | BBSIZ0 | r      | LVP     | —      | STVREN | 1000 01-1                         |

| 300008h | CONFIG5L              | _     |       |        |        |        | _       | CP1    | CP0    | 11                                |

| 300009h | CONFIG5H              | CPD   | CPB   |        |        |        | —       |        | _      | 11                                |

| 30000Ah | CONFIG6L              | —     |       |        |        |        | —       | WRT1   | WRT0   | 11                                |

| 30000Bh | CONFIG6H              | WRTD  | WRTB  | WRTC   |        |        | —       |        | _      | 111                               |

| 30000Ch | CONFIG7L              | —     |       |        |        |        | —       | EBTR1  | EBTR0  | 11                                |

| 30000Dh | CONFIG7H              | _     | EBTRB |        | _      | _      | _       | _      | _      | -1                                |

| 3FFFFEh | DEVID1 <sup>(1)</sup> | DEV2  | DEV1  | DEV0   | REV4   | REV3   | REV2    | REV1   | REV0   | ×××× ×××××(2)                     |

| 3FFFFFh | DEVID2 <sup>(1)</sup> | DEV10 | DEV9  | DEV8   | DEV7   | DEV6   | DEV5    | DEV4   | DEV3   | 0000 1100                         |

TABLE 24-1: CONFIGURATION BITS AND DEVICE IDs

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved, maintain as '0'. Shaded cells are unimplemented, read as '0'.

Note 1: Unimplemented in PIC18F2221/4221 devices; maintain these bits set.

2: See Register 24-14 for DEVID1 values. DEVID registers are read-only and cannot be programmed by the user.

# PIC18F2221/2321/4221/4321 FAMILY

| BNC                           | <b>N</b>                                 | Branch if                                                                                | Not Overflo                                                                                                                                                                                                                                                                                | w               |  |  |  |  |  |

|-------------------------------|------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Synta                         | ax:                                      | BNOV n                                                                                   | BNOV n                                                                                                                                                                                                                                                                                     |                 |  |  |  |  |  |

| Oper                          | ands:                                    | -128 ≤ n ≤ 1                                                                             | 27                                                                                                                                                                                                                                                                                         |                 |  |  |  |  |  |

| Oper                          | ation:                                   | If Overflow<br>(PC) + 2 + 2                                                              | ,                                                                                                                                                                                                                                                                                          |                 |  |  |  |  |  |

| Statu                         | s Affected:                              | None                                                                                     |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |  |

| Enco                          | oding:                                   | 1110                                                                                     | 0101 nnr                                                                                                                                                                                                                                                                                   | in nnnn         |  |  |  |  |  |

| Desc                          | ription:                                 | program wil<br>The 2's con<br>added to the<br>incremented<br>instruction,<br>PC + 2 + 2r | If the Overflow bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |                 |  |  |  |  |  |

| Word                          | ls:                                      | 1                                                                                        |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |  |

| Cycle                         | es:                                      | 1(2)                                                                                     |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |  |

| Q Cycle Activity:<br>If Jump: |                                          |                                                                                          |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |  |

|                               | Q1                                       | Q2                                                                                       | Q3                                                                                                                                                                                                                                                                                         | Q4              |  |  |  |  |  |

|                               | Decode                                   | Read literal<br>'n'                                                                      | Process<br>Data                                                                                                                                                                                                                                                                            | Write to<br>PC  |  |  |  |  |  |

|                               | No<br>operation                          | No<br>operation                                                                          | No<br>operation                                                                                                                                                                                                                                                                            | No<br>operation |  |  |  |  |  |

| lf No                         | o Jump:                                  |                                                                                          |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |  |

|                               | Q1                                       | Q2                                                                                       | Q3                                                                                                                                                                                                                                                                                         | Q4              |  |  |  |  |  |

|                               | Decode                                   | Read literal<br>'n'                                                                      | Process<br>Data                                                                                                                                                                                                                                                                            | No<br>operation |  |  |  |  |  |

| <u>Exan</u>                   | •                                        | HERE                                                                                     | BNOV Jump                                                                                                                                                                                                                                                                                  |                 |  |  |  |  |  |

|                               | Before Instruc<br>PC<br>After Instructio | = ade                                                                                    | dress (HERE)                                                                                                                                                                                                                                                                               |                 |  |  |  |  |  |

|                               | If Overflo<br>P(<br>If Overflo<br>P(     | C = ade<br>w = 1;                                                                        | dress (Jump)<br>dress (HERE                                                                                                                                                                                                                                                                |                 |  |  |  |  |  |

| BNZ                                                                                                                                                                                                                                                                                              |                                                                                                     | Branch if                      | Branch if Not Zero       |                 |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------|--------------------------|-----------------|--|--|--|--|--|--|

| Synta                                                                                                                                                                                                                                                                                            | ax:                                                                                                 | BNZ n                          |                          |                 |  |  |  |  |  |  |

| Opera                                                                                                                                                                                                                                                                                            | ands:                                                                                               | $-128 \le n \le 1$             | 127                      |                 |  |  |  |  |  |  |

| Opera                                                                                                                                                                                                                                                                                            | ation:                                                                                              | If Zero bit is<br>(PC) + 2 + 2 | ,                        |                 |  |  |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                            | s Affected:                                                                                         | None                           |                          |                 |  |  |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                             | ding:                                                                                               | 1110                           | 0001 nn:                 | nn nnnn         |  |  |  |  |  |  |

| Description:<br>If the Zero bit is '0', then the progra<br>will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will h<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is ther<br>two-cycle instruction. |                                                                                                     |                                |                          |                 |  |  |  |  |  |  |

| Word                                                                                                                                                                                                                                                                                             | s:                                                                                                  | 1                              | 1                        |                 |  |  |  |  |  |  |

| Cycle                                                                                                                                                                                                                                                                                            | es:                                                                                                 | 1(2)                           |                          |                 |  |  |  |  |  |  |

| Q Cy<br>If Ju                                                                                                                                                                                                                                                                                    | ycle Activity:<br>mp:                                                                               |                                |                          |                 |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                  | Q1                                                                                                  | Q2                             | Q3                       | Q4              |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                  | Decode                                                                                              | Read literal<br>'n'            | Process<br>Data          | Write to<br>PC  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                  | No<br>operation                                                                                     | No<br>operation                | No<br>operation          | No<br>operation |  |  |  |  |  |  |