Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2321-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: DEVICE FEAT                   | URES                                                                                                         | 1                                                                                                            | 1                                                                                                            |                                                                                                              |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Features                                 | PIC18F2221                                                                                                   | PIC18F2321                                                                                                   | PIC18F4221                                                                                                   | PIC18F4321                                                                                                   |

| Operating Frequency                      | DC – 40 MHz                                                                                                  |

| Program Memory (Bytes)                   | 4096                                                                                                         | 8192                                                                                                         | 4096                                                                                                         | 8192                                                                                                         |

| Program Memory (Instructions)            | 2048                                                                                                         | 4096                                                                                                         | 2048                                                                                                         | 4096                                                                                                         |

| Data Memory (Bytes)                      | 512                                                                                                          | 512                                                                                                          | 512                                                                                                          | 512                                                                                                          |

| Data EEPROM Memory (Bytes)               | 256                                                                                                          | 256                                                                                                          | 256                                                                                                          | 256                                                                                                          |

| Interrupt Sources                        | 19                                                                                                           | 19                                                                                                           | 20                                                                                                           | 20                                                                                                           |

| I/O Ports                                | Ports A, B, C, (E)                                                                                           | Ports A, B, C, (E)                                                                                           | Ports A, B, C, D, E                                                                                          | Ports A, B, C, D, E                                                                                          |

| Timers                                   | 4                                                                                                            | 4                                                                                                            | 4                                                                                                            | 4                                                                                                            |

| Capture/Compare/PWM Modules              | 2                                                                                                            | 2                                                                                                            | 1                                                                                                            | 1                                                                                                            |

| Enhanced Capture/Compare/<br>PWM Modules | 0                                                                                                            | 0                                                                                                            | 1                                                                                                            | 1                                                                                                            |

| Serial Communications                    | MSSP,<br>Enhanced USART                                                                                      | MSSP,<br>Enhanced USART                                                                                      | MSSP,<br>Enhanced USART                                                                                      | MSSP,<br>Enhanced USART                                                                                      |

| Parallel Communications (PSP)            | No                                                                                                           | No                                                                                                           | Yes                                                                                                          | Yes                                                                                                          |

| 10-bit Analog-to-Digital Module          | 10 Input Channels                                                                                            | 10 Input Channels                                                                                            | 13 Input Channels                                                                                            | 13 Input Channels                                                                                            |

| Resets (and Delays)                      | POR, BOR,<br>RESET Instruction,<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST),<br>MCLR (optional),<br>WDT |

| Programmable Low-Voltage<br>Detect       | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          |

| Programmable Brown-out Reset             | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          |

| Instruction Set                          | 75 Instructions;<br>83 with Extended<br>Instruction Set<br>enabled                                           |

| Packages                                 | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN                                                     | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN                                                     | 40-pin PDIP<br>44-pin QFN<br>44-pin TQFP                                                                     | 40-pin PDIP<br>44-pin QFN<br>44-pin TQFP                                                                     |

### TABLE 1-1: DEVICE FEATURES

| TABLE 1-3: PIC1                                        |            |            |         | 1 1/01          | JESCRI    |                                                                                                                                                                                       |

|--------------------------------------------------------|------------|------------|---------|-----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                               | Pi         | Pin Number |         | Pin             |           | Description                                                                                                                                                                           |

|                                                        | PDIP       | QFN        | TQFP    | Туре            | Туре      | Description                                                                                                                                                                           |

|                                                        |            |            |         |                 |           | PORTD is a bidirectional I/O port or a Parallel Slave<br>Port (PSP) for interfacing to a microprocessor port.<br>These pins have TTL input buffers when the PSP<br>module is enabled. |

| RD0/PSP0<br>RD0<br>PSP0                                | 19         | 38         | 38      | I/O<br>I/O      | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |

| RD1/PSP1<br>RD1<br>PSP1                                | 20         | 39         | 39      | I/O<br>I/O      | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |

| RD2/PSP2<br>RD2<br>PSP2                                | 21         | 40         | 40      | I/O<br>I/O      | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |

| RD3/PSP3<br>RD3<br>PSP3                                | 22         | 41         | 41      | I/O<br>I/O      | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |

| RD4/PSP4<br>RD4<br>PSP4                                | 27         | 2          | 2       | I/O<br>I/O      | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |

| RD5/PSP5/P1B<br>RD5<br>PSP5<br>P1B                     | 28         | 3          | 3       | I/O<br>I/O<br>O | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                    |

| RD6/PSP6/P1C<br>RD6<br>PSP6<br>P1C                     | 29         | 4          | 4       | I/O<br>I/O<br>O | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                    |

| RD7/PSP7/P1D<br>RD7<br>PSP7<br>P1D                     | 30         | 5          | 5       | I/O<br>I/O<br>O | ST<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                    |

| <b>Legend:</b> TTL = TTL<br>ST = Schr<br>$I^2C$ = ST w | nitt Trigg | er input   | with CN | /IOS lev        | /els      | CMOS = CMOS compatible input or output<br>I = Input P = Power<br>O = Output                                                                                                           |

### TABLE 1-3: PIC18F4221/4321 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

## 3.7.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 3-2) controls several aspects of the device clock's operation, both in full power operation and in power-managed modes.

The System Clock Select bits, SCS<1:0>, select the clock source. The available clock sources are the primary clock (defined by the FOSC<3:0> Configuration bits), the secondary clock (Timer1 oscillator) and the internal oscillator block. The clock source changes immediately after either of the SCS<1:0> bits are changed, following a brief clock transition interval. The SCS bits are reset on all forms of Reset.

The Internal Oscillator Frequency Select bits (IRCF<2:0>) select the frequency output of the internal oscillator block to drive the device clock. The choices are the INTRC source (31 kHz), the INTOSC source (8 MHz) or one of the frequencies derived from the INTOSC postscaler (31.25 kHz to 4 MHz). If the internal oscillator block is supplying the device clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the default output frequency of the internal oscillator block is set at 1 MHz.

When a nominal output frequency of 31 kHz is selected (IRCF<2:0> = 000), users may choose which internal oscillator acts as the source. This is done with the INTSRC bit in the OSCTUNE register (OSCTUNE<7>). Setting this bit selects INTOSC as a 31.25 kHz clock source derived from the INTOSC postscaler. Clearing INTSRC selects INTRC (nominally 31 kHz) as the clock source and disables the INTOSC to reduce current consumption.

This option allows users to select the tunable and more precise INTOSC as a clock source, while maintaining power savings with a very low clock speed. Additionally, the INTOSC source will already be stable should a switch to a higher frequency be needed quickly. Regardless of the setting of INTSRC, INTRC always remains the clock source for features such as the Watchdog Timer and the Fail-Safe Clock Monitor.

The OSTS, IOFS and T1RUN bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer and PLL Start-up Timer (if enabled) have timed out and the primary clock is providing the device clock in primary clock modes. The IOFS bit indicates when the internal oscillator block has stabilized and is providing the device clock in RC Clock modes. The T1RUN bit (T1CON<6>) indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these three bits will be set at any time. If none of these bits are set, the INTRC is providing the clock or the internal oscillator block has just started and is not yet stable.

The IDLEN bit controls whether the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 4.0** "**Power-Managed Modes**".

| Note 1: | The Timer1 oscillator must be enabled to    |  |  |  |  |  |  |  |  |

|---------|---------------------------------------------|--|--|--|--|--|--|--|--|

|         | select the secondary clock source. The      |  |  |  |  |  |  |  |  |

|         | Timer1 oscillator is enabled by setting the |  |  |  |  |  |  |  |  |

|         | T1OSCEN bit in the Timer1 Control regis-    |  |  |  |  |  |  |  |  |

|         | ter (T1CON<3>). If the Timer1 oscillator    |  |  |  |  |  |  |  |  |

|         | is not enabled, then any attempt to select  |  |  |  |  |  |  |  |  |

|         | a secondary clock source will be ignored.   |  |  |  |  |  |  |  |  |

| 2:      | It is recommended that the Timer1           |  |  |  |  |  |  |  |  |

2: It is recommended that the Timer1 oscillator be operating and stable before selecting the secondary clock source or a very long delay may occur while the Timer1 oscillator starts.

### 3.7.2 OSCILLATOR TRANSITIONS

The PIC18F2221/2321/4221/4321 family of devices contains circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 4.1.2 "Entering Power-Managed Modes"**.

#### 6.0 MEMORY ORGANIZATION

There are three types of memory in PIC18 Enhanced microcontroller devices:

- Program Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device, since it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Flash program memory is provided in Section 7.0 "Flash Program Memory". Data EEPROM is discussed separately in Section 8.0 "Data EEPROM Memory".

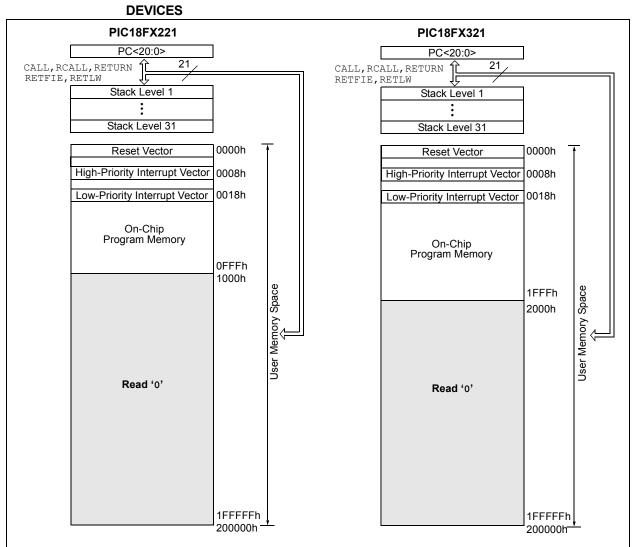

#### 6.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

The PIC18F2221 and PIC18F4221 each have 4 Kbytes of Flash memory and can store up to 2048 single-word instructions. The PIC18F2321 and PIC18F4321 each have 8 Kbytes of Flash memory and can store up to 4096 single-word instructions.

PIC18 devices have two interrupt vectors. The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

The program memory maps for PIC18F2221/4221 and PIC18F2321/4321 devices are shown in Figure 6-1.

FIGURE 6-1: PROGRAM MEMORY MAP AND STACK FOR PIC18F2221/2321/4221/4321 FAMILY

NOTES:

| Name    | Bit 7                                   | Bit 6                 | Bit 5        | Bit 4     | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|-----------------------------------------|-----------------------|--------------|-----------|---------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                | PEIE/GIEL             | TMR0IE       | INT0IE    | RBIE    | TMR0IF | INT0IF | RBIF   | 55                         |

| RCON    | IPEN                                    | SBOREN <sup>(1)</sup> | _            | RI        | TO      | PD     | POR    | BOR    | 54                         |

| PIR1    | PSPIF <sup>(2)</sup>                    | ADIF                  | RCIF         | TXIF      | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1    | PSPIE <sup>(2)</sup>                    | ADIE                  | RCIE         | TXIE      | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1    | PSPIP <sup>(2)</sup>                    | ADIP                  | RCIP         | TXIP      | SSPIP   | CCP1IP | TMR2IP | TMR1IP | 58                         |

| PIR2    | OSCFIF                                  | CMIF                  | —            | EEIF      | BCLIF   | HLVDIF | TMR3IF | CCP2IF | 58                         |

| PIE2    | OSCFIE                                  | CMIE                  | _            | EEIE      | BCLIE   | HLVDIE | TMR3IE | CCP2IE | 58                         |

| IPR2    | OSCFIP                                  | CMIP                  | —            | EEIP      | BCLIP   | HLVDIP | TMR3IP | CCP2IP | 58                         |

| TRISB   | PORTB Data Direction Register           |                       |              |           |         |        |        |        |                            |

| TRISC   | PORTC Data Direction Register           |                       |              |           |         |        |        |        | 58                         |

| TMR1L   | Timer1 Reg                              | gister Low By         | /te          |           |         |        |        |        | 56                         |

| TMR1H   | Timer1 Reg                              | gister High B         | yte          |           |         |        |        |        | 56                         |

| T1CON   | RD16                                    | T1RUN                 | T1CKPS1      | T1CKPS0   | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 56                         |

| TMR3H   | Timer3 Reg                              | gister High B         | yte          |           |         |        |        |        | 57                         |

| TMR3L   | Timer3 Reg                              | gister Low B          | /te          |           |         |        |        |        | 57                         |

| T3CON   | RD16                                    | T3CCP2                | T3CKPS1      | T3CKPS0   | T3CCP1  | T3SYNC | TMR3CS | TMR3ON | 57                         |

| CCPR1L  | Capture/Co                              | mpare/PWN             | 1 Register 1 | Low Byte  |         |        |        |        | 57                         |

| CCPR1H  | Capture/Co                              | mpare/PWN             | 1 Register 1 | High Byte |         |        |        |        | 57                         |

| CCP1CON | P1M1 <sup>(2)</sup>                     | P1M0 <sup>(2)</sup>   | DC1B1        | DC1B0     | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0 | 57                         |

| CCPR2L  | Capture/Compare/PWM Register 2 Low Byte |                       |              |           |         |        |        |        | 57                         |

| CCPR2H  | Capture/Co                              | mpare/PWN             | 1 Register 2 | High Byte |         |        |        |        | 57                         |

| CCP2CON | _                                       | _                     | DC2B1        | DC2B0     | CCP2M3  | CCP2M2 | CCP2M1 | CCP2M0 | 57                         |

| TABLE 16-3: | <b>REGISTERS ASSOCIATED WITH CAPTURE</b> | COMPARE, TIMER1 AND TIMER3 |

|-------------|------------------------------------------|----------------------------|

|             |                                          |                            |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by Capture/Compare, Timer1 or Timer3.

Note 1: The SBOREN bit is only available when the BOREN<1:0> Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

**2:** These bits are unimplemented on 28-pin devices and read as '0'.

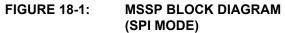

## 18.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

#### 18.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with address masking for both 10-bit and 7-bit addressing)

The  $\mathrm{I}^2\mathrm{C}$  interface supports the following modes in hardware:

- · Master mode

- Multi-Master mode

- Slave mode

### 18.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON1 and SSPCON2). The use of these registers and their individual Configuration bits differ significantly depending on whether the MSSP module is operated in SPI or I<sup>2</sup>C mode.

Additional details are provided under the individual sections.

#### 18.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four SPI modes are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) SDO

- Serial Data In (SDI) SDI/SDA

- Serial Clock (SCK) SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

• Slave Select (SS)

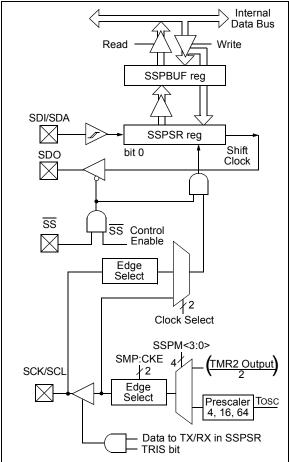

Figure 18-1 shows the block diagram of the MSSP module when operating in SPI mode.

#### 18.3.3 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, reinitialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISA<5> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

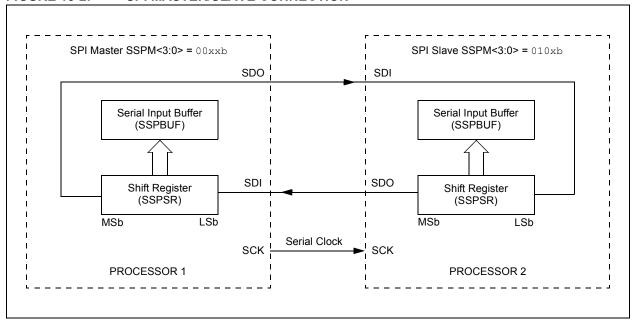

#### 18.3.4 TYPICAL CONNECTION

Figure 18-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- Master sends data Slave sends data

- · Master sends dummy data Slave sends data

#### FIGURE 18-2: SPI MASTER/SLAVE CONNECTION

#### 18.4.2 OPERATION

The MSSP module functions are enabled by setting MSSP Enable bit, SSPEN (SSPCON1<5>).

The SSPCON1 register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON1<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode clock

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

#### 18.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The I<sup>2</sup>C Slave mode hardware will always generate an interrupt on an address match. Address masking will allow the hardware to generate an interrupt for more than one address (up to 31 in 7-Bit Addressing mode and up to 63 in 10-Bit Addressing mode). Through the mode select bits, the user can also choose to interrupt on Start and Stop bits

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overrightarrow{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON1<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

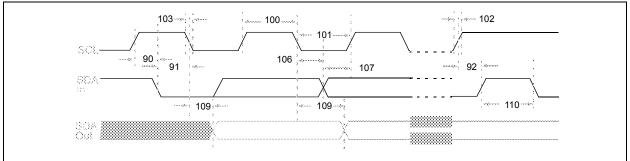

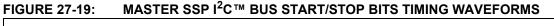

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter 100 and parameter 101.

#### 18.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. MSSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated, if enabled) on the falling edge of the ninth SCL pulse.

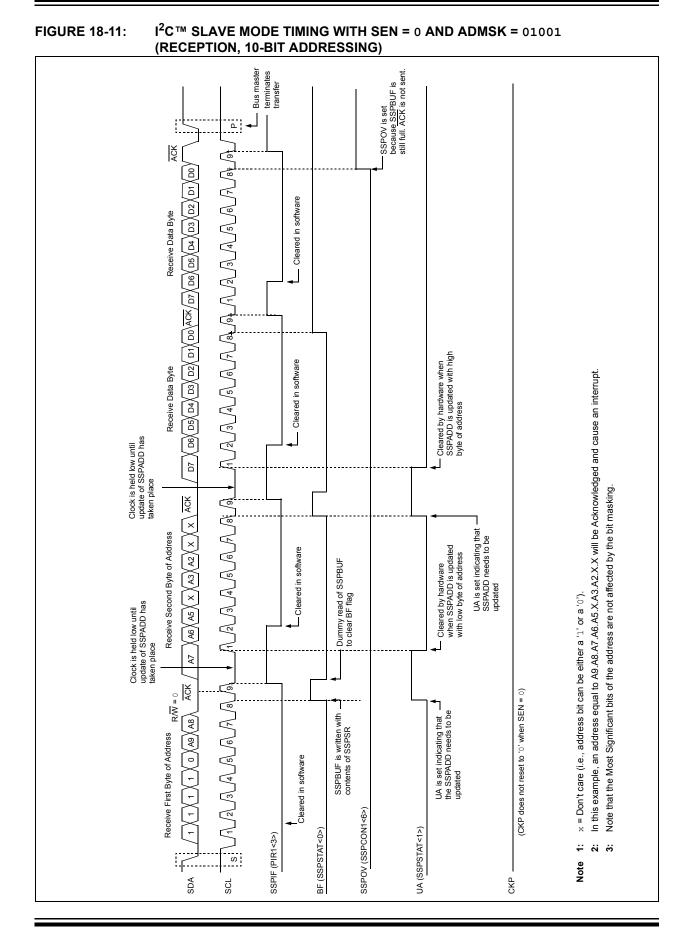

In 10-Bit Addressing mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

© 2009 Microchip Technology Inc.

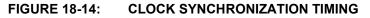

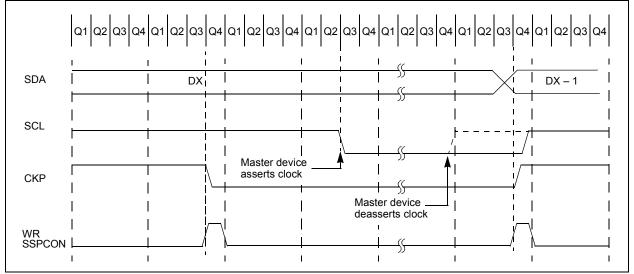

# 18.4.4.5 Clock Synchronization and the CKP bit

When the CKP bit is cleared, the SCL output is forced to '0'. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has

already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2$ C bus have deasserted SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 18-14).

| REGISTER 19-2: | RCSTA: R                        |                                                                                   | TATUS AN       |                |              | TER           |              |              |  |  |

|----------------|---------------------------------|-----------------------------------------------------------------------------------|----------------|----------------|--------------|---------------|--------------|--------------|--|--|

|                | R/W-0                           | R/W-0                                                                             | R/W-0          | R/W-0          | R/W-0        | R-0           | R-0          | R-x          |  |  |

|                | SPEN                            | RX9                                                                               | SREN           | CREN           | ADDEN        | FERR          | OERR         | RX9D         |  |  |

|                | bit 7                           |                                                                                   |                |                |              |               |              | bit 0        |  |  |

| bit 7          |                                 | ial Dart Enal                                                                     | bla bit        |                |              |               |              |              |  |  |

| bit 7          |                                 | ial Port Enal                                                                     |                | DV/DT and      | TV/CK pipe   | an aprial pa  | rt nina)     |              |  |  |

|                |                                 | oort disabled                                                                     |                |                | TX/CK pins   | as senai po   | it pins)     |              |  |  |

| bit 6          | <b>RX9:</b> 9-bit               | Receive Ena                                                                       | able bit       |                |              |               |              |              |  |  |

|                |                                 | <ul><li>1 = Selects 9-bit reception</li><li>0 = Selects 8-bit reception</li></ul> |                |                |              |               |              |              |  |  |

| bit 5          | SREN: Sin                       | gle Receive                                                                       | Enable bit     |                |              |               |              |              |  |  |

|                | <u>Asynchron</u><br>Don't care. |                                                                                   |                |                |              |               |              |              |  |  |

|                | Synchrono                       | us mode – N                                                                       | /laster:       |                |              |               |              |              |  |  |

|                |                                 | s single rece                                                                     |                |                |              |               |              |              |  |  |

|                |                                 | es single rec                                                                     |                |                |              |               |              |              |  |  |

|                |                                 | leared after                                                                      | -              | complete.      |              |               |              |              |  |  |

|                | Don't care.                     | <u>us mode – S</u>                                                                | <u>blave:</u>  |                |              |               |              |              |  |  |

| bit 4          |                                 | ntinuous Re                                                                       | ceive Enable   | e bit          |              |               |              |              |  |  |

|                | Asynchron                       |                                                                                   |                |                |              |               |              |              |  |  |

|                | 1 = Enable                      |                                                                                   |                |                |              |               |              |              |  |  |

|                | 0 = Disable                     | es receiver                                                                       |                |                |              |               |              |              |  |  |

|                | Synchrono                       |                                                                                   | · · · ·        |                | ODEN         |               |              |              |  |  |

|                |                                 | s continuous<br>es continuou                                                      |                | til enable bit | CREN is cle  | eared (CREI   | N overrides  | SREN)        |  |  |

| bit 3          |                                 | ddress Dete                                                                       |                | t              |              |               |              |              |  |  |

| bit o          |                                 | ous mode 9-                                                                       |                |                |              |               |              |              |  |  |

|                |                                 |                                                                                   |                |                | upt and load | s the receiv  | e buffer whe | en RSR<8>    |  |  |

|                | 0 = Disabl                      | es address o                                                                      | detection, all | bytes are r    | eceived and  | ninth bit car | n be used as | s parity bit |  |  |

|                |                                 | ous mode 9-                                                                       | bit (RX9 = c   | ) <u>):</u>    |              |               |              |              |  |  |

|                | Don't care.                     |                                                                                   |                |                |              |               |              |              |  |  |

| bit 2          |                                 | ming Error b                                                                      |                |                |              |               |              |              |  |  |

|                | 1 = Framin<br>0 = No fran       |                                                                                   | be updated     | by reading     | RCREG regi   | ister and rec | eiving next  | valid byte)  |  |  |

| bit 1          | OERR: OV                        | errun Error b                                                                     | pit            |                |              |               |              |              |  |  |

|                |                                 | n error (can                                                                      | be cleared b   | by clearing b  | oit CREN)    |               |              |              |  |  |

|                | 0 = No ove                      |                                                                                   |                |                |              |               |              |              |  |  |

| bit 0          |                                 | bit of Receiv                                                                     |                |                |              |               | <b>C</b>     | _            |  |  |

|                | I his can be                    | e address/da                                                                      | ata bit or a p | arity bit and  | must be cal  | culated by u  | ser tirmware | 9.           |  |  |

|                | Legend:                         |                                                                                   |                |                |              |               |              |              |  |  |

|                | R = Reada                       | ble bit                                                                           | W = W          | /ritable bit   | U = Unin     | nplemented    | bit, read as | ʻ0'          |  |  |

|                | -n = Value                      |                                                                                   | '1' = B        | it is set      |              | s cleared     | x = Bit is u |              |  |  |

|                |                                 |                                                                                   | i – D          |                |              |               |              |              |  |  |

| BNC           |                                                      | Branch if                                                                                                                                                                                                                                                                               | Not Carry                   |                 | BNN          | I                                                                      | Branch if                                                                           | Branch if Not Negative                                 |                 |  |  |

|---------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|--------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------|--|--|

| Synta         | IX:                                                  | BNC n                                                                                                                                                                                                                                                                                   |                             |                 | Synta        | ax:                                                                    | BNN n                                                                               | BNN n                                                  |                 |  |  |

| Opera         | ands:                                                | -128 ≤ n ≤ 1                                                                                                                                                                                                                                                                            | 127                         |                 | Oper         | ands:                                                                  | -128 ≤ n ≤ ′                                                                        | 127                                                    |                 |  |  |

| Opera         | ation:                                               | If Carry bit i<br>(PC) + 2 + 2                                                                                                                                                                                                                                                          |                             |                 | Oper         | ation:                                                                 | If Negative<br>(PC) + 2 +                                                           |                                                        |                 |  |  |

| Statu         | s Affected:                                          | None                                                                                                                                                                                                                                                                                    |                             |                 | Statu        | s Affected:                                                            | None                                                                                |                                                        |                 |  |  |

| Enco          | ding:                                                | 1110                                                                                                                                                                                                                                                                                    | 0011 nnr                    | nn nnnn         | Enco         | ding:                                                                  | 1110                                                                                | 0111 nn                                                | nn nnnn         |  |  |

| Desci         | ription:                                             | If the Carry bit is '0', then the program<br>will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |                             | Desc            | ription:     | program wi<br>The 2's cor<br>added to th<br>incremente<br>instruction, | nplement num<br>e PC. Since th<br>d to fetch the<br>the new addr<br>n. This instruc | nber '2n' is<br>ne PC will have<br>next<br>ess will be |                 |  |  |

| Word          | s:                                                   | 1                                                                                                                                                                                                                                                                                       |                             |                 | Word         | ls:                                                                    | 1                                                                                   |                                                        |                 |  |  |

| Cycle         | S:                                                   | 1(2)                                                                                                                                                                                                                                                                                    |                             |                 | Cycle        | es:                                                                    | 1(2)                                                                                |                                                        |                 |  |  |

| Q Cy<br>If Ju | /cle Activity:<br>mp:                                |                                                                                                                                                                                                                                                                                         |                             |                 | Q C<br>If Ju | ycle Activity:<br>mp:                                                  |                                                                                     |                                                        |                 |  |  |

| -             | Q1                                                   | Q2                                                                                                                                                                                                                                                                                      | Q3                          | Q4              |              | Q1                                                                     | Q2                                                                                  | Q3                                                     | Q4              |  |  |

|               | Decode                                               | Read literal<br>'n'                                                                                                                                                                                                                                                                     | Process<br>Data             | Write to<br>PC  |              | Decode                                                                 | Read literal<br>'n'                                                                 | Process<br>Data                                        | Write to<br>PC  |  |  |

|               | No<br>operation                                      | No<br>operation                                                                                                                                                                                                                                                                         | No<br>operation             | No<br>operation |              | No<br>operation                                                        | No<br>operation                                                                     | No<br>operation                                        | No<br>operation |  |  |

| lf No         | Jump:                                                |                                                                                                                                                                                                                                                                                         |                             |                 | lf No        | o Jump:                                                                |                                                                                     |                                                        |                 |  |  |

| r             | Q1                                                   | Q2                                                                                                                                                                                                                                                                                      | Q3                          | Q4              |              | Q1                                                                     | Q2                                                                                  | Q3                                                     | Q4              |  |  |

|               | Decode                                               | Read literal<br>'n'                                                                                                                                                                                                                                                                     | Process<br>Data             | No<br>operation |              | Decode                                                                 | Read literal<br>'n'                                                                 | Process<br>Data                                        | No<br>operation |  |  |

|               | Before Instruc<br>PC<br>After Instructio<br>If Carry | = ade<br>on<br>= 0;                                                                                                                                                                                                                                                                     | BNC Jump                    |                 |              | Before Instruc<br>PC<br>After Instructi<br>If Negati                   | = ad<br>on<br>ve = 0;                                                               | BNN Jump<br>dress (HERE                                | )               |  |  |

|               | PC<br>If Carry<br>PC                                 | = 1;                                                                                                                                                                                                                                                                                    | dress (Jump)<br>dress (HERE |                 |              | P<br>If Negati<br>P                                                    | ve = 1;                                                                             | dress (Jump<br>dress (HERE                             |                 |  |  |

| BNC                           | <b>N</b>                                 | Branch if                                                                                                                                                                                                                                                                                  | Not Overflo                 | w               |  |  |  |

|-------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|--|--|--|

| Synta                         | ax:                                      | BNOV n                                                                                                                                                                                                                                                                                     |                             |                 |  |  |  |

| Oper                          | ands:                                    | -128 ≤ n ≤ 1                                                                                                                                                                                                                                                                               | 27                          |                 |  |  |  |

| Oper                          | ation:                                   | If Overflow<br>(PC) + 2 + 2                                                                                                                                                                                                                                                                | ,                           |                 |  |  |  |

| Statu                         | s Affected:                              | None                                                                                                                                                                                                                                                                                       |                             |                 |  |  |  |

| Enco                          | oding:                                   | 1110                                                                                                                                                                                                                                                                                       | 0101 nnr                    | in nnnn         |  |  |  |

| Desc                          | ription:                                 | If the Overflow bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |                             |                 |  |  |  |

| Word                          | ls:                                      | 1                                                                                                                                                                                                                                                                                          |                             |                 |  |  |  |

| Cycle                         | es:                                      | 1(2)                                                                                                                                                                                                                                                                                       | 1(2)                        |                 |  |  |  |

| Q Cycle Activity:<br>If Jump: |                                          |                                                                                                                                                                                                                                                                                            |                             |                 |  |  |  |

|                               | Q1                                       | Q2                                                                                                                                                                                                                                                                                         | Q3                          | Q4              |  |  |  |

|                               | Decode                                   | Read literal<br>'n'                                                                                                                                                                                                                                                                        | Process<br>Data             | Write to<br>PC  |  |  |  |

|                               | No<br>operation                          | No<br>operation                                                                                                                                                                                                                                                                            | No<br>operation             | No<br>operation |  |  |  |

| lf No                         | o Jump:                                  |                                                                                                                                                                                                                                                                                            |                             |                 |  |  |  |

|                               | Q1                                       | Q2                                                                                                                                                                                                                                                                                         | Q3                          | Q4              |  |  |  |

|                               | Decode                                   | Read literal<br>'n'                                                                                                                                                                                                                                                                        | Process<br>Data             | No<br>operation |  |  |  |

| <u>Exan</u>                   | •                                        | HERE                                                                                                                                                                                                                                                                                       | BNOV Jump                   |                 |  |  |  |

|                               | Before Instruc<br>PC<br>After Instructio | = ade                                                                                                                                                                                                                                                                                      | dress (HERE)                |                 |  |  |  |

|                               | If Overflo<br>P(<br>If Overflo<br>P(     | C = ade<br>w = 1;                                                                                                                                                                                                                                                                          | dress (Jump)<br>dress (HERE |                 |  |  |  |

| BNZ           |                                                                                                     | Branch if                                                                                                                                                                                                                                                                              | Not Zero                 |                 |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------|--|--|--|--|

| Synta         | ax:                                                                                                 | BNZ n                                                                                                                                                                                                                                                                                  | BNZ n                    |                 |  |  |  |  |

| Opera         | ands:                                                                                               | $-128 \le n \le 1$                                                                                                                                                                                                                                                                     | 127                      |                 |  |  |  |  |

| Opera         | ation:                                                                                              | If Zero bit is '0',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                  |                          |                 |  |  |  |  |

| Statu         | s Affected:                                                                                         | None                                                                                                                                                                                                                                                                                   |                          |                 |  |  |  |  |

| Enco          | ding:                                                                                               | 1110                                                                                                                                                                                                                                                                                   | 0001 nn:                 | nn nnnn         |  |  |  |  |

| Desc          | ription:                                                                                            | If the Zero bit is '0', then the program<br>will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |                          |                 |  |  |  |  |

| Word          | s:                                                                                                  | 1                                                                                                                                                                                                                                                                                      |                          |                 |  |  |  |  |

| Cycle         | es:                                                                                                 | 1(2)                                                                                                                                                                                                                                                                                   |                          |                 |  |  |  |  |

| Q Cy<br>If Ju | ycle Activity:<br>mp:                                                                               |                                                                                                                                                                                                                                                                                        |                          |                 |  |  |  |  |

|               | Q1                                                                                                  | Q2                                                                                                                                                                                                                                                                                     | Q3                       | Q4              |  |  |  |  |

|               | Decode                                                                                              | Read literal<br>'n'                                                                                                                                                                                                                                                                    | Process<br>Data          | Write to<br>PC  |  |  |  |  |

|               | No<br>operation                                                                                     | No<br>operation                                                                                                                                                                                                                                                                        | No<br>operation          | No<br>operation |  |  |  |  |

| lf No         | Jump:                                                                                               |                                                                                                                                                                                                                                                                                        | •                        |                 |  |  |  |  |

| -             | Q1                                                                                                  | Q2                                                                                                                                                                                                                                                                                     | Q3                       | Q4              |  |  |  |  |

|               | Decode                                                                                              | Read literal<br>'n'                                                                                                                                                                                                                                                                    | Process<br>Data          | No<br>operation |  |  |  |  |

|               | Before Instruc<br>PC                                                                                | = ad                                                                                                                                                                                                                                                                                   | BNZ Jump<br>dress (HERE) |                 |  |  |  |  |

|               | After Instruction<br>If Zero = 0;<br>PC = address (Jump)<br>If Zero = 1;<br>PC = address (HERE + 2) |                                                                                                                                                                                                                                                                                        |                          |                 |  |  |  |  |

| SUBLW                                                        | 5           | Subtract W from Literal      |                          |         |   |           |  |

|--------------------------------------------------------------|-------------|------------------------------|--------------------------|---------|---|-----------|--|

| Syntax:                                                      | 9           | SUBLW                        | k                        |         |   |           |  |

| Operands:                                                    | C           | $0 \le k \le 25$             | 5                        |         |   |           |  |

| Operation:                                                   | k           | $i - (W) \rightarrow$        | W                        |         |   |           |  |

| Status Affected:                                             | ١           | I, OV, C,                    | DC, Z                    |         |   |           |  |

| Encoding:                                                    | Γ           | 0000                         | 1000                     | kkk     | k | kkkk      |  |

| Description                                                  |             |                              | acted from               |         |   |           |  |

| Words:                                                       | 1           |                              |                          |         |   |           |  |

| Cycles:                                                      | 1           |                              |                          |         |   |           |  |

| Q Cycle Activity:                                            |             |                              |                          |         |   |           |  |

| Q1                                                           |             | Q2                           | Q3                       |         |   | Q4        |  |

| Decode                                                       |             | Read<br>eral 'k'             | Proce<br>Data            |         | W | rite to W |  |

| Example 1:                                                   | S           | UBLW (                       | )2h                      |         |   |           |  |

| Before Instru<br>W<br>C<br>After Instruc<br>W<br>C<br>Z<br>N | =           | 01h<br>?<br>01h<br>1 ;r<br>0 | esult is p               | ositive | 9 |           |  |

| Example 2:                                                   | S           | UBLW (                       | )2h                      |         |   |           |  |

| Before Instru<br>W<br>C<br>After Instruc<br>W                | =           | 02h<br>?<br>00h              |                          |         |   |           |  |

| C<br>Z<br>N                                                  | =<br>=<br>= | 1;r<br>1<br>0                | esult is z               | ero     |   |           |  |

| Example 3:                                                   | S           | SUBLW (                      | )2h                      |         |   |           |  |