Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betalls                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2321-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

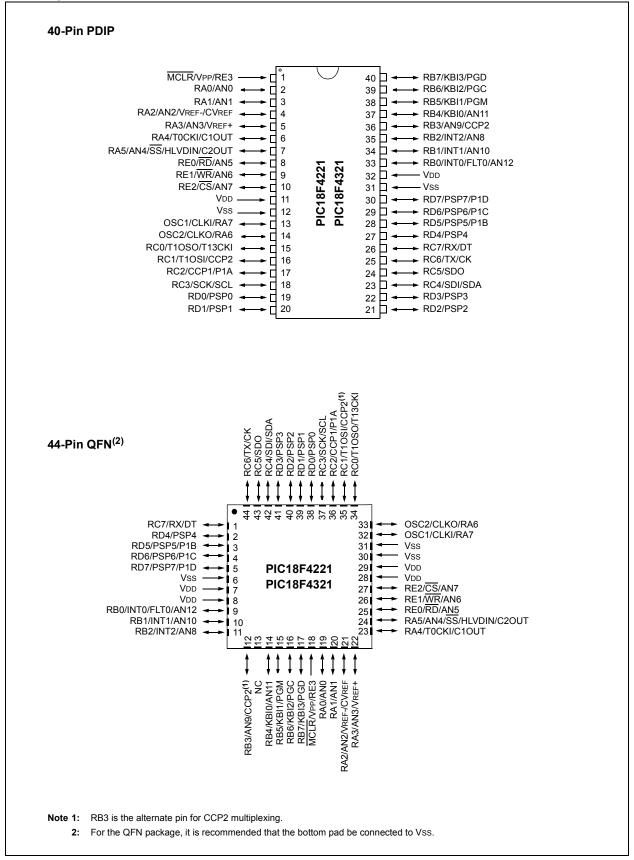

### **Pin Diagrams (Continued)**

| Din Nama                                                      | Pi         | n Numb   | ber     | Pin             | Buffer                    | Description                                                                                                         |  |  |

|---------------------------------------------------------------|------------|----------|---------|-----------------|---------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                      | PDIP       | QFN      | TQFP    | Туре            | Туре                      | Description                                                                                                         |  |  |

|                                                               |            |          |         |                 |                           | PORTB is a bidirectional I/O port. PORTB can be<br>software programmed for internal weak pull-ups on all<br>inputs. |  |  |

| RB0/INT0/FLT0/AN12<br>RB0<br>INT0<br>FLT0<br>AN12             | 33         | 9        | 8       | I/O<br>I<br>I   | TTL<br>ST<br>ST<br>Analog | Digital I/O.<br>External Interrupt 0.<br>PWM Fault input for Enhanced CCP1.<br>Analog input 12.                     |  |  |

| RB1/INT1/AN10<br>RB1<br>INT1<br>AN10                          | 34         | 10       | 9       | I/O<br>I<br>I   | TTL<br>ST<br>Analog       | Digital I/O.<br>External Interrupt 1.<br>Analog Input 10.                                                           |  |  |

| RB2/INT2/AN8<br>RB2<br>INT2<br>AN8                            | 35         | 11       | 10      | I/O<br>I<br>I   | TTL<br>ST<br>Analog       | Digital I/O.<br>External Interrupt 2.<br>Analog Input 8.                                                            |  |  |

| RB3/AN9/CCP2<br>RB3<br>AN9<br>CCP2 <sup>(2)</sup>             | 36         | 12       | 11      | I/O<br>I<br>I/O | TTL<br>Analog<br>ST       | Digital I/O.<br>Analog Input 9.<br>Capture 2 input/Compare 2 output/PWM2 output.                                    |  |  |

| RB4/KBI0/AN11<br>RB4<br>KBI0<br>AN11                          | 37         | 14       | 14      | I/O<br>I<br>I   | TTL<br>TTL<br>Analog      | Digital I/O.<br>Interrupt-on-change pin.<br>Analog input 11.                                                        |  |  |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM                            | 38         | 15       | 15      | I/O<br>I<br>I/O | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP™ Programming enable pin.                               |  |  |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                            | 39         | 16       | 16      | I/O<br>I<br>I/O | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>In-circuit debugger and ICSP programming<br>clock pin.                  |  |  |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD                            | 40         | 17       | 17      | I/O<br>I<br>I/O | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>In-circuit debugger and ICSP programming<br>data pin.                   |  |  |

| Legend: TTL = TTL c<br>ST = Schm<br>I <sup>2</sup> C = ST wit | itt Trigge | er input | with CN | IOS lev         | vels                      | CMOS = CMOS compatible input or output<br>I = Input P = Power<br>O = Output                                         |  |  |

### TABLE 1-3: PIC18F4221/4321 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

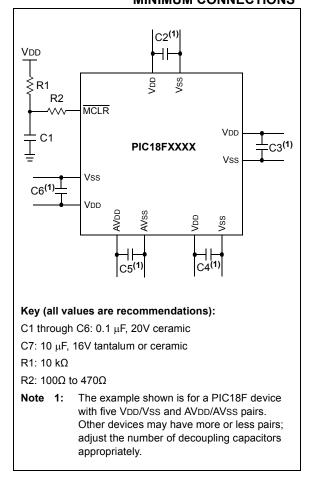

### 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18F MICROCONTROLLERS

### 2.1 Basic Connection Requirements

Getting started with the PIC18F2221/2321/4221/4321 family family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin

(see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.4 "ICSP Pins")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for analog modules is implemented

| Note: | The AVDD and AVSS pins must always be  |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|

|       | connected, regardless of whether any o |  |  |  |  |  |  |

|       | the analog modules are being used.     |  |  |  |  |  |  |

The minimum mandatory connections are shown in Figure 2-1.

### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

### 4.0 POWER-MANAGED MODES

PIC18F2221/2321/4221/4321 family devices offer a total of seven operating modes for more efficient power-management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery-powered devices).

There are three categories of power-managed modes:

- Run modes

- Idle modes

- Sleep mode

These categories define which portions of the device are clocked and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power-managed modes include several powersaving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC devices, where all device clocks are stopped.

### 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions: if the CPU is to be clocked or not and the selection of a clock source. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS<1:0 bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

### 4.1.1 CLOCK SOURCES

The SCS<1:0 bits allow the selection of one of three clock sources for power-managed modes. They are:

- the primary clock, as defined by the FOSC<3:0> Configuration bits

- the secondary clock (the Timer1 oscillator)

- the internal oscillator block (for RC modes)

### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS1:SCS0 bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| Mada     | oscco       | N Bits   | Module  | Clocking    |                                                                                                                                       |  |

|----------|-------------|----------|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Mode     | IDLEN<7>(1) | SCS<1:0> | CPU     | Peripherals | Available Clock and Oscillator Source                                                                                                 |  |

| Sleep    | 0           | N/A      | Off     | Off         | None – All clocks are disabled                                                                                                        |  |

| PRI_RUN  | N/A         | 00       | Clocked | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC and<br>Internal Oscillator Block. <sup>(2)</sup><br>This is the normal full power execution mode. |  |

| SEC_RUN  | N/A         | 01       | Clocked | Clocked     | Secondary – Timer1 Oscillator                                                                                                         |  |

| RC_RUN   | N/A         | 1x       | Clocked | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                                              |  |

| PRI_IDLE | 1           | 00       | Off     | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC                                                                                                   |  |

| SEC_IDLE | 1           | 01       | Off     | Clocked     | Secondary – Timer1 Oscillator                                                                                                         |  |

| RC_IDLE  | 1           | 1x       | Off     | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                                              |  |

TABLE 4-1: POWER-MANAGED MODES

Note 1: IDLEN reflects its value when the SLEEP instruction is executed.

2: Includes INTOSC and INTOSC postscaler, as well as the INTRC source.

### 4.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped; and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval TCSD following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

## TABLE 4-2:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Clock Source<br>before Wake-up | Clock Source<br>after Wake-up | Exit Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Clock Ready Status<br>Bit (OSCCON) |  |

|--------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|

|                                | LP, XT, HS                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                    |  |

| Primary Device Clock           | HSPLL                         | теер(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OSTS                               |  |

| (PRI_IDLE mode)                | EC, RC                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                    |  |

|                                | INTOSC <sup>(2)</sup>         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IOFS                               |  |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                    |  |

| 11050                          | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OSTS                               |  |

| T1OSC                          | EC, RC                        | TCSD <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                    |  |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IOFS                               |  |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                    |  |

| INTOSC <sup>(3)</sup>          | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OSTS                               |  |

|                                | EC, RC                        | $\begin{array}{c c} & & & \\ \hline S & & \\ \hline & & \\ \hline S & & \\ \hline & & \\ \hline S & & \\ \hline T CSD^{(1)} \\ \hline S & & \\ \hline T OST + t_{rc}^{(3)} \\ \hline & & \\ \hline T CSD^{(1)} \\ \hline \end{array} \\ \hline \hline & & \\ \hline T OST + t_{rc}^{(3)} \\ \hline & & \\ \hline T CSD^{(1)} \\ \hline \end{array} \\ \hline \hline & & \\ \hline \hline S & & \\ \hline T OST + t_{rc}^{(3)} \\ \hline \hline \end{array} \\ $ |                                    |  |

|                                | INTOSC <sup>(2)</sup>         | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IOFS                               |  |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                    |  |

| None                           | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OSTS                               |  |

| (Sleep mode)                   | EC, RC                        | TCSD <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                    |  |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IOFS                               |  |

**Note 1:** TCSD (parameter 38) is a required delay when waking from Sleep and all Idle modes and runs concurrently with any other required delays (see **Section 4.4 "Idle Modes**"). On Reset, INTOSC defaults to 1 MHz.

2: Includes both the INTOSC 8 MHz source and postscaler derived frequencies.

**3:** TOST is the Oscillator Start-up Timer (parameter 32). t<sub>rc</sub> is the PLL Lock-out Timer (parameter F12); it is also designated as TPLL.

4: Execution continues during TIOBST (parameter 39), the INTOSC stabilization period.

### 7.4 Erasing Flash Program Memory

The minimum erase block is 32 words or 64 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. TBLPTR<5:0> are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

### 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer register with address of row being erased.

- 2. Set the EECON1 register for the erase operation:

- set EEPGD bit to point to program memory;

- · clear the CFGS bit to access program memory;

- set WREN bit to enable writes;

- set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit. This will begin the row erase cycle.

- 7. The CPU will stall for duration of the erase (about 2 ms using internal timer).

- 8. Re-enable interrupts.

|                      | MOVLW<br>MOVWF<br>MOVWF<br>MOVLW<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL | ; load TBLPTR with the base<br>; address of the memory block                                                                                                        |

|----------------------|-------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ERASE_ROW            | MOVWP                                     | IDLFIKL                                                                             |                                                                                                                                                                     |

|                      | BSF<br>BCF<br>BSF<br>BSF<br>BCF           | EECON1, EEPGD<br>EECON1, CFGS<br>EECON1, WREN<br>EECON1, FREE<br>INTCON, GIE        | <pre>; point to Flash program memory<br/>; access Flash program memory<br/>; enable write to memory<br/>; enable Row Erase operation<br/>; disable interrupts</pre> |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF   | 55h<br>EECON2<br>0AAh<br>EECON2<br>EECON2<br>EECON1, WR                             | <pre>; write 55h ; write 0AAh ; start erase (CPU stall)</pre>                                                                                                       |

|                      | BSF                                       | INTCON, GIE                                                                         | ; re-enable interrupts                                                                                                                                              |

### EXAMPLE 7-2: ERASING A FLASH PROGRAM MEMORY ROW

### 15.2 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 15-2). When the RD16 control bit (T3CON<7>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

### 15.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in Section 13.0 "Timer1 Module".

### 15.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE (PIE2<1>).

### 15.5 Resetting Timer3 Using the CCP Special Event Trigger

If either of the CCP modules is configured to use Timer3 and to generate a Special Event Trigger in Compare mode (CCP1M<3:0> or CCP2M<3:0> = 1011), this signal will reset Timer3. It will also start an A/D conversion if the A/D module is enabled (see **Section 16.3.4** "**Special Event Trigger**" for more information).

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPR2H:CCPR2L register pair effectively becomes a period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from a CCP module, the write will take precedence.

Note: The Special Event Triggers from the CCP2 module will not set the TMR3IF interrupt flag bit (PIR2<1>).

| Name   | Bit 7      | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|------------|---------------|---------|---------|---------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH   | PEIE/GIEL     | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR2   | OSCFIF     | CMIF          | _       | EEIF    | BCLIF   | HLVDIF | TMR3IF | CCP2IF | 58                         |

| PIE2   | OSCFIE     | CMIE          | _       | EEIE    | BCLIE   | HLVDIE | TMR3IE | CCP2IE | 58                         |

| IPR2   | OSCFIP     | CMIP          | _       | EEIP    | BCLIP   | HLVDIP | TMR3IP | CCP2IP | 58                         |

| TMR3L  | Timer3 Reg | gister Low B  | yte     |         |         |        |        |        | 57                         |

| TMR3H  | Timer3 Reg | gister High B | yte     |         |         |        |        |        | 57                         |

| T1CON  | RD16       | T1RUN         | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 56                         |

| T3CON  | RD16       | T3CCP2        | T3CKPS1 | T3CKPS0 | T3CCP1  | T3SYNC | TMR3CS | TMR3ON | 57                         |

TABLE 15-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

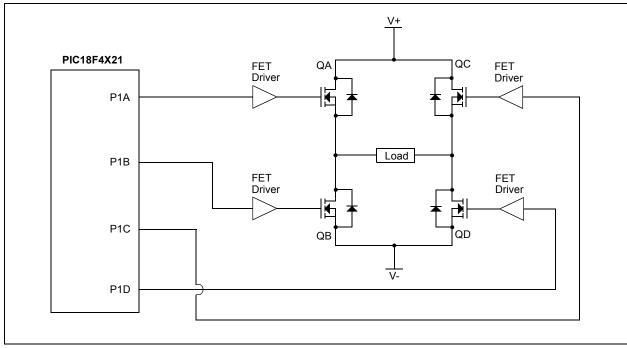

### FIGURE 17-7: EXAMPLE OF FULL-BRIDGE APPLICATION

### 17.4.5.1 Direction Change in Full-Bridge Mode

In the Full-Bridge Output mode, the P1M1 bit in the CCP1CON register allows user to control the forward/ reverse direction. When the application firmware changes this direction control bit, the module will assume the new direction on the next PWM cycle.

Just before the end of the current PWM period, the modulated outputs (P1B and P1D) are placed in their inactive state, while the unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction. This occurs in a time interval of 4 Tosc \* (Timer2 Prescale Value) before the next PWM period begins. The Timer2 prescaler will be either 1, 4 or 16, depending on the value of the T2CKPS<1:0> bits (T2CON<1:0>). During the interval from the switch of the unmodulated outputs to the beginning of the next period, the modulated outputs (P1B and P1D) remain inactive. This relationship is shown in Figure 17-8.

Note that in the Full-Bridge Output mode, the ECCP1 module does not provide any dead-band delay. In general, since only one output is modulated at all times, dead-band delay is not required. However, there is a situation where a dead-band delay might be required. This situation occurs when both of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

Figure 17-9 shows an example where the PWM direction changes from forward to reverse at a near 100% duty cycle. At time t1, the outputs P1A and P1D become inactive, while output P1C becomes active. In this example, since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current may flow through power devices, QC and QD (see Figure 17-7), for the duration of 't'. The same phenomenon will occur to power devices, QA and QB, for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, one of the following requirements must be met:

- 1. Reduce PWM for a PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

© 2009 Microchip Technology Inc.

| Name    | Bit 7                | Bit 6       | Bit 5       | Bit 4         | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------|-------------|-------------|---------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL   | TMR0IE      | INT0IE        | RBIE  | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF        | RCIF        | TXIF          | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE        | RCIE        | TXIE          | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP        | RCIP        | TXIP          | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                         |

| RCSTA   | SPEN                 | RX9         | SREN        | CREN          | ADDEN | FERR   | OERR   | RX9D   | 57                         |

| TXREG   | EUSART T             | ransmit Reg | ister       |               |       |        |        |        | 57                         |

| TXSTA   | CSRC                 | TX9         | TXEN        | SYNC          | SENDB | BRGH   | TRMT   | TX9D   | 57                         |

| BAUDCON | ABDOVF               | RCIDL       | RXDTP       | TXCKP         | BRG16 | —      | WUE    | ABDEN  | 57                         |

| SPBRGH  | EUSART B             | aud Rate G  | enerator Re | gister High I | Byte  |        |        |        | 57                         |

| SPBRG   | EUSART B             | aud Rate G  | enerator Re | gister Low E  | Byte  |        |        |        | 57                         |

### TABLE 19-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

Legend: — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

### 19.4 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTA<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any power-managed mode.

### 19.4.1 EUSART SYNCHRONOUS SLAVE TRANSMISSION

The operation of the Synchronous Master and Slave modes are identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREG register.

- c) Flag bit, TXIF, will not be set.

- When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit, TXIF, will now be set.

- e) If enable bit, TXIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If the signal from the CK pin is to be inverted, set the TXCKP bit.

- 5. If 9-bit transmission is desired, set bit, TX9.

- 6. Enable the transmission by setting enable bit, TXEN.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 8. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| IADEE 13-3 | . KLOIC              |              |             |              |       |        |        |        |                            |

|------------|----------------------|--------------|-------------|--------------|-------|--------|--------|--------|----------------------------|

| Name       | Bit 7                | Bit 6        | Bit 5       | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

| INTCON     | GIE/GIEH             | PEIE/GIEL    | TMR0IE      | INT0IE       | RBIE  | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1       | PSPIF <sup>(1)</sup> | ADIF         | RCIF        | TXIF         | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1       | PSPIE <sup>(1)</sup> | ADIE         | RCIE        | TXIE         | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1       | PSPIP <sup>(1)</sup> | ADIP         | RCIP        | TXIP         | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                         |

| RCSTA      | SPEN                 | RX9          | SREN        | CREN         | ADDEN | FERR   | OERR   | RX9D   | 57                         |

| TXREG      | EUSART T             | ransmit Regi | ister       |              |       |        |        |        | 57                         |

| TXSTA      | CSRC                 | TX9          | TXEN        | SYNC         | SENDB | BRGH   | TRMT   | TX9D   | 57                         |

| BAUDCON    | ABDOVF               | RCIDL        | RXDTP       | TXCKP        | BRG16 | —      | WUE    | ABDEN  | 57                         |

| SPBRGH     | EUSART E             | aud Rate Ge  | enerator Re | gister High  | Byte  |        |        |        | 57                         |

| SPBRG      | EUSART E             | Baud Rate Ge | enerator Re | gister Low I | Byte  |        |        |        | 57                         |

|            |                      |              |             |              |       |        |        |        |                            |

## TABLE 19-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

| REGISTER 24-2: | CONFIG             | 2L: CONF                                                                                                         | IGURATI          | ON REGIS                  | TER 2 LOV            | V (BYTE AD            | DRESS 300       | 002h)                 |  |

|----------------|--------------------|------------------------------------------------------------------------------------------------------------------|------------------|---------------------------|----------------------|-----------------------|-----------------|-----------------------|--|

|                | U-0                | U-0                                                                                                              | U-0              | R/P-1                     | R/P-1                | R/P-1                 | R/P-1           | R/P-1                 |  |

|                | _                  | _                                                                                                                | _                | BORV1 <sup>(1)</sup>      | BORV0 <sup>(1)</sup> | BOREN1 <sup>(2)</sup> | BOREN0(2)       | PWRTEN <sup>(2)</sup> |  |

|                | bit 7              |                                                                                                                  |                  |                           |                      |                       |                 | bit 0                 |  |

| bit 7-5        | Unimplem           | nented: Re                                                                                                       | <b>ad as</b> '0' |                           |                      |                       |                 |                       |  |

| bit 4-3        | BORV<1:0           | 0>: Brown-                                                                                                       | out Reset        | Voltage bits <sup>(</sup> | 1)                   |                       |                 |                       |  |

|                | 11 <b>= Minin</b>  | num setting                                                                                                      | J                |                           |                      |                       |                 |                       |  |

|                | •                  |                                                                                                                  |                  |                           |                      |                       |                 |                       |  |

|                | •                  |                                                                                                                  |                  |                           |                      |                       |                 |                       |  |

|                | 00 <b>= Maxi</b> i | mum settin                                                                                                       | g                |                           |                      |                       |                 |                       |  |

| bit 2-1        | BOREN<1            | I: <b>0&gt;:</b> Browr                                                                                           | n-out Rese       | t Enable bits             | ;(2)                 |                       |                 |                       |  |

|                |                    |                                                                                                                  |                  |                           | •                    | REN is disable        | ,               |                       |  |

|                |                    |                                                                                                                  |                  | in hardware               | only and dis         | sabled in Slee        | ep mode         |                       |  |

|                |                    | OREN is dis<br>/n-out Rese                                                                                       |                  | and controlle             | ed by softwa         | are (SBOREN           | is enabled)     |                       |  |

|                |                    |                                                                                                                  |                  | in hardware               | •                    | •                     | ,               |                       |  |

| bit 0          | PWRTEN:            | Power-up                                                                                                         | Timer Ena        | able bit <sup>(2)</sup>   |                      |                       |                 |                       |  |

|                | 1 = PWRT           |                                                                                                                  |                  |                           |                      |                       |                 |                       |  |

|                | 0 <b>= PWRT</b>    |                                                                                                                  |                  |                           |                      |                       |                 |                       |  |

|                | Note 1:            | See Sect                                                                                                         | ion 27.1 '       | 'DC Charac                | teristics" fo        | or the specific       | ations.         |                       |  |

|                | 2:                 | 2: The Power-up Timer is decoupled from Brown-out Reset, allowing these features to be independently controlled. |                  |                           |                      |                       |                 |                       |  |

|                | Legend:            |                                                                                                                  |                  |                           |                      |                       |                 |                       |  |

|                | R = Reada          | able bit                                                                                                         | P = Pr           | ogrammable                | ebit U=l             | Jnimplemente          | ed bit, read as | s 'O'                 |  |

| <b>.</b>                               | •                                   |

|----------------------------------------|-------------------------------------|

| -n = Value when device is unprogrammed | u = Unchanged from programmed state |

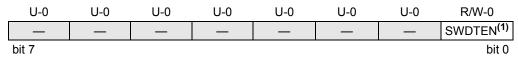

### REGISTER 24-14: WDTCON: WATCHDOG TIMER CONTROL REGISTER

bit 7-1 Unimplemented: Read as '0'

bit 0 **SWDTEN:** Software Controlled Watchdog Timer Enable bit<sup>(1)</sup>

1 = Watchdog Timer is on

0 = Watchdog Timer is off

**Note 1:** This bit has no effect if the Configuration bit, WDTEN, is enabled.

| Legend:                            |                   |  |

|------------------------------------|-------------------|--|

| R = Readable bit                   | W = Writable bit  |  |

| U = Unimplemented bit, read as '0' | -n = Value at POR |  |

### TABLE 24-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name   | Bit 7 | Bit 6                 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Reset<br>Values<br>on page |

|--------|-------|-----------------------|-------|-------|-------|-------|-------|--------|----------------------------|

| RCON   | IPEN  | SBOREN <sup>(1)</sup> |       | RI    | TO    | PD    | POR   | BOR    | 56                         |

| WDTCON | _     | _                     | _     |       | _     | _     |       | SWDTEN | 56                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

Note 1: The SBOREN bit is only available when the BOREN<1:0> Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

| BRA      | L .                                    | Uncondit                                                              | ior                 | al Bra                       | anch                            |                      |                          |  |

|----------|----------------------------------------|-----------------------------------------------------------------------|---------------------|------------------------------|---------------------------------|----------------------|--------------------------|--|

| Synta    | ax:                                    | BRA n                                                                 |                     |                              |                                 |                      |                          |  |

| Oper     | ands:                                  | -1024 ≤ n ≤                                                           | 10                  | 23                           |                                 |                      |                          |  |

| Oper     | ation:                                 | (PC) + 2 +                                                            | 2n                  | $\rightarrow$ PC             |                                 |                      |                          |  |

| Statu    | s Affected:                            | None                                                                  |                     |                              |                                 |                      |                          |  |

| Enco     | ding:                                  | 1101                                                                  | C                   | nnn                          | nnnr                            | L                    | nnnn                     |  |

| Desc     | ription:                               | Add the 2's<br>the PC. Sir<br>incremente<br>the new ad<br>instruction | nce<br>ed to<br>dre | the PC<br>o fetch<br>ss will | will hav<br>the next<br>be PC + | /e<br>t ins<br>· 2 · | struction,<br>+ 2n. This |  |

| Word     | ls:                                    | 1                                                                     |                     |                              |                                 |                      |                          |  |

| Cycle    | es:                                    | 2                                                                     |                     |                              |                                 |                      |                          |  |

| QC       | ycle Activity:                         |                                                                       |                     |                              |                                 |                      |                          |  |

|          | Q1                                     | Q2                                                                    |                     | C                            | 23                              |                      | Q4                       |  |

|          | Decode                                 | Read liter<br>'n'                                                     | al                  |                              | cess<br>ata                     |                      | Write to<br>PC           |  |

|          | No<br>operation                        | No<br>operatio                                                        | n                   |                              | lo<br>ation                     | 0                    | No<br>peration           |  |

| Example: |                                        | HERE                                                                  |                     | BRA                          | Jump                            |                      |                          |  |

|          | Before Instru<br>PC<br>After Instructi | =                                                                     | ad                  | dress                        | (HERE)                          |                      |                          |  |

|          | PC                                     | =                                                                     | ad                  | dress                        | (Jump)                          |                      |                          |  |

| BSF                                               | Bit Set f                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |      |                      |  |  |  |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|----------------------|--|--|--|

| Syntax:                                           | BSF f, b {                                                                                                                                                                                                                                                                                                                                                                                                                                        | อโ             |      |                      |  |  |  |

| Operands:                                         | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0, 1]$                                                                                                                                                                                                                                                                                                                                                                                            |                |      |                      |  |  |  |

| Operation:                                        | $1 \rightarrow \text{f}$                                                                                                                                                                                                                                                                                                                                                                                                                          |                |      |                      |  |  |  |

| Status Affected:                                  | None                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |      |                      |  |  |  |

| Encoding:                                         | 1000                                                                                                                                                                                                                                                                                                                                                                                                                                              | bbba           | ffff | ffff                 |  |  |  |

| Description:                                      | Bit 'b' in register 'f' is set.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                |      |                      |  |  |  |

| Words:                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |      |                      |  |  |  |

| Cycles:                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |      |                      |  |  |  |

| Q Cycle Activity:                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |      |                      |  |  |  |

| Q1                                                | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                | Q3             |      | Q4                   |  |  |  |

| Decode                                            | Read register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                 | Proces<br>Data |      | Write<br>egister 'f' |  |  |  |

| Example: BSF FLAG_REG, 7, 1<br>Before Instruction |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |      |                      |  |  |  |

| After Instruction                                 | FLAG_REG = 0Ah<br>After Instruction<br>FLAG_REG = 8Ah                                                                                                                                                                                                                                                                                                                                                                                             |                |      |                      |  |  |  |

| NEGF              | Negate f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | NEGF f {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Operands:         | $0 \le f \le 255$<br>$a \in [0, 1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Operation:        | $(\overline{f}) + 1 \rightarrow f$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Status Affected:  | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Encoding:         | 0110 110a ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Description:      | Location 'f' is negated using two's<br>complement. The result is placed in the<br>data memory location 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| NOF       | NOP No Operation |            |           |      |    |          |  |  |  |  |

|-----------|------------------|------------|-----------|------|----|----------|--|--|--|--|

| Synta     | ax:              | NOP        |           |      |    |          |  |  |  |  |

| Oper      | ands:            | None       |           |      |    |          |  |  |  |  |

| Oper      | ation:           | No operati | on        |      |    |          |  |  |  |  |

| Statu     | s Affected:      | None       |           |      |    |          |  |  |  |  |

| Encoding: |                  | 0000       | 0000      | 0000 |    | 0000     |  |  |  |  |

|           |                  | 1111       | XXXX XXXX |      | xx | XXXX     |  |  |  |  |

| Desc      | ription:         | No operati | on.       |      |    |          |  |  |  |  |

| Word      | ls:              | 1          |           |      |    |          |  |  |  |  |

| Cycle     | es:              | 1          |           |      |    |          |  |  |  |  |

| QC        | ycle Activity:   |            |           |      |    |          |  |  |  |  |

|           | Q1               | Q2         | Q         | 3    |    | Q4       |  |  |  |  |

|           | Decode           | No         | No        | )    |    | No       |  |  |  |  |

|           |                  | operation  | opera     | tion | op | peration |  |  |  |  |

Example:

None.

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: NEGF REG, 1

> Before Instruction REG = 0011 1010 [3Ah] After Instruction REG = 1100 0110 [C6h]

© 2009 Microchip Technology Inc.

| RLN         | ICF                                              | Rotate Le                                                                                                                                                                                     | eft f (No Car                                                                                                                                                                              | ry)                                                                                                                                                                                  |  |  |  |  |  |

|-------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Synt        | ax:                                              | RLNCF                                                                                                                                                                                         | f {,d {,a}}                                                                                                                                                                                |                                                                                                                                                                                      |  |  |  |  |  |

| Oper        | rands:                                           | $0 \le f \le 255$<br>$d \in [0, 1]$<br>$a \in [0, 1]$                                                                                                                                         | <b>d</b> ∈ [0, 1]                                                                                                                                                                          |                                                                                                                                                                                      |  |  |  |  |  |

| Oper        | ration:                                          | · · ·                                                                                                                                                                                         | $(f < n >) \rightarrow dest < n + 1 >,$<br>$(f < 7 >) \rightarrow dest < 0 >$                                                                                                              |                                                                                                                                                                                      |  |  |  |  |  |

| Statu       | is Affected:                                     | N, Z                                                                                                                                                                                          |                                                                                                                                                                                            |                                                                                                                                                                                      |  |  |  |  |  |