#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

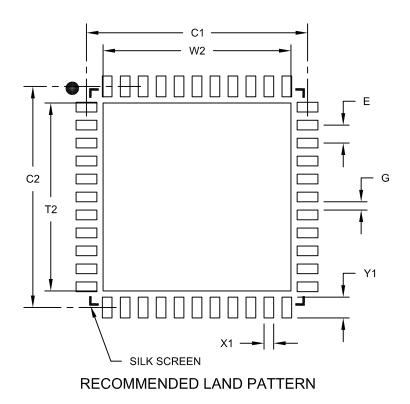

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2321-e-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.0 POWER-MANAGED MODES

PIC18F2221/2321/4221/4321 family devices offer a total of seven operating modes for more efficient power-management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery-powered devices).

There are three categories of power-managed modes:

- Run modes

- Idle modes

- Sleep mode

These categories define which portions of the device are clocked and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power-managed modes include several powersaving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC devices, where all device clocks are stopped.

#### 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions: if the CPU is to be clocked or not and the selection of a clock source. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS<1:0 bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

#### 4.1.1 CLOCK SOURCES

The SCS<1:0 bits allow the selection of one of three clock sources for power-managed modes. They are:

- the primary clock, as defined by the FOSC<3:0> Configuration bits

- the secondary clock (the Timer1 oscillator)

- the internal oscillator block (for RC modes)

#### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS1:SCS0 bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| Mode     | OSCCON Bits |          | Module  | Clocking    | Available Clock and Oscillator Source                                                                                                 |  |

|----------|-------------|----------|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

|          | IDLEN<7>(1) | SCS<1:0> | CPU     | Peripherals | Available Clock and Oscillator Source                                                                                                 |  |

| Sleep    | 0           | N/A      | Off     | Off         | None – All clocks are disabled                                                                                                        |  |

| PRI_RUN  | N/A         | 00       | Clocked | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC and<br>Internal Oscillator Block. <sup>(2)</sup><br>This is the normal full power execution mode. |  |

| SEC_RUN  | N/A         | 01       | Clocked | Clocked     | Secondary – Timer1 Oscillator                                                                                                         |  |

| RC_RUN   | N/A         | 1x       | Clocked | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                                              |  |

| PRI_IDLE | 1           | 00       | Off     | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC                                                                                                   |  |

| SEC_IDLE | 1           | 01       | Off     | Clocked     | Secondary – Timer1 Oscillator                                                                                                         |  |

| RC_IDLE  | 1           | 1x       | Off     | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                                              |  |

TABLE 4-1: POWER-MANAGED MODES

Note 1: IDLEN reflects its value when the SLEEP instruction is executed.

2: Includes INTOSC and INTOSC postscaler, as well as the INTRC source.

If the IRCF bits and the INTSRC bit are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear; there will be no indication of the current clock source. The INTRC source is providing the device clocks.

If the IRCF bits are changed from all clear (thus, enabling the INTOSC output) or if INTSRC is set, the IOFS bit becomes set after the INTOSC output becomes stable. Clocks to the device continue while the INTOSC source stabilizes after an interval of TIOBST (parameter 39, Table 27-10).

If the IRCF bits were previously at a non-zero value, or if INTSRC was set before setting SCS1 and the INTOSC source was already stable, the IOFS bit will remain set.

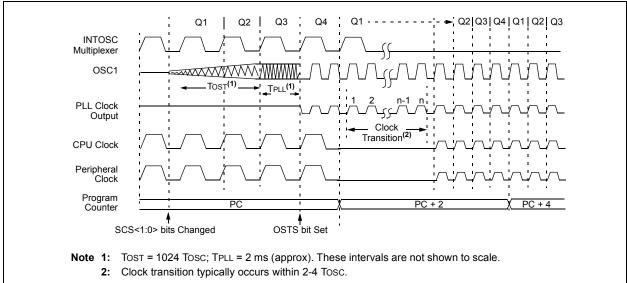

On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

PC + 4

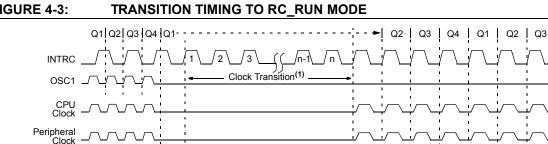

#### FIGURE 4-3:

Note 1: Clock transition typically occurs within 2-4 Tosc.

Program Counter

PC

#### FIGURE 4-4: TRANSITION TIMING FROM RC RUN MODE TO PRI RUN MODE

PC + 2

#### 4.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped; and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval TCSD following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

## TABLE 4-2:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Clock Source<br>before Wake-up | Clock Source<br>after Wake-up | Exit Delay                            | Clock Ready Status<br>Bit (OSCCON) |  |

|--------------------------------|-------------------------------|---------------------------------------|------------------------------------|--|

|                                | LP, XT, HS                    |                                       |                                    |  |

| Primary Device Clock           | HSPLL                         | TCSD <sup>(1)</sup>                   | OSTS                               |  |

| (PRI_IDLE mode)                | EC, RC                        |                                       |                                    |  |

|                                | INTOSC <sup>(2)</sup>         |                                       | IOFS                               |  |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |  |

| 11050                          | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |  |

| T1OSC                          | EC, RC                        | TCSD <sup>(1)</sup>                   |                                    |  |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                 | IOFS                               |  |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |  |

| INTOSC <sup>(3)</sup>          | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |  |

|                                | EC, RC                        | Tcsd <sup>(1)</sup>                   |                                    |  |

|                                | INTOSC <sup>(2)</sup>         | None                                  | IOFS                               |  |

|                                | LP, XT, HS                    | Tost <sup>(3)</sup>                   |                                    |  |

| None                           | HSPLL                         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS                               |  |

| (Sleep mode)                   | EC, RC                        | TCSD <sup>(1)</sup>                   |                                    |  |

|                                | INTOSC <sup>(2)</sup>         | TIOBST <sup>(4)</sup>                 | IOFS                               |  |

**Note 1:** TCSD (parameter 38) is a required delay when waking from Sleep and all Idle modes and runs concurrently with any other required delays (see **Section 4.4 "Idle Modes**"). On Reset, INTOSC defaults to 1 MHz.

2: Includes both the INTOSC 8 MHz source and postscaler derived frequencies.

**3:** TOST is the Oscillator Start-up Timer (parameter 32). t<sub>rc</sub> is the PLL Lock-out Timer (parameter F12); it is also designated as TPLL.

4: Execution continues during TIOBST (parameter 39), the INTOSC stabilization period.

NOTES:

| Name  | Bit 7                                                        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on page |

|-------|--------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|----------------------------|

| PORTC | ATC PORTC Data Latch Register (Read and Write to Data Latch) |       |       |       |       |       |       | 58    |                            |

| LATC  |                                                              |       |       |       |       |       |       |       | 58                         |

| TRISC |                                                              |       |       |       |       |       |       |       | 58                         |

| TABLE 11-6: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTC |

|-------------|--------------------------------------------|

|-------------|--------------------------------------------|

| RTCinit |        |              |                                               |

|---------|--------|--------------|-----------------------------------------------|

|         | MOVLW  | 80h          | ; Preload TMR1 register pair                  |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                       |

|         | CLRF   | TMR1L        |                                               |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,               |

|         | MOVWF  | T1CON        | ; Asynchronous operation, external oscillator |

|         | CLRF   | secs         | ; Initialize timekeeping registers            |

|         | CLRF   | mins         | ;                                             |

|         | MOVLW  | .12          |                                               |

|         | MOVWF  | hours        |                                               |

|         | BSF    | PIE1, TMR1IE | ; Enable Timer1 interrupt                     |

|         | RETURN |              |                                               |

| RTCisr  |        |              |                                               |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                  |

|         | BCF    | PIR1, TMR1IF | ; Clear interrupt flag                        |

|         | INCF   | secs, F      | ; Increment seconds                           |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                         |

|         | CPFSGT | secs         |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | secs         | ; Clear seconds                               |

|         | INCF   | mins, F      | ; Increment minutes                           |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                         |

|         | CPFSGT | mins         |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | mins         | ; clear minutes                               |

|         | INCF   | hours, F     | ; Increment hours                             |

|         | MOVLW  | .23          | ; 24 hours elapsed?                           |

|         | CPFSGT | hours        |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | hours        | ; Reset hours                                 |

|         | RETURN |              | ; Done                                        |

#### TABLE 13-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Name   | Bit 7                      | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|----------------------------|-----------|---------|---------|---------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH                   | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1   | PSPIF <sup>(1)</sup>       | ADIF      | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1   | PSPIE <sup>(1)</sup>       | ADIE      | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1   | PSPIP <sup>(1)</sup>       | ADIP      | RCIP    | TXIP    | SSPIP   | CCP1IP | TMR2IP | TMR1IP | 58                         |

| TMR1L  | _ Timer1 Register Low Byte |           |         |         |         |        |        |        | 56                         |

| TMR1H  | Timer1 Register High Byte  |           |         |         |         |        |        | 56     |                            |

| T1CON  | RD16                       | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 56                         |

Legend: Shaded cells are not used by the Timer1 module.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

#### 16.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

#### 16.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers 1, 2 or 3, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode.

## TABLE 16-1:CCP MODE – TIMER<br/>RESOURCES

| CCP/ECCP Mode | Timer Resource   |  |  |  |  |

|---------------|------------------|--|--|--|--|

| Capture       | Timer1 or Timer3 |  |  |  |  |

| Compare       | Timer1 or Timer3 |  |  |  |  |

| PWM           | Timer2           |  |  |  |  |

The assignment of a particular timer to a module is determined by the Timer to CCP enable bits in the T3CON register (Register 15-1). Both modules may be active at any given time and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time. The interactions between the two modules are summarized in Figure 16-1 and Figure 16-2. In Timer1 in Asynchronous Counter mode, the capture operation will not work.

#### 16.1.2 CCP2 PIN ASSIGNMENT

The pin assignment for CCP2 (Capture input, Compare and PWM output) can change, based on device configuration. The CCP2MX Configuration bit determines which pin CCP2 is multiplexed to. By default, it is assigned to RC1 (CCP2MX = 1). If the Configuration bit is cleared, CCP2 is multiplexed with RB3.

Changing the pin assignment of CCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for CCP2 operation, regardless of where it is located.

| CCP1 Mode          | CCP2 Mode          | Interaction                                                                                                                                                                                                                                                         |

|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capture            | Capture            | Each module can use TMR1 or TMR3 as the time base. The time base can be different for each CCP.                                                                                                                                                                     |

| Capture            | Compare            | CCP2 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Automatic A/D conversions on trigger event can also be done. Operation of CCP1 could be affected if it is using the same timer as a time base. |

| Compare            | Capture            | CCP1 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Operation of CCP2 could be affected if it is using the same timer as a time base.                                                              |

| Compare Compare    |                    | Either module can be configured for the Special Event Trigger to reset the time base.<br>Automatic A/D conversions on CCP2 trigger event can be done. Conflicts may occur if<br>both modules are using the same time base.                                          |

| Capture            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| Compare            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Capture            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Compare            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | PWM                | Both PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                                                                                                                                            |

#### TABLE 16-2: INTERACTIONS BETWEEN CCP1 AND CCP2 FOR TIMER RESOURCES

**Note 1:** Includes standard and Enhanced PWM operation.

#### 17.4.9 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP module for PWM operation:

- 1. Configure the PWM pins, P1A and P1B (and P1C and P1D, if used), as inputs by setting the corresponding TRIS bits.

- 2. Set the PWM period by loading the PR2 register.

- 3. If auto-shutdown is required, do the following:

- Disable auto-shutdown (ECCPASE = 0)

- Configure source (FLT0, Comparator 1 or Comparator 2)

- Wait for non-shutdown condition

- Configure the ECCP module for the desired PWM mode and configuration by loading the CCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the P1M<1:0 bits.

- Select the polarities of the PWM output signals with the CCP1M<3:0> bits.

- 5. Set the PWM duty cycle by loading the CCPR1L register and CCP1CON<5:4> bits.

- 6. For Half-Bridge Output mode, set the deadband delay by loading ECCP1DEL<6:0> with the appropriate value.

- 7. If auto-shutdown operation is required, load the ECCP1AS register:

- Select the auto-shutdown sources using the ECCPAS<2:0> bits.

- Select the shutdown states of the PWM output pins using the PSSAC<1:0> and PSSBD<1:0> bits.

- Set the ECCPASE bit (ECCP1AS<7>).

- Configure the comparators using the CMCON register.

- Configure the comparator inputs as analog inputs.

- 8. If auto-restart operation is required, set the PRSEN bit (ECCP1DEL<7>).

- 9. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit (PIR1<1>).

- Set the TMR2 prescale value by loading the T2CKPS bits (T2CON<1:0>).

- Enable Timer2 by setting the TMR2ON bit (T2CON<2>).

- 10. Enable PWM outputs after a new PWM cycle has started:

- Wait until TMRx overflows (TMRxIF bit is set).

- Enable the CCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- Clear the ECCPASE bit (ECCP1AS<7>).

## 17.4.10 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the ECCP pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from INTOSC and the postscaler may not be stable immediately.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCP module without change. In all other power-managed modes, the selected power-managed mode clock will clock Timer2. Other power-managed mode clocks will most likely be different than the primary clock frequency.

#### 17.4.10.1 Operation with Fail-Safe Clock Monitor

If the Fail-Safe Clock Monitor is enabled, a clock failure will force the device into the power-managed RC\_RUN mode and the OSCFIF bit (PIR2<7>) will be set. The ECCP will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

See the previous section for additional details.

#### 17.4.11 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the CCP registers to their Reset states.

This forces the Enhanced CCP module to reset to a state compatible with the standard CCP module.

#### 18.4.2 OPERATION

The MSSP module functions are enabled by setting MSSP Enable bit, SSPEN (SSPCON1<5>).

The SSPCON1 register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON1<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode clock

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

#### 18.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The I<sup>2</sup>C Slave mode hardware will always generate an interrupt on an address match. Address masking will allow the hardware to generate an interrupt for more than one address (up to 31 in 7-Bit Addressing mode and up to 63 in 10-Bit Addressing mode). Through the mode select bits, the user can also choose to interrupt on Start and Stop bits

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overrightarrow{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON1<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter 100 and parameter 101.

#### 18.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. MSSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated, if enabled) on the falling edge of the ninth SCL pulse.

In 10-Bit Addressing mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

|         | -          |              |                  | -                | -               | _              | -               | _      | -                          |

|---------|------------|--------------|------------------|------------------|-----------------|----------------|-----------------|--------|----------------------------|

| Name    | Bit 7      | Bit 6        | Bit 5            | Bit 4            | Bit 3           | Bit 2          | Bit 1           | Bit 0  | Reset<br>Values<br>on page |

| INTCON  | GIE/GIEH   | PEIE/GIEL    | TMR0IE           | INT0IE           | RBIE            | TMR0IF         | INT0IF          | RBIF   | 55                         |

| PIR1    | PSPIF      | ADIF         | RCIF             | TXIF             | SSPIF           | CCP1IF         | TMR2IF          | TMR1IF | 58                         |

| PIE1    | PSPIE      | ADIE         | RCIE             | TXIE             | SSPIE           | CCP1IE         | TMR2IE          | TMR1IE | 58                         |

| IPR1    | PSPIP      | ADIP         | RCIP             | TXIP             | SSPIP           | CCP1IP         | TMR2IP          | TMR1IP | 58                         |

| PIR2    | OSCFIF     | CMIF         | _                | EEIF             | BCLIF           | HLVDIF         | TMR3IF          | CCP2IF | 58                         |

| PIE2    | OSCFIE     | CMIE         | _                | EEIE             | BCLIE           | HLVDIE         | TMR3IE          | CCP2IE | 58                         |

| IPR2    | OSCFIP     | CMIP         | _                | EEIP             | BCLIP           | HLVDIP         | TMR3IP          | CCP2IP | 58                         |

| TRISC   | TRISC7     | TRISC6       | TRISC5           | TRISC4           | TRISC3          | TRISC2         | TRISC1          | TRISC0 | 58                         |

| TRISD   | TRISD7     | TRISD6       | TRISD5           | TRISD4           | TRISD3          | TRISD2         | TRISD1          | TRISD0 | 58                         |

| SSPBUF  | MSSP Rec   | eive Buffer/ | Fransmit Re      | gister           |                 |                |                 |        | 56                         |

| SSPADD  | ADD7       | ADD6         | ADD5             | ADD4             | ADD3            | ADD2           | ADD1            | ADD0   | 56                         |

| TMR2    | Timer2 Reg | gister       |                  |                  |                 |                |                 |        | 56                         |

| PR2     | Timer2 Per | iod Register |                  |                  |                 |                |                 |        | 56                         |

| SSPCON1 | WCOL       | SSPOV        | SSPEN            | CKP              | SSPM3           | SSPM2          | SSPM1           | SSPM0  | 56                         |

| SSPCON2 | GCEN       | ACKSTAT      | ACKDT/<br>ADMSK5 | ACKEN/<br>ADMSK5 | RCEN/<br>ADMSK5 | PEN/<br>ADMSK5 | RSEN/<br>ADMSK5 | SEN    | 56                         |

| SSPSTAT | SMP        | CKE          | D/A              | Р                | S               | R/W            | UA              | BF     | 56                         |

## TABLE 18-4: REGISTERS ASSOCIATED WITH I<sup>2</sup>C<sup>™</sup> OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C$  mode.

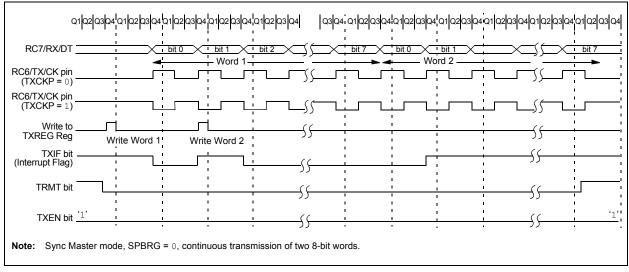

#### 19.3 EUSART Synchronous Master Mode

The Master mode indicates that the processor transmits the master clock on the CK line. The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the TX and RX pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line.

Clock polarity (CK) is selected with the TXCKP bit (BAUDCON<4>). Setting TXCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as low.

#### 19.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 19-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available).

Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG is empty and the TXIF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF is set regardless of the state of enable bit TXIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If the signal from the CK pin is to be inverted, set the TXCKP bit.

- 4. If interrupts are desired, set enable bit, TXIE.

- 5. If 9-bit transmission is desired, set bit, TX9.

- 6. Enable the transmission by setting bit, TXEN.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 8. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### FIGURE 19-11: SYNCHRONOUS TRANSMISSION

#### 20.4 Operation in Power-Managed Modes

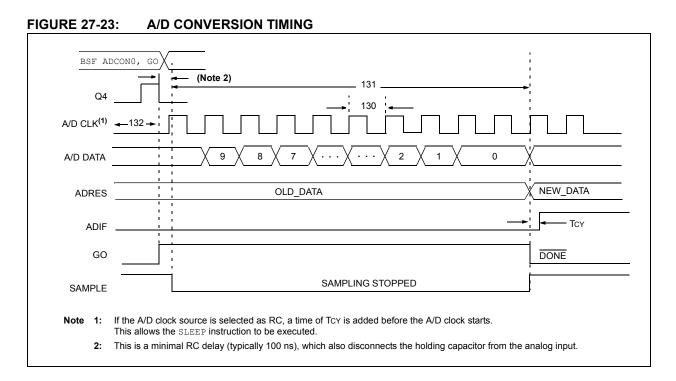

The selection of the automatic acquisition time and A/D conversion clock is determined in part by the clock source and frequency while in a power-managed mode.

If the A/D is expected to operate while the device is in a power-managed mode, the ACQT<2:0> and ADCS<2:0> bits in ADCON2 should be updated in accordance with the clock source to be used in that mode. After entering the mode, an A/D acquisition or conversion may be started. Once started, the device should continue to be clocked by the same clock source until the conversion has been completed.

If desired, the device may be placed into the corresponding Idle mode during the conversion. If the device clock frequency is less than 1 MHz, the A/D RC clock source should be selected.

Operation in Sleep mode requires the A/D FRC clock to be selected. If bits ACQT<2:0> are set to '000' and a conversion is started, the conversion will be delayed one instruction cycle to allow execution of the SLEEP instruction and entry to Sleep mode. The IDLEN bit (OSCCON<7>) must have already been cleared prior to starting the conversion.

#### 20.5 Configuring Analog Port Pins

The ADCON1, TRISA, TRISB and TRISE registers all configure the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<3:0> bits and the TRIS bits.

- Note 1: When reading the Port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert as analog inputs. Analog levels on a digitally configured input will be accurately converted.

- 2: Analog levels on any pin defined as a digital input may cause the digital input buffer to consume current out of the device's specification limits.

- 3: The PBADEN bit in Configuration Register 3H configures PORTB pins to reset as analog or digital pins by controlling how the PCFG<3:0> bits in ADCON1 are reset.

# REGISTER 24-6: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h) U-0 U-0 U-0 U-0 R/C-1 R/C-1 — — — — — CP1 CP0 bit 7 bit 0 bit 0 bit 0 D D D D

- bit 7-2 Unimplemented: Read as '0'

- bit 1 CP1: Code Protection bit

- 1 = Block 1 not code-protected<sup>(1)</sup>

- $0 = \text{Block 1 code-protected}^{(1)}$

- bit 0 **CP0:** Code Protection bit

- 1 = Block 0 not code-protected<sup>(1)</sup>

- 0 = Block 0 code-protected<sup>(1)</sup>

| Legend:              |                    |                                     |

|----------------------|--------------------|-------------------------------------|

| R = Readable bit     | C = Clearable bit  | U = Unimplemented bit, read as '0'  |

| -n = Value when devi | ce is unprogrammed | u = Unchanged from programmed state |

#### REGISTER 24-7: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

| R/C-1 | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| CPD   | CPB   | _   | _   | _   | —   | _   | _     |

| bit 7 |       |     |     |     |     |     | bit 0 |

- bit 7 CPD: Data EEPROM Code Protection bit

- 1 = Data EEPROM not code-protected

- 0 = Data EEPROM code-protected

- bit 6 CPB: Boot Block Code Protection bit

- 1 = Boot block not code-protected<sup>(1)</sup>

- 0 = Boot block code-protected<sup>(1)</sup>

- bit 5-0 Unimplemented: Read as '0'

Note 1: See Figure 24-5 for variable block boundaries.

| Legend:              |                    |                                     |

|----------------------|--------------------|-------------------------------------|

| R = Readable bit     | C = Clearable bit  | U = Unimplemented bit, read as '0'  |

| -n = Value when devi | ce is unprogrammed | u = Unchanged from programmed state |

#### REGISTER 24-12: DEVID1: DEVICE ID REGISTER 1 FOR PIC18F2221/2321/4221/4321 DEVICES

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-5 DEV<2:0>: Device ID bits

000 = PIC18F4321

010 = PIC18F4221

001 = PIC18F2321

011 = PIC18F2221

#### bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to indicate the device revision.

| Legend:                |                      |                                     |

|------------------------|----------------------|-------------------------------------|

| R = Read-only bit      | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device | e is unprogrammed    | u = Unchanged from programmed state |

#### REGISTER 24-13: DEVID2: DEVICE ID REGISTER 2 FOR PIC18F2221/2321/4221/4321 DEVICES

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

#### bit 7-0 DEV<10:3>: Device ID bits

These bits are used with the DEV<2:0> bits in the Device ID Register 1 to identify the part number.

0010 0001 = PIC18F2221/2321/4221/4321 devices

**Note:** These values for DEV<10:3> may be shared with other devices. The specific device is always identified by using the entire DEV<10:0> bit sequence.

| Legend:                |                      |                                     |

|------------------------|----------------------|-------------------------------------|

| R = Read-only bit      | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device | e is unprogrammed    | u = Unchanged from programmed state |

| ANDWF                                                      | AND W w                                                                                                                                                                            | ith f                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | BC          |                                                                                                              | Branch if                                                           | Carry                               |                 |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------|-----------------|

| Syntax:                                                    | ANDWF                                                                                                                                                                              | f {,d {,a}}                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Syntax:     |                                                                                                              | BC n                                                                |                                     |                 |

| Operands:                                                  | $0 \le f \le 255$                                                                                                                                                                  |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Operands:   |                                                                                                              | -128 ≤ n ≤ ′                                                        |                                     |                 |

|                                                            | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                             |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Operation:  |                                                                                                              | If Carry bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC              |                                     |                 |

| Operation:                                                 | (W) .AND.                                                                                                                                                                          | (f) $\rightarrow$ dest                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Status Affe | cted:                                                                                                        | None                                                                |                                     |                 |

| Status Affected:                                           | N, Z                                                                                                                                                                               |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Encoding:   |                                                                                                              | 1110                                                                | 0010 nnr                            | nn nnnn         |

| Encoding:<br>Description:                                  | register 'f. I<br>in W. If 'd' is<br>in register '<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode wher<br>Section 25 | he Access Ba<br>he BSR is use<br>(default).<br>nd the extend<br>led, this instru-<br>Literal Offset A<br>never $f \le 95$ (5<br><b>.2.3 "Byte-Or</b> | f       ffff         Ded with       Description:         besult is stored       If the Carry bit is '1', t         will branch.       will branch.         result is stored       The 2's complement n         added to the PC. Since       incremented to fetch f         is stored back       added to the PC. Since         k is selected.       instruction, the new a         to select the       PC + 2 + 2n. This inst         d instruction       Words:       1         ion operates       Cycles:       1(2)         h). See       Q Cycle Activity:         ented and       If Jump: |             | bit is '1', then<br>nplement num<br>e PC. Since the<br>d to fetch the r<br>the new addre<br>n. This instruct | the program<br>ber '2n' is<br>e PC will have<br>next<br>ess will be |                                     |                 |

|                                                            |                                                                                                                                                                                    | ed Instruction<br>set Mode" for                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             | Q1                                                                                                           | Q2                                                                  | Q3                                  | Q4              |

| Words:                                                     | 1                                                                                                                                                                                  |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | De          | code                                                                                                         | Read literal<br>'n'                                                 | Process<br>Data                     | Write to<br>PC  |

| Cycles:                                                    | 1                                                                                                                                                                                  |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             | No                                                                                                           | No                                                                  | No                                  | No              |

| Q Cycle Activity                                           | -                                                                                                                                                                                  |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | оре         | ration                                                                                                       | operation                                                           | operation                           | operation       |

| Q1                                                         | Q2                                                                                                                                                                                 | Q3                                                                                                                                                   | Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | lf No Jum   | D:                                                                                                           |                                                                     |                                     |                 |

| Decode                                                     | Read                                                                                                                                                                               | Process                                                                                                                                              | Write to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             | Q1                                                                                                           | Q2                                                                  | Q3                                  | Q4              |

|                                                            | register 'f'                                                                                                                                                                       | Data                                                                                                                                                 | destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | De          | code                                                                                                         | Read literal<br>'n'                                                 | Process<br>Data                     | No<br>operation |

| Example:<br>Before Instr<br>W<br>REG<br>After Instruc<br>W | = 17h<br>= C2h                                                                                                                                                                     | REG, 0, 0                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | After I     | e Instruc<br>PC<br>nstructio<br>If Carry<br>PC                                                               | = ad<br>on<br>= 1;                                                  | BC 5<br>dress (HERE)<br>dress (HERE |                 |

| BNC           |                                                      | Branch if Not Carry                                                                                                                                                                                                                                                                     |                             | BNN             |                       | Branch if                                                              | Branch if Not Negative                                                              |                                         |                 |  |  |

|---------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|-----------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------|-----------------|--|--|

| Synta         | ax:                                                  | BNC n                                                                                                                                                                                                                                                                                   |                             |                 | Synta                 | IX:                                                                    | BNN n                                                                               | BNN n                                   |                 |  |  |

| Oper          | ands:                                                | -128 ≤ n ≤ 127                                                                                                                                                                                                                                                                          |                             | Oper            | ands:                 | -128 ≤ n ≤ ′                                                           | 127                                                                                 |                                         |                 |  |  |

| Oper          | ation:                                               | If Carry bit i<br>(PC) + 2 + 2                                                                                                                                                                                                                                                          |                             |                 | Oper                  | ation:                                                                 | If Negative<br>(PC) + 2 +                                                           |                                         |                 |  |  |

| Statu         | s Affected:                                          | None                                                                                                                                                                                                                                                                                    |                             |                 | Statu                 | s Affected:                                                            | None                                                                                |                                         |                 |  |  |

| Enco          | ding:                                                | 1110                                                                                                                                                                                                                                                                                    | 0011 nnr                    | nn nnnn         | Enco                  | ding:                                                                  | 1110                                                                                | 0111 nr                                 | inn nnnn        |  |  |

| Description:  |                                                      | If the Carry bit is '0', then the program<br>will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |                             | Desc            | ription:              | program wi<br>The 2's cor<br>added to th<br>incremente<br>instruction, | nplement nun<br>e PC. Since th<br>d to fetch the<br>the new addr<br>n. This instruc | nber '2n' is<br>ne PC will have<br>next |                 |  |  |

| Word          | s:                                                   | 1                                                                                                                                                                                                                                                                                       |                             |                 | Word                  | s:                                                                     | 1                                                                                   |                                         |                 |  |  |

| Cycle         | es:                                                  | 1(2)                                                                                                                                                                                                                                                                                    |                             |                 | Cycle                 | S:                                                                     | 1(2)                                                                                |                                         |                 |  |  |

| Q Cy<br>If Ju | ycle Activity:<br>mp:                                |                                                                                                                                                                                                                                                                                         |                             |                 | Q C <u>y</u><br>If Ju | /cle Activity:<br>mp:                                                  |                                                                                     |                                         |                 |  |  |

|               | Q1                                                   | Q2                                                                                                                                                                                                                                                                                      | Q3                          | Q4              |                       | Q1                                                                     | Q2                                                                                  | Q3                                      | Q4              |  |  |

|               | Decode                                               | Read literal<br>'n'                                                                                                                                                                                                                                                                     | Process<br>Data             | Write to<br>PC  |                       | Decode                                                                 | Read literal<br>'n'                                                                 | Process<br>Data                         | Write to<br>PC  |  |  |

|               | No<br>operation                                      | No<br>operation                                                                                                                                                                                                                                                                         | No<br>operation             | No<br>operation |                       | No<br>operation                                                        | No<br>operation                                                                     | No<br>operation                         | No<br>operation |  |  |

| lf No         | Jump:                                                |                                                                                                                                                                                                                                                                                         |                             |                 | lf No                 | Jump:                                                                  |                                                                                     |                                         |                 |  |  |

|               | Q1                                                   | Q2                                                                                                                                                                                                                                                                                      | Q3                          | Q4              |                       | Q1                                                                     | Q2                                                                                  | Q3                                      | Q4              |  |  |

|               | Decode                                               | Read literal<br>'n'                                                                                                                                                                                                                                                                     | Process<br>Data             | No<br>operation |                       | Decode                                                                 | Read literal<br>'n'                                                                 | Process<br>Data                         | No<br>operation |  |  |

|               | Before Instruc<br>PC<br>After Instructio<br>If Carry | = ade<br>on<br>= 0;                                                                                                                                                                                                                                                                     | BNC Jump                    |                 |                       | Before Instruc<br>PC<br>After Instructi<br>If Negati                   | = ad<br>on<br>ve = 0;                                                               | BNN Jum <u>y</u><br>dress (HERE         | 2)              |  |  |

|               | PC<br>If Carry<br>PC                                 | = 1;                                                                                                                                                                                                                                                                                    | dress (Jump)<br>dress (HERE |                 |                       | If Negati                                                              | ve = 1;                                                                             | dress (Jump<br>dress (HERE              |                 |  |  |

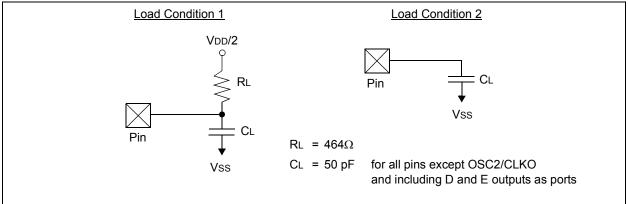

#### 27.4.2 TIMING CONDITIONS

The temperature and voltages specified in Table 27-5 apply to all timing specifications unless otherwise noted. Figure 27-5 specifies the load conditions for the timing specifications.

Note: Because of space limitations, the generic terms "PIC18FXXXX" and "PIC18LFXXXX" are used throughout this section to refer to the PIC18F2221/2321/4221/4321 and PIC18LF2221/2321/4221/4321 families of devices specifically and only those devices.

#### TABLE 27-5: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

| AC CHARACTERISTICS | Standard Operating Conditions (unless otherwise stated)                     |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------|--|--|--|--|--|

|                    | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |  |  |  |  |  |

|                    | $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended                        |  |  |  |  |  |

|                    | Operating voltage VDD range as described in DC spec Section 27.1 and        |  |  |  |  |  |

|                    | Section 27.3.                                                               |  |  |  |  |  |

|                    | LF parts operate for industrial temperatures only.                          |  |  |  |  |  |

#### FIGURE 27-5: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

| Param.<br>No. | Symbol  | Charac            | teristic                  | teristic Min N   |                  | Units | Conditions                             |

|---------------|---------|-------------------|---------------------------|------------------|------------------|-------|----------------------------------------|

| 100           | Тнідн   | Clock High Time   | 100 kHz mode              | 2(Tosc)(BRG + 1) |                  | ms    |                                        |