#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2321-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: DEVICE FEAT                   | URES                                                                                                         | 1                                                                                                            | 1                                                                                                            |                                                                                                              |  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| Features                                 | PIC18F2221                                                                                                   | PIC18F2321                                                                                                   | PIC18F4221                                                                                                   | PIC18F4321                                                                                                   |  |

| Operating Frequency                      | DC – 40 MHz                                                                                                  |  |

| Program Memory (Bytes)                   | 4096                                                                                                         | 8192                                                                                                         | 4096                                                                                                         | 8192                                                                                                         |  |

| Program Memory (Instructions)            | 2048                                                                                                         | 4096                                                                                                         | 2048                                                                                                         | 4096                                                                                                         |  |

| Data Memory (Bytes)                      | 512                                                                                                          | 512                                                                                                          | 512                                                                                                          | 512                                                                                                          |  |

| Data EEPROM Memory (Bytes)               | 256                                                                                                          | 256                                                                                                          | 256                                                                                                          | 256                                                                                                          |  |

| Interrupt Sources                        | 19                                                                                                           | 19                                                                                                           | 20                                                                                                           | 20                                                                                                           |  |

| I/O Ports                                | Ports A, B, C, (E)                                                                                           | Ports A, B, C, (E)                                                                                           | Ports A, B, C, D, E                                                                                          | Ports A, B, C, D, E                                                                                          |  |

| Timers                                   | 4                                                                                                            | 4                                                                                                            | 4                                                                                                            | 4                                                                                                            |  |

| Capture/Compare/PWM Modules              | 2                                                                                                            | 2                                                                                                            | 1                                                                                                            | 1                                                                                                            |  |

| Enhanced Capture/Compare/<br>PWM Modules | 0                                                                                                            | 0                                                                                                            | 1                                                                                                            | 1                                                                                                            |  |

| Serial Communications                    | MSSP,<br>Enhanced USART                                                                                      | MSSP, MSSP,<br>Enhanced USART Enhanced USART                                                                 |                                                                                                              | MSSP,<br>Enhanced USART                                                                                      |  |

| Parallel Communications (PSP)            | No                                                                                                           | No                                                                                                           | Yes                                                                                                          | Yes                                                                                                          |  |

| 10-bit Analog-to-Digital Module          | 10 Input Channels                                                                                            | 10 Input Channels                                                                                            | 13 Input Channels                                                                                            | 13 Input Channels                                                                                            |  |

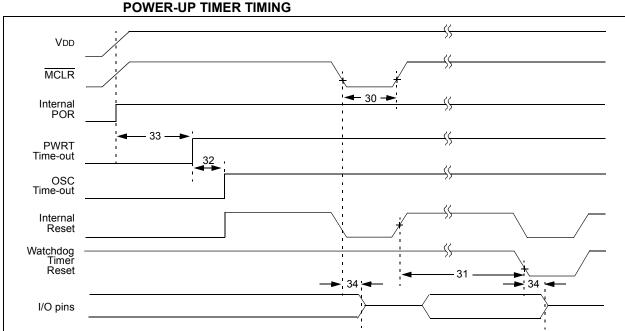

| Resets (and Delays)                      | POR, BOR,<br>RESET Instruction,<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST),<br>MCLR (optional),<br>WDT |  |

| Programmable Low-Voltage<br>Detect       | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          |  |

| Programmable Brown-out Reset             | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          |  |

| Instruction Set                          | 75 Instructions;<br>83 with Extended<br>Instruction Set<br>enabled                                           |  |

| Packages                                 | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN                                                     | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN                                                     | 40-pin PDIP<br>44-pin QFN<br>44-pin TQFP                                                                     | 40-pin PDIP<br>44-pin QFN<br>44-pin TQFP                                                                     |  |

### TABLE 1-1: DEVICE FEATURES

## 3.0 OSCILLATOR CONFIGURATIONS

### 3.1 Oscillator Types

The PIC18F2221/2321/4221/4321 family of devices can be operated in ten different oscillator modes. The user can program the Configuration bits, FOSC<3:0>, in Configuration Register 1H to select one of these ten modes:

- 1. LP Low-Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High-Speed Crystal/Resonator

- 4. HSPLL High-Speed Crystal/Resonator with PLL enabled

- 5. RC External Resistor/Capacitor with Fosc/4 output on RA6

- 6. RCIO External Resistor/Capacitor with I/O on RA6

- 7. INTIO1 Internal Oscillator with Fosc/4 output on RA6 and I/O on RA7

- 8. INTIO2 Internal Oscillator with I/O on RA6 and RA7

- 9. EC External Clock with Fosc/4 output

- 10. ECIO External Clock with I/O on RA6

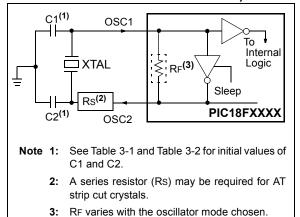

### 3.2 Crystal Oscillator/Ceramic Resonators

In XT, LP, HS or HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 3-1 shows the pin connections.

The oscillator design requires the use of a parallel cut crystal.

**Note:** Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications.

### FIGURE 3-1:

### CRYSTAL/CERAMIC RESONATOR OPERATION (XT, LP, HS OR HSPLL CONFIGURATION)

### TABLE 3-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| Typical Capacitor Values Used:                   |  |  |  |  |  |  |

|--------------------------------------------------|--|--|--|--|--|--|

| Mode Freq OSC1 OSC2                              |  |  |  |  |  |  |

| XT 3.58 MHz 22 pF 22 pF                          |  |  |  |  |  |  |

| On a site such as any few designs mulder as such |  |  |  |  |  |  |

### Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application. Refer to the following application notes for oscillator specific information:

- AN588, "PIC<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices"

- AN849, "Basic PIC<sup>®</sup> Oscillator Design"

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

See the notes following Table 3-2 for additional information.

Note: When using resonators with frequencies above 3.5 MHz, the use of HS mode, rather than XT mode, is recommended. HS mode may be used at any VDD for which the controller is rated. If HS is selected, it is possible that the gain of the oscillator will overdrive the resonator. Therefore, a series resistor may be placed between the OSC2 pin and the resonator. good starting а point. the As recommended value of Rs is 330Ω.

| File Name | Bit 7                                                                                                                                                                                                         | Bit 6                 | Bit 5           | Bit 4         | Bit 3          | Bit 2          | Bit 1            | Bit 0                                 | Value on<br>POR, BOR | Details or<br>page: |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|---------------|----------------|----------------|------------------|---------------------------------------|----------------------|---------------------|

| TOSU      | — — Top-of-Stack Upper Byte (TOS<20:16>)                                                                                                                                                                      |                       |                 |               |                |                |                  |                                       |                      | 55, 60              |

| TOSH      | Top-of-Stack                                                                                                                                                                                                  | High Byte (TC         | S<15:8>)        |               |                |                |                  |                                       | 0000 0000            | 55, 60              |

| TOSL      | Top-of-Stack                                                                                                                                                                                                  | Low Byte (TO          | S<7:0>)         |               |                |                |                  |                                       | 0000 0000            | 55, 60              |

| STKPTR    | STKFUL <sup>(6)</sup>                                                                                                                                                                                         | STKUNF <sup>(6)</sup> | _               | SP4           | SP3            | SP2            | SP1              | SP0                                   | 00-0 0000            | 55, 61              |

| PCLATU    | _                                                                                                                                                                                                             | _                     | Holding Regi    | ster for PC<2 | 1:16>          |                |                  |                                       | 00 0000              | 55, 60              |

| PCLATH    | Holding Regis                                                                                                                                                                                                 | ster for PC<15        | 5:8>            |               |                |                |                  |                                       | 0000 0000            | 55, 60              |

| PCL       | PC Low Byte                                                                                                                                                                                                   | (PC<7:0>)             |                 |               |                |                |                  |                                       | 0000 0000            | 55, 60              |

| TBLPTRU   | _                                                                                                                                                                                                             | _                     | bit 21          | Program Mei   | mory Table Poi | inter Upper By | te (TBLPTR<20    | ):16>)                                | 00 0000              | 55, 82              |

| TBLPTRH   | Program Mer                                                                                                                                                                                                   | nory Table Poi        | inter High Byte | e (TBLPTR<1   | 5:8>)          |                |                  |                                       | 0000 0000            | 55, 82              |

| TBLPTRL   | Program Men                                                                                                                                                                                                   | nory Table Poi        | inter Low Byte  | (TBLPTR<7:0   | 0>)            |                |                  |                                       | 0000 0000            | 55, 82              |

| TABLAT    | Program Men                                                                                                                                                                                                   | nory Table Lat        | ch              |               |                |                |                  |                                       | 0000 0000            | 55, 82              |

| PRODH     | Product Regi                                                                                                                                                                                                  | ster High Byte        |                 |               |                |                |                  |                                       | XXXX XXXX            | 55, 95              |

| PRODL     | Product Regi                                                                                                                                                                                                  | ster Low Byte         |                 |               |                |                |                  |                                       | XXXX XXXX            | 55, 95              |

| INTCON    | GIE/GIEH                                                                                                                                                                                                      | PEIE/GIEL             | TMR0IE          | INTOIE        | RBIE           | TMR0IF         | <b>INT0IF</b>    | RBIF                                  | 0000 000x            | 55, 99              |

| INTCON2   | RBPU                                                                                                                                                                                                          | INTEDG0               | INTEDG1         | INTEDG2       | _              | TMR0IP         | _                | RBIP                                  | 1111 -1-1            | 55, 100             |

| INTCON3   | INT2IP                                                                                                                                                                                                        | INT1IP                | _               | INT2IE        | INT1IE         | _              | INT2IF           | INT1IF                                | 11-0 0-00            | 55, 101             |

| INDF0     |                                                                                                                                                                                                               | s of FSR0 to a        | uddress data n  |               |                | changed (not a | a physical regis |                                       | N/A                  | 55, 74              |

| POSTINCO  |                                                                                                                                                                                                               |                       |                 | -             |                |                | (not a physical  | · · · · · · · · · · · · · · · · · · · | N/A                  | 55, 74              |

| POSTDEC0  |                                                                                                                                                                                                               |                       |                 | -             |                |                | (not a physica   |                                       | N/A                  | 55, 74              |

| PREINC0   |                                                                                                                                                                                                               |                       |                 | -             |                |                | not a physical r |                                       | N/A                  | 55, 74              |

| PLUSW0    |                                                                                                                                                                                                               | s of FSR0 to a        |                 | -             |                |                | not a physical r |                                       | N/A                  | 55, 74              |

| FSR0H     | _                                                                                                                                                                                                             | _                     | _               | _             | Indirect Data  | Memory Addre   | ess Pointer 0 H  | igh Byte                              | 0000                 | 55, 74              |

| FSR0L     | Indirect Data                                                                                                                                                                                                 | Memory Addr           | ess Pointer 0   | Low Byte      |                |                |                  |                                       | XXXX XXXX            | 55, 74              |

| WREG      | Working Regi                                                                                                                                                                                                  | ster                  |                 |               |                |                |                  |                                       | XXXX XXXX            | 55                  |

| INDF1     |                                                                                                                                                                                                               |                       | ddress data n   | nemory – valu | e of FSR1 not  | changed (not   | a physical regis | ter)                                  | N/A                  | 55, 74              |

| POSTINC1  | Uses content                                                                                                                                                                                                  | s of FSR1 to a        | ddress data n   | nemory – valu | e of FSR1 pos  | t-incremented  | (not a physical  | register)                             | N/A                  | 55, 74              |

| POSTDEC1  |                                                                                                                                                                                                               |                       |                 |               |                |                | I (not a physica |                                       | N/A                  | 55, 74              |

| PREINC1   |                                                                                                                                                                                                               |                       |                 | -             |                |                | not a physical r |                                       | N/A                  | 55, 74              |

| PLUSW1    |                                                                                                                                                                                                               | s of FSR1 to a        |                 | -             |                |                | not a physical r |                                       | N/A                  | 55, 74              |

| FSR1H     | _                                                                                                                                                                                                             | _                     | _               | _             | Indirect Data  | Memory Addre   | ess Pointer 1 H  | igh Byte                              | 0000                 | 56, 74              |

| FSR1L     | Indirect Data                                                                                                                                                                                                 | Memory Addr           | ess Pointer 1   | Low Byte      |                |                |                  |                                       | XXXX XXXX            | 56, 74              |

| BSR       | _                                                                                                                                                                                                             | _                     | _               | _             | Bank Select I  | Register       |                  |                                       | 0000                 | 56, 65              |

| INDF2     | Uses content                                                                                                                                                                                                  | s of FSR2 to a        | ddress data n   | nemory – valu | 1              | <u> </u>       | a physical regis | ter)                                  | N/A                  | 56, 74              |

| POSTINC2  | Uses contents of FSR2 to address data memory – value of FSR2 not changed (not a physical register)<br>Uses contents of FSR2 to address data memory – value of FSR2 post-incremented (not a physical register) |                       |                 |               |                |                | N/A              | 56, 74                                |                      |                     |

| POSTDEC2  | Uses content                                                                                                                                                                                                  | s of FSR2 to a        | address data n  | nemory – valu | e of FSR2 pos  | t-decremented  | I (not a physica | l register)                           | N/A                  | 56, 74              |

| PREINC2   |                                                                                                                                                                                                               |                       |                 |               |                |                | not a physical r |                                       | N/A                  | 56, 74              |

| PLUSW2    |                                                                                                                                                                                                               | s of FSR2 to a        |                 |               |                |                | not a physical r |                                       | N/A                  | 56, 74              |

| FSR2H     | _                                                                                                                                                                                                             | _                     | _               | _             | Indirect Data  | Memory Addre   | ess Pointer 2 H  | igh Byte                              | 0000                 | 56, 74              |

| FSR2L     | Indirect Data                                                                                                                                                                                                 | Memory Addr           | ess Pointer 2   | Low Byte      |                | , .            |                  |                                       | XXXX XXXX            | 56, 74              |

|           |                                                                                                                                                                                                               |                       |                 | -             |                |                |                  |                                       |                      | ,                   |

#### **TABLE 6-2**: **REGISTER FILE SUMMARY (PIC18F2221/2321/4221/4321)**

Note

The SBOREN bit is only available when the BOREN<1:0> Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)". 1:

2: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in 3: INTOSC Modes".

4: The RE3 bit is only available when Master Clear Reset is disabled (MCLRE Configuration bit = 0); otherwise, RE3 reads as '0'. This bit is read-only.

RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. 5: When disabled, these bits read as '0'.

6: Bit 7 and bit 6 are cleared by user software or by a POR.

### 10.6 INTx Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge; if the bit is clear, the trigger is on the falling edge. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit, INTxF, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxE. Flag bit, INTxF, must be cleared in software in the Interrupt.

All external interrupts (INT0, INT1 and INT2) can wakeup the processor from Idle or Sleep modes if bit INTxE was set prior to going into those modes. If the Global Interrupt Enable bit, GIE, is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high-priority interrupt source.

### 10.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit, TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). See Section 12.0 "Timer0 Module" for further details on the Timer0 module.

### 10.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

### **10.9 Context Saving During Interrupts**

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (see **Section 6.3 "Data Memory Organization"**), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 10-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| EXAMPLE 10-1: | SAVING STATUS, WREG AND BSR REGISTERS IN RAM |   |

|---------------|----------------------------------------------|---|

|               |                                              | 1 |

|          |                     | ·                              |

|----------|---------------------|--------------------------------|

| MOVWF    | W_TEMP              | ; W_TEMP is in virtual bank    |

| MOVFF    | STATUS, STATUS_TEMP | ; STATUS_TEMP located anywhere |

| MOVFF    | BSR, BSR_TEMP       | ; BSR_TMEP located anywhere    |

| ;        |                     |                                |

| ; USER : | ISR CODE            |                                |

| ;        |                     |                                |

| MOVFF    | BSR_TEMP, BSR       | ; Restore BSR                  |

| MOVF     | W_TEMP, W           | ; Restore WREG                 |

| MOVFF    | STATUS_TEMP, STATUS | ; Restore STATUS               |

|          |                     |                                |

### 11.4 PORTD, TRISD and LATD Registers

| Note: | PORTD    | is | only | available | on | 40/44-pin |

|-------|----------|----|------|-----------|----|-----------|

|       | devices. |    |      |           |    |           |

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

Three of the PORTD pins are multiplexed with outputs P1B, P1C and P1D of the Enhanced CCP module. The operation of these additional PWM output pins is covered in greater detail in Section 17.0 "Enhanced Capture/Compare/PWM (ECCP) Module".

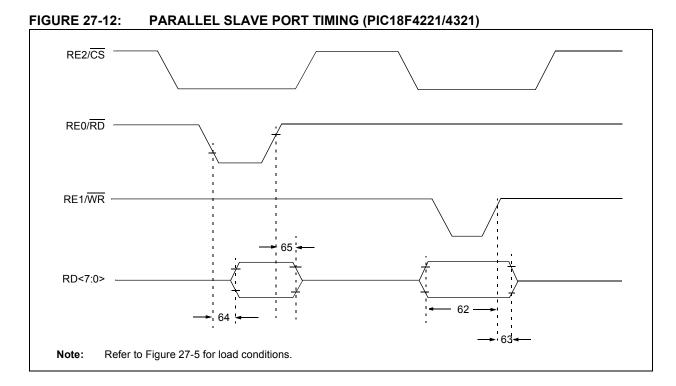

Note: On a Power-on Reset, these pins are configured as digital inputs. PORTD can also be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit, PSPMODE (TRISE<4>). In this mode, the input buffers are TTL. See **Section 11.6 "Parallel Slave Port"** for additional information on the Parallel Slave Port (PSP).

| Note: | When the Enhanced PWM mode is used        |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|

|       | with either dual or quad outputs, the PSP |  |  |  |  |  |  |  |  |

|       | functions of PORTD are automatically      |  |  |  |  |  |  |  |  |

|       | disabled.                                 |  |  |  |  |  |  |  |  |

### EXAMPLE 11-4: INITIALIZING PORTD

| CLRF  | PORTD | ; Initialize PORTD by<br>; clearing output<br>: data latches |

|-------|-------|--------------------------------------------------------------|

| CLRF  | LATD  | ; Alternate method                                           |

|       |       | ; to clear output                                            |

|       |       | ; data latches                                               |

| MOVLW | OCFh  | ; Value used to                                              |

|       |       | ; initialize data                                            |

|       |       | ; direction                                                  |

| MOVWF | TRISD | ; Set RD<3:0> as inputs                                      |

|       |       | ; RD<5:4> as outputs                                         |

|       |       | ; RD<7:6> as inputs                                          |

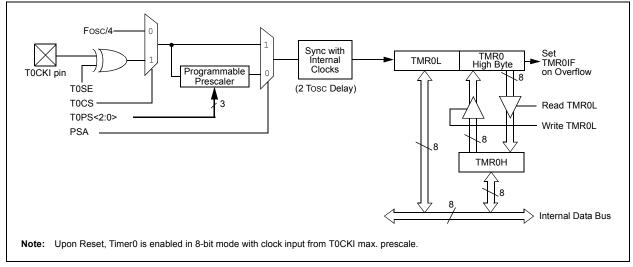

### 12.1 Timer0 Operation

Timer0 can operate as either a timer or a counter; the mode is selected with the TOCS bit (TOCON<5>). In Timer mode (TOCS = 0), the module increments on every clock by default unless a different prescaler value is selected (see **Section 12.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the T0CS bit (= 1). In this mode, Timer0 increments either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (T0CON<4>); clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

### 12.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode; it is actually a buffered version of the real high byte of Timer0 which is not directly readable nor writable (refer to Figure 12-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

### FIGURE 12-1: TIMER0 BLOCK DIAGRAM (8-BIT MODE)

### FIGURE 12-2: TIMER0 BLOCK DIAGRAM (16-BIT MODE)

### 16.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

### 16.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers 1, 2 or 3, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode.

## TABLE 16-1:CCP MODE – TIMER<br/>RESOURCES

| CCP/ECCP Mode | Timer Resource   |

|---------------|------------------|

| Capture       | Timer1 or Timer3 |

| Compare       | Timer1 or Timer3 |

| PWM           | Timer2           |

The assignment of a particular timer to a module is determined by the Timer to CCP enable bits in the T3CON register (Register 15-1). Both modules may be active at any given time and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time. The interactions between the two modules are summarized in Figure 16-1 and Figure 16-2. In Timer1 in Asynchronous Counter mode, the capture operation will not work.

### 16.1.2 CCP2 PIN ASSIGNMENT

The pin assignment for CCP2 (Capture input, Compare and PWM output) can change, based on device configuration. The CCP2MX Configuration bit determines which pin CCP2 is multiplexed to. By default, it is assigned to RC1 (CCP2MX = 1). If the Configuration bit is cleared, CCP2 is multiplexed with RB3.

Changing the pin assignment of CCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for CCP2 operation, regardless of where it is located.

| CCP1 Mode          | CCP2 Mode          | Interaction                                                                                                                                                                                                                                                         |

|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capture            | Capture            | Each module can use TMR1 or TMR3 as the time base. The time base can be different for each CCP.                                                                                                                                                                     |

| Capture            | Compare            | CCP2 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Automatic A/D conversions on trigger event can also be done. Operation of CCP1 could be affected if it is using the same timer as a time base. |

| Compare            | Capture            | CCP1 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Operation of CCP2 could be affected if it is using the same timer as a time base.                                                              |

| Compare            | Compare            | Either module can be configured for the Special Event Trigger to reset the time base.<br>Automatic A/D conversions on CCP2 trigger event can be done. Conflicts may occur if<br>both modules are using the same time base.                                          |

| Capture            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| Compare            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Capture            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Compare            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | PWM                | Both PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                                                                                                                                            |

### TABLE 16-2: INTERACTIONS BETWEEN CCP1 AND CCP2 FOR TIMER RESOURCES

**Note 1:** Includes standard and Enhanced PWM operation.

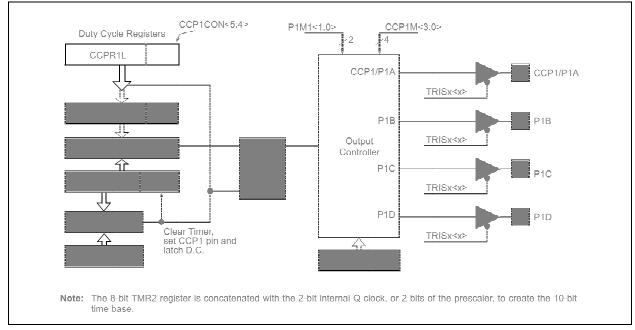

### 17.4 Enhanced PWM Mode

The Enhanced PWM mode provides additional PWM output options for a broader range of control applications. The module is a backward compatible version of the standard CCP module and offers up to four outputs, designated P1A through P1D. Users are also able to select the polarity of the signal (either active-high or active-low). The module's output mode and polarity are configured by setting the P1M<1:0> and CCP1M<3:0> bits of the CCP1CON register.

Figure 17-1 shows a simplified block diagram of PWM operation. All control registers are double-buffered and are loaded at the beginning of a new PWM cycle (the period boundary when Timer2 resets) in order to prevent glitches on any of the outputs. The exception is the PWM Dead-Band Delay register, ECCP1DEL, which is loaded at either the duty cycle boundary or the period boundary (whichever comes first). Because of the buffering, the module waits until the assigned timer resets, instead of starting immediately. This means that Enhanced PWM waveforms do not exactly match the standard PWM waveforms, but are instead offset by one full instruction cycle (4 Tosc).

As before, the user must manually configure the appropriate TRIS bits for output.

### 17.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following equation.

### EQUATION 17-1:

$$PWM Period = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 Prescale Value)$$

PWM frequency is defined as 1/[PWM period]. When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is copied from CCPR1L into CCPR1H

- Note: The Timer2 postscaler (see Section 14.0 "Timer2 Module") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

## FIGURE 17-1: SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODULE

| REGISTER 17-3: | ECCP1AS                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                             | JRE/COMP                                  | PARE/PW     | M AUTO-  | SHUTDOW               | N                     |  |

|----------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------|-------------|----------|-----------------------|-----------------------|--|

|                | R/W-0                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                       | R/W-0                                     | R/W-0       | R/W-0    | R/W-0                 | R/W-0                 |  |

|                | ECCPASE                                                                         | ECCPAS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ECCPAS1                                     | ECCPAS0                                   | PSSAC1      | PSSAC0   | PSSBD1 <sup>(1)</sup> | PSSBD0 <sup>(1)</sup> |  |

|                | bit 7                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                             |                                           |             |          |                       | bit 0                 |  |

| bit 7          | ECCPASE:                                                                        | ECCP Auto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -Shutdown                                   | Event Status                              | bit         |          |                       |                       |  |

|                | 1 = A shuto<br>0 = ECCP                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                             | d; ECCP out                               | puts are in | shutdown | state                 |                       |  |

| bit 6-4        | ECCPAS<2                                                                        | :0>: ECCP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Auto-Shutdo                                 | own Source                                | Select bits |          |                       |                       |  |

|                | 110 = FLT0<br>101 = FLT0<br>100 = FLT0<br>011 = Eithe<br>010 = Com<br>001 = Com | <pre>111 = FLT0 or Comparator 1 or Comparator 2<br/>110 = FLT0 or Comparator 2<br/>101 = FLT0 or Comparator 1<br/>100 = FLT0<br/>011 = Either Comparator 1 or 2<br/>010 = Comparator 2 output<br/>001 = Comparator 1 output<br/>000 = Auto-shutdown is disabled</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                             |                                           |             |          |                       |                       |  |

| bit 3-2        | 1x = Pins A                                                                     | and C are t<br>output is tri-<br>Pins A and C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ri-state (40/4<br>state (28-pin<br>C to '1' | own State Co<br>44-pin device<br>devices) |             |          |                       |                       |  |

| bit 1-0        | <b>PSSBD&lt;1:</b><br>1x = Pins B<br>01 = Drive I<br>00 = Drive I               | <b>D&gt;:</b> Pins B a and D tri-st Pins B and D tri-st Pins B and D tri-st Pins B and D | nd D Shutdo<br>ate<br>D to '1'<br>D to '0'  | own State Co<br>bin devices; I            |             |          |                       |                       |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

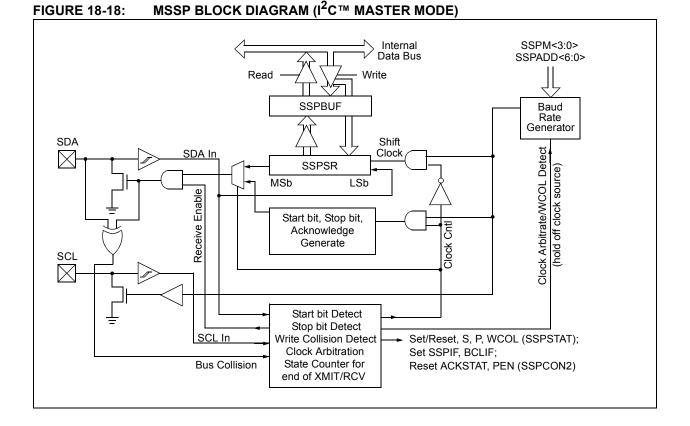

### 18.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPIF, to be set (MSSP interrupt, if enabled):

- · Start condition

- Stop condition

- · Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated Start

## 19.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of the two serial I/O modules. (Generically, the USART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a halfduplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN/J2602 bus) systems.

The EUSART can be configured in the following modes:

- Asynchronous (full duplex) with:

- Auto-wake-up on Break signal

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half duplex) with selectable clock polarity

- Synchronous Slave (half duplex) with selectable clock polarity

The pins of the Enhanced USART are multiplexed with PORTC. In order to configure RC6/TX/CK and RC7/RX/DT as an EUSART:

- bit SPEN (RCSTA<7>) must be set (= 1)

- bit TRISC<7> must be set (= 1)

- bit TRISC<6> must be set (= 1)

| Note: | The EUSART control will automatically               |

|-------|-----------------------------------------------------|

|       | reconfigure the pin from input to output as needed. |

The operation of the Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These are detailed on the following pages in Register 19-1, Register 19-2 and Register 19-3, respectively.

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                       |            |                             |                       |            |                             |                       |            |                             |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|

| BAUD<br>RATE | Fosc = 40.000 MHz     |                               |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |