Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D.L.II.                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Details                    |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2321-i-ss |

TABLE 3-2: CAPACITOR SELECTION FOR QUARTZ CRYSTALS

| Osc Type | Crystal<br>Freq                     | Typical Capacitor Values Tested: |                                  |  |  |  |

|----------|-------------------------------------|----------------------------------|----------------------------------|--|--|--|

|          | rieq                                | C1                               | C2                               |  |  |  |

| LP       | 32 kHz                              | 22 pF                            | 22 pF                            |  |  |  |

| XT       | 1 MHz<br>4 MHz                      | 22 pF<br>22 pF                   | 22 pF<br>22 pF                   |  |  |  |

| HS       | 4 MHz<br>10 MHz<br>20 MHz<br>25 MHz | 22 pF<br>22 pF<br>22 pF<br>22 pF | 22 pF<br>22 pF<br>22 pF<br>22 pF |  |  |  |

### Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application. Refer to the following application notes for oscillator specific information:

- AN588, "PIC<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices"

- AN849, "Basic PIC® Oscillator Design"

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design"

- · AN949, "Making Your Oscillator Work"

See the notes following this table for additional information.

- **Note 1:** Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 2: When operating below 3V VDD, or when using certain ceramic resonators at any voltage, it may be necessary to use the HS mode or switch to a crystal oscillator.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **4:** Rs may be required to avoid overdriving crystals with low drive level specification.

- 5: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

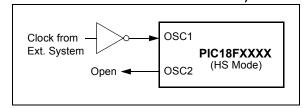

An external clock source may also be connected to the OSC1 pin in the HS mode, as shown in Figure 3-2. When operated in this mode, parameters D033 and D043 apply.

FIGURE 3-2: EXTERNAL CLOCK INPUT OPERATION (HS OSC CONFIGURATION)

### 3.3 External Clock Input

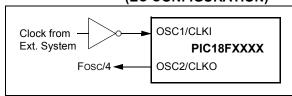

The EC and ECIO Oscillator modes require an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

In the EC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 3-3 shows the pin connections for the EC Oscillator mode.

FIGURE 3-3: EXTERNAL CLOCK INPUT OPERATION (EC CONFIGURATION)

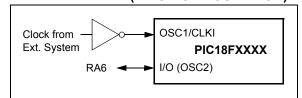

The ECIO Oscillator mode functions like the EC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 3-4 shows the pin connections for the ECIO Oscillator mode. When operated in this mode, parameters D033A and D043A apply.

FIGURE 3-4: EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

### 4.4.3 RC IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. Although its value is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCF bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to any non-zero value, or the INTSRC bit is set, the INTOSC output is enabled. The IOFS bit becomes set, after the INTOSC output becomes stable, after an interval of TIOBST (parameter 39, Table 27-10). Clocks to the peripherals continue while the INTOSC source stabilizes. If the IRCF bits were previously at a non-zero value, or INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set. If the IRCF bits and INTSRC are all clear, the INTOSC output will not be enabled, the IOFS bit will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD following the wake event, the CPU begins executing code being clocked by the INTOSC multiplexer. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

### 4.5 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes (see Section 4.2 "Run Modes", Section 4.3 "Sleep Mode" and Section 4.4 "Idle Modes").

#### 4.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode, or the Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see **Section 10.0 "Interrupts"**).

A fixed delay of interval TCSD following the wake event is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

#### 4.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 4.2 "Run Modes" and Section 4.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 24.2 "Watchdog Timer (WDT)").

The WDT timer and postscaler are cleared by executing a SLEEP or CLRWDT instruction, the loss of a currently selected clock source (if the Fail-Safe Clock Monitor is enabled) and modifying the IRCF bits in the OSCCON register if the internal oscillator block is the device clock source.

#### 4.5.3 EXIT BY RESET

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock becomes ready. At that time, the OSTS bit is set and the device begins executing code. If the internal oscillator block is the new clock source, the IOFS bit is set instead.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up and the type of oscillator if the new clock source is the primary clock. Exit delays are summarized in Table 4-2.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see Section 24.3 "Two-Speed Start-up") or Fail-Safe Clock Monitor (see Section 24.4 "Fail-Safe Clock Monitor") is enabled, the device may begin execution as soon as the Reset source has cleared. Execution is clocked by the INTOSC multiplexer driven by the internal oscillator block. Execution is clocked by the internal oscillator block until either the primary clock becomes ready or a power-managed mode is entered before the primary clock becomes ready; the primary clock is then shut down.

#### 5.5 Device Reset Timers

PIC18F2221/2321/4221/4321 family devices incorporate three separate on-chip timers that help regulate the Power-on Reset process. Their main function is to ensure that the device clock is stable before code is executed. These timers are:

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- · PLL Lock Time-out

### 5.5.1 POWER-UP TIMER (PWRT)

The Power-up Timer (PWRT) of the PIC18F2221/2321/4221/4321 family devices is an 11-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip to chip due to temperature and process variation. See DC parameter 33 for details.

The PWRT is enabled by clearing the PWRTEN Configuration bit.

# 5.5.2 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter 33). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP, HS and HSPLL modes and only on Power-on Reset, or on exit from most power-managed modes.

#### 5.5.3 PLL LOCK TIME-OUT

With the PLL enabled in HSPLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A separate timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

#### 5.5.4 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows:

- 1. After the POR pulse has cleared, PWRT time-out is invoked (if enabled).

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and the status of the PWRT. Figure 5-3, Figure 5-4, Figure 5-5, Figure 5-6 and Figure 5-7 all depict time-out sequences on power-up, with the Power-up Timer enabled and the device operating in HS Oscillator mode. Figures 5-3 through 5-6 also apply to devices operating in XT or LP modes. For devices in RC mode and with the PWRT disabled, there will be no time-out at all.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, all time-outs will expire. Bringing MCLR high will begin execution immediately (Figure 5-5). This is useful for testing purposes or to synchronize more than one PIC18FXXXX device operating in parallel.

TABLE 5-2: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator     | Power-up <sup>(2)</sup> and I                          | Brown-out Reset                 | Exit from                       |

|----------------|--------------------------------------------------------|---------------------------------|---------------------------------|

| Configuration  | PWRTEN = 0                                             | PWRTEN = 1                      | Power-Managed Mode              |

| HSPLL          | 66 ms <sup>(1)</sup> + 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> |

| HS, XT, LP     | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                       | 1024 Tosc                       |

| EC, ECIO       | 66 ms <sup>(1)</sup>                                   | _                               | _                               |

| RC, RCIO       | 66 ms <sup>(1)</sup>                                   | _                               | _                               |

| INTIO1, INTIO2 | 66 ms <sup>(1)</sup>                                   | <del></del>                     | _                               |

Note 1: 66 ms (65.5 ms) is the nominal Power-up Timer (PWRT) delay.

2: 2 ms is the nominal time required for the PLL to lock.

The PLUSW register can be used to implement a form of indexed addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

### 6.4.3.3 Operations by FSRs on FSRs

Indirect addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to INDF2 or POSTDEC2 will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses indirect addressing.

Similarly, operations by indirect addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

# 6.5 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different. This is due to the introduction of a new addressing mode for the data memory space.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect addressing with FSR0 and FSR1 also remain unchanged.

# 6.5.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of indirect addressing using the FSR2 register pair within Access RAM. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of indexed addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0); and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in direct addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

# 6.5.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use direct addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is shown in Figure 6-8.

Those who desire to use bit-oriented or byte-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 24.2.1** "Extended Instruction Syntax".

#### 7.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

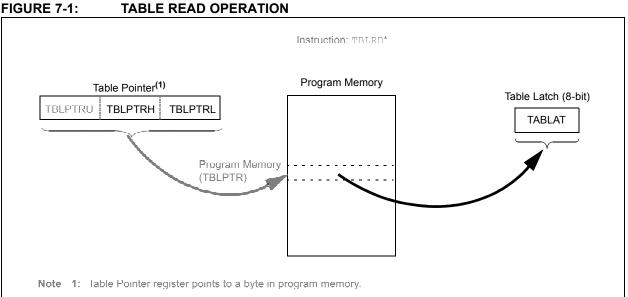

#### 7.1 **Table Reads and Table Writes**

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 7-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in Section 7.5 "Writing to Flash Program Memory". Figure 7-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word-aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned.

FIGURE 7-1:

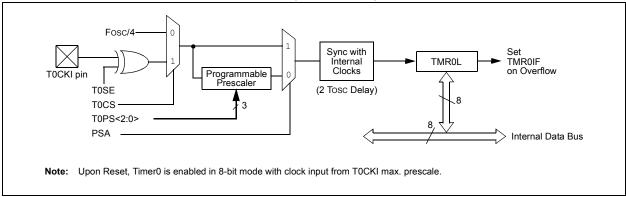

### 12.1 Timer0 Operation

Timer0 can operate as either a timer or a counter; the mode is selected with the T0CS bit (T0CON<5>). In Timer mode (T0CS = 0), the module increments on every clock by default unless a different prescaler value is selected (see **Section 12.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the T0CS bit (= 1). In this mode, Timer0 increments either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (T0CON<4>); clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the

internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

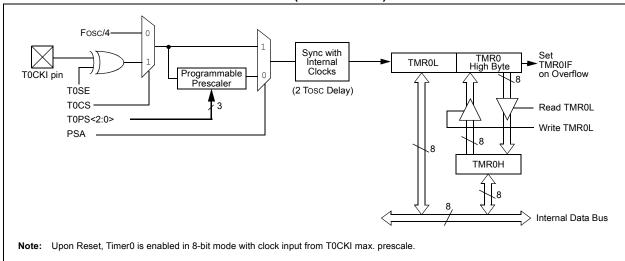

# 12.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode; it is actually a buffered version of the real high byte of Timer0 which is not directly readable nor writable (refer to Figure 12-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

### FIGURE 12-1: TIMER0 BLOCK DIAGRAM (8-BIT MODE)

#### FIGURE 12-2: TIMERO BLOCK DIAGRAM (16-BIT MODE)

TABLE 16-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

| Name    | Bit 7                                    | Bit 6                         | Bit 5              | Bit 4     | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |  |  |

|---------|------------------------------------------|-------------------------------|--------------------|-----------|---------|--------|--------|--------|----------------------------|--|--|

| INTCON  | GIE/GIEH                                 | PEIE/GIEL                     | TMR0IE             | INT0IE    | RBIE    | TMR0IF | INT0IF | RBIF   | 55                         |  |  |

| RCON    | IPEN                                     | SBOREN <sup>(1)</sup>         | — RI TO PD POR BOR |           |         |        |        | 54     |                            |  |  |

| PIR1    | PSPIF <sup>(2)</sup>                     | ADIF                          | RCIF               | TXIF      | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 58                         |  |  |

| PIE1    | PSPIE <sup>(2)</sup>                     | ADIE                          | RCIE               | TXIE      | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 58                         |  |  |

| IPR1    | PSPIP <sup>(2)</sup>                     | ADIP                          | RCIP               | TXIP      | SSPIP   | CCP1IP | TMR2IP | TMR1IP | 58                         |  |  |

| PIR2    | OSCFIF                                   | CMIF                          | _                  | EEIF      | BCLIF   | HLVDIF | TMR3IF | CCP2IF | 58                         |  |  |

| PIE2    | OSCFIE                                   | CMIE                          | _                  | EEIE      | BCLIE   | HLVDIE | TMR3IE | CCP2IE | 58                         |  |  |

| IPR2    | OSCFIP                                   | CMIP                          | -                  | EEIP      | BCLIP   | HLVDIP | TMR3IP | CCP2IP | 58                         |  |  |

| TRISB   | PORTB Da                                 | PORTB Data Direction Register |                    |           |         |        |        |        |                            |  |  |

| TRISC   | PORTC Da                                 | ta Direction                  | Register           |           |         |        |        |        | 58                         |  |  |

| TMR1L   | Timer1 Reg                               | gister Low By                 | yte                |           |         |        |        |        | 56                         |  |  |

| TMR1H   | Timer1 Reg                               | gister High B                 | yte                |           |         |        |        |        | 56                         |  |  |

| T1CON   | RD16                                     | T1RUN                         | T1CKPS1            | T1CKPS0   | T10SCEN | T1SYNC | TMR1CS | TMR10N | 56                         |  |  |

| TMR3H   | Timer3 Reg                               | gister High B                 | yte                |           |         |        |        |        | 57                         |  |  |

| TMR3L   | Timer3 Reg                               | gister Low By                 | yte                |           |         |        |        |        | 57                         |  |  |

| T3CON   | RD16                                     | T3CCP2                        | T3CKPS1            | T3CKPS0   | T3CCP1  | T3SYNC | TMR3CS | TMR3ON | 57                         |  |  |

| CCPR1L  | Capture/Co                               | mpare/PWN                     | / Register 1       | Low Byte  |         |        |        |        | 57                         |  |  |

| CCPR1H  | Capture/Co                               | mpare/PWN                     | /I Register 1      | High Byte |         |        |        |        | 57                         |  |  |

| CCP1CON | P1M1 <sup>(2)</sup>                      | P1M0 <sup>(2)</sup>           | DC1B1              | DC1B0     | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0 | 57                         |  |  |

| CCPR2L  | Capture/Co                               | mpare/PWN                     | /I Register 2      | Low Byte  |         |        |        |        | 57                         |  |  |

| CCPR2H  | Capture/Compare/PWM Register 2 High Byte |                               |                    |           |         |        |        |        |                            |  |  |

| CCP2CON | _                                        | _                             | DC2B1              | DC2B0     | CCP2M3  | CCP2M2 | CCP2M1 | CCP2M0 | 57                         |  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by Capture/Compare, Timer1 or Timer3.

**Note 1:** The SBOREN bit is only available when the BOREN<1:0> Configuration bits = 01; otherwise, it is disabled and reads as '0'. See **Section 5.4 "Brown-out Reset (BOR)"**.

<sup>2:</sup> These bits are unimplemented on 28-pin devices and read as '0'.

Note:

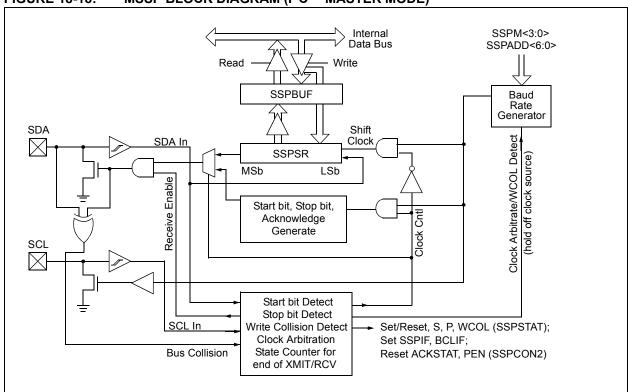

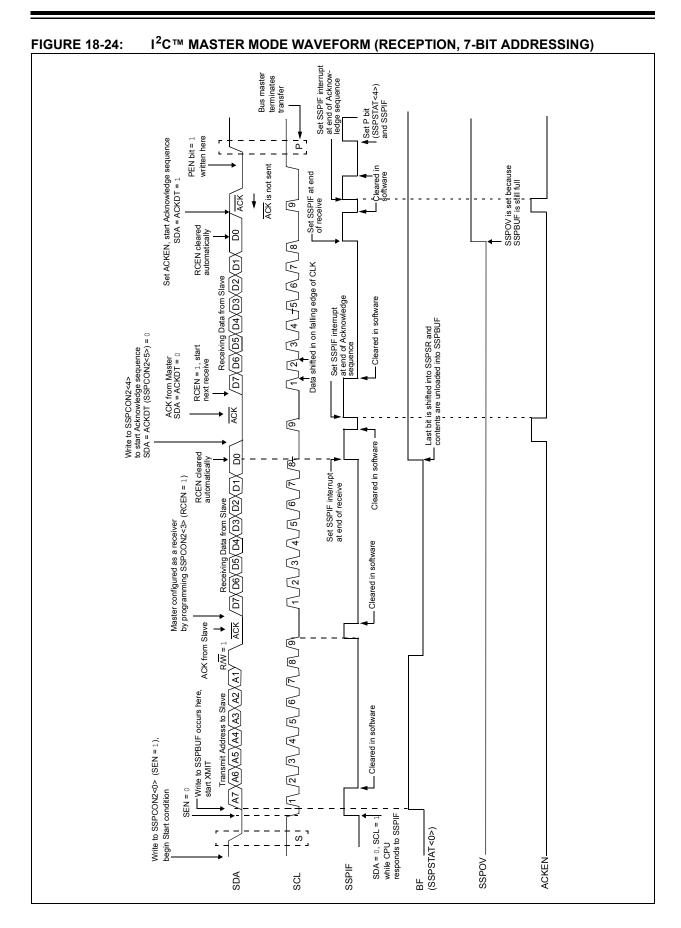

#### 18.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $\rm I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- Assert a Repeated Start condition on SDA and SCL.

- Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPIF, to be set (MSSP interrupt, if enabled):

- · Start condition

- Stop condition

- · Data transfer byte transmitted/received

- · Acknowledge transmit

- · Repeated Start

FIGURE 18-18: MSSP BLOCK DIAGRAM (I<sup>2</sup>C™ MASTER MODE)

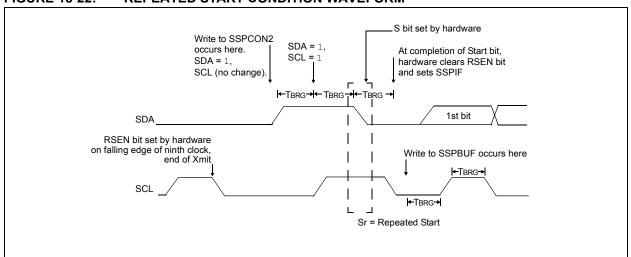

# 18.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins. the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

**Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

#### 18.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

FIGURE 18-22: REPEATED START CONDITION WAVEFORM

TABLE 19-3: BAUD RATES FOR ASYNCHRONOUS MODES

|              |                       |            |                             |                       | SYNC       | = 0, BRGH                   | l = 0, BRG            | <b>316 =</b> 0 |                             |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc                  | = 40.000   | MHz                         | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |                |                             | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | _                     | _          | _                           | _                     | _          | _                           | _                     | _              | _                           | _                     | _          | _                           |

| 1.2          | _                     | _          | _                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16           | 129                         | 1.201                 | -0.16      | 103                         |

| 2.4          | 2.441                 | 1.73       | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16           | 64                          | 2.403                 | -0.16      | 51                          |

| 9.6          | 9.615                 | 0.16       | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73           | 15                          | 9.615                 | -0.16      | 12                          |

| 19.2         | 19.531                | 1.73       | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73           | 7                           | _                     | _          | _                           |

| 57.6         | 56.818                | -1.36      | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58          | 2                           | _                     | _          | _                           |

| 115.2        | 125.000               | 8.51       | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18         | 1                           |                       | _          | _                           |

|             |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |  |  |  |  |  |

|-------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|--|

| BAUD        | Fos                   | c = 4.000                     | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |  |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |  |

| 0.3         | 0.300                 | 0.16                          | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |  |  |  |  |  |

| 1.2         | 1.202                 | 0.16                          | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |  |  |  |  |  |

| 2.4         | 2.404                 | 0.16                          | 25                          | 2.403                 | -0.16      | 12                          | _                     | _          | _                           |  |  |  |  |  |

| 9.6         | 8.929                 | -6.99                         | 6                           | _                     | _          | _                           | _                     | _          | _                           |  |  |  |  |  |

| 19.2        | 20.833                | 8.51                          | 2                           | _                     | _          | _                           | _                     | _          | _                           |  |  |  |  |  |

| 57.6        | 62.500                | 8.51                          | 0                           | _                     | _          | _                           | _                     | _          | _                           |  |  |  |  |  |

| 115.2       | 62.500                | -45.75                        | 0                           |                       | _          | _                           | -                     | _          | _                           |  |  |  |  |  |

|             |                       |          |       |                       | SYNC       | = 0, BRGH                   | l = 1, BRG            | 16 = 0     |                             |                       |            |                             |

|-------------|-----------------------|----------|-------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc                  | = 40.000 | ) MHz | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | Rate     |       | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | _                     | _        | _     | _                     | _          | _                           | -                     | _          | _                           | _                     | _          | _                           |

| 1.2         | _                     | _        | _     | _                     | _          | _                           | _                     | _          | _                           | _                     | _          | _                           |

| 2.4         | _                     | _        | _     | _                     | _          | _                           | 2.441                 | 1.73       | 255                         | 2.403                 | -0.16      | 207                         |

| 9.6         | 9.766                 | 1.73     | 255   | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |

| 19.2        | 19.231                | 0.16     | 129   | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |

| 57.6        | 58.140                | 0.94     | 42    | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |

| 115.2       | 113.636               | -1.36    | 21    | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | _                     | _          | _                           |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |  |  |  |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|--|

| BAUD<br>RATE | Fosc                  | c = 4.000                     | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |  |

| 0.3          | _                     | _                             | _                           |                       | _          | _                           | 0.300                 | -0.16      | 207                         |  |  |  |  |  |

| 1.2          | 1.202                 | 0.16                          | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |  |  |  |  |

| 2.4          | 2.404                 | 0.16                          | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |  |  |  |  |

| 9.6          | 9.615                 | 0.16                          | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | _                           |  |  |  |  |  |

| 19.2         | 19.231                | 0.16                          | 12                          | _                     | _          | _                           | _                     | _          | _                           |  |  |  |  |  |

| 57.6         | 62.500                | 8.51                          | 3                           | _                     | _          | _                           | _                     | _          | _                           |  |  |  |  |  |

| 115.2        | 125.000               | 8.51                          | 1                           | _                     | _          | _                           | _                     | _          | _                           |  |  |  |  |  |

TABLE 19-3: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|              |                       |            |                             |                       | SYNC       | = 0, BRG                    | l = 0, BRG            | 16 = 1     |                             |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc                  | = 40.000   | ) MHz                       | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.00       | 8332                        | 0.300                 | 0.02       | 4165                        | 0.300                 | 0.02       | 2082                        | 0.300                 | -0.04      | 1665                        |

| 1.2          | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.03      | 1041                        | 1.200                 | -0.03      | 520                         | 1.201                 | -0.16      | 415                         |

| 2.4          | 2.402                 | 0.06       | 1040                        | 2.399                 | -0.03      | 520                         | 2.404                 | 0.16       | 259                         | 2.403                 | -0.16      | 207                         |

| 9.6          | 9.615                 | 0.16       | 259                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |

| 19.2         | 19.231                | 0.16       | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |

| 57.6         | 58.140                | 0.94       | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |

| 115.2        | 113.636               | -1.36      | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           |                       | _          | _                           |

|             |                       |            | s                           | YNC = 0, E            | BRGH = 0   | o, BRG16 =                  | 1                     |            |                             |  |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|

| BAUD        | Fosc                  | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 0.3         | 0.300                 | 0.04       | 832                         | 0.300                 | -0.16      | 415                         | 0.300                 | -0.16      | 207                         |  |

| 1.2         | 1.202                 | 0.16       | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |

| 2.4         | 2.404                 | 0.16       | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |

| 9.6         | 9.615                 | 0.16       | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | _                           |  |

| 19.2        | 19.231                | 0.16       | 12                          | _                     | _          | _                           | _                     | _          | _                           |  |

| 57.6        | 62.500                | 8.51       | 3                           | _                     | _          | _                           | _                     | _          | _                           |  |

| 115.2       | 125.000               | 8.51       | 1                           | _                     | _          | _                           | _                     | _          | _                           |  |

|              |                       |            |                             | SYNC = 0,             | BRGH :     | = 1, BRG16                  | = 1 or SY             | NC = 1,    | BRG16 = 1                   |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc                  | = 40.000   | ) MHz                       | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.00       | 33332                       | 0.300                 | 0.00       | 16665                       | 0.300                 | 0.00       | 8332                        | 0.300                 | -0.01      | 6665                        |

| 1.2          | 1.200                 | 0.00       | 8332                        | 1.200                 | 0.02       | 4165                        | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.04      | 1665                        |

| 2.4          | 2.400                 | 0.02       | 4165                        | 2.400                 | 0.02       | 2082                        | 2.402                 | 0.06       | 1040                        | 2.400                 | -0.04      | 832                         |

| 9.6          | 9.606                 | 0.06       | 1040                        | 9.596                 | -0.03      | 520                         | 9.615                 | 0.16       | 259                         | 9.615                 | -0.16      | 207                         |

| 19.2         | 19.193                | -0.03      | 520                         | 19.231                | 0.16       | 259                         | 19.231                | 0.16       | 129                         | 19.230                | -0.16      | 103                         |

| 57.6         | 57.803                | 0.35       | 172                         | 57.471                | -0.22      | 86                          | 58.140                | 0.94       | 42                          | 57.142                | 0.79       | 34                          |

| 115.2        | 114.943               | -0.22      | 86                          | 116.279               | 0.94       | 42                          | 113.636               | -1.36      | 21                          | 117.647               | -2.12      | 16                          |

|             |                       | SYN        | IC = 0, BR                  | GH = 1, BI            | RG16 = 1   | or SYNC =                   | 1, BRG1               | 6 = 1            |                             |  |  |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------------|-----------------------------|--|--|

| BAUD        | Fos                   | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fos                   | Fosc = 1.000 MHz |                             |  |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |

| 0.3         | 0.300                 | 0.01       | 3332                        | 0.300                 | -0.04      | 1665                        | 0.300                 | -0.04            | 832                         |  |  |

| 1.2         | 1.200                 | 0.04       | 832                         | 1.201                 | -0.16      | 415                         | 1.201                 | -0.16            | 207                         |  |  |

| 2.4         | 2.404                 | 0.16       | 415                         | 2.403                 | -0.16      | 207                         | 2.403                 | -0.16            | 103                         |  |  |

| 9.6         | 9.615                 | 0.16       | 103                         | 9.615                 | -0.16      | 51                          | 9.615                 | -0.16            | 25                          |  |  |

| 19.2        | 19.231                | 0.16       | 51                          | 19.230                | -0.16      | 25                          | 19.230                | -0.16            | 12                          |  |  |

| 57.6        | 58.824                | 2.12       | 16                          | 55.555                | 3.55       | 8                           | _                     | _                | _                           |  |  |

| 115.2       | 111.111               | -3.55      | 8                           | _                     | _          | _                           | _                     | _                | _                           |  |  |

### 19.2 EUSART Asynchronous Mode

The Asynchronous mode of operation is selected by clearing the SYNC bit (TXSTA<4>). In this mode, the EUSART uses standard Non-Return-to-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8 bits. An on-chip dedicated 8-bit/16-bit Baud Rate Generator can be used to derive standard baud rate frequencies from the oscillator.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent but use the same data format and baud rate. The Baud Rate Generator produces a clock, either x16 or x64 of the bit shift rate depending on the BRGH and BRG16 bits (TXSTA<2> and BAUDCON<3>). Parity is not supported by the hardware but can be implemented in software and stored as the 9th data bit.

The TXCKP (BAUDCON<4>) and RXDTP (BAUDCON<5>) bits allow the TX and RX signals to be inverted (polarity reversed). Devices that buffer signals between TTL and RS-232 levels also invert the signal. Setting the TXCKP and RXDTP bits allows for the use of circuits that provide buffering without inverting the signal.

In Asynchronous mode, clock polarity is selected with the TXCKP bit (BAUDCON<4>). Setting TXCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as low. Data polarity is selected with the RXDTP bit (BAUDCON<5>). Setting RXDTP inverts data on RX, while clearing the bit has no affect on received data

When operating in Asynchronous mode, the EUSART module consists of the following important elements:

- · Baud Rate Generator

- · Sampling Circuit

- · Asynchronous Transmitter

- · Asynchronous Receiver

- · Auto-Wake-up on Break signal

- 12-bit Break Character Transmit

- · Auto-Baud Rate Detection

- · Pin State Polarity

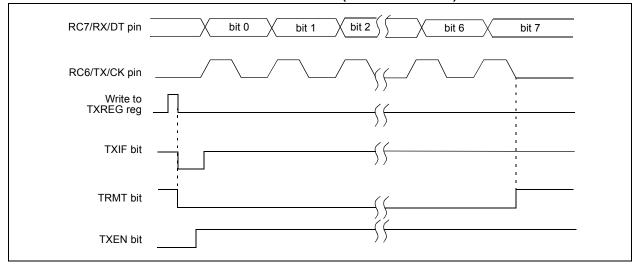

# 19.2.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 19-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREG register (if available).

Once the TXREG register transfers the data to the TSR register (occurs in one TcY), the TXREG register is empty and the TXIF flag bit (PIR1<4>) is set. This interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF will be set regardless of the state of TXIE; it cannot be cleared in software. TXIF is also not cleared immediately upon loading TXREG, but becomes valid in the second instruction cycle following the load instruction. Polling TXIF immediately following a load of TXREG will return invalid results.

While TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty.

The TXCKP bit (BAUDCON<4>) allows the TX signal to be inverted (polarity reversed). Devices that buffer signals from TTL to RS-232 levels also invert the signal (when TTL = 1, RS-232 = negative). Inverting the polarity of the TX pin data by setting the TXCKP bit allows for use of circuits that provide buffering without inverting the signal.

- **Note 1:** The TSR register is not mapped in data memory so it is not available to the user.

- **2:** Flag bit TXIF is set when enable bit TXEN is set.

To set up an Asynchronous Transmission:

- Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- If the signal from the TX pin is to be inverted, set the TXCKP bit.

- 4. If interrupts are desired, set enable bit, TXIE.

- If 9-bit transmission is desired, set transmit bit, TX9; can be used as address/data bit.

- Enable the transmission by setting bit, TXEN, which will also set bit, TXIF.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 8. Load data to the TXREG register (starts transmission).

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set

FIGURE 19-12: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

TABLE 19-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7                | Bit 6       | Bit 5       | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------|-------------|-------------|-------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL   | TMR0IE      | INT0IE      | RBIE  | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF        | RCIF        | TXIF        | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE        | RCIE        | TXIE        | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP        | RCIP        | TXIP        | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                         |

| RCSTA   | SPEN                 | RX9         | SREN        | CREN        | ADDEN | FERR   | OERR   | RX9D   | 57                         |

| TXREG   | EUSART T             | ransmit Reg | ister       |             |       |        |        |        | 57                         |

| TXSTA   | CSRC                 | TX9         | TXEN        | SYNC        | SENDB | BRGH   | TRMT   | TX9D   | 57                         |

| BAUDCON | ABDOVF               | RCIDL       | RXDTP       | TXCKP       | BRG16 | _      | WUE    | ABDEN  | 57                         |

| SPBRGH  | EUSART E             | Baud Rate G | enerator Re | gister High | Byte  | •      |        | •      | 57                         |

| SPBRG   | EUSART E             | Baud Rate G | enerator Re | gister Low  | Byte  |        |        |        | 57                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

Syntax:

| BNC              | Branch i                                  | f Not Ca                                            | rry  |      |  |

|------------------|-------------------------------------------|-----------------------------------------------------|------|------|--|

| Syntax:          | BNC n                                     |                                                     |      |      |  |

| Operands:        | -128 ≤ n ≤                                | $-128 \le n \le 127$                                |      |      |  |

| Operation:       | •                                         | If Carry bit is '0', $(PC) + 2 + 2n \rightarrow PC$ |      |      |  |

| Status Affected: | None                                      |                                                     |      |      |  |

| Encoding:        | 1110                                      | 0011                                                | nnnn | nnnn |  |

| Description:     | If the Carry bit is '0', then the program |                                                     |      |      |  |

The 2's complement number '2n' is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

two-cycle instruction.

Words: 1 Cycles: 1(2)

Q Cycle Activity:

If Jump:

| Q1        | Q2           | Q3        | Q4        |

|-----------|--------------|-----------|-----------|

| Decode    | Read literal | Process   | Write to  |

|           | ʻn'          | Data      | PC        |

| No        | No           | No        | No        |

| operation | operation    | operation | operation |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | ʻn'          | Data    | operation |

Example: HERE BNC Jump

Before Instruction

PC address (HERE)

After Instruction

If Carry PC

address (Jump)

If Carry PC

address (HERE + 2)

**BNN Branch if Not Negative** BNN n

$\text{-}128 \leq n \leq 127$ Operands: Operation: If Negative bit is '0'.  $(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

1110 Encoding: 0111 nnnn nnnn

If the Negative bit is '0', then the Description:

program will branch.

The 2's complement number '2n' is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

two-cycle instruction.

Words: 1

Cycles: 1(2)

Q Cycle Activity:

If Jump:

| Q1        | Q2           | Q3        | Q4        |

|-----------|--------------|-----------|-----------|

| Decode    | Read literal | Process   | Write to  |

|           | ʻn'          | Data      | PC        |

| No        | No           | No        | No        |

| operation | operation    | operation | operation |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | 'n'          | Data    | operation |

Example: HERE BNN Jump

Before Instruction

PC address (HERE)

After Instruction

If Negative

address (Jump)

If Negative

address (HERE + 2)

BRA Unconditional Branch

Syntax: BRA n

Operands:  $-1024 \le n \le 1023$ Operation:  $(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1101 Onnn nnnn nnnn

Description: Add the 2's complement number '2n' to

the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This

instruction is a two-cycle instruction.

Words: 1 Cycles: 2

Q Cycle Activity:

|   | Q1        | Q2           | Q3        | Q4        |

|---|-----------|--------------|-----------|-----------|

| ĺ | Decode    | Read literal | Process   | Write to  |

|   |           | ʻn'          | Data      | PC        |

| ĺ | No        | No           | No        | No        |

|   | operation | operation    | operation | operation |

Example: HERE BRA Jump

Before Instruction

PC = address (HERE)

After Instruction

PC = address (Jump)

| BSF              | Bit Set f                                             |      |      |      |

|------------------|-------------------------------------------------------|------|------|------|

| Syntax:          | BSF f, b                                              | {,a} |      |      |

| Operands:        | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$ |      |      |      |

| Operation:       | $1 \rightarrow \text{f}$                              |      |      |      |

| Status Affected: | None                                                  |      |      |      |

| Encoding:        | 1000                                                  | bbba | ffff | ffff |

|                  |                                                       |      |      |      |

Description: Bit 'b' in register 'f' is set.

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank (default).

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 25.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.

Words: 1

Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: BSF FLAG\_REG, 7, 1

Before Instruction

FLAG\_REG = 0Ah

After Instruction

FLAG\_REG = 8Ah

# 27.3 DC Characteristics: PIC18F2221/2321/4221/4321 (Industrial) PIC18LF2221/2321/4221/4321 (Industrial) (Continued)

| DC CHARACTERISTICS |        | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for extended |           |     |       |                                                                                                  |

|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-------|--------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                     | Min       | Max | Units | Conditions                                                                                       |

|                    | lpu    | Weak Pull-up Current                                                                                                                                                                                                               |           |     |       |                                                                                                  |

| D070               | IPURB  | PORTB Weak Pull-up Current                                                                                                                                                                                                         | 50        | 400 | μΑ    | VDD = 5V, VPIN = VSS                                                                             |

|                    | Vol    | Output Low Voltage                                                                                                                                                                                                                 |           |     |       |                                                                                                  |

| D080               |        | I/O Ports                                                                                                                                                                                                                          | _         | 0.6 | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                                                      |

| D083               |        | OSC2/CLKO<br>(RC, RCIO, EC, ECIO modes)                                                                                                                                                                                            | _         | 0.6 | V     | IOL = $1.6 \text{ mA}$ , VDD = $4.5 \text{V}$ , $-40 ^{\circ}\text{C}$ to $+85 ^{\circ}\text{C}$ |

|                    | Vон    | Output High Voltage <sup>(3)</sup>                                                                                                                                                                                                 |           |     |       |                                                                                                  |

| D090               |        | I/O Ports                                                                                                                                                                                                                          | VDD - 0.7 | _   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                                                     |

| D092               |        | OSC2/CLKO<br>(RC, RCIO, EC, ECIO modes)                                                                                                                                                                                            | VDD - 0.7 | _   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°C to +85°C                                                     |

|                    |        | Capacitive Loading Specs on Output Pins                                                                                                                                                                                            |           |     |       |                                                                                                  |

| D100               | COSC2  | OSC2 Pin                                                                                                                                                                                                                           | _         | 15  | pF    | In XT, HS and LP modes when external clock is used to drive OSC1                                 |

| D101               | Cio    | All I/O Pins and OSC2<br>(in RC mode)                                                                                                                                                                                              | _         | 50  | pF    | Maximum that allows the AC Timing Specifications to be met                                       |

| D102               | Св     | SCL, SDA                                                                                                                                                                                                                           | _         | 400 | pF    | Maximum bus capacitance permitted by I <sup>2</sup> C™<br>Specification                          |

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC<sup>®</sup> device be driven with an external clock while in RC mode.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**<sup>3:</sup>** Negative current is defined as current sourced by the pin.

# APPENDIX E: MIGRATION FROM MID-RANGE TO ENHANCED DEVICES

A detailed discussion of the differences between the mid-range MCU devices (i.e., PIC16CXXX) and the Enhanced devices (i.e., PIC18FXXX) is provided in AN716, "Migrating Designs from PIC16C74A/74B to PIC18C442". The changes discussed, while device specific, are generally applicable to all mid-range to Enhanced device migrations.

This Application Note is available as Literature Number DS00716.

APPENDIX F: MIGRATION FROM HIGH-END TO ENHANCED DEVICES

A detailed discussion of the migration pathway and differences between the high-end MCU devices (i.e., PIC17CXXX) and the Enhanced devices (i.e., PIC18FXXX) is provided in AN726, "PIC17CXXX to PIC18CXXX Migration".

This Application Note is available as Literature Number DS00726.

| DAW                                                                | 298    | Synchronous Master Mode                         | 228 |

|--------------------------------------------------------------------|--------|-------------------------------------------------|-----|

| DC Characteristics                                                 | 347    | Associated Registers, Receive                   | 230 |

| Power-Down and Supply Current                                      | 337    | Associated Registers, Transmit                  |     |

| Supply Voltage                                                     | 336    | Reception                                       |     |

| DCFSNZ                                                             | 299    | Transmission                                    | 228 |

| DECF                                                               | 298    | Synchronous Slave Mode                          | 231 |

| DECFSZ                                                             | 299    | Associated Registers, Receive                   | 232 |

| Development Support                                                | 329    | Associated Registers, Transmit                  | 231 |

| Device Differences                                                 | 386    | Reception                                       | 232 |

| Device Overview                                                    | 9      | Transmission                                    | 231 |

| Details on Individual Family Members                               |        | Extended Instruction Set                        |     |

| Features (table)                                                   | 11     | ADDFSR                                          | 322 |

| New Core Features                                                  | 9      | ADDULNK                                         |     |

| Other Special Features                                             |        | and Using MPLAB Tools                           |     |

| Device Reset Timers                                                |        | CALLW                                           |     |

| Oscillator Start-up Timer (OST)                                    |        | Considerations for Use                          |     |

| PLL Lock Time-out                                                  |        | MOVSF                                           | 323 |