Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

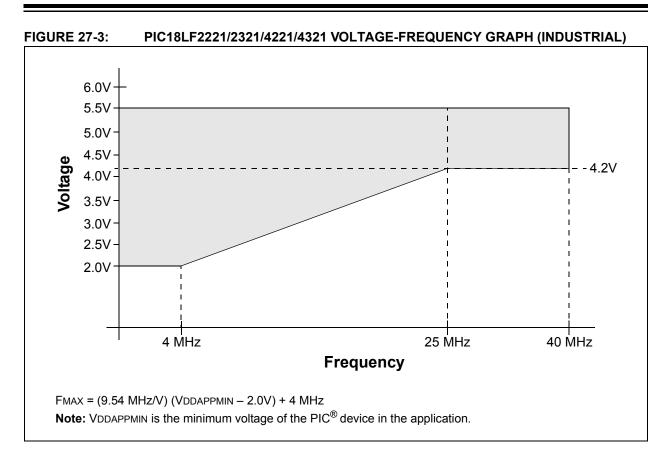

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2321t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

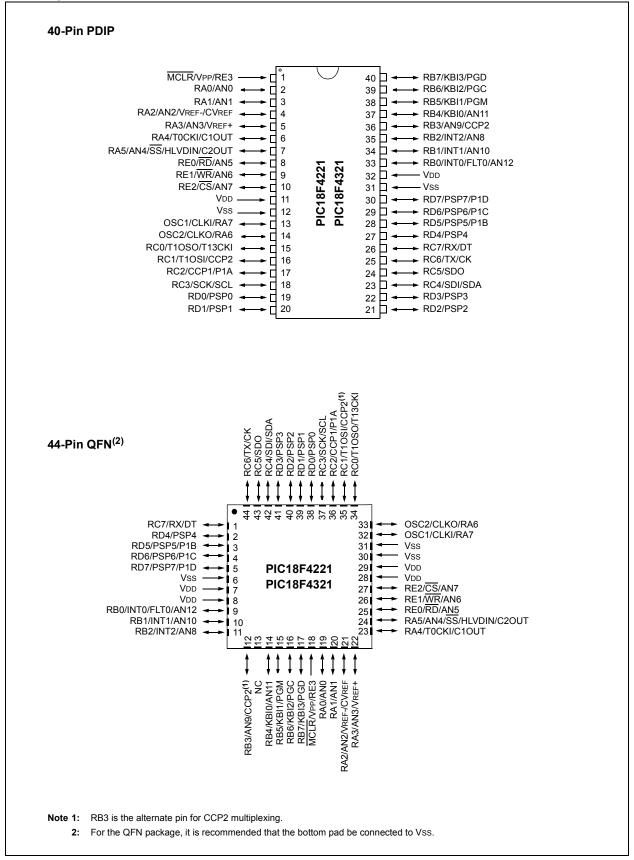

#### **Pin Diagrams (Continued)**

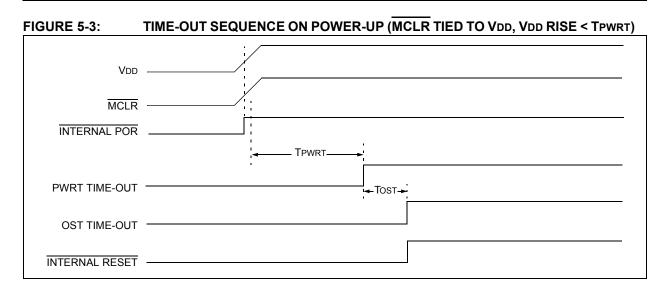

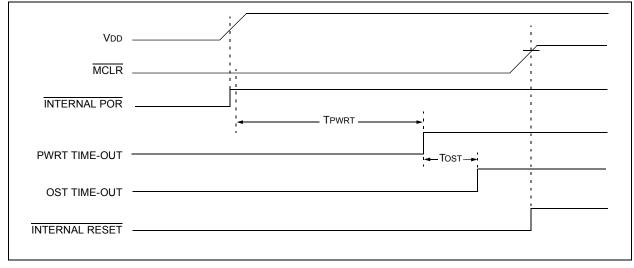

# FIGURE 5-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

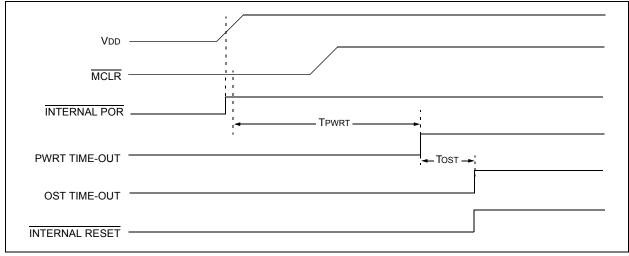

# FIGURE 5-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

### EXAMPLE 7-3: WRITING TO FLASH PROGRAM MEMORY (CONTINUED)

| PROGRAM_MEMORY |              |                             |

|----------------|--------------|-----------------------------|

| BCF            | INTCON, GIE  | ; disable interrupts        |

| MOVLW          | 55h          | ; required sequence         |

| MOVWF          | EECON2       | ; write 55h                 |

| MOVLW          | 0AAh         |                             |

| MOVWF          | EECON2       | ; write AAh                 |

| BSF            | EECON1, WR   | ; start program (CPU stall) |

| NOP            |              |                             |

| BSF            | INTCON, GIE  | ; re-enable interrupts      |

| DECFSZ         | COUNTER_HI   | ; loop until done           |

| GOTO           | PROGRAM_LOOP |                             |

| BCF            | EECON1, WREN | ; disable write to memory   |

|                |              |                             |

### 7.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

# 7.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

### 7.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See Section 24.0 "Special Features of the CPU" for more detail.

## 7.6 Flash Program Operation During Code Protection

See Section 24.5 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7                                                 | Bit 6         | Bit 5       | Bit 4          | Bit 3         | Bit 2        | Bit 1         | Bit 0      | Reset<br>Values on<br>page |

|---------|-------------------------------------------------------|---------------|-------------|----------------|---------------|--------------|---------------|------------|----------------------------|

| TBLPTRU | _                                                     |               | bit 21      | Program Me     | emory Table F | Pointer Uppe | r Byte (TBLP  | TR<20:16>) | 55                         |

| TBPLTRH | Program Memory Table Pointer High Byte (TBLPTR<15:8>) |               |             |                |               |              |               | 55         |                            |

| TBLPTRL | Program Memory Table Pointer Low Byte (TBLPTR<7:0>)   |               |             |                |               |              | 55            |            |                            |

| TABLAT  | Program Me                                            | emory Table   | Latch       |                |               |              |               |            | 55                         |

| INTCON  | GIE/GIEH                                              | PEIE/GIEL     | TMR0IE      | INT0IE         | RBIE          | TMR0IF       | <b>INT0IF</b> | RBIF       | 55                         |

| EECON2  | EEPROM C                                              | Control Regis | ster 2 (not | t a physical r | egister)      |              |               |            | 57                         |

| EECON1  | EEPGD                                                 | CFGS          | _           | FREE           | WRERR         | WREN         | WR            | RD         | 57                         |

| IPR2    | OSCFIP                                                | CMIP          | _           | EEIP           | BCLIP         | HLVDIP       | TMR3IP        | CCP2IP     | 58                         |

| PIR2    | OSCFIF                                                | CMIF          |             | EEIF           | BCLIF         | HLVDIF       | TMR3IF        | CCP2IF     | 58                         |

| PIE2    | OSCFIE                                                | CMIE          |             | EEIE           | BCLIE         | HLVDIE       | TMR3IE        | CCP2IE     | 58                         |

TABLE 7-2:

REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

# 15.2 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 15-2). When the RD16 control bit (T3CON<7>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

# 15.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in Section 13.0 "Timer1 Module".

# 15.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE (PIE2<1>).

# 15.5 Resetting Timer3 Using the CCP Special Event Trigger

If either of the CCP modules is configured to use Timer3 and to generate a Special Event Trigger in Compare mode (CCP1M<3:0> or CCP2M<3:0> = 1011), this signal will reset Timer3. It will also start an A/D conversion if the A/D module is enabled (see **Section 16.3.4** "**Special Event Trigger**" for more information).

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPR2H:CCPR2L register pair effectively becomes a period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from a CCP module, the write will take precedence.

Note: The Special Event Triggers from the CCP2 module will not set the TMR3IF interrupt flag bit (PIR2<1>).

| Name   | Bit 7                     | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|---------------------------|--------------|---------|---------|---------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH                  | PEIE/GIEL    | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR2   | OSCFIF                    | CMIF         | _       | EEIF    | BCLIF   | HLVDIF | TMR3IF | CCP2IF | 58                         |

| PIE2   | OSCFIE                    | CMIE         | _       | EEIE    | BCLIE   | HLVDIE | TMR3IE | CCP2IE | 58                         |

| IPR2   | OSCFIP                    | CMIP         | _       | EEIP    | BCLIP   | HLVDIP | TMR3IP | CCP2IP | 58                         |

| TMR3L  | Timer3 Reg                | gister Low B | yte     |         |         |        |        |        | 57                         |

| TMR3H  | Timer3 Register High Byte |              |         |         |         |        |        |        | 57                         |

| T1CON  | RD16                      | T1RUN        | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 56                         |

| T3CON  | RD16                      | T3CCP2       | T3CKPS1 | T3CKPS0 | T3CCP1  | T3SYNC | TMR3CS | TMR3ON | 57                         |

TABLE 15-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

# 18.3.8 OPERATION IN POWER-MANAGED MODES

In SPI Master mode, module clocks may be operating at a different speed than when in full power mode. In the case of Sleep mode, all clocks are halted.

In Idle modes, a clock is provided to the peripherals. That clock should be from the primary clock source, the secondary clock (Timer1 oscillator at 32.768 kHz) or the INTOSC source. See **Section 3.7 "Clock Sources and Oscillator Switching**" for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

If MSSP interrupts are enabled, they can wake the controller from Sleep mode, or one of the Idle modes, when the master completes sending data. If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

If the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the devices wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any power-managed mode and data to be shifted into the SPI Transmit/ Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

# 18.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

### 18.3.10 BUS MODE COMPATIBILITY

Table 18-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| Standard SPI Mode | Control I | Bits State |

|-------------------|-----------|------------|

| Terminology       | СКР       | CKE        |

| 0, 0              | 0         | 1          |

| 0, 1              | 0         | 0          |

| 1, 0              | 1         | 1          |

| 1, 1              | 1         | 0          |

### TABLE 18-1: SPI BUS MODES

There is also an SMP bit which controls when the data is sampled.

| Name    | Bit 7                 | Bit 6                 | Bit 5                         | Bit 4                           | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|-----------------------|-----------------------|-------------------------------|---------------------------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH              | PEIE/GIEL             | TMR0IE                        | INT0IE                          | RBIE  | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1    | PSPIF <sup>(1)</sup>  | ADIF                  | RCIF                          | TXIF                            | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1    | PSPIE <sup>(1)</sup>  | ADIE                  | RCIE                          | TXIE                            | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1    | PSPIP <sup>(1)</sup>  | ADIP                  | RCIP                          | TXIP                            | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                         |

| TRISA   | TRISA7 <sup>(2)</sup> | TRISA6 <sup>(2)</sup> | PORTA Da                      | Data Direction Control Register |       |        |        |        |                            |

| TRISC   | PORTC Da              | ta Direction          | Control Reg                   | gister                          |       |        |        |        | 58                         |

| SSPBUF  | MSSP Rec              | eive Buffer/7         | eive Buffer/Transmit Register |                                 |       |        |        |        |                            |

| SSPCON1 | WCOL                  | SSPOV                 | SSPEN                         | CKP                             | SSPM3 | SSPM2  | SSPM1  | SSPM0  | 56                         |

| SSPSTAT | SMP                   | CKE                   | D/A                           | Р                               | S     | R/W    | UA     | BF     | 56                         |

# TABLE 18-2: REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: Shaded cells are not used by the MSSP in SPI mode.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

**2:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

### 18.4.3.3 Reception

When the R/W bit of the address byte is clear and an address match occurs, the R/W bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON1<6>) is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit, SSPIF (PIR1<3>), must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON2<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit, CKP (SSPCON1<4>). See **Section 18.4.4** "**Clock Stretching**" for more detail.

### 18.4.3.4 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low regardless of SEN (see Section 18.4.4 "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then pin RC3/ SCK/SCL should be enabled by setting bit, CKP (SSPCON1<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 18-10).

The  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not  $\overline{ACK}$ ), then the data transfer is complete. In this case, when the  $\overline{ACK}$  is latched by the slave, the slave logic is reset and the slave monitors for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the next transmit data must be loaded into the SSPBUF register. Again, pin RC3/SCK/SCL must be enabled by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

# 19.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of the two serial I/O modules. (Generically, the USART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a halfduplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN/J2602 bus) systems.

The EUSART can be configured in the following modes:

- Asynchronous (full duplex) with:

- Auto-wake-up on Break signal

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half duplex) with selectable clock polarity

- Synchronous Slave (half duplex) with selectable clock polarity

The pins of the Enhanced USART are multiplexed with PORTC. In order to configure RC6/TX/CK and RC7/RX/DT as an EUSART:

- bit SPEN (RCSTA<7>) must be set (= 1)

- bit TRISC<7> must be set (= 1)

- bit TRISC<6> must be set (= 1)

| Note: | The EUSART control will automatically               |

|-------|-----------------------------------------------------|

|       | reconfigure the pin from input to output as needed. |

The operation of the Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These are detailed on the following pages in Register 19-1, Register 19-2 and Register 19-3, respectively.

### 19.2.4 AUTO-WAKE-UP ON SYNC BREAK CHARACTER

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper byte reception cannot be performed. The auto-wake-up feature allows the controller to wake-up due to activity on the RX/DT line while the EUSART is operating in Asynchronous mode.

The auto-wake-up feature is enabled by setting the WUE bit (BAUDCON<1>). Once set, the typical receive sequence on RX/DT is disabled and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a Wake-up Signal character for the LIN/J2602 protocol.)

Following a wake-up event, the module generates an RCIF interrupt. The interrupt is generated synchronously to the Q clocks in normal operating modes (Figure 19-8) and asynchronously, if the device is in Sleep mode (Figure 19-9). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared once a low-tohigh transition is observed on the RX line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

#### 19.2.4.1 Special Considerations Using Auto-Wake-up

Since auto-wake-up functions by sensing rising edge transitions on RX/DT, information with any state changes before the Stop bit may signal a false end-of-character

and cause data or framing errors. To work properly, therefore, the initial character in the transmission must be all '0's. This can be 00h (8 bytes) for standard RS-232 devices or 000h (12 bits) for the LIN/J2602 bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., XT or HS mode). The Sync Break (or Wake-up Signal) character must be of sufficient length and be followed by a sufficient interval to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

# 19.2.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared after this when a rising edge is seen on RX/DT. The interrupt condition is then cleared by reading the RCREG register. Ordinarily, the data in RCREG will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RCIF flag is set should not be used as an indicator of the integrity of the data in RCREG. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

|                         | (C (C2)C3)C3   | . C 및 C 2 C 2 C 2 C 2                 | lodosforios                           | (CHO2)CHO.                            | 404030303  | 사이막이언이란이  | elogosjo: | 10401010                              | 3,034,03,00 | dodados(ario                           | 73 <u>1</u> 5 |

|-------------------------|----------------|---------------------------------------|---------------------------------------|---------------------------------------|------------|-----------|-----------|---------------------------------------|-------------|----------------------------------------|---------------|

| O9K15                   | mananan.       | aununun.                              | RENENCI                               | ndrunun                               | min ana    | 370707031 | UNUNUNI.  | haan                                  | inan.       | nonumon                                | S.C           |

|                         | ्रे अंध कर केई | 2003 (                                | :                                     | 5                                     | 2 .<br>2 . |           | 4<br>4    | k i<br>K i                            | di di jerre | Antégites est                          | ž.            |

| 9628 B8 <sup>33</sup> - | (              | ÷                                     | 7                                     | · · · · · · · · · · · · · · · · · · · | · · · · ·  |           |           | · · · · · · · · · · · · · · · · · · · | Sama        |                                        | ,,,,,         |

|                         |                |                                       | 5<br>2                                | * ;<br>, .                            |            |           | 4         |                                       |             | ;                                      |               |

| SACT Core -             | ÷              | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | ::                                    |            |           |           |                                       |             | ······································ |               |

|                         |                |                                       |                                       | < 1<br>                               | 1. N. N.   | . :       |           | 4 .                                   |             | · · · · ·                              |               |

| 84087                   | r<br>          |                                       |                                       | ç                                     |            | d.        |           |                                       | · Altraces  | a familia                              |               |

|                         |                |                                       |                                       | e                                     | 4          | 1         | Matter 33 | e toMyster read                       | e a Maca    |                                        |               |

|                         |                |                                       | ÷                                     | ·                                     | 18 C       |           |           | *                                     | · ·         | 1                                      |               |

# FIGURE 19-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING NORMAL OPERATION

# FIGURE 19-9: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

### 19.4.2 EUSART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep, or any Idle mode and bit SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting the CREN bit prior to entering Sleep or any Idle mode, then a word may be received while in this low-power mode. Once the word is received, the RSR register will transfer the data to the RCREG register; if the RCIE enable bit is set, the interrupt generated will wake the chip from the lowpower mode. If the global interrupt is enabled, the program will branch to the interrupt vector. To set up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If the signal from the CK pin is to be inverted, set the TXCKP bit.

- 4. If 9-bit reception is desired, set bit, RX9.

- 5. To enable reception, set enable bit, CREN.

- Flag bit, RCIF, will be set when reception is complete. An interrupt will be generated if enable bit, RCIE, was set.

- 7. Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing bit, CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name    | Bit 7                                            | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|--------------------------------------------------|--------------|--------|--------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                         | PEIE/GIEL    | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1    | PSPIF <sup>(1)</sup>                             | ADIF         | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1    | PSPIE <sup>(1)</sup>                             | ADIE         | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1    | PSPIP <sup>(1)</sup>                             | ADIP         | RCIP   | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                         |

| RCSTA   | SPEN                                             | RX9          | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 57                         |

| RCREG   | EUSART F                                         | Receive Regi | ster   |        |       |        |        |        | 57                         |

| TXSTA   | CSRC                                             | TX9          | TXEN   | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 57                         |

| BAUDCON | ABDOVF                                           | RCIDL        | RXDTP  | TXCKP  | BRG16 | —      | WUE    | ABDEN  | 57                         |

| SPBRGH  | GH EUSART Baud Rate Generator Register High Byte |              |        |        |       |        |        |        | 57                         |

| SPBRG   | G EUSART Baud Rate Generator Register Low Byte   |              |        |        |       |        |        |        | 57                         |

### TABLE 19-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

NOTES:

| REGISTER 24-2: | CONFIG             | 2L: CONF                   | IGURATI                   | ON REGIS                  | TER 2 LOV            | V (BYTE AD            | DRESS 300       | 002h)                 |

|----------------|--------------------|----------------------------|---------------------------|---------------------------|----------------------|-----------------------|-----------------|-----------------------|

|                | U-0                | U-0                        | U-0                       | R/P-1                     | R/P-1                | R/P-1                 | R/P-1           | R/P-1                 |

|                | _                  | _                          | _                         | BORV1 <sup>(1)</sup>      | BORV0 <sup>(1)</sup> | BOREN1 <sup>(2)</sup> | BOREN0(2)       | PWRTEN <sup>(2)</sup> |

|                | bit 7              |                            |                           |                           |                      |                       |                 | bit 0                 |

| bit 7-5        | Unimplem           | nented: Re                 | <b>ad as</b> '0'          |                           |                      |                       |                 |                       |

| bit 4-3        | BORV<1:0           | 0>: Brown-                 | out Reset                 | Voltage bits <sup>(</sup> | 1)                   |                       |                 |                       |

|                | 11 <b>= Minin</b>  | num setting                | J                         |                           |                      |                       |                 |                       |

|                | •                  |                            |                           |                           |                      |                       |                 |                       |

|                | •                  |                            |                           |                           |                      |                       |                 |                       |

|                | 00 <b>= Maxi</b> i | mum settin                 | g                         |                           |                      |                       |                 |                       |

| bit 2-1        | BOREN<1            | I: <b>0&gt;:</b> Browr     | n-out Rese                | t Enable bits             | ;(2)                 |                       |                 |                       |

|                |                    |                            |                           |                           | •                    | REN is disable        | ,               |                       |

|                |                    |                            |                           | in hardware               | only and dis         | sabled in Slee        | ep mode         |                       |

|                |                    | DREN is dis<br>/n-out Rese |                           | and controlle             | ed by softwa         | are (SBOREN           | is enabled)     |                       |

|                |                    |                            |                           | in hardware               | •                    | •                     | ,               |                       |

| bit 0          | PWRTEN:            | Power-up                   | Timer Ena                 | able bit <sup>(2)</sup>   |                      |                       |                 |                       |

|                | 1 = PWRT           |                            |                           |                           |                      |                       |                 |                       |

|                | 0 <b>= PWRT</b>    |                            |                           |                           |                      |                       |                 |                       |

|                | Note 1:            | See Sect                   | ion 27.1 '                | 'DC Charac                | teristics" fo        | or the specific       | ations.         |                       |

|                | 2:                 |                            | er-up Time<br>endently co |                           | ed from Brov         | vn-out Reset,         | allowing thes   | e features to         |

|                | Legend:            |                            |                           |                           |                      |                       |                 |                       |

|                | R = Reada          | able bit                   | P = Pr                    | ogrammable                | ebit U=l             | Jnimplemente          | ed bit, read as | s 'O'                 |

| <b>.</b>                               | •                                   |

|----------------------------------------|-------------------------------------|

| -n = Value when device is unprogrammed | u = Unchanged from programmed state |

#### REGISTER 24-10: CONFIG7L: CONFIGURATION REGISTER 7 LOW (BYTE ADDRESS 30000Ch) U-0 U-0 U-0 U-0 U-0 U-0 R/C-1 R/C-1 EBTR1 EBTR0 bit 7 bit 0 bit 7-2 Unimplemented: Read as '0' bit 1 EBTR1: Table Read Protection bit 1 = Block 1 not protected from table reads executed in other blocks<sup>(1)</sup> 0 = Block 1 protected from table reads executed in other blocks<sup>(1)</sup> EBTR0: Table Read Protection bit bit 0 1 = Block 0 not protected from table reads executed in other blocks<sup>(1)</sup> 0 = Block 0 protected from table reads executed in other blocks<sup>(1)</sup> Note 1: See Figure 24-5 for variable block boundaries.

| Legend:                |                   |                                     |

|------------------------|-------------------|-------------------------------------|

| R = Readable bit       | C = Clearable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device | is unprogrammed   | u = Unchanged from programmed state |

#### REGISTER 24-11: CONFIG7H: CONFIGURATION REGISTER 7 HIGH (BYTE ADDRESS 30000Dh)

|   | U-0   | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---|-------|-------|-----|-----|-----|-----|-----|-------|

|   | —     | EBTRB | —   | —   | —   | —   | _   | —     |

| ł | oit 7 |       |     |     |     |     |     | bit 0 |

- bit 7 Unimplemented: Read as '0'

- bit 6 **EBTRB:** Boot Block Table Read Protection bit

- 1 = Boot block not protected from table reads executed in other blocks<sup>(1)</sup>

- 0 = Boot block protected from table reads executed in other blocks<sup>(1)</sup>

- bit 5-0 Unimplemented: Read as '0'

**Note 1:** See Figure 24-5 for variable block boundaries.

| Legend:                |                    |                                     |

|------------------------|--------------------|-------------------------------------|

| R = Readable bit       | C = Clearable bit  | U = Unimplemented bit, read as '0'  |

| -n = Value when device | ce is unprogrammed | u = Unchanged from programmed state |

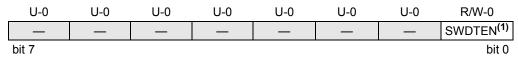

### REGISTER 24-14: WDTCON: WATCHDOG TIMER CONTROL REGISTER

bit 7-1 Unimplemented: Read as '0'

bit 0 **SWDTEN:** Software Controlled Watchdog Timer Enable bit<sup>(1)</sup>

1 = Watchdog Timer is on

0 = Watchdog Timer is off

**Note 1:** This bit has no effect if the Configuration bit, WDTEN, is enabled.

| Legend:                            |                   |  |

|------------------------------------|-------------------|--|

| R = Readable bit                   | W = Writable bit  |  |

| U = Unimplemented bit, read as '0' | -n = Value at POR |  |

#### TABLE 24-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name   | Bit 7 | Bit 6                 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Reset<br>Values<br>on page |

|--------|-------|-----------------------|-------|-------|-------|-------|-------|--------|----------------------------|

| RCON   | IPEN  | SBOREN <sup>(1)</sup> |       | RI    | TO    | PD    | POR   | BOR    | 56                         |

| WDTCON | _     | _                     | _     |       | _     | _     | _     | SWDTEN | 56                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

Note 1: The SBOREN bit is only available when the BOREN<1:0> Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

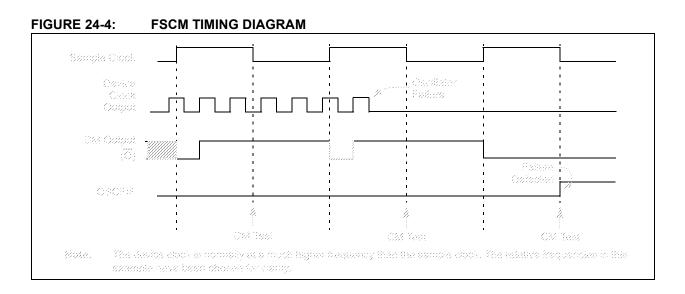

## 24.4.3 FSCM INTERRUPTS IN POWER-MANAGED MODES

By entering a power-managed mode, the clock multiplexer selects the clock source selected by the OSCCON register. Fail-Safe Monitoring of the powermanaged clock source resumes in the power-managed mode.

If an oscillator failure occurs during power-managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTOSC multiplexer. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, subsequent interrupts while in Idle mode will cause the CPU to begin executing instructions while being clocked by the INTOSC source.

# 24.4.4 POR OR WAKE FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited Power-on Reset (POR) or low-power Sleep mode. When the primary device clock is EC, RC or INTRC modes, monitoring can begin immediately following these events.

For oscillator modes involving a crystal or resonator (HS, HSPLL, LP or XT), the situation is somewhat different. Since the oscillator may require a start-up time considerably longer than the FCSM sample clock time, a false clock failure may be detected. To prevent this, the internal oscillator block is automatically configured as the device clock and functions until the primary clock is stable (the OST and PLL timers have timed out). This is identical to Two-Speed Start-up mode. Once the primary clock is stable, the INTRC returns to its role as the FSCM source.

| Note: | The same logic that prevents false oscilla-<br>tor failure interrupts on POR, or wake from<br>Sleep, will also prevent the detection of |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | the oscillator's failure to start at all follow-<br>ing these events. This can be avoided by                                            |  |  |  |  |  |

|       | monitoring the OSTS bit and using a timing routine to determine if the oscillator                                                       |  |  |  |  |  |

|       | is taking too long to start. Even so, no oscillator failure interrupt will be flagged.                                                  |  |  |  |  |  |

As noted in Section 24.3.1 "Special Considerations for Using Two-Speed Start-up", it is also possible to select another clock configuration and enter an alternate power-managed mode while waiting for the primary clock to become stable. When the new powermanaged mode is selected, the primary clock is disabled.

| BRA   | BRA Unconditional Branch               |                                                                       |                     |                              |                                 |                      |                          |

|-------|----------------------------------------|-----------------------------------------------------------------------|---------------------|------------------------------|---------------------------------|----------------------|--------------------------|

| Synta | ax:                                    | BRA n                                                                 |                     |                              |                                 |                      |                          |

| Oper  | ands:                                  | -1024 ≤ n ≤                                                           | 10                  | 23                           |                                 |                      |                          |

| Oper  | ation:                                 | (PC) + 2 +                                                            | 2n                  | $\rightarrow$ PC             |                                 |                      |                          |

| Statu | s Affected:                            | None                                                                  |                     |                              |                                 |                      |                          |

| Enco  | ding:                                  | 1101                                                                  | C                   | nnn                          | nnnr                            | L                    | nnnn                     |

| Desc  | ription:                               | Add the 2's<br>the PC. Sir<br>incremente<br>the new ad<br>instruction | nce<br>ed to<br>dre | the PC<br>o fetch<br>ss will | will hav<br>the next<br>be PC + | /e<br>t ins<br>· 2 · | struction,<br>+ 2n. This |

| Word  | ls:                                    | 1                                                                     |                     |                              |                                 |                      |                          |

| Cycle | es:                                    | 2                                                                     |                     |                              |                                 |                      |                          |

| QC    | ycle Activity:                         |                                                                       |                     |                              |                                 |                      |                          |

|       | Q1                                     | Q2                                                                    |                     | C                            | 23                              |                      | Q4                       |

|       | Decode                                 | Read liter<br>'n'                                                     | al                  |                              | cess<br>ata                     |                      | Write to<br>PC           |

|       | No<br>operation                        | No<br>operatio                                                        | n                   |                              | lo<br>ation                     | 0                    | No<br>peration           |

| Exam  | <u>nple:</u>                           | HERE                                                                  |                     | BRA                          | Jump                            |                      |                          |

|       | Before Instru<br>PC<br>After Instructi | =                                                                     | ad                  | dress                        | (HERE)                          |                      |                          |

|       | PC                                     | =                                                                     | ad                  | dress                        | (Jump)                          |                      |                          |

| BSF                                               | Bit Set f                                                                                                                                                                            |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                           |                                                                                                                                                                                      | BSF f, b {,a}                                                                                                                          |                                                                                                 |                                                                                      |  |  |  |  |

| Operands:                                         | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0, 1]$                                                                                                                               | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \end{array}$                                                                    |                                                                                                 |                                                                                      |  |  |  |  |

| Operation:                                        | $1 \rightarrow \text{f}$                                                                                                                                                             |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

| Status Affected:                                  | None                                                                                                                                                                                 |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

| Encoding:                                         | 1000                                                                                                                                                                                 | bbba                                                                                                                                   | ffff                                                                                            | ffff                                                                                 |  |  |  |  |

| Description:                                      | Bit 'b' in reg<br>If 'a' is '0', ti<br>If 'a' is '1', ti<br>GPR bank of<br>If 'a' is '0' a<br>set is enabl<br>in Indexed I<br>mode when<br>Section 25<br>Bit-Oriente<br>Literal Offs | he Access<br>he BSR is<br>(default).<br>nd the ext<br>ed, this in<br>Literal Off<br>ever $f \leq 9$<br><b>.2.3 "Byt</b><br>of Instruct | s Bank i<br>s used to<br>tended i<br>sstructio<br>(set Add<br>(5 (5Fh))<br>e-Orien<br>ctions in | o select the<br>nstruction<br>n operates<br>ressing<br>. See<br>ted and<br>n Indexed |  |  |  |  |

| Words:                                            | 1                                                                                                                                                                                    |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

| Cycles:                                           | 1                                                                                                                                                                                    |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

| Q Cycle Activity:                                 |                                                                                                                                                                                      |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

| Q1                                                | Q2                                                                                                                                                                                   | Q3                                                                                                                                     |                                                                                                 | Q4                                                                                   |  |  |  |  |

| Decode                                            | Read register 'f'                                                                                                                                                                    | Proces<br>Data                                                                                                                         |                                                                                                 | Write<br>egister 'f'                                                                 |  |  |  |  |

| Example: BSF FLAG_REG, 7, 1<br>Before Instruction |                                                                                                                                                                                      |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

| After Instruction                                 | FLAG_REG = 0Ah<br>After Instruction<br>FLAG_REG = 8Ah                                                                                                                                |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

| NEGF              | Negate f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:           | NEGF f {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Operands:         | 0 ≤ f ≤ 255<br>a ∈ [0, 1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Operation:        | $(\overline{f}) + 1 \rightarrow f$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Status Affected:  | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Encoding:         | 0110 110a ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Description:      | Location 'f' is negated using two's<br>complement. The result is placed in the<br>data memory location 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |  |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| NOF               | )           | No Opera   | No Operation        |           |  |          |  |  |

|-------------------|-------------|------------|---------------------|-----------|--|----------|--|--|

| Synta             | ax:         | NOP        |                     |           |  |          |  |  |

| Oper              | ands:       | None       |                     |           |  |          |  |  |

| Oper              | ation:      | No operati | on                  |           |  |          |  |  |

| Statu             | s Affected: | None       |                     |           |  |          |  |  |

| Encoding:         |             | 0000       | 0000                | 0000      |  | 0000     |  |  |

|                   |             | 1111       | XXXX                | XXXX XXXX |  | XXXX     |  |  |

| Desc              | ription:    | No operati | No operation.       |           |  |          |  |  |

| Word              | ls:         | 1          | 1                   |           |  |          |  |  |

| Cycle             | es:         | 1          | 1                   |           |  |          |  |  |

| Q Cycle Activity: |             |            |                     |           |  |          |  |  |

|                   | Q1          | Q2         | Q                   | 3         |  | Q4       |  |  |

|                   | Decode      | No         | No                  | )         |  | No       |  |  |

|                   |             | operation  | operation operation |           |  | peration |  |  |

Example:

None.

| Q1     | Q2           | Q3      | Q4           |  |

|--------|--------------|---------|--------------|--|

| Decode | Read         | Process | Write        |  |

|        | register 'f' | Data    | register 'f' |  |

Example: NEGF REG, 1

> Before Instruction REG = 0011 1010 [3Ah] After Instruction REG = 1100 0110 [C6h]

© 2009 Microchip Technology Inc.

| RCA   | LL             | Relative C                                                    | Call                                 |                | RES        | SET                         | Reset      |                                                                     |         |          |

|-------|----------------|---------------------------------------------------------------|--------------------------------------|----------------|------------|-----------------------------|------------|---------------------------------------------------------------------|---------|----------|

| Synta | ax:            | RCALL n                                                       |                                      | Synt           | ax:        | RESET                       | RESET      |                                                                     |         |          |

| Oper  | ands:          | -1024 ≤ n ≤                                                   | 1023                                 |                | Oper       | rands:                      | None       |                                                                     |         |          |

| Oper  | ation:         | $(PC) + 2 \rightarrow TOS,$<br>(PC) + 2 + 2n $\rightarrow$ PC |                                      | Oper           | Operation: |                             | egisters a | nd flags t<br>Reset                                                 | hat are |          |

| Statu | s Affected:    | None                                                          |                                      |                | Statu      | is Affected:                | All        |                                                                     |         |          |

| Enco  | ding:          | 1101                                                          | 1nnn nni                             | nn nnnn        | Enco       | oding:                      | 0000       | 0000                                                                | 1111    | 1111     |

| Desc  | ription:       |                                                               | call with a jurr                     |                | Desc       | cription:                   |            | This instruction provides a way to execute a MCLR Reset in software |         |          |

|       |                |                                                               | C + 2) is push                       |                | Word       | ds:                         | 1          |                                                                     |         |          |

|       |                |                                                               | i, add the 2's c<br>' to the PC. Sir | complement     | Cycle      | es:                         | 1          |                                                                     |         |          |

|       |                | have incren                                                   | nented to fetch                      | n the next     | QC         | ycle Activity:              |            |                                                                     |         |          |

|       |                | ,                                                             | the new addre                        |                |            | Q1                          | Q2         | Q3                                                                  | 5       | Q4       |

|       |                | two-cycle in                                                  |                                      | 1011 15 a      |            | Decode                      | Start      | No                                                                  |         | No       |

| Word  | ls:            | 1                                                             |                                      |                |            |                             | Reset      | opera                                                               | tion c  | peration |

| Cycle | es:            | 2                                                             |                                      |                | E          |                             |            |                                                                     |         |          |

|       | vcle Activity: |                                                               |                                      |                | Exar       |                             | RESET      |                                                                     |         |          |

|       | Q1             | Q2                                                            | Q3                                   | Q4             |            | After Instructi<br>Register |            | /alue                                                               |         |          |

|       | Decode         | Read literal<br>'n'                                           | Process<br>Data                      | Write to<br>PC |            | Flags*                      | = Reset \  |                                                                     |         |          |

|       |                | PUSH PC                                                       |                                      |                |            |                             |            |                                                                     |         |          |

|       |                | to stack                                                      |                                      |                |            |                             |            |                                                                     |         |          |

|       | No             | No                                                            | No                                   | No             |            |                             |            |                                                                     |         |          |

|       | operation      | operation                                                     | operation                            | operation      |            |                             |            |                                                                     |         |          |

Example: HERE RCALL Jump

> Before Instruction PC = Address (HERE) After Instruction

PC = Address (Jump) TOS = Address (HERE + 2)

# 27.4 AC (Timing) Characteristics

# 27.4.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created using one of the following formats:

| 1. TppS2ppS                | 6                               | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|----------------------------|---------------------------------|-----------|----------------------------------------|

| 2. TppS                    |                                 | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                          |                                 |           |                                        |

| F                          | Frequency                       | Т         | Time                                   |

| Lowercase le               | etters (pp) and their meanings: |           |                                        |

| рр                         |                                 |           |                                        |

| сс                         | CCP1                            | osc       | OSC1                                   |

| ck                         | CLKO                            | rd        | RD                                     |

| cs                         | CS                              | rw        | RD or WR                               |

| di                         | SDI                             | sc        | SCK                                    |

| do                         | SDO                             | ss        | SS                                     |

| dt                         | Data in                         | tO        | TOCKI                                  |

| io                         | I/O port                        | t1        | T13CKI                                 |

| mc                         | MCLR                            | wr        | WR                                     |

| Uppercase le               | etters and their meanings:      |           |                                        |

| S                          |                                 |           |                                        |

| F                          | Fall                            | Р         | Period                                 |

| Н                          | High                            | R         | Rise                                   |

| I                          | Invalid (High-impedance)        | V         | Valid                                  |

| L                          | Low                             | Z         | High-impedance                         |

| I <sup>2</sup> C only      |                                 |           |                                        |

| AA                         | output access                   | High      | High                                   |

| BUF                        | Bus free                        | Low       | Low                                    |

| TCC:ST (I <sup>2</sup> C s | pecifications only)             | •         |                                        |

| CC                         |                                 |           |                                        |

| HD                         | Hold                            | SU        | Setup                                  |

| ST                         |                                 |           |                                        |

| DAT                        | DATA input hold                 | STO       | Stop condition                         |

| STA                        | Start condition                 |           |                                        |

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com