Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2321t-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

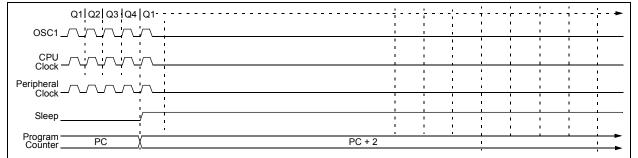

# 4.3 Sleep Mode

The power-managed Sleep mode in the PIC18F2221/ 2321/4221/4321 family devices is identical to the legacy Sleep mode offered in all other PIC devices. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 4-5). All clock source status bits are cleared.

Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS<1:0> bits becomes ready (see Figure 4-6), or it will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see **Section 24.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

## 4.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS<1:0> bits; however, the CPU will not be clocked. The clock source status bits are not affected. Setting IDLEN and executing a SLEEP instruction provides a quick method of switching from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TCSD (parameter 38, Table 27-10) while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or the Sleep mode, a WDT time-out will result in a WDT wake-up to the Run mode currently specified by the SCS<1:0> bits.

FIGURE 4-5: TRANSITION TIMING FOR ENTRY TO SLEEP MODE

| REGISTER 5-1: |                                                                                                                             |                                                                                                                                                                                 |              |                 | -              | - /            | <b>-</b> (2)                  |              |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|----------------|----------------|-------------------------------|--------------|

|               | R/W-0                                                                                                                       | R/W-1 <sup>(1)</sup>                                                                                                                                                            | U-0          | R/W-1           | R-1            | R-1            | R/W-0 <sup>(2)</sup>          | R/W-0        |

|               | IPEN                                                                                                                        | SBOREN                                                                                                                                                                          |              | RI              | TO             | PD             | POR                           | BOR          |

|               | bit 7                                                                                                                       |                                                                                                                                                                                 |              |                 |                |                |                               | bit 0        |

| bit 7         | IPEN: Inte                                                                                                                  | errupt Priority                                                                                                                                                                 | Enable bit   |                 |                |                |                               |              |

|               |                                                                                                                             | e priority level                                                                                                                                                                |              |                 |                |                |                               |              |

|               |                                                                                                                             | le priority leve                                                                                                                                                                |              |                 | CXXX Comp      | patibility mo  | de)                           |              |

| bit 6         |                                                                                                                             | : BOR Softwa<br><1:0> = 01:                                                                                                                                                     | re Enable I  | Dit             |                |                |                               |              |

|               | 1 = BOR i                                                                                                                   |                                                                                                                                                                                 |              |                 |                |                |                               |              |

|               | 0 = BOR i                                                                                                                   |                                                                                                                                                                                 |              |                 |                |                |                               |              |

|               |                                                                                                                             | <1:0> = 00, 1                                                                                                                                                                   |              |                 |                |                |                               |              |

|               |                                                                                                                             | bled and read                                                                                                                                                                   |              |                 |                |                |                               |              |

| bit 5         |                                                                                                                             | nented: Read                                                                                                                                                                    |              |                 |                |                |                               |              |

| bit 4         |                                                                                                                             | Instruction F                                                                                                                                                                   | •            | 4               | 4 h <b>6</b>   |                |                               |              |

|               | 0 = The R                                                                                                                   | RESET instruct<br>RESET instruct<br>wn-out Reset                                                                                                                                | ion was ex   |                 |                |                | st be set in so               | ftware after |

| bit 3         | TO: Watch                                                                                                                   | ndog Time-ou                                                                                                                                                                    | t Flag bit   |                 |                |                |                               |              |

|               |                                                                                                                             | y power-up, ⊂<br>)T time-out oc                                                                                                                                                 |              | truction or SI  | LEEP instruc   | tion           |                               |              |

| bit 2         | PD: Powe                                                                                                                    | er-Down Deteo                                                                                                                                                                   | ction Flag b | oit             |                |                |                               |              |

|               | <ul> <li>1 = Set by power-up or by the CLRWDT instruction</li> <li>0 = Set by execution of the SLEEP instruction</li> </ul> |                                                                                                                                                                                 |              |                 |                |                |                               |              |

| bit 1         | <b>POR</b> : Power-on Reset Status bit <sup>(2)</sup>                                                                       |                                                                                                                                                                                 |              |                 |                |                |                               |              |

|               |                                                                                                                             | <ul> <li>1 = A Power-on Reset has not occurred (set by firmware only)</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul> |              |                 |                |                |                               |              |

| bit 0         | BOR: Bro                                                                                                                    | wn-out Reset                                                                                                                                                                    | Status bit   |                 |                |                |                               |              |

|               |                                                                                                                             | wn-out Reset                                                                                                                                                                    |              |                 |                |                |                               |              |

|               | 0 = A Bro                                                                                                                   | wn-out Reset                                                                                                                                                                    | occurred (   | must be set i   | in software    | after a Brow   | /n-out Reset                  | occurs)      |

|               | Note 1:                                                                                                                     | If SBOREN                                                                                                                                                                       | is enabled   | , its Reset sta | ate is '1'; ot | herwise, it is | <b>s</b> 'O'.                 |              |

|               | 2:                                                                                                                          | The actual F<br>notes follov<br>additional in                                                                                                                                   | ving this r  |                 |                |                | of device Res<br>state of Reg |              |

|               | <u> </u>                                                                                                                    |                                                                                                                                                                                 |              |                 |                |                |                               | 1            |

|               | Legend:                                                                                                                     |                                                                                                                                                                                 |              |                 |                |                |                               |              |

|               | R = Readable bit $W$ = Writable bit $U$ = Unimplemented bit, read as '0' $W$ = $W$ $W$ = $W$                                |                                                                                                                                                                                 |              |                 |                |                |                               |              |

|               | -n = Value                                                                                                                  | at POR                                                                                                                                                                          | '1' = E      | Bit is set      | .0, = Bit      | is cleared     | x = Bit is u                  | nknown       |

|               |                                                                                                                             |                                                                                                                                                                                 |              |                 |                |                |                               |              |

|               | Note 1:                                                                                                                     | It is recom                                                                                                                                                                     |              |                 |                |                |                               | t has been   |

|               |                                                                                                                             | detected so                                                                                                                                                                     | that subse   | equent Power    | -on Resets     | may be det     | ected.                        |              |

2: Brown-out Reset is said to have occurred when BOR is '0' and POR is '1' (assuming that POR was set to '1' by software immediately after Power-on Reset).

# 5.5 Device Reset Timers

PIC18F2221/2321/4221/4321 family devices incorporate three separate on-chip timers that help regulate the Power-on Reset process. Their main function is to ensure that the device clock is stable before code is executed. These timers are:

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- PLL Lock Time-out

#### 5.5.1 POWER-UP TIMER (PWRT)

The Power-up Timer (PWRT) of the PIC18F2221/ 2321/4221/4321 family devices is an 11-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip to chip due to temperature and process variation. See DC parameter 33 for details.

The PWRT is enabled by clearing the PWRTEN Configuration bit.

#### 5.5.2 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter 33). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP, HS and HSPLL modes and only on Power-on Reset, or on exit from most power-managed modes.

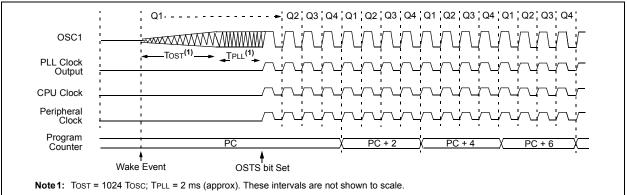

# 5.5.3 PLL LOCK TIME-OUT

With the PLL enabled in HSPLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A separate timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

#### 5.5.4 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows:

- 1. After the POR pulse has cleared, PWRT time-out is invoked (if enabled).

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and the status of the PWRT. Figure 5-3, Figure 5-4, Figure 5-5, Figure 5-6 and Figure 5-7 all depict time-out sequences on power-up, with the Power-up Timer enabled and the device operating in HS Oscillator mode. Figures 5-3 through 5-6 also apply to devices operating in XT or LP modes. For devices in RC mode and with the PWRT disabled, there will be no time-out at all.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, all time-outs will expire. Bringing MCLR high will begin execution immediately (Figure 5-5). This is useful for testing purposes or to synchronize more than one PIC18FXXXX device operating in parallel.

| Oscillator     | Power-up <sup>(2)</sup> and                            | Exit from                       |                                 |  |

|----------------|--------------------------------------------------------|---------------------------------|---------------------------------|--|

| Configuration  | <b>PWRTEN</b> = 0                                      | <b>PWRTEN</b> = 1               | Power-Managed Mode              |  |

| HSPLL          | 66 ms <sup>(1)</sup> + 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> |  |

| HS, XT, LP     | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                       | 1024 Tosc                       |  |

| EC, ECIO       | 66 ms <sup>(1)</sup>                                   | _                               | —                               |  |

| RC, RCIO       | 66 ms <sup>(1)</sup>                                   | _                               | —                               |  |

| INTIO1, INTIO2 | 66 ms <sup>(1)</sup>                                   | —                               | —                               |  |

TABLE 5-2:TIME-OUT IN VARIOUS SITUATIONS

**Note 1:** 66 ms (65.5 ms) is the nominal Power-up Timer (PWRT) delay.

**2**: 2 ms is the nominal time required for the PLL to lock.

NOTES:

# 8.0 DATA EEPROM MEMORY

The data EEPROM is a nonvolatile memory array, separate from the data RAM and program memory, that is used for long-term storage of program data. It is not directly mapped in either the register file or program memory space but is indirectly addressed through the Special Function Registers (SFRs). The EEPROM is readable and writable during normal operation over the entire VDD range.

Four SFRs are used to read and write to the data EEPROM as well as the program memory. They are:

- EECON1

- EECON2

- EEDATA

- EEADR

The data EEPROM allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and the EEADR register holds the address of the EEPROM location being accessed.

The EEPROM data memory is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer. It will vary with voltage and temperature as well as from chip to chip. Please refer to parameter D122 (Table 27-1 in **Section 27.0 "Electrical Characteristics"**) for exact limits.

# 8.1 EECON1 and EECON2 Registers

Access to the data EEPROM is controlled by two registers: EECON1 and EECON2. These are the same registers which control access to the program memory and are used in a similar manner for the data EEPROM.

The EECON1 register (Register 8-1) is the control register for data and program memory access. Control bit EEPGD determines if the access will be to program or data EEPROM memory. When clear, operations will access the data EEPROM memory. When set, program memory is accessed.

Control bit CFGS determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When set, subsequent operations access Configuration registers. When CFGS is clear, the EEPGD bit selects either program Flash or data EEPROM memory.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WREN bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR bit         |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|

|       | is read as '1'. This can indicate that a write |  |  |  |  |  |

|       | operation was prematurely terminated by        |  |  |  |  |  |

|       | a Reset, or a write operation was              |  |  |  |  |  |

|       | attempted improperly.                          |  |  |  |  |  |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

| Note: | The EEIF interrupt flag bit (PIR2<4>) is set |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|

|       | when the write is complete. It must be       |  |  |  |  |  |

|       | cleared in software.                         |  |  |  |  |  |

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. See **Section 7.1 "Table Reads** and **Table Writes"** regarding table reads.

The EECON2 register is not a physical register. It is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

# **10.0 INTERRUPTS**

The PIC18F2221/2321/4221/4321 family devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the lowpriority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2

- PIE1, PIE2

- IPR1, IPR2

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a lowpriority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while any interrupt is enabled. Doing so may cause erratic microcontroller behavior.

# 10.6 INTx Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge; if the bit is clear, the trigger is on the falling edge. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit, INTxF, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxE. Flag bit, INTxF, must be cleared in software in the Interrupt.

All external interrupts (INT0, INT1 and INT2) can wakeup the processor from Idle or Sleep modes if bit INTxE was set prior to going into those modes. If the Global Interrupt Enable bit, GIE, is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high-priority interrupt source.

### 10.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit, TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). See Section 12.0 "Timer0 Module" for further details on the Timer0 module.

# 10.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

# **10.9 Context Saving During Interrupts**

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (see **Section 6.3 "Data Memory Organization"**), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 10-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| EXAMPLE 10-1: | SAVING STATUS, WREG AND BSR REGISTERS IN RAM |   |

|---------------|----------------------------------------------|---|

|               |                                              | 1 |

|          |                     | ·                              |

|----------|---------------------|--------------------------------|

| MOVWF    | W_TEMP              | ; W_TEMP is in virtual bank    |

| MOVFF    | STATUS, STATUS_TEMP | ; STATUS_TEMP located anywhere |

| MOVFF    | BSR, BSR_TEMP       | ; BSR_TMEP located anywhere    |

| ;        |                     |                                |

| ; USER : | ISR CODE            |                                |

| ;        |                     |                                |

| MOVFF    | BSR_TEMP, BSR       | ; Restore BSR                  |

| MOVF     | W_TEMP, W           | ; Restore WREG                 |

| MOVFF    | STATUS_TEMP, STATUS | ; Restore STATUS               |

|          |                     |                                |

| Name  | Bit 7                                                        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on page |

|-------|--------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|----------------------------|

| PORTC | RC7                                                          | RC6   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | 58                         |

| LATC  | ATC PORTC Data Latch Register (Read and Write to Data Latch) |       |       |       |       |       | 58    |       |                            |

| TRISC | PORTC Data Direction Register                                |       |       |       |       |       | 58    |       |                            |

| TABLE 11-6: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTC |

|-------------|--------------------------------------------|

|-------------|--------------------------------------------|

# 11.4 PORTD, TRISD and LATD Registers

| Note: | PORTD    | is | only | available | on | 40/44-pin |

|-------|----------|----|------|-----------|----|-----------|

|       | devices. |    |      |           |    |           |

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

Three of the PORTD pins are multiplexed with outputs P1B, P1C and P1D of the Enhanced CCP module. The operation of these additional PWM output pins is covered in greater detail in Section 17.0 "Enhanced Capture/Compare/PWM (ECCP) Module".

Note: On a Power-on Reset, these pins are configured as digital inputs. PORTD can also be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit, PSPMODE (TRISE<4>). In this mode, the input buffers are TTL. See **Section 11.6 "Parallel Slave Port"** for additional information on the Parallel Slave Port (PSP).

| Note: | When the Enhanced PWM mode is used        |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|

|       | with either dual or quad outputs, the PSP |  |  |  |  |  |

|       | functions of PORTD are automatically      |  |  |  |  |  |

|       | disabled.                                 |  |  |  |  |  |

#### EXAMPLE 11-4: INITIALIZING PORTD

| CLRF  | PORTD | ; Initialize PORTD by<br>; clearing output<br>: data latches |

|-------|-------|--------------------------------------------------------------|

| CLRF  | LATD  | ; Alternate method                                           |

|       |       | ; to clear output                                            |

|       |       | ; data latches                                               |

| MOVLW | OCFh  | ; Value used to                                              |

|       |       | ; initialize data                                            |

|       |       | ; direction                                                  |

| MOVWF | TRISD | ; Set RD<3:0> as inputs                                      |

|       |       | ; RD<5:4> as outputs                                         |

|       |       | ; RD<7:6> as inputs                                          |

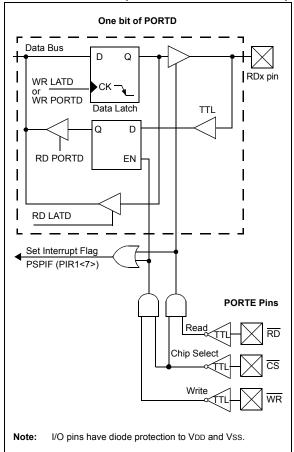

## 11.6 Parallel Slave Port

| Note: | The Parallel Slave Port is only available on |

|-------|----------------------------------------------|

|       | 40/44-pin devices.                           |

In addition to its function as a general I/O port, PORTD can also operate as an 8-bit wide Parallel Slave Port (PSP) or microprocessor port. PSP operation is controlled by the 4 upper bits of the TRISE register (Register 11-1). Setting control bit, PSPMODE (TRISE<4>), enables PSP operation as long as the Enhanced CCP module is not operating in Dual Output or Quad Output PWM mode. In Slave mode, the port is asynchronously readable and writable by the external world.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting the control bit, PSPMODE, enables the PORTE I/O pins to become control inputs for the microprocessor port. When set, port pin RE0 is the RD input, RE1 is the WR input and RE2 is the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits, PFCG<3:0> (ADCON1<3:0>), must also be set to a value in the range of '1010' through '1111'.

A write to the PSP occurs when both the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  lines are first detected low and ends when either are detected high. The PSPIF and IBF flag bits are both set when the write ends.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The data in PORTD is read out and the OBF bit is clear. If the user writes new data to PORTD to set OBF, the data is immediately read out; however, the OBF bit is not set.

When either the  $\overline{CS}$  or  $\overline{RD}$  lines are detected high, the PORTD pins return to the input state and the PSPIF bit is set. User applications should wait for PSPIF to be set before servicing the PSP. When this happens, the IBF and OBF bits can be polled and the appropriate action taken. The timing for the control signals in Write and Read modes is shown in Figure 11-3 and Figure 11-4, respectively.

#### 18.3.5 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 18-2) is to broadcast data by the software protocol.

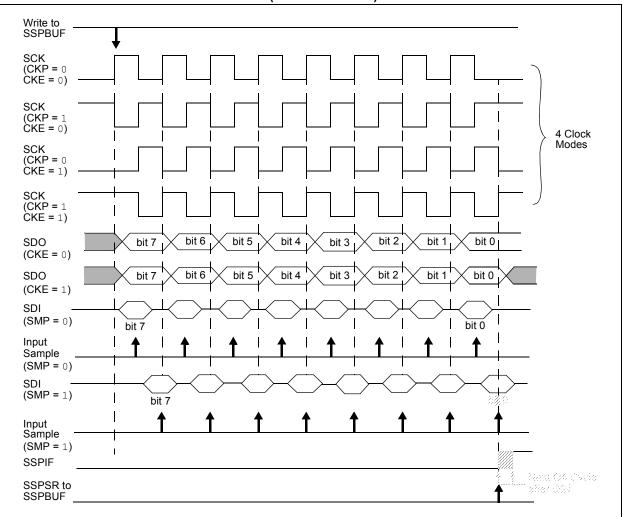

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI operation is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "Line Activity Monitor" mode. The clock polarity is selected by appropriately programming the CKP bit (SSPCON1<4>). This then, would give waveforms for SPI communication as shown in Figure 18-3, Figure 18-5 and Figure 18-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user-programmable to be one of the following:

- · Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum data rate (at 40 MHz) of 10.00 Mbps.

Figure 18-3 shows the waveforms for Master mode. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

FIGURE 18-3: SPI MODE WAVEFORM (MASTER MODE)

# 18.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit (SSPCON1<4>).

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep.

# 18.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI operation must be in Slave mode with the  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 04h). When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the

SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When     | the SP    | l interfa          | ace is in Sla | ave mode  |

|---------|----------|-----------|--------------------|---------------|-----------|

|         | with     | SS        | pin                | control       | enabled   |

|         | (SSPC    | ON1<3     | : <b>0&gt; =</b> 0 | 100), the S   | PI module |

|         | will res | et if the | SS pir             | n is set to V | DD.       |

2: If the SPI interface is used in Slave mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

# FIGURE 18-4: SLAVE SYNCHRONIZATION WAVEFORM

| Name    | Bit 7                | Bit 6       | Bit 5       | Bit 4         | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------|-------------|-------------|---------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL   | TMR0IE      | INT0IE        | RBIE  | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF        | RCIF        | TXIF          | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE        | RCIE        | TXIE          | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP        | RCIP        | TXIP          | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                         |

| RCSTA   | SPEN                 | RX9         | SREN        | CREN          | ADDEN | FERR   | OERR   | RX9D   | 57                         |

| TXREG   | EUSART T             | ransmit Reg | ister       |               |       |        |        |        | 57                         |

| TXSTA   | CSRC                 | TX9         | TXEN        | SYNC          | SENDB | BRGH   | TRMT   | TX9D   | 57                         |

| BAUDCON | ABDOVF               | RCIDL       | RXDTP       | TXCKP         | BRG16 | —      | WUE    | ABDEN  | 57                         |

| SPBRGH  | EUSART B             | aud Rate G  | enerator Re | gister High I | Byte  |        |        |        | 57                         |

| SPBRG   | EUSART B             | aud Rate G  | enerator Re | gister Low E  | Byte  |        |        |        | 57                         |

## TABLE 19-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

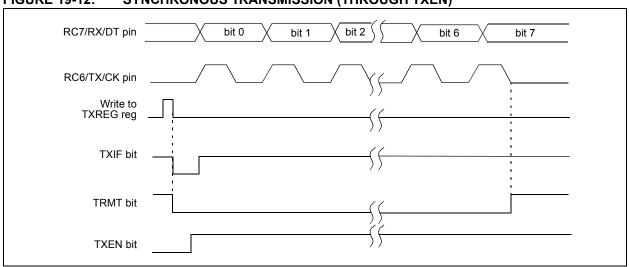

#### FIGURE 19-12: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

## TABLE 19-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7                                         | Bit 6       | Bit 5       | Bit 4      | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|-----------------------------------------------|-------------|-------------|------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                      | PEIE/GIEL   | TMR0IE      | INT0IE     | RBIE  | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1    | PSPIF <sup>(1)</sup>                          | ADIF        | RCIF        | TXIF       | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1    | PSPIE <sup>(1)</sup>                          | ADIE        | RCIE        | TXIE       | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1    | PSPIP <sup>(1)</sup>                          | ADIP        | RCIP        | TXIP       | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                         |

| RCSTA   | SPEN                                          | RX9         | SREN        | CREN       | ADDEN | FERR   | OERR   | RX9D   | 57                         |

| TXREG   | EUSART T                                      | ransmit Reg | ister       |            |       |        |        |        | 57                         |

| TXSTA   | CSRC                                          | TX9         | TXEN        | SYNC       | SENDB | BRGH   | TRMT   | TX9D   | 57                         |

| BAUDCON | ABDOVF                                        | RCIDL       | RXDTP       | TXCKP      | BRG16 | —      | WUE    | ABDEN  | 57                         |

| SPBRGH  | EUSART Baud Rate Generator Register High Byte |             |             |            |       |        |        |        | 57                         |

| SPBRG   | EUSART E                                      | aud Rate G  | enerator Re | gister Low | Byte  |        |        |        | 57                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

**Note 1:** These bits are unimplemented on 28-pin devices and read as '0'.

## 20.4 Operation in Power-Managed Modes

The selection of the automatic acquisition time and A/D conversion clock is determined in part by the clock source and frequency while in a power-managed mode.

If the A/D is expected to operate while the device is in a power-managed mode, the ACQT<2:0> and ADCS<2:0> bits in ADCON2 should be updated in accordance with the clock source to be used in that mode. After entering the mode, an A/D acquisition or conversion may be started. Once started, the device should continue to be clocked by the same clock source until the conversion has been completed.

If desired, the device may be placed into the corresponding Idle mode during the conversion. If the device clock frequency is less than 1 MHz, the A/D RC clock source should be selected.

Operation in Sleep mode requires the A/D FRC clock to be selected. If bits ACQT<2:0> are set to '000' and a conversion is started, the conversion will be delayed one instruction cycle to allow execution of the SLEEP instruction and entry to Sleep mode. The IDLEN bit (OSCCON<7>) must have already been cleared prior to starting the conversion.

# 20.5 Configuring Analog Port Pins

The ADCON1, TRISA, TRISB and TRISE registers all configure the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<3:0> bits and the TRIS bits.

- Note 1: When reading the Port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert as analog inputs. Analog levels on a digitally configured input will be accurately converted.

- 2: Analog levels on any pin defined as a digital input may cause the digital input buffer to consume current out of the device's specification limits.

- 3: The PBADEN bit in Configuration Register 3H configures PORTB pins to reset as analog or digital pins by controlling how the PCFG<3:0> bits in ADCON1 are reset.

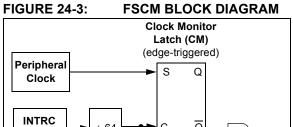

# 24.4 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation in the event of an external oscillator failure by automatically switching the device clock to the internal oscillator block. The FSCM function is enabled by setting the FCMEN Configuration bit.

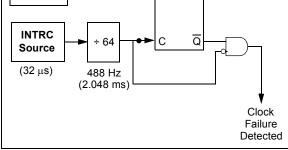

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide a backup clock in the event of a clock failure. Clock monitoring (shown in Figure 24-3) is accomplished by creating a sample clock signal, which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral device clock and the sample clock are presented as inputs to the Clock Monitor latch (CM). The CM is set on the falling edge of the device clock source, but cleared on the rising edge of the sample clock.

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 24-4). This causes the following:

- the FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>);

- the device clock source is switched to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the fail-safe condition); and

- · the WDT is reset.

During switchover, the postscaler frequency from the internal oscillator block may not be sufficiently stable for timing sensitive applications. In these cases, it may be desirable to select another clock configuration and enter an alternate power-managed mode. This can be done to attempt a partial recovery or execute a controlled shutdown. See Section 4.1.4 "Multiple Sleep Commands" and Section 24.3.1 "Special Considerations for Using Two-Speed Start-up" for more details. To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF<2:0>, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF<2:0> bits prior to entering Sleep mode.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator block fails, no failure would be detected, nor would any action be possible.

## 24.4.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTOSC clock when a clock failure is detected. Depending on the frequency selected by the IRCF<2:0> bits, this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, fail-safe clock events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

## 24.4.2 EXITING FAIL-SAFE OPERATION

The fail-safe condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 1H (with any required start-up delays that are required for the oscillator mode, such as OST or PLL timer). The INTOSC multiplexer provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTOSC multiplexer. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

| MO\         | /LW              | Move Lit            | Move Literal to W |           |             |  |  |  |  |

|-------------|------------------|---------------------|-------------------|-----------|-------------|--|--|--|--|

| Synta       | ax:              | MOVLW               | MOVLW k           |           |             |  |  |  |  |

| Oper        | ands:            | $0 \le k \le 25$    | $0 \le k \le 255$ |           |             |  |  |  |  |

| Oper        | ation:           | $k\toW$             |                   |           |             |  |  |  |  |

| Statu       | s Affected:      | None                |                   |           |             |  |  |  |  |

| Enco        | ding:            | 0000                | 1110              | kkkk      | k kkk       |  |  |  |  |

| Desc        | ription:         | The eight-          | bit literal '     | k' is loa | ded into W. |  |  |  |  |

| Words:      |                  | 1                   | 1                 |           |             |  |  |  |  |

| Cycle       | es:              | 1                   | 1                 |           |             |  |  |  |  |

| QC          | ycle Activity:   |                     |                   |           |             |  |  |  |  |

|             | Q1               | Q2                  | Q3                | 6         | Q4          |  |  |  |  |

|             | Decode           | Read<br>literal 'k' | Proce<br>Dat      |           | Write to W  |  |  |  |  |

|             |                  |                     |                   |           |             |  |  |  |  |

| <u>Exan</u> | nple:            | MOVLW               | 5Ah               |           |             |  |  |  |  |

|             | After Instructio | n                   |                   |           |             |  |  |  |  |

|             | W                | = 5Ah               |                   |           |             |  |  |  |  |

| MOVWF                    | Move W t                                                                                                                                                         | o f                                                          |                                                                                                                                |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                  | MOVWF                                                                                                                                                            | f {,a}                                                       |                                                                                                                                |

| Operands:                | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                         |                                                              |                                                                                                                                |

| Operation:               | $(W) \to f$                                                                                                                                                      |                                                              |                                                                                                                                |

| Status Affected:         | None                                                                                                                                                             |                                                              |                                                                                                                                |

| Encoding:                | 0110                                                                                                                                                             | 111a ff                                                      | ff ffff                                                                                                                        |

|                          | 256-byte ba<br>If 'a' is '0', tl<br>If 'a' is '1', tl<br>GPR bank (<br>If 'a' is '0' a<br>set is enabl<br>in Indexed I<br>mode when<br>Section 25<br>Bit-Oriente | ne Access Ba<br>ne BSR is use<br>(default).<br>nd the extend | nk is selected.<br>d to select the<br>ed instruction<br>ction operates<br>Addressing<br>Fh). See<br>iented and<br>s in Indexed |

| Words:                   | 1                                                                                                                                                                |                                                              |                                                                                                                                |

| Cycles:                  | 1                                                                                                                                                                |                                                              |                                                                                                                                |

|                          |                                                                                                                                                                  |                                                              |                                                                                                                                |

| Q Cycle Activity:        |                                                                                                                                                                  |                                                              |                                                                                                                                |

| Q Cycle Activity:<br>Q1  | Q2                                                                                                                                                               | Q3                                                           | Q4                                                                                                                             |

|                          | Q2<br>Read<br>register 'f'                                                                                                                                       | Q3<br>Process<br>Data                                        | Q4<br>Write<br>register 'f'                                                                                                    |

| Q1                       | Read<br>register 'f'                                                                                                                                             | Process                                                      | Write                                                                                                                          |

| Q1<br>Decode             | Read<br>register 'f'                                                                                                                                             | Process<br>Data                                              | Write                                                                                                                          |

| Q1<br>Decode<br>Example: | Read<br>register 'f'<br>MOVWF I<br>tion<br>= 4Fh<br>= FFh                                                                                                        | Process<br>Data                                              | Write                                                                                                                          |

# DC Characteristics: Power-Down and Supply Current PIC18F2221/2321/4221/4321 (Industrial) PIC18LF2221/2321/4221/4321 (Industrial) (Continued)

| PIC18LF2221/2321/4221/4321<br>(Industrial)<br>PIC18F2221/2321/4221/4321<br>(Industrial, Extended) |                                     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial                                                                                                                             |      |       |                      |            |                                         |  |

|---------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------|------------|-----------------------------------------|--|

|                                                                                                   |                                     | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |       |                      |            |                                         |  |

| Param<br>No.                                                                                      | Device                              | Тур                                                                                                                                                                                                                                                            | Max  | Units | Conditions           |            |                                         |  |

|                                                                                                   | Supply Current (IDD) <sup>(2)</sup> |                                                                                                                                                                                                                                                                |      |       |                      |            |                                         |  |

|                                                                                                   | PIC18LF2X21/4X21                    | 12                                                                                                                                                                                                                                                             | 19   | μA    | -40°C <sup>(5)</sup> |            |                                         |  |

|                                                                                                   |                                     |                                                                                                                                                                                                                                                                | 19   | μA    | -10°C                |            |                                         |  |

|                                                                                                   |                                     | 13                                                                                                                                                                                                                                                             | 19   | μA    | +25°C                | VDD = 2.0V |                                         |  |

|                                                                                                   |                                     | 13                                                                                                                                                                                                                                                             | 19   | μA    | +85°C                |            |                                         |  |

|                                                                                                   | PIC18LF2X21/4X21                    | 40                                                                                                                                                                                                                                                             | 45   | μA    | -40°C <sup>(5)</sup> |            |                                         |  |

|                                                                                                   |                                     |                                                                                                                                                                                                                                                                | 45   | μA    | -10°C                | VDD = 3.0V | Fosc = 32 kHz<br>( <b>SEC_RUN</b> mode, |  |

|                                                                                                   |                                     | 33                                                                                                                                                                                                                                                             | 45   | μA    | +25°C                | VDD = 3.0V | Timer1 as clock) <sup>(3)</sup>         |  |

|                                                                                                   |                                     | 27                                                                                                                                                                                                                                                             | 45   | μA    | +85°C                |            |                                         |  |

|                                                                                                   | All Devices                         | 101                                                                                                                                                                                                                                                            | 115  | μA    | -40°C <sup>(5)</sup> |            |                                         |  |

|                                                                                                   |                                     | _                                                                                                                                                                                                                                                              | 110  | μA    | -10°C                | VDD = 5.0V |                                         |  |

|                                                                                                   |                                     | 83                                                                                                                                                                                                                                                             | 110  | μA    | +25°C                | VDD = 3.0V |                                         |  |

|                                                                                                   |                                     | 65                                                                                                                                                                                                                                                             | 88   | μA    | +85°C                |            |                                         |  |

|                                                                                                   | PIC18LF2X21/4X21                    | 2.5                                                                                                                                                                                                                                                            | 5    | μA    | -40°C <sup>(5)</sup> |            |                                         |  |

|                                                                                                   |                                     | —                                                                                                                                                                                                                                                              | 5    | μA    | -10°C                | VDD = 2.0V |                                         |  |

|                                                                                                   |                                     | 3.0                                                                                                                                                                                                                                                            | 5    | μA    | +25°C                | VDD - 2.0V |                                         |  |

|                                                                                                   |                                     | 3.5                                                                                                                                                                                                                                                            | 8    | μA    | +85°C                |            |                                         |  |

|                                                                                                   | PIC18LF2X21/4X21                    | 3.9                                                                                                                                                                                                                                                            | 7    | μA    | -40°C <sup>(5)</sup> | _          | Fosc = 32 kHz                           |  |

|                                                                                                   |                                     | _                                                                                                                                                                                                                                                              | 7    | μA    | -10°C                | VDD = 3.0V | (SEC_IDLE mode,                         |  |

|                                                                                                   |                                     | 4.5                                                                                                                                                                                                                                                            | 7    | μA    | +25°C                |            | Timer1 as clock) <sup>(3)</sup>         |  |

|                                                                                                   |                                     | 5.2                                                                                                                                                                                                                                                            | 10.7 | μA    | +85°C                |            | ,<br>,                                  |  |

|                                                                                                   | All Devices                         | 7.5                                                                                                                                                                                                                                                            | 10   | μΑ    | -40°C <sup>(5)</sup> | 4          |                                         |  |

|                                                                                                   |                                     | _                                                                                                                                                                                                                                                              | 10   | μΑ    | -10°C                | VDD = 5.0V |                                         |  |