Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4221-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: DEVICE FEAT                   | URES                                                                                                         | 1                                                                                                            | 1                                                                                                            |                                                                                                              |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Features                                 | PIC18F2221                                                                                                   | PIC18F2321                                                                                                   | PIC18F4221                                                                                                   | PIC18F4321                                                                                                   |

| Operating Frequency                      | DC – 40 MHz                                                                                                  |

| Program Memory (Bytes)                   | 4096                                                                                                         | 8192                                                                                                         | 4096                                                                                                         | 8192                                                                                                         |

| Program Memory (Instructions)            | 2048                                                                                                         | 4096                                                                                                         | 2048                                                                                                         | 4096                                                                                                         |

| Data Memory (Bytes)                      | 512                                                                                                          | 512                                                                                                          | 512                                                                                                          | 512                                                                                                          |

| Data EEPROM Memory (Bytes)               | 256                                                                                                          | 256                                                                                                          | 256                                                                                                          | 256                                                                                                          |

| Interrupt Sources                        | 19                                                                                                           | 19                                                                                                           | 20                                                                                                           | 20                                                                                                           |

| I/O Ports                                | Ports A, B, C, (E)                                                                                           | Ports A, B, C, (E)                                                                                           | Ports A, B, C, D, E                                                                                          | Ports A, B, C, D, E                                                                                          |

| Timers                                   | 4                                                                                                            | 4                                                                                                            | 4                                                                                                            | 4                                                                                                            |

| Capture/Compare/PWM Modules              | 2                                                                                                            | 2                                                                                                            | 1                                                                                                            | 1                                                                                                            |

| Enhanced Capture/Compare/<br>PWM Modules | 0                                                                                                            | 0                                                                                                            | 1                                                                                                            | 1                                                                                                            |

| Serial Communications                    | MSSP,<br>Enhanced USART                                                                                      | MSSP,<br>Enhanced USART                                                                                      | MSSP,<br>Enhanced USART                                                                                      | MSSP,<br>Enhanced USART                                                                                      |

| Parallel Communications (PSP)            | No                                                                                                           | No                                                                                                           | Yes                                                                                                          | Yes                                                                                                          |

| 10-bit Analog-to-Digital Module          | 10 Input Channels                                                                                            | 10 Input Channels                                                                                            | 13 Input Channels                                                                                            | 13 Input Channels                                                                                            |

| Resets (and Delays)                      | POR, BOR,<br>RESET Instruction,<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST),<br>MCLR (optional),<br>WDT |

| Programmable Low-Voltage<br>Detect       | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          |

| Programmable Brown-out Reset             | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          |

| Instruction Set                          | 75 Instructions;<br>83 with Extended<br>Instruction Set<br>enabled                                           |

| Packages                                 | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN                                                     | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN                                                     | 40-pin PDIP<br>44-pin QFN<br>44-pin TQFP                                                                     | 40-pin PDIP<br>44-pin QFN<br>44-pin TQFP                                                                     |

# TABLE 1-1: DEVICE FEATURES

NOTES:

| <b>REGISTER 3-2:</b> | OSCCON: OSCILLATOR CONTROL REGISTER                          |                               |                |                |                  |               |                                  |       |  |  |

|----------------------|--------------------------------------------------------------|-------------------------------|----------------|----------------|------------------|---------------|----------------------------------|-------|--|--|

|                      | R/W-0                                                        | R/W-1                         | R/W-0          | R/W-0          | R <sup>(1)</sup> | R-0           | R/W-0                            | R/W-0 |  |  |

|                      | IDLEN                                                        | IRCF2                         | IRCF1          | IRCF0          | OSTS             | IOFS          | SCS1                             | SCS0  |  |  |

|                      | bit 7                                                        |                               |                |                |                  |               | •                                | bit 0 |  |  |

|                      |                                                              |                               |                |                |                  |               |                                  |       |  |  |

| bit 7                | IDLEN: Idle                                                  | e Enable bit                  |                |                |                  |               |                                  |       |  |  |

|                      |                                                              | enters an lo                  |                |                |                  |               |                                  |       |  |  |

|                      |                                                              | enters Slee                   | •              |                |                  | s executed    |                                  |       |  |  |

| bit 6-4              |                                                              | : Internal Os                 |                |                | ct bits          |               |                                  |       |  |  |

|                      | 111 = 8 M<br>110 = 4 M                                       | Hz (INTOSC<br>Hz              | anves cloc     | k directiy)    |                  |               |                                  |       |  |  |

|                      | 101 <b>= 2 M</b>                                             | Hz                            |                |                |                  |               |                                  |       |  |  |

|                      | 100 = 1 M                                                    |                               |                |                |                  |               |                                  |       |  |  |

|                      | 011 = 500<br>010 = 250                                       |                               |                |                |                  |               |                                  |       |  |  |

|                      | 001 = 125                                                    |                               |                |                |                  |               |                                  |       |  |  |

|                      |                                                              | Hz (from eit                  |                |                | • ·              | (2)           |                                  |       |  |  |

| bit 3                |                                                              | cillator Start-               |                |                |                  |               |                                  |       |  |  |

|                      |                                                              |                               |                |                |                  |               | llator is runn<br>tor is not rea |       |  |  |

| bit 2                |                                                              | DSC Freque                    | -              | -              | 0/1              | ,             |                                  | ,     |  |  |

|                      |                                                              | C frequency                   | -              |                |                  |               |                                  |       |  |  |

|                      | 0 = INTOS                                                    | SC frequency                  | / is not stabl | е              |                  |               |                                  |       |  |  |

| bit 1-0              |                                                              | System Clo                    |                | ts             |                  |               |                                  |       |  |  |

|                      |                                                              | nal oscillator                |                | -              |                  |               |                                  |       |  |  |

|                      |                                                              | ondary (Time<br>ary oscillato |                | 1              |                  |               |                                  |       |  |  |

|                      | Note 1:                                                      | Reset state                   | depends or     | n state of the | e IESO Conf      | iguration bit |                                  |       |  |  |

|                      | 2: Source selected by the INTSRC bit (OSCTUNE<7>), see text. |                               |                |                |                  |               |                                  |       |  |  |

|                      | 3: Default output frequency of INTOSC on Reset.              |                               |                |                |                  |               |                                  |       |  |  |

|                      | Lowende                                                      |                               |                |                |                  |               |                                  |       |  |  |

|                      | Legend:<br>R = Reada                                         | hla hit                       | ۸۸ – ۱۸        | /ritable bit   | II – I Inin      | nlomented     | bit, read as                     | ·0'   |  |  |

|                      | -n = Value                                                   |                               |                | it is set      |                  | s cleared     | x = Bit is u                     |       |  |  |

|                      |                                                              |                               | D              |                | 0 - 51(1         |               | л – Dit 13 u                     |       |  |  |

|                      |                                                              |                               |                |                |                  |               |                                  |       |  |  |

### EXAMPLE 7-3: WRITING TO FLASH PROGRAM MEMORY

|               | MOVLW          | D'64'               | ; | number of bytes in erase block                 |

|---------------|----------------|---------------------|---|------------------------------------------------|

|               | MOVWF          | COUNTER             |   |                                                |

|               | MOVLW          | BUFFER ADDR HIGH    | ; | point to buffer                                |

|               | MOVWF          | FSROH               |   |                                                |

|               | MOVLW          | BUFFER ADDR LOW     |   |                                                |

|               | MOVWF          | FSROL               |   |                                                |

|               | MOVLW          | CODE ADDR UPPER     | ; | Load TBLPTR with the base                      |

|               | MOVWF          | TBLPTRU —           |   | address of the memory block                    |

|               | MOVLW          | CODE ADDR HIGH      |   | 1                                              |

|               | MOVWF          | TBLPTRH             |   |                                                |

|               | MOVLW          | CODE ADDR LOW       | ; | 6 LSB = 0                                      |

|               | MOVWF          | TBLPTRL             | , |                                                |

| READ BLOCK    |                |                     |   |                                                |

|               | TBLRD*+        | -                   | ; | read into TABLAT, and inc                      |

|               | MOVF           | TABLAT, W           |   | get data                                       |

|               |                | POSTINCO            |   | store data and increment FSR0                  |

|               |                | COUNTER             | - | done?                                          |

|               | BRA            | READ BLOCK          |   | repeat                                         |

| MODIFY WORD   | Didi           | 111112_220011       | , | 202040                                         |

| 110D111_0010D | MOVLW          | DATA ADDR HIGH      |   | point to buffer                                |

|               | MOVWF          | FSROH               | , | 00 201101                                      |

|               | MOVWF          | DATA ADDR LOW       |   |                                                |

|               | MOVLW<br>MOVWF | FSROL               |   |                                                |

|               |                |                     |   | undate buffer word and increment EGDO          |

|               | MOVLW          | NEW_DATA_LOW        | ; | update buffer word and increment FSR0          |

|               | MOVWF          | POSTINCO            |   | undate buffer word                             |

|               | MOVLW          | NEW_DATA_HIGH       | ; | update buffer word                             |

|               | MOVWF          | INDF0               |   |                                                |

| ERASE_BLOCK   |                |                     |   |                                                |

|               | MOVLW          |                     |   | load TBLPTR with the base                      |

|               | MOVWF          | TBLPTRU             | ; | address of the memory block                    |

|               | MOVLW          | CODE_ADDR_HIGH      |   |                                                |

|               | MOVWF          | TBLPTRH             |   |                                                |

|               | MOVLW          | CODE_ADDR_LOW       | ; | 6  LSB = 0                                     |

|               | MOVWF          | TBLPTRL             |   |                                                |

|               | BCF            | EECON1, CFGS        |   | point to PROG/EEPROM memory                    |

|               | BSF            | EECON1, EEPGD       | ; | point to Flash program memory                  |

|               | BSF            | EECON1, WREN        | ; | enable write to memory                         |

|               | BSF            | EECON1, FREE        | ; | enable Row Erase operation                     |

|               | BCF            | INTCON, GIE         | ; | disable interrupts                             |

|               | MOVLW          | 55h                 | ; | Required sequence                              |

|               | MOVWF          | EECON2              | ; | write 55h                                      |

|               | MOVLW          | 0AAh                |   |                                                |

|               | MOVWF          | EECON2              | ; | write AAh                                      |

|               | BSF            | EECON1, WR          | ; | start erase (CPU stall)                        |

|               | NOP            |                     |   |                                                |

|               | BSF            | INTCON, GIE         | ; | re-enable interrupts                           |

| WRITE_BUFFER_ | BACK           |                     |   |                                                |

|               | MOVLW          | 8                   | ; | number of write buffer groups of 8 bytes       |

|               | MOVWF          | COUNTER HI          |   |                                                |

|               | MOVLW          | BUFFER ADDR HIGH    | ; | point to buffer                                |

|               | MOVWF          | FSR0H               | • | -                                              |

|               | MOVLW          | BUFFER ADDR LOW     |   |                                                |

|               | MOVWF          | FSROL               |   |                                                |

| PROGRAM LOOP  |                | -                   |   |                                                |

|               | MOVLW          | 8                   | : | number of bytes in holding register            |

|               | MOVWF          | COUNTER             | , | i i i i i i i i i i i i i i i i i i i          |

| WRITE WORD TO |                |                     |   |                                                |

|               | MOVF           | POSTINCO, W         |   | get low byte of buffer data and increment FSR0 |

|               | MOVF<br>MOVWF  | TABLAT              |   | present data to table latch                    |

|               | TBLWT+*        |                     |   | short write                                    |

|               | т п л т т      |                     |   | to internal TBLWT holding register, increment  |

|               |                |                     |   | TBLPTR                                         |

|               | DFCFC7         | COUNTER             |   | loop until buffers are full                    |

|               |                |                     | ; | TOOP WHETT DUITETS ALE TUIT                    |

|               | GOTO           | WRITE_WORD_TO_HREGS |   |                                                |

|               |                |                     |   |                                                |

### 8.5 Operation During Code-Protect

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

The microcontroller itself can both read and write to the internal data EEPROM, regardless of the state of the code-protect Configuration bit. Refer to Section 24.0 "Special Features of the CPU" for additional information.

### 8.6 Protection Against Spurious Write

To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT, parameter 33).

The write initiate sequence and the WREN bit together help prevent an accidental write during Brown-out Reset, power glitch or software malfunction.

### 8.7 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing data. Such data is typically updated at least one time within the number of writes defined by specification, D124. If any location storing data is not written at least this often, the data EEPROM array must be refreshed. For this reason, values that change infrequently, or not at all, should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 8-3.

**Note:** If data EEPROM is only used to store constants and/or data that changes often, an array refresh is likely not required. See specification, D124.

| EXAMPLE 8-3: | DATA EEPROM REFRESH ROUTINE |

|--------------|-----------------------------|

|--------------|-----------------------------|

|      |        | DATA EEL KG   |                              |

|------|--------|---------------|------------------------------|

|      | CLRF   | EEADR         | ; Start at address 0         |

|      | BCF    | EECON1, CFGS  | ; Set for memory             |

|      | BCF    | EECON1, EEPGD | ; Set for Data EEPROM        |

|      | BCF    | INTCON, GIE   | ; Disable interrupts         |

|      | BSF    | EECON1, WREN  | ; Enable writes              |

| LOOP |        |               | ; Loop to refresh array      |

|      | BSF    | EECON1, RD    | ; Read current address       |

|      | MOVLW  | 55h           | ;                            |

|      | MOVWF  | EECON2        | ; Write 55h                  |

|      | MOVLW  | 0AAh          | ;                            |

|      | MOVWF  | EECON2        | ; Write OAAh                 |

|      | BSF    | EECON1, WR    | ; Set WR bit to begin write  |

|      | BTFSC  | EECON1, WR    | ; Wait for write to complete |

|      | BRA    | \$-2          |                              |

|      | INCFSZ | EEADR, F      | ; Increment address          |

|      | BRA    | LOOP          | ; Not zero, do it again      |

|      | BCF    | EECON1, WREN  | ; Disable writes             |

|      | BSF    | INTCON, GIE   | ; Enable interrupts          |

| 1    |        |               |                              |

| INTCON3:                              | INTERRU                      | PICONII         | ROL REGI    | SIER 3       |              |        |        |  |  |

|---------------------------------------|------------------------------|-----------------|-------------|--------------|--------------|--------|--------|--|--|

| R/W-1                                 | R/W-1                        | U-0             | R/W-0       | R/W-0        | U-0          | R/W-0  | R/W-0  |  |  |

| INT2IP                                | INT1IP                       | —               | INT2IE      | INT1IE       | —            | INT2IF | INT1IF |  |  |

| bit 7                                 |                              |                 |             |              |              |        | bit 0  |  |  |

| INT2IP: IN                            | T2 External                  | nterrupt Pri    | ority bit   |              |              |        |        |  |  |

| 1 = High priority<br>0 = Low priority |                              |                 |             |              |              |        |        |  |  |

| INT1IP: IN                            | T1 External                  | nterrupt Pri    | ority bit   |              |              |        |        |  |  |

| 1 = High p<br>0 = Low pr              |                              |                 |             |              |              |        |        |  |  |

| Unimplem                              | ented: Read                  | <b>l as</b> '0' |             |              |              |        |        |  |  |

| INT2IE: IN                            | T2 External                  | nterrupt En     | able bit    |              |              |        |        |  |  |

|                                       | es the INT2 e                |                 | •           |              |              |        |        |  |  |

|                                       | es the INT2                  |                 | •           |              |              |        |        |  |  |

|                                       | T1 External                  | •               |             |              |              |        |        |  |  |

|                                       | es the INT1 e<br>es the INT1 |                 | •           |              |              |        |        |  |  |

| Unimplem                              | ented: Read                  | <b>l as</b> '0' |             |              |              |        |        |  |  |

| INT2IF: IN                            | T2 External I                | nterrupt Fla    | ıg bit      |              |              |        |        |  |  |

|                                       | IT2 external                 | •               | •           | t be cleared | in software) | )      |        |  |  |

| 0 = The IN                            | IT2 external                 | interrupt dic   | d not occur |              |              |        |        |  |  |

|                                       | T1 External I                | •               | •           |              |              |        |        |  |  |

|                                       | IT1 external                 |                 | · ·         | t be cleared | in software) | )      |        |  |  |

| 0 = 1  ne IN                          | IT1 external                 | interrupt aic   | not occur   |              |              |        |        |  |  |

### REGISTER 10-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

|       | R/W-1                    | R/W-1         | U-0             | R/W-1        | R/W-1        | R/W-1       | R/W-1           | R/W-1  |

|-------|--------------------------|---------------|-----------------|--------------|--------------|-------------|-----------------|--------|

|       | OSCFIP                   | CMIP          |                 | EEIP         | BCLIP        | HLVDIP      | TMR3IP          | CCP2IP |

|       | bit 7                    |               |                 |              |              |             |                 | bit 0  |

|       |                          |               |                 |              |              |             |                 |        |

| bit 7 |                          |               | il Interrupt P  | riority bit  |              |             |                 |        |

|       | 1 = High p<br>0 = Low pr |               |                 |              |              |             |                 |        |

| bit 6 | CMIP: Com                | parator Inte  | errupt Priorit  | y bit        |              |             |                 |        |

|       | 1 = High p<br>0 = Low pr | •             |                 |              |              |             |                 |        |

| bit 5 | Unimpleme                | ented: Rea    | <b>d as</b> '0' |              |              |             |                 |        |

| bit 4 | EEIP: Data               | EEPROM/       | Flash Write     | Operation In | terrupt Prio | rity bit    |                 |        |

|       | 1 = High p<br>0 = Low pr | •             |                 |              |              |             |                 |        |

| bit 3 | BCLIP: Bus               | s Collision I | nterrupt Prio   | rity bit     |              |             |                 |        |

|       | 1 = High p<br>0 = Low pr | •             |                 |              |              |             |                 |        |

| bit 2 | HLVDIP: Hi               | igh/Low-Vo    | ltage Detect    | Interrupt Pr | iority bit   |             |                 |        |

|       | 1 = High p               |               |                 |              |              |             |                 |        |

|       | 0 = Low pr               | iority        |                 |              |              |             |                 |        |

| bit 1 |                          |               | ow Interrupt    | Priority bit |              |             |                 |        |

|       | 1 = High p<br>0 = Low pr | •             |                 |              |              |             |                 |        |

| bit 0 | CCP2IP: C                | CP2 Interru   | pt Priority bi  | t            |              |             |                 |        |

|       | 1 = High p<br>0 = Low pr | •             |                 |              |              |             |                 |        |

|       | Legend:                  |               |                 |              |              |             |                 |        |

|       | R = Readat               | ole bit       | W = Wr          | itable bit   | U = Unim     | plemented I | oit, read as '( | D'     |

|       |                          |               |                 |              |              |             |                 |        |

'1' = Bit is set

'0' = Bit is cleared

#### REGISTER 10-9: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

-n = Value at POR

x = Bit is unknown

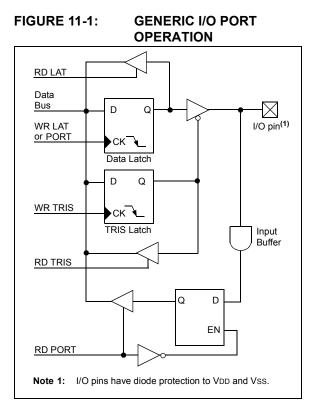

# 11.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (Data Latch register)

The Data Latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 11-1.

# 11.1 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin). Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The Data Latch (LATA) register is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input and one of the comparator outputs to become the RA4/T0CKI/C1OUT pin. Pins RA6 and RA7 are multiplexed with the main oscillator pins. They are enabled as oscillator or I/O pins by the selection of the main oscillator in the Configuration register (see **Section 24.1 "Configuration Bits**" for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs and the comparator voltage reference output. The operation of pins RA<3:0> and RA5 as A/D converter inputs is selected by clearing or setting the control bits in the ADCON1 register (A/D Control Register 1).

Pins RA0 through RA5 may also be used as comparator inputs or outputs by setting the appropriate bits in the CMCON register. To use RA<3:0> as digital inputs, it is also necessary to turn off the comparators.

| Note: | On a Power-on Reset, RA5 and RA<3:0>          |

|-------|-----------------------------------------------|

|       | are configured as analog inputs and read      |

|       | as '0'. RA4 is configured as a digital input. |

The RA4/T0CKI/C1OUT pin is a Schmitt Trigger input. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 11-1: INITIALIZING PORTA

| CLRF  | PORTA  | ; | Initialize PORTA by       |

|-------|--------|---|---------------------------|

|       |        | ; | clearing output           |

|       |        | ; | data latches              |

| CLRF  | LATA   | ; | Alternate method          |

|       |        | ; | to clear output           |

|       |        | ; | data latches              |

| MOVLW | OFh    | ; | Configure all A/D         |

| MOVWF | ADCON1 | ; | for digital inputs        |

| MOVWF | 07h    | ; | Configure comparators     |

| MOVWF | CMCON  | ; | for digital input         |

| MOVLW | OCFh   | ; | Value used to             |

|       |        | ; | initialize data           |

|       |        | ; | direction                 |

| MOVWF | TRISA  | ; | Set RA<7:6,3:0> as inputs |

|       |        | ; | RA<5:4> as outputs        |

| 1     |        |   |                           |

### 11.4 PORTD, TRISD and LATD Registers

| Note: | PORTD    | is | only | available | on | 40/44-pin |

|-------|----------|----|------|-----------|----|-----------|

|       | devices. |    |      |           |    |           |

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

Three of the PORTD pins are multiplexed with outputs P1B, P1C and P1D of the Enhanced CCP module. The operation of these additional PWM output pins is covered in greater detail in Section 17.0 "Enhanced Capture/Compare/PWM (ECCP) Module".

Note: On a Power-on Reset, these pins are configured as digital inputs. PORTD can also be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit, PSPMODE (TRISE<4>). In this mode, the input buffers are TTL. See **Section 11.6 "Parallel Slave Port"** for additional information on the Parallel Slave Port (PSP).

| Note: | When the Enhanced PWM mode is used        |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | with either dual or quad outputs, the PSP |  |  |  |  |  |  |  |

|       | functions of PORTD are automatically      |  |  |  |  |  |  |  |

|       | disabled.                                 |  |  |  |  |  |  |  |

#### EXAMPLE 11-4: INITIALIZING PORTD

| CLRF  | PORTD | ; Initialize PORTD by<br>; clearing output<br>: data latches |

|-------|-------|--------------------------------------------------------------|

| CLRF  | LATD  | ; Alternate method                                           |

|       |       | ; to clear output                                            |

|       |       | ; data latches                                               |

| MOVLW | OCFh  | ; Value used to                                              |

|       |       | ; initialize data                                            |

|       |       | ; direction                                                  |

| MOVWF | TRISD | ; Set RD<3:0> as inputs                                      |

|       |       | ; RD<5:4> as outputs                                         |

|       |       | ; RD<7:6> as inputs                                          |

|       |       |                                                              |

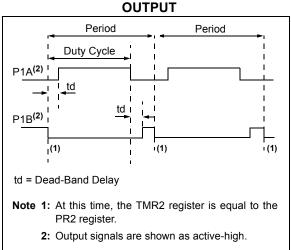

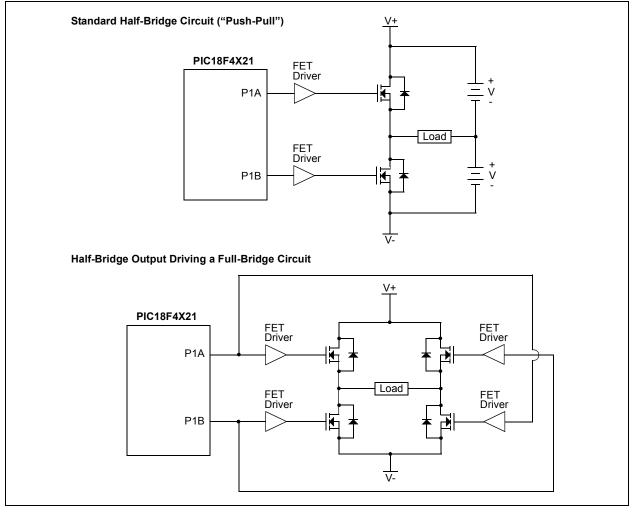

### 17.4.4 HALF-BRIDGE MODE

In the Half-Bridge Output mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the P1A pin, while the complementary PWM output signal is output on the P1B pin (Figure 17-4). This mode can be used for half-bridge applications, as shown in Figure 17-5, or for full-bridge applications where four power switches are being modulated with two PWM signals.

In Half-Bridge Output mode, the programmable deadband delay can be used to prevent shoot-through current in half-bridge power devices. The value of bits, PDC<6:0>, sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 17.4.6 "Programmable Dead-Band Delay"** for more details of the dead-band delay operations.

Since the P1A and P1B outputs are multiplexed with the PORTC<2> and PORTD<5> data latches, the TRISC<2> and TRISD<5> bits must be cleared to configure P1A and P1B as outputs.

# FIGURE 17-4: HALF-BRIDGE PWM

### FIGURE 17-5: EXAMPLES OF HALF-BRIDGE OUTPUT MODE APPLICATIONS

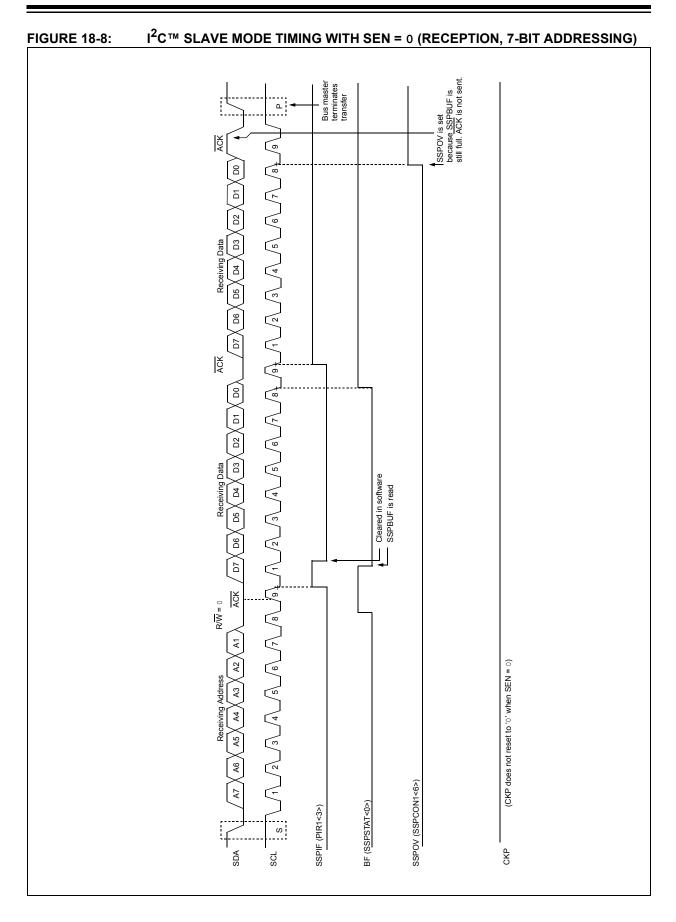

### 18.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 18.4.7 "Baud Rate"** for more detail.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPCON2<0>).

- 2. SSPIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- 4. Address is shifted out the SDA pin until all 8 bits are transmitted.

- 5. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register.

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 7. The user loads the SSPBUF with eight bits of data.

- 8. Data is shifted out the SDA pin until all 8 bits are transmitted.

- 9. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register.

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPCON2<2>).

- 12. Interrupt is generated once the Stop condition is complete.

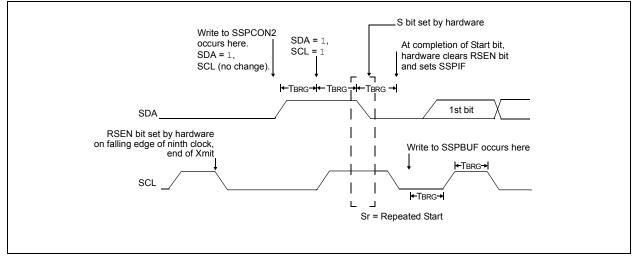

### 18.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- **Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

### 18.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

### FIGURE 18-22: REPEATED START CONDITION WAVEFORM

| Mnemo     | onic,        | Description                     | Cycles | 16-Bit Instruction Word |      |      |      | Status          | N     |

|-----------|--------------|---------------------------------|--------|-------------------------|------|------|------|-----------------|-------|

| Operands  |              | Description                     | Cycles | MSb                     |      |      | LSb  | Affected        | Notes |

| LITERAL ( | <b>DPERA</b> | TIONS                           |        |                         |      |      |      |                 |       |

| ADDLW     | k            | Add Literal and WREG            | 1      | 0000                    | 1111 | kkkk | kkkk | C, DC, Z, OV, N |       |

| ANDLW     | k            | AND Literal with WREG           | 1      | 0000                    | 1011 | kkkk | kkkk | Z, N            |       |

| IORLW     | k            | Inclusive OR Literal with WREG  | 1      | 0000                    | 1001 | kkkk | kkkk | Z, N            |       |

| LFSR      | f, k         | Move Literal (12-bit) 2nd Word  | 2      | 1110                    | 1110 | 00ff | kkkk | None            |       |

|           |              | to FSR(f) 1st Word              |        | 1111                    | 0000 | kkkk | kkkk |                 |       |

| MOVLB     | k            | Move Literal to BSR<3:0>        | 1      | 0000                    | 0001 | 0000 | kkkk | None            |       |

| MOVLW     | k            | Move Literal to WREG            | 1      | 0000                    | 1110 | kkkk | kkkk | None            |       |

| MULLW     | k            | Multiply Literal with WREG      | 1      | 0000                    | 1101 | kkkk | kkkk | None            |       |

| RETLW     | k            | Return with Literal in WREG     | 2      | 0000                    | 1100 | kkkk | kkkk | None            |       |

| SUBLW     | k            | Subtract WREG from Literal      | 1      | 0000                    | 1000 | kkkk | kkkk | C, DC, Z, OV, N |       |

| XORLW     | k            | Exclusive OR Literal with WREG  | 1      | 0000                    | 1010 | kkkk | kkkk | Z, N            |       |

| DATA MEN  | IORY ←       | > PROGRAM MEMORY OPERATIO       | NS     |                         |      |      |      |                 |       |

| TBLRD*    |              | Table Read                      | 2      | 0000                    | 0000 | 0000 | 1000 | None            |       |

| TBLRD*+   |              | Table Read with Post-Increment  |        | 0000                    | 0000 | 0000 | 1001 | None            |       |

| TBLRD*-   |              | Table Read with Post-Decrement  |        | 0000                    | 0000 | 0000 | 1010 | None            |       |

| TBLRD+*   |              | Table Read with Pre-Increment   |        | 0000                    | 0000 | 0000 | 1011 | None            |       |

| TBLWT*    |              | Table Write                     | 2      | 0000                    | 0000 | 0000 | 1100 | None            |       |

| TBLWT*+   |              | Table Write with Post-Increment |        | 0000                    | 0000 | 0000 | 1101 | None            |       |

| TBLWT*-   |              | Table Write with Post-Decrement |        | 0000                    | 0000 | 0000 | 1110 | None            |       |

| TBLWT+*   |              | Table Write with Pre-Increment  |        | 0000                    | 0000 | 0000 | 1111 | None            |       |

### TABLE 25-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| POP                                     | •                             | Рор Тор                                                                                               | Pop Top of Return Stack                                       |                                                      |                                      |                                                     |  |  |  |  |

|-----------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------|--------------------------------------|-----------------------------------------------------|--|--|--|--|

| Synta                                   | ax:                           | POP                                                                                                   | POP                                                           |                                                      |                                      |                                                     |  |  |  |  |

| Oper                                    | ands:                         | None                                                                                                  | None                                                          |                                                      |                                      |                                                     |  |  |  |  |

| Oper                                    | ation:                        | $(TOS) \rightarrow bi$                                                                                | $(TOS) \rightarrow bit bucket$                                |                                                      |                                      |                                                     |  |  |  |  |

| Statu                                   | s Affected:                   | None                                                                                                  |                                                               |                                                      |                                      |                                                     |  |  |  |  |

| Enco                                    | ding:                         | 0000                                                                                                  | 0000                                                          | 000                                                  | C                                    | 0110                                                |  |  |  |  |

| Description:                            |                               | The TOS v<br>stack and is<br>then becom<br>was pushed<br>This instruct<br>the user to<br>stack to inc | s discard<br>nes the p<br>d onto th<br>ction is p<br>properly | led. The<br>previous<br>e return<br>rovided<br>manag | e T(<br>s va<br>n sta<br>to<br>je th | DS value<br>lue that<br>ack.<br>enable<br>ne return |  |  |  |  |

| Word                                    | ls:                           | 1                                                                                                     |                                                               |                                                      |                                      |                                                     |  |  |  |  |

| Cycle                                   | es:                           | 1                                                                                                     |                                                               |                                                      |                                      |                                                     |  |  |  |  |

| QC                                      | ycle Activity:                |                                                                                                       |                                                               |                                                      |                                      |                                                     |  |  |  |  |

|                                         | Q1                            | Q2                                                                                                    | Q3                                                            |                                                      |                                      | Q4                                                  |  |  |  |  |

|                                         | Decode                        | No<br>operation                                                                                       | POP 1<br>valu                                                 |                                                      | op                                   | No<br>peration                                      |  |  |  |  |

| <u>Exan</u>                             | <u>nple:</u>                  | POP<br>GOTO                                                                                           | NEW                                                           |                                                      |                                      |                                                     |  |  |  |  |

| Before Instructio<br>TOS<br>Stack (1 le |                               | tion<br>level down)                                                                                   | -                                                             | )031A2<br>)14332                                     |                                      |                                                     |  |  |  |  |

|                                         | After Instructic<br>TOS<br>PC | on                                                                                                    | -                                                             | )14332<br>NEW                                        | h                                    |                                                     |  |  |  |  |

| PUS                                            | н                           | Push Top                                                                                  | Push Top of Return Stack            |                                                |                                |                                     |  |  |  |

|------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------|--------------------------------|-------------------------------------|--|--|--|

| Synta                                          | ax:                         | PUSH                                                                                      | PUSH                                |                                                |                                |                                     |  |  |  |

| Operands:                                      |                             | None                                                                                      |                                     |                                                |                                |                                     |  |  |  |

| Oper                                           | ation:                      | (PC + 2) $\rightarrow$                                                                    | TOS                                 |                                                |                                |                                     |  |  |  |

| Statu                                          | s Affected:                 | None                                                                                      |                                     |                                                |                                |                                     |  |  |  |

| Enco                                           | ding:                       | 0000                                                                                      | 0000                                | 000                                            | 0                              | 0101                                |  |  |  |

| Description:                                   |                             | The PC + 2<br>the return s<br>value is pus<br>This instruc<br>software sta<br>then pushin | tack.<br>shed c<br>tion a<br>ack by | The prev<br>lown on t<br>llows imp<br>modifyir | ious<br>the s<br>blem<br>ng T( | TOS<br>stack.<br>enting a<br>OS and |  |  |  |

| Word                                           | s:                          | 1                                                                                         |                                     |                                                |                                |                                     |  |  |  |

| Cycle                                          | es:                         | 1                                                                                         |                                     |                                                |                                |                                     |  |  |  |

| QC                                             | ycle Activity:              |                                                                                           |                                     |                                                |                                |                                     |  |  |  |

|                                                | Q1                          | Q2                                                                                        |                                     | Q3                                             |                                | Q4                                  |  |  |  |

| Decode                                         |                             | PUSH<br>PC + 2 onto<br>return stack                                                       | No<br>operation                     |                                                | op                             | No<br>peration                      |  |  |  |

| Exan                                           | <u>nple:</u>                | PUSH                                                                                      |                                     |                                                |                                |                                     |  |  |  |

|                                                | Before Instruc<br>TOS<br>PC | tion                                                                                      | =<br>=                              | 345Ah<br>0124h                                 |                                |                                     |  |  |  |

| After Instruction<br>PC<br>TOS<br>Stack (1 lev |                             | on                                                                                        | =                                   | 0126h                                          |                                |                                     |  |  |  |

# 25.2.2 EXTENDED INSTRUCTION SET

| ADD       | FSR                      | Add Lite         | ral to FS                                                                   | SR             |          |  |  |  |

|-----------|--------------------------|------------------|-----------------------------------------------------------------------------|----------------|----------|--|--|--|

| Synta     | x:                       | ADDFSR           | ADDFSR f, k                                                                 |                |          |  |  |  |

| Operands: |                          | $0 \le k \le 63$ |                                                                             |                |          |  |  |  |

|           |                          | f ∈ [ 0, 1, 2    | 2]                                                                          |                |          |  |  |  |

| Opera     | ation:                   | FSR(f) + k       | $\rightarrow$ FSR(f                                                         | <sup>-</sup> ) |          |  |  |  |

| Status    | Affected:                | None             |                                                                             |                |          |  |  |  |

| Enco      | ding:                    | 1110             | 1000                                                                        | ffkk           | kkkk     |  |  |  |

| Descr     | iption:                  |                  | The 6-bit literal 'k' is added to the contents of the FSR specified by 'f'. |                |          |  |  |  |

| Words:    |                          | 1                |                                                                             |                |          |  |  |  |

| Cycle     | s:                       | 1                |                                                                             |                |          |  |  |  |

| Q Cy      | cle Activity:            |                  |                                                                             |                |          |  |  |  |

|           | Q1                       | Q2               | Q3                                                                          |                | Q4       |  |  |  |

| Γ         | Decode                   | Read             | Proces                                                                      | ss V           | Vrite to |  |  |  |

|           |                          | literal 'k'      | Data                                                                        |                | FSR      |  |  |  |

| Exam      | <u>ple:</u>              | ADDFSR 2,        | , 23h                                                                       |                |          |  |  |  |

| E         | Before Instruc<br>FSR2   | tion<br>= 03FFh  |                                                                             |                |          |  |  |  |

| ŀ         | After Instructio<br>FSR2 | on<br>= 0422h    |                                                                             |                |          |  |  |  |

| ADDULNK           | Add Literal to                                                                                                                                                                                                                                                                                                           | FSR2 and        | Return          |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|--|--|--|--|

| Syntax:           | ADDULNK k                                                                                                                                                                                                                                                                                                                |                 |                 |  |  |  |  |

| Operands:         | $0 \le k \le 63$                                                                                                                                                                                                                                                                                                         |                 |                 |  |  |  |  |

| Operation:        | FSR2 + k $\rightarrow$ FS<br>(TOS) $\rightarrow$ PC                                                                                                                                                                                                                                                                      | R2,             |                 |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                                     |                 |                 |  |  |  |  |

| Encoding:         | 1110 1000                                                                                                                                                                                                                                                                                                                | 11kk            | kkkk            |  |  |  |  |

| Worder            | contents of FSR2. A RETURN is then<br>executed by loading the PC with the<br>TOS.<br>The instruction takes two cycles to<br>execute; a NOP is performed during the<br>second cycle.<br>This may be thought of as a special<br>case of the ADDFSR instruction, where<br>f = 3 (binary '11'); it operates only on<br>FSR2. |                 |                 |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                        |                 |                 |  |  |  |  |

| Cycles:           | 2                                                                                                                                                                                                                                                                                                                        |                 |                 |  |  |  |  |

| Q Cycle Activity: | 02                                                                                                                                                                                                                                                                                                                       | 02              | 04              |  |  |  |  |

| Q1                | Q2                                                                                                                                                                                                                                                                                                                       | Q3              | Q4              |  |  |  |  |

| Decode            | Read<br>literal 'k'                                                                                                                                                                                                                                                                                                      | Process<br>Data | Write to<br>FSR |  |  |  |  |

| No                | No                                                                                                                                                                                                                                                                                                                       | No              | No              |  |  |  |  |

| Operation         | Operation                                                                                                                                                                                                                                                                                                                | Operation       | Operation       |  |  |  |  |

| Example: | ADDULNK  | 23h  |

|----------|----------|------|

|          | ADDODINI | 2011 |

| Before Instruct  | tion |       |

|------------------|------|-------|

| FSR2             | =    | 03FFh |

| PC               | =    | 0100h |

| After Instructio | n    |       |

| FSR2             | =    | 0422h |

| PC               | =    | (TOS) |

|                  |      |       |

**Note:** All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction syntax then becomes: {label} instruction argument(s).

# DC Characteristics: Power-Down and Supply Current PIC18F2221/2321/4221/4321 (Industrial) PIC18LF2221/2321/4221/4321 (Industrial) (Continued)