Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                              |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 4KB (2K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

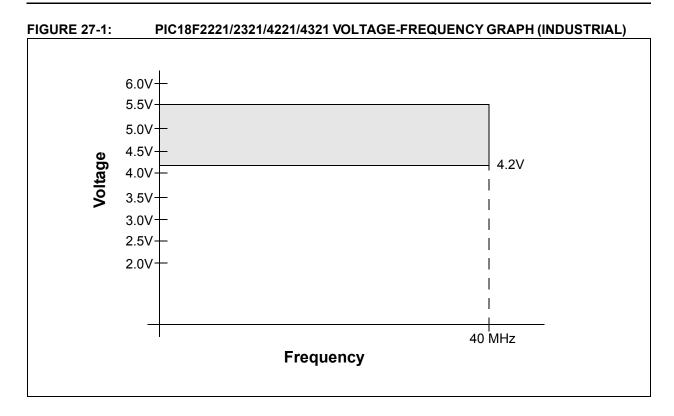

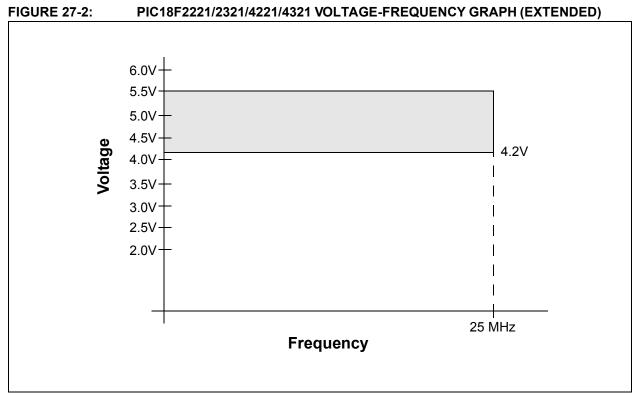

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 13x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4221-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File Name | Bit 7               | Bit 6                 | Bit 5                     | Bit 4               | Bit 3               | Bit 2               | Bit 1                      | Bit 0                 | Value on<br>POR, BOR | Details on<br>page: |

|-----------|---------------------|-----------------------|---------------------------|---------------------|---------------------|---------------------|----------------------------|-----------------------|----------------------|---------------------|

| TMR0H     | Timer0 Regis        | ter High Byte         |                           |                     |                     |                     |                            |                       | 0000 0000            | 56, 131             |

| TMR0L     | Timer0 Regis        | ter Low Byte          |                           |                     |                     |                     |                            |                       | XXXX XXXX            | 56, 131             |

| T0CON     | TMR0ON              | T08BIT                | TOCS                      | T0SE                | PSA                 | T0PS2               | T0PS1                      | T0PS0                 | 1111 1111            | 56, 129             |

| OSCCON    | IDLEN               | IRCF2                 | IRCF1                     | IRCF0               | OSTS                | IOFS                | SCS1                       | SCS0                  | 0100 q000            | 37, 56              |

| HLVDCON   | VDIRMAG             | _                     | IRVST                     | HLVDEN              | HLVDL3              | HLVDL2              | HLVDL1                     | HLVDL0                | 0-00 0101            | 56, 253             |

| WDTCON    | —                   | —                     | —                         | _                   | _                   | _                   | —                          | SWDTEN                | 0                    | 56, 270             |

| RCON      | IPEN                | SBOREN <sup>(1)</sup> | _                         | RI                  | TO                  | PD                  | POR                        | BOR                   | 0q-1 11q0            | 48, 54, 108         |

| TMR1H     | Timer1 Regis        | ter High Byte         |                           |                     |                     |                     |                            | •                     | XXXX XXXX            | 56, 137             |

| TMR1L     | Timer1 Regis        | ter Low Byte          | _                         | _                   |                     |                     | _                          |                       | XXXX XXXX            | 56, 137             |

| T1CON     | RD16                | T1RUN                 | T1CKPS1                   | T1CKPS0             | T10SCEN             | T1SYNC              | TMR1CS                     | TMR10N                | 0000 0000            | 56, 133             |

| TMR2      | Timer2 Regis        | ter                   |                           |                     |                     |                     |                            | •                     | 0000 0000            | 56, 140             |

| PR2       | Timer2 Period       | d Register            |                           |                     |                     |                     |                            |                       | 1111 1111            | 56, 140             |

| T2CON     | —                   | T2OUTPS3              | T2OUTPS2                  | T2OUTPS1            | T2OUTPS0            | TMR2ON              | T2CKPS1                    | T2CKPS0               | -000 0000            | 56, 139             |

| SSPBUF    | MSSP Receiv         | ve Buffer/Tran        | smit Register             |                     |                     |                     |                            |                       | ****                 | 56, 175,<br>176     |

| SSPADD    | MSSP Addres         | ss Register in        | I <sup>2</sup> C™ Slave m | ode. MSSP B         | aud Rate Relo       | ad Register in      | I <sup>2</sup> C Master mo | ode.                  | 0000 0000            | 56, 176             |

| SSPSTAT   | SMP                 | CKE                   | D/Ā                       | Р                   | S                   | R/W                 | UA                         | BF                    | 0000 0000            | 56, 168,<br>177     |

| SSPCON1   | WCOL                | SSPOV                 | SSPEN                     | СКР                 | SSPM3               | SSPM2               | SSPM1                      | SSPM0                 | 0000 0000            | 56, 169,<br>178     |

| SSPCON2   | GCEN                | ACKSTAT               | ACKDT/<br>ADMSK5          | ACKEN/<br>ADMSK4    | RCEN/<br>ADMSK3     | PEN/<br>ADMSK2      | RSEN/<br>ADMSK1            | SEN                   | 0000 0000            | 56, 179             |

| ADRESH    | A/D Result R        | egister High B        | yte                       |                     |                     |                     |                            |                       | xxxx xxxx            | 57, 242             |

| ADRESL    | A/D Result Re       | egister Low By        | /te                       |                     |                     |                     |                            |                       | XXXX XXXX            | 57, 242             |

| ADCON0    | —                   | —                     | CHS3                      | CHS2                | CHS1                | CHS0                | GO/DONE                    | ADON                  | 00 0000              | 57, 233             |

| ADCON1    | —                   | _                     | VCFG1                     | VCFG0               | PCFG3               | PCFG2               | PCFG1                      | PCFG0                 | 00 0qqq              | 57, 234             |

| ADCON2    | ADFM                | —                     | ACQT2                     | ACQT1               | ACQT0               | ADCS2               | ADCS1                      | ADCS0                 | 0-00 0000            | 57, 235             |

| CCPR1H    | Capture/Com         | pare/PWM Re           | gister 1 High I           | Byte                |                     |                     |                            |                       | XXXX XXXX            | 57, 146             |

| CCPR1L    | Capture/Com         | pare/PWM Re           | gister 1 Low E            | Byte                |                     |                     |                            |                       | XXXX XXXX            | 57, 146             |

| CCP1CON   | P1M1 <sup>(2)</sup> | P1M0 <sup>(2)</sup>   | DC1B1                     | DC1B0               | CCP1M3              | CCP1M2              | CCP1M1                     | CCP1M0                | 0000 0000            | 57, 145,<br>153     |

| CCPR2H    | Capture/Com         | pare/PWM Re           | gister 2 High I           | Byte                |                     |                     |                            |                       | XXXX XXXX            | 57, 146             |

| CCPR2L    | Capture/Com         | pare/PWM Re           | gister 2 Low E            | Byte                |                     |                     |                            |                       | XXXX XXXX            | 57, 146             |

| CCP2CON   | —                   | —                     | DC2B1                     | DC2B0               | CCP2M3              | CCP2M2              | CCP2M1                     | CCP2M0                | 00 0000              | 57, 145             |

| BAUDCON   | ABDOVF              | RCIDL                 | RXDTP                     | TXCKP               | BRG16               | —                   | WUE                        | ABDEN                 | 0100 0-00            | 57, 214             |

| ECCP1DEL  | PRSEN               | PDC6 <sup>(2)</sup>   | PDC5 <sup>(2)</sup>       | PDC4 <sup>(2)</sup> | PDC3 <sup>(2)</sup> | PDC2 <sup>(2)</sup> | PDC1 <sup>(2)</sup>        | PDC0 <sup>(2)</sup>   | 0000 0000            | 57, 162             |

| ECCP1AS   | ECCPASE             | ECCPAS2               | ECCPAS1                   | ECCPAS0             | PSSAC1              | PSSAC0              | PSSBD1 <sup>(2)</sup>      | PSSBD0 <sup>(2)</sup> | 0000 0000            | 57, 163             |

| CVRCON    | CVREN               | CVROE                 | CVRR                      | CVRSS               | CVR3                | CVR2                | CVR1                       | CVR0                  | 0000 0000            | 57, 249             |

| CMCON     | C2OUT               | C1OUT                 | C2INV                     | C1INV               | CIS                 | CM2                 | CM1                        | CM0                   | 0000 0111            | 57, 243             |

| TMR3H     | Timer3 Regis        | ter High Byte         |                           |                     |                     |                     |                            |                       | **** ****            | 57, 143             |

| TMR3L     | Timer3 Regis        | ter Low Byte          |                           |                     | 1                   |                     |                            | 1                     | **** ****            | 57, 143             |

| T3CON     | RD16                | T3CCP2                | T3CKPS1                   | T3CKPS0             | T3CCP1              | T3SYNC              | TMR3CS                     | TMR3ON                | 0000 0000            | 57, 141             |

#### TABLE 6-2:REGISTER FILE SUMMARY (PIC18F2221/2321/4221/4321) (CONTINUED)

$\label{eq:legend: second sec$

Note 1: The SBOREN bit is only available when the BOREN<1:0> Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

2: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

3: The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in INTOSC Modes".

4: The RE3 bit is only available when Master Clear Reset is disabled (MCLRE Configuration bit = 0); otherwise, RE3 reads as '0'. This bit is read-only.

5: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

6: Bit 7 and bit 6 are cleared by user software or by a POR.

#### 6.3.5 STATUS REGISTER

The STATUS register, shown in Register 6-2, contains the arithmetic status of the ALU. As with any other SFR, it can be the operand for any instruction.

If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, the results of the instruction are not written; instead, the STATUS register is updated according to the instruction performed. Therefore, the result of an instruction with the STATUS register as its destination may be different than intended. As an example, CLRF STATUS will set the Z bit and leave the remaining Status bits unchanged ('000u u1uu'). It is recommended that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions that do not affect Status bits, see the instruction set summaries in Table 24-2 and Table 24-3.

Note: The C and DC bits operate as the borrow and digit borrow bits, respectively, in subtraction.

#### REGISTER 6-2: STATUS REGISTER

|         | U-0                                                                                                             | U-0                                                          | U-0                           | R/W-x            | R/W-x                                            | R/W-x        | R/W-x         | R/W-x    |  |

|---------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------|------------------|--------------------------------------------------|--------------|---------------|----------|--|

|         | —                                                                                                               | —                                                            | —                             | N                | OV                                               | Z            | DC            | С        |  |

|         | bit 7                                                                                                           |                                                              |                               |                  |                                                  |              |               | bit 0    |  |

|         |                                                                                                                 |                                                              |                               |                  |                                                  |              |               |          |  |

| bit 7-5 | Unimplen                                                                                                        | nented: Read                                                 | <b>d as</b> '0'               |                  |                                                  |              |               |          |  |

| bit 4   | N: Negative bit<br>This bit is used for signed arithmetic (2's complement). It indicates whether the result was |                                                              |                               |                  |                                                  |              |               |          |  |

|         | negative (                                                                                                      | ALU MSB =                                                    | 1).                           | c (2's comp      | lement). It in                                   | dicates whe  | ther the res  | ult was  |  |

|         | <ul> <li>1 = Result was negative</li> <li>0 = Result was positive</li> </ul>                                    |                                                              |                               |                  |                                                  |              |               |          |  |

| bit 3   | OV: Overf                                                                                                       | low bit                                                      |                               |                  |                                                  |              |               |          |  |

|         | magnitude<br>1 = Overfl                                                                                         | used for sign<br>which cause<br>ow occurred<br>erflow occurr | es the sign b<br>for signed a | oit (bit 7 of th | ne result) to o                                  | change state | 9.            | າe 7-bit |  |

| bit 2   | Z: Zero bit                                                                                                     | t                                                            |                               |                  |                                                  |              |               |          |  |

|         |                                                                                                                 | esult of an ari                                              |                               |                  |                                                  | )            |               |          |  |

| bit 1   | DC: Digit                                                                                                       | Carry/borrow                                                 | bit                           |                  |                                                  |              |               |          |  |

|         | For ADDWI                                                                                                       | F, ADDLW, SUI                                                | BLW and SUE                   | BWF instructi    | ons:                                             |              |               |          |  |

|         |                                                                                                                 | y-out from the<br>rry-out from t                             |                               |                  |                                                  | rred         |               |          |  |

|         | Note:                                                                                                           | complemer                                                    | nt of the sec                 | ond operan       | d. A subtrac<br>d. For rotate<br>ie source reg   | e (RRF, RLF) |               |          |  |

| bit 0   | C: Carry/b                                                                                                      | orrow bit                                                    |                               |                  |                                                  |              |               |          |  |

|         | For ADDWI                                                                                                       | F, ADDLW, SUI                                                | BLW <b>and</b> SUE            | BWF instructi    | ons:                                             |              |               |          |  |

|         |                                                                                                                 | y-out from the<br>rry-out from t                             |                               |                  |                                                  |              |               |          |  |

|         | Note:                                                                                                           | complemer                                                    | nt of the sec                 | ond operan       | d. A subtrac<br>d. For rotate<br>order bit of th | e (RRF, RLF) | ) instruction |          |  |

|         | Legend:                                                                                                         |                                                              |                               |                  |                                                  |              |               | ]        |  |

|         | R = Reada                                                                                                       | able bit                                                     | W = W                         | /ritable bit     | U = Unim                                         | plemented    | bit, read as  | ʻ0'      |  |

'1' = Bit is set

-n = Value at POR

x = Bit is unknown

'0' = Bit is cleared

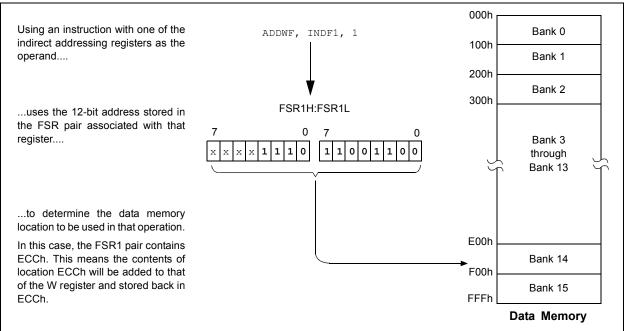

### 6.4.3.1 FSR Registers and the INDF Operand

At the core of indirect addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. The four upper bits of the FSRnH register are not used so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers: they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because indirect addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

#### 6.4.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers that cannot be indirectly read or written to. Accessing these registers actually accesses the associated FSR register pair, but also performs a specific action on its stored value. They are:

- POSTDEC: accesses the FSR value, then automatically decrements it by 1 afterwards

- POSTINC: accesses the FSR value, then automatically increments it by 1 afterwards

- PREINC: increments the FSR value by 1, then uses it in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the new value in the operation.

In this context, accessing an INDF register uses the value in the FSR registers without changing them. Similarly, accessing a PLUSW register gives the FSR value offset by that in the W register; neither value is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR registers.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

#### FIGURE 6-7: INDIRECT ADDRESSING

| RTCinit |        |              |                                               |

|---------|--------|--------------|-----------------------------------------------|

|         | MOVLW  | 80h          | ; Preload TMR1 register pair                  |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                       |

|         | CLRF   | TMR1L        |                                               |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,               |

|         | MOVWF  | T1CON        | ; Asynchronous operation, external oscillator |

|         | CLRF   | secs         | ; Initialize timekeeping registers            |

|         | CLRF   | mins         | ;                                             |

|         | MOVLW  | .12          |                                               |

|         | MOVWF  | hours        |                                               |

|         | BSF    | PIE1, TMR1IE | ; Enable Timer1 interrupt                     |

|         | RETURN |              |                                               |

| RTCisr  |        |              |                                               |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                  |

|         | BCF    | PIR1, TMR1IF | ; Clear interrupt flag                        |

|         | INCF   | secs, F      | ; Increment seconds                           |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                         |

|         | CPFSGT | secs         |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | secs         | ; Clear seconds                               |

|         | INCF   | mins, F      | ; Increment minutes                           |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                         |

|         | CPFSGT | mins         |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | mins         | ; clear minutes                               |

|         | INCF   | hours, F     | ; Increment hours                             |

|         | MOVLW  | .23          | ; 24 hours elapsed?                           |

|         | CPFSGT | hours        |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | hours        | ; Reset hours                                 |

|         | RETURN |              | ; Done                                        |

#### TABLE 13-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Name   | Bit 7                        | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|------------------------------|---------------|---------|---------|---------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH                     | PEIE/GIEL     | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1   | PSPIF <sup>(1)</sup>         | ADIF          | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1   | PSPIE <sup>(1)</sup>         | ADIE          | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1   | PSPIP <sup>(1)</sup>         | ADIP          | RCIP    | TXIP    | SSPIP   | CCP1IP | TMR2IP | TMR1IP | 58                         |

| TMR1L  | Timer1 Reg                   | gister Low By | /te     |         |         |        |        |        | 56                         |

| TMR1H  | 1H Timer1 Register High Byte |               |         |         |         |        |        |        | 56                         |

| T1CON  | RD16                         | T1RUN         | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 56                         |

Legend: Shaded cells are not used by the Timer1 module.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

#### 18.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- · Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full detect bit, BF (SSPSTAT<0>), and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored and the write collision detect bit, WCOL

(SSPCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The Buffer Full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 18-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP Status register (SSPSTAT) indicates the various status conditions.

| Note: | To avoid lost data in Master mode, a read of |

|-------|----------------------------------------------|

|       | the SSPBUF must be performed to clear the    |

|       | Buffer Full (BF) detect bit (SSPSTAT<0>)     |

|       | between each transmission.                   |

|       |                                              |

Note: The SSPBUF register cannot be used with read-modify-write instructions, such as BCF, BTFSC and COMF, etc.

#### EXAMPLE 18-1: LOADING THE SSPBUF (SSPSR) REGISTER

| LOOP | BTFSS | SSPSTAT, BF | ;Has data been received (transmit complete)? |

|------|-------|-------------|----------------------------------------------|

|      | BRA   | LOOP        | ;No                                          |

|      | MOVF  | SSPBUF, W   | ;WREG reg = contents of SSPBUF               |

|      | MOVWF | RXDATA      | ;Save in user RAM, if data is meaningful     |

|      | MOVF  | TXDATA, W   | ;W reg = contents of TXDATA                  |

|      | MOVWF | SSPBUF      | ;New data to xmit                            |

|         | -          |              |                  | -                | -               | _              | -               | _      | -                          |

|---------|------------|--------------|------------------|------------------|-----------------|----------------|-----------------|--------|----------------------------|

| Name    | Bit 7      | Bit 6        | Bit 5            | Bit 4            | Bit 3           | Bit 2          | Bit 1           | Bit 0  | Reset<br>Values<br>on page |

| INTCON  | GIE/GIEH   | PEIE/GIEL    | TMR0IE           | INT0IE           | RBIE            | TMR0IF         | INT0IF          | RBIF   | 55                         |

| PIR1    | PSPIF      | ADIF         | RCIF             | TXIF             | SSPIF           | CCP1IF         | TMR2IF          | TMR1IF | 58                         |

| PIE1    | PSPIE      | ADIE         | RCIE             | TXIE             | SSPIE           | CCP1IE         | TMR2IE          | TMR1IE | 58                         |

| IPR1    | PSPIP      | ADIP         | RCIP             | TXIP             | SSPIP           | CCP1IP         | TMR2IP          | TMR1IP | 58                         |

| PIR2    | OSCFIF     | CMIF         | _                | EEIF             | BCLIF           | HLVDIF         | TMR3IF          | CCP2IF | 58                         |

| PIE2    | OSCFIE     | CMIE         | _                | EEIE             | BCLIE           | HLVDIE         | TMR3IE          | CCP2IE | 58                         |

| IPR2    | OSCFIP     | CMIP         | _                | EEIP             | BCLIP           | HLVDIP         | TMR3IP          | CCP2IP | 58                         |

| TRISC   | TRISC7     | TRISC6       | TRISC5           | TRISC4           | TRISC3          | TRISC2         | TRISC1          | TRISC0 | 58                         |

| TRISD   | TRISD7     | TRISD6       | TRISD5           | TRISD4           | TRISD3          | TRISD2         | TRISD1          | TRISD0 | 58                         |

| SSPBUF  | MSSP Rec   | eive Buffer/ | Fransmit Re      | gister           |                 |                |                 |        | 56                         |

| SSPADD  | ADD7       | ADD6         | ADD5             | ADD4             | ADD3            | ADD2           | ADD1            | ADD0   | 56                         |

| TMR2    | Timer2 Reg | gister       |                  |                  |                 |                |                 |        | 56                         |

| PR2     | Timer2 Per | iod Register |                  |                  |                 |                |                 |        | 56                         |

| SSPCON1 | WCOL       | SSPOV        | SSPEN            | CKP              | SSPM3           | SSPM2          | SSPM1           | SSPM0  | 56                         |

| SSPCON2 | GCEN       | ACKSTAT      | ACKDT/<br>ADMSK5 | ACKEN/<br>ADMSK5 | RCEN/<br>ADMSK5 | PEN/<br>ADMSK5 | RSEN/<br>ADMSK5 | SEN    | 56                         |

| SSPSTAT | SMP        | CKE          | D/A              | Р                | S               | R/W            | UA              | BF     | 56                         |

### TABLE 18-4: REGISTERS ASSOCIATED WITH I<sup>2</sup>C<sup>™</sup> OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C$  mode.

| REGISTER 19-2: | RCSTA: R                        |                                                        | TATUS AN       |                |              | TER           |              |              |

|----------------|---------------------------------|--------------------------------------------------------|----------------|----------------|--------------|---------------|--------------|--------------|

|                | R/W-0                           | R/W-0                                                  | R/W-0          | R/W-0          | R/W-0        | R-0           | R-0          | R-x          |

|                | SPEN                            | RX9                                                    | SREN           | CREN           | ADDEN        | FERR          | OERR         | RX9D         |

|                | bit 7                           |                                                        |                |                |              |               |              | bit 0        |

| bit 7          |                                 | ial Dart Enal                                          | bla bit        |                |              |               |              |              |

| bit 7          |                                 | ial Port Enal                                          |                | DV/DT and      | TV/CK pipe   | an aprial pa  | rt nina)     |              |

|                |                                 | oort disabled                                          |                |                | TX/CK pins   | as senai po   | it pins)     |              |

| bit 6          | <b>RX9:</b> 9-bit               | Receive Ena                                            | able bit       |                |              |               |              |              |

|                |                                 | <ul> <li>9-bit recept</li> <li>8-bit recept</li> </ul> |                |                |              |               |              |              |

| bit 5          | SREN: Sin                       | gle Receive                                            | Enable bit     |                |              |               |              |              |

|                | <u>Asynchron</u><br>Don't care. |                                                        |                |                |              |               |              |              |

|                | Synchrono                       | us mode – N                                            | /laster:       |                |              |               |              |              |

|                |                                 | s single rece                                          |                |                |              |               |              |              |

|                |                                 | es single rec                                          |                |                |              |               |              |              |

|                |                                 | leared after                                           | -              | complete.      |              |               |              |              |

|                | Don't care.                     | <u>us mode – S</u>                                     | <u>blave:</u>  |                |              |               |              |              |

| bit 4          |                                 | ntinuous Re                                            | ceive Enable   | e bit          |              |               |              |              |

|                | Asynchron                       |                                                        |                |                |              |               |              |              |

|                | 1 = Enable                      |                                                        |                |                |              |               |              |              |

|                | 0 = Disable                     | es receiver                                            |                |                |              |               |              |              |

|                | Synchrono                       |                                                        |                |                | ODEN         |               |              |              |

|                |                                 | s continuous<br>es continuou                           |                | til enable bit | CREN is cle  | eared (CREI   | N overrides  | SREN)        |

| bit 3          |                                 | ddress Dete                                            |                | t              |              |               |              |              |

| bit o          |                                 | ous mode 9-                                            |                |                |              |               |              |              |

|                |                                 |                                                        |                |                | upt and load | s the receiv  | e buffer whe | en RSR<8>    |

|                | 0 = Disabl                      | es address o                                           | detection, all | bytes are r    | eceived and  | ninth bit car | n be used as | s parity bit |

|                |                                 | ous mode 9-                                            | bit (RX9 = c   | ) <u>):</u>    |              |               |              |              |

|                | Don't care.                     |                                                        |                |                |              |               |              |              |

| bit 2          |                                 | ming Error b                                           |                |                |              |               |              |              |

|                | 1 = Framin<br>0 = No fran       |                                                        | be updated     | by reading     | RCREG regi   | ister and rec | eiving next  | valid byte)  |

| bit 1          | OERR: OV                        | errun Error b                                          | pit            |                |              |               |              |              |

|                |                                 | n error (can                                           | be cleared b   | by clearing b  | oit CREN)    |               |              |              |

|                | 0 = No ove                      |                                                        |                |                |              |               |              |              |

| bit 0          |                                 | bit of Receiv                                          |                |                |              |               | <b>C</b>     | _            |

|                | I his can be                    | e address/da                                           | ata bit or a p | arity bit and  | must be cal  | culated by u  | ser tirmware | 9.           |

|                | Legend:                         |                                                        |                |                |              |               |              |              |

|                | R = Reada                       | ble bit                                                | W = W          | /ritable bit   | U = Unin     | nplemented    | bit, read as | ʻ0'          |

|                | -n = Value                      |                                                        | '1' = B        | it is set      |              | s cleared     | x = Bit is u |              |

|                |                                 |                                                        | i – D          |                |              |               |              |              |

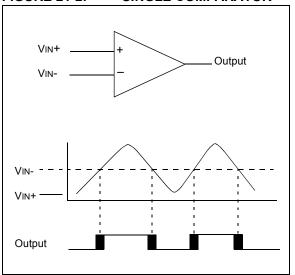

### 21.2 Comparator Operation

A single comparator is shown in Figure 21-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 21-2 represent the uncertainty, due to input offsets and response time.

#### 21.3 Comparator Reference

Depending on the comparator operating mode, either an external or internal voltage reference may be used. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 21-2).

FIGURE 21-2: SINGLE COMPARATOR

#### 21.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSS and VDD and can be applied to either pin of the comparator(s).

#### 21.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference from the comparator voltage reference module. This module is described in more detail in **Section 22.0 "Comparator Voltage Reference Module"**.

The internal reference is only available in the mode where four inputs are multiplexed to two comparators (CM<2:0> = 110). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

### 21.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (see Section 27.0 "Electrical Characteristics").

#### 21.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RA4 and RA5 I/O pins. When enabled, multiplexors in the output path of the RA4 and RA5 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 21-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA4 and RA5 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<5:4>).

- Note 1: When reading the Port register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- Analog levels on any pin defined as a digital input may cause the input buffer to consume more current than is specified.

NOTES:

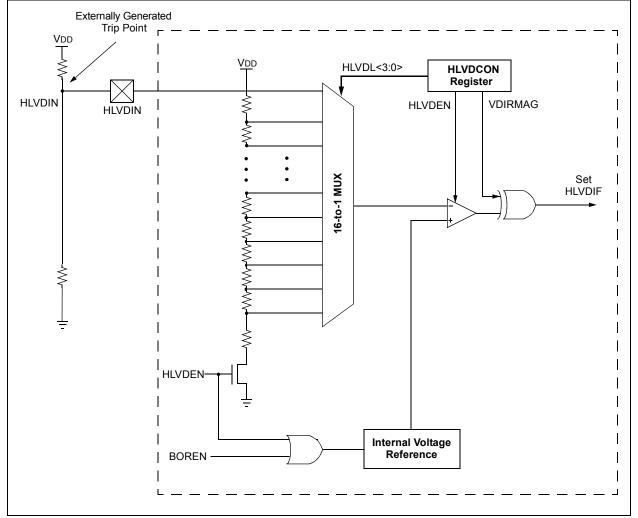

### 23.1 Operation

When the HLVD module is enabled, a comparator uses an internally generated reference voltage as the set point. The set point is compared with the trip point, where each node in the resistor divider represents a trip point voltage. The "trip point" voltage is the voltage level at which the device detects a high or low-voltage event, depending on the configuration of the module. When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal by setting the HLVDIF bit. The trip point voltage is software programmable to any one of 16 values. The trip point is selected by programming the HLVDL<3:0> bits (HLVDCON<3:0>).

The HLVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits HLVDL<3:0> are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, HLVDIN. This gives users flexibility because it allows them to configure the High/Low-Voltage Detect interrupt to occur at any voltage in the valid operating range.

### 23.2 HLVD Setup

The following steps are needed to set up the HLVD module:

- 1. Disable the module by clearing the HLVDEN bit (HLVDCON<4>).

- 2. Write the value to the HLVDL<3:0> bits that selects the desired HLVD trip point.

- Set the VDIRMAG bit to detect high voltage (VDIRMAG = 1) or low voltage (VDIRMAG = 0).

- 4. Enable the HLVD module by setting the HLVDEN bit.

- 5. Clear the HLVD interrupt flag (PIR2<2>), which may have been set from a previous interrupt.

- Enable the HLVD interrupt if interrupts are desired by setting the HLVDIE and GIE bits (PIE<2> and INTCON<7>). An interrupt will not be generated until the IRVST bit is set.

#### 23.3 Current Consumption

When the module is enabled, the HLVD comparator and voltage divider are enabled and will consume static current. The total current consumption, when enabled, is specified in electrical specification parameter D022B. Depending on the application, the HLVD module does not need to be operating constantly. To decrease the current requirements, the HLVD circuitry may only need to be enabled for short periods where the voltage is checked. After doing the check, the HLVD module may be disabled.

#### 23.4 HLVD Start-up Time

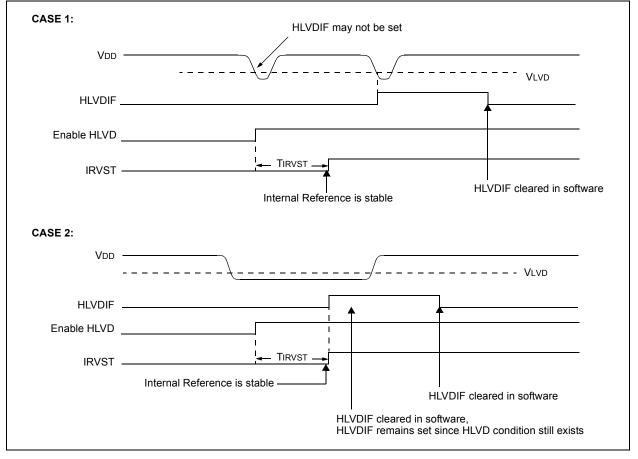

The internal reference voltage of the HLVD module, specified in electrical specification parameter D420, may be used by other internal circuitry, such as the Programmable Brown-out Reset. If the HLVD or other circuits using the voltage reference are disabled to lower the device's current consumption, the reference voltage circuit will require time to become stable before a low or high-voltage condition can be reliably detected. This start-up time, TIRVST, is an interval that is independent of device clock speed. It is specified in electrical specification parameter 36.

The HLVD interrupt flag is not enabled until TIRVST has expired and a stable reference voltage is reached. For this reason, brief excursions beyond the set point may not be detected during this interval. Refer to Figure 23-2 or Figure 23-3.

| ADDWFC                                                                        | ADD W and Carry bit to f                                                                                                                                                                                                               | ANDLW                                                     | AND Literal with W                                                                 |  |  |  |  |  |

|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                                       | ADDWFC f {,d {,a}}                                                                                                                                                                                                                     | Syntax:                                                   | ANDLW k                                                                            |  |  |  |  |  |

| Operands:                                                                     | $0 \leq f \leq 255$                                                                                                                                                                                                                    | Operands:                                                 | $0 \le k \le 255$                                                                  |  |  |  |  |  |

|                                                                               | $d \in [0, 1]$                                                                                                                                                                                                                         | Operation:                                                | (W) .AND. $k \rightarrow W$                                                        |  |  |  |  |  |

| Operation                                                                     | $\mathbf{a} \in [0, 1]$                                                                                                                                                                                                                | Status Affected:                                          | N, Z                                                                               |  |  |  |  |  |

| Operation:                                                                    | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                                                                                     | Encoding:                                                 | 0000 1011 kkkk kkkk                                                                |  |  |  |  |  |

| Status Affected:<br>Encoding:                                                 | N,OV, C, DC, Z                                                                                                                                                                                                                         | Description:                                              | The contents of W are ANDed with the 8-bit literal 'k'. The result is placed in W. |  |  |  |  |  |

| Description:                                                                  | Add W, the Carry flag and data memory                                                                                                                                                                                                  | Words:                                                    | 1                                                                                  |  |  |  |  |  |

|                                                                               | location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is                                                                                                                                                | Cycles:                                                   | 1                                                                                  |  |  |  |  |  |

|                                                                               | placed in data memory location 'f'.                                                                                                                                                                                                    | Q Cycle Activity:                                         |                                                                                    |  |  |  |  |  |

|                                                                               | If 'a' is '0', the Access Bank is selected.                                                                                                                                                                                            | Q1                                                        | Q2 Q3 Q4                                                                           |  |  |  |  |  |

|                                                                               | If 'a' is '1', the BSR is used to select the GPR bank (default).<br>If 'a' is '0' and the extended instruction                                                                                                                         |                                                           | Read literal     Process     Write to W       'k'     Data                         |  |  |  |  |  |

|                                                                               | set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. | <u>Example:</u><br>Before Instruc<br>W<br>After Instructi | = A3h                                                                              |  |  |  |  |  |

| Words:                                                                        | 1                                                                                                                                                                                                                                      | W                                                         | = 03h                                                                              |  |  |  |  |  |

| Cycles:                                                                       | 1                                                                                                                                                                                                                                      |                                                           |                                                                                    |  |  |  |  |  |

| Q Cycle Activity:                                                             |                                                                                                                                                                                                                                        |                                                           |                                                                                    |  |  |  |  |  |

| Q1                                                                            | Q2 Q3 Q4                                                                                                                                                                                                                               |                                                           |                                                                                    |  |  |  |  |  |

| Decode                                                                        | Read<br>register 'f'ProcessWrite to<br>destination                                                                                                                                                                                     |                                                           |                                                                                    |  |  |  |  |  |

| Example:                                                                      | ADDWFC REG, 0, 1                                                                                                                                                                                                                       |                                                           |                                                                                    |  |  |  |  |  |

| Before Instru<br>Carry b<br>REG<br>W<br>After Instruct<br>Carry b<br>REG<br>W | it = 1<br>= 02h<br>= 4Dh                                                                                                                                                                                                               |                                                           |                                                                                    |  |  |  |  |  |

| BRA   | L .                                    | Unconditional Branch                                                  |                     |                              |                                 |                      |                          |  |  |

|-------|----------------------------------------|-----------------------------------------------------------------------|---------------------|------------------------------|---------------------------------|----------------------|--------------------------|--|--|

| Synta | ax:                                    | BRA n                                                                 |                     |                              |                                 |                      |                          |  |  |

| Oper  | ands:                                  | -1024 ≤ n ≤                                                           | 10                  | 23                           |                                 |                      |                          |  |  |

| Oper  | ation:                                 | (PC) + 2 +                                                            | 2n                  | $\rightarrow$ PC             |                                 |                      |                          |  |  |

| Statu | s Affected:                            | None                                                                  |                     |                              |                                 |                      |                          |  |  |

| Enco  | ding:                                  | 1101                                                                  | C                   | nnn                          | nnnr                            | L                    | nnnn                     |  |  |

| Desc  | ription:                               | Add the 2's<br>the PC. Sir<br>incremente<br>the new ad<br>instruction | nce<br>ed to<br>dre | the PC<br>o fetch<br>ss will | will hav<br>the next<br>be PC + | /e<br>t ins<br>· 2 · | struction,<br>+ 2n. This |  |  |

| Word  | ls:                                    | 1                                                                     |                     |                              |                                 |                      |                          |  |  |

| Cycle | es:                                    | 2                                                                     |                     |                              |                                 |                      |                          |  |  |

| QC    | ycle Activity:                         |                                                                       |                     |                              |                                 |                      |                          |  |  |

|       | Q1                                     | Q2                                                                    |                     | C                            | 23                              |                      | Q4                       |  |  |

|       | Decode                                 | Read liter<br>'n'                                                     | al                  |                              | cess<br>ata                     |                      | Write to<br>PC           |  |  |

|       | No<br>operation                        | No<br>operatio                                                        | n                   |                              | lo<br>ation                     | 0                    | No<br>peration           |  |  |

| Exam  | <u>nple:</u>                           | HERE                                                                  |                     | BRA                          | Jump                            |                      |                          |  |  |

|       | Before Instru<br>PC<br>After Instructi | =                                                                     | ad                  | dress                        | (HERE)                          |                      |                          |  |  |

|       | PC                                     | =                                                                     | ad                  | dress                        | (Jump)                          |                      |                          |  |  |

| BSF                                                   | Bit Set f                                                                                                                                                                            |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                               | BSF f, b {                                                                                                                                                                           | อโ                                                                                                                                     |                                                                                                 |                                                                                      |  |  |  |  |

| Operands:                                             | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0, 1]$                                                                                                                               | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \end{array}$                                                                    |                                                                                                 |                                                                                      |  |  |  |  |

| Operation:                                            | $1 \rightarrow f < b >$                                                                                                                                                              |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

| Status Affected:                                      | None                                                                                                                                                                                 |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

| Encoding:                                             | 1000                                                                                                                                                                                 | bbba                                                                                                                                   | ffff                                                                                            | ffff                                                                                 |  |  |  |  |

| Description:                                          | Bit 'b' in reg<br>If 'a' is '0', ti<br>If 'a' is '1', ti<br>GPR bank of<br>If 'a' is '0' a<br>set is enabl<br>in Indexed I<br>mode when<br>Section 25<br>Bit-Oriente<br>Literal Offs | he Access<br>he BSR is<br>(default).<br>nd the ext<br>ed, this in<br>Literal Off<br>ever $f \leq 9$<br><b>.2.3 "Byt</b><br>of Instruct | s Bank i<br>s used to<br>tended i<br>sstructio<br>(set Add<br>(5 (5Fh))<br>e-Orien<br>ctions in | o select the<br>nstruction<br>n operates<br>ressing<br>. See<br>ted and<br>n Indexed |  |  |  |  |

| Words:                                                | 1                                                                                                                                                                                    |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

| Cycles:                                               | 1                                                                                                                                                                                    |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

| Q Cycle Activity:                                     |                                                                                                                                                                                      |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

| Q1                                                    | Q2                                                                                                                                                                                   | Q3                                                                                                                                     |                                                                                                 | Q4                                                                                   |  |  |  |  |

| Decode                                                | Read register 'f'                                                                                                                                                                    | Proces<br>Data                                                                                                                         |                                                                                                 | Write<br>egister 'f'                                                                 |  |  |  |  |

| Example: BSF FLAG_REG, 7, 1<br>Before Instruction     |                                                                                                                                                                                      |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

| FLAG_REG = 0Ah<br>After Instruction<br>FLAG_REG = 8Ah |                                                                                                                                                                                      |                                                                                                                                        |                                                                                                 |                                                                                      |  |  |  |  |

| LFS         | R                          | Load FSF                                                            | र              |                            |                                      | мс  | <b>VF</b>                                                                    | Move f                   |                                                                                                                                                                                                                                   |                 |  |

|-------------|----------------------------|---------------------------------------------------------------------|----------------|----------------------------|--------------------------------------|-----|------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| Synta       | ax:                        | LFSR f, k                                                           |                |                            |                                      | Syr | ntax:                                                                        | MOVF f{                  | ,d {,a}}                                                                                                                                                                                                                          |                 |  |

| Oper        | ands:                      | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 409 \end{array}$ | 95             |                            |                                      | Ope | erands:                                                                      | 0 ≤ f ≤ 255<br>d ∈ [0,1] |                                                                                                                                                                                                                                   |                 |  |

| Oper        | ation:                     | $k \to FSRf$                                                        |                |                            |                                      |     |                                                                              | <b>a</b> ∈[0,1]          |                                                                                                                                                                                                                                   |                 |  |

| Statu       | s Affected:                | None                                                                |                |                            |                                      | Ope | eration:                                                                     | $f \to dest$             |                                                                                                                                                                                                                                   |                 |  |