Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4221-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.6.4 PLL IN INTOSC MODES

The 4x Phase Locked Loop (PLL) can be used with the internal oscillator block to produce faster device clock speeds than are normally possible with the internal oscillator sources. When enabled, the PLL produces a clock speed of 16 MHz or 32 MHz.

Unlike HSPLL mode, the PLL is controlled through software. The control bit, PLLEN (OSCTUNE<6>), is used to enable or disable its operation. If PLL is enabled and a Two-Speed Start-up from wake is performed, execution is delayed until the PLL starts.

The PLL is available when the device is configured to use the internal oscillator block as its primary clock source (FOSC<3:0> = 1001 or 1000). Additionally, the PLL will only function when the selected output frequency is either 4 MHz or 8 MHz (OSCCON<6:4> = 111or 110). If both of these conditions are not met, the PLL is disabled and the PLLEN bit remains clear (writes are ignored).

#### 3.6.5 INTOSC FREQUENCY DRIFT

The factory calibrates the internal oscillator block output (INTOSC) for 8 MHz. However, this frequency may drift as VDD or temperature changes and can affect the controller operation in a variety of ways. It is possible to adjust the INTOSC frequency by modifying the value in the OSCTUNE register. This has no effect on the INTRC clock source frequency.

Tuning the INTOSC source requires knowing when to make the adjustment, in which direction it should be made and in some cases, how large a change is needed. Three compensation techniques are discussed in Section 3.6.5.1 "Compensating with the EUSART", Section 3.6.5.2 "Compensating with the Timers" and Section 3.6.5.3 "Compensating with the CCP Module in Capture Mode" but other techniques may be used.

| REGISTER 3-1: | OSCTUNE: OSCILLATOR TUNING REGISTER |

|---------------|-------------------------------------|

| KEGIJIEK J-I. | USCIONE. USCILLATOR TOMING REDISTER |

|         | 0001014                          |                                                |                 |               |              |               |                                         |        |

|---------|----------------------------------|------------------------------------------------|-----------------|---------------|--------------|---------------|-----------------------------------------|--------|

|         | R/W-0                            | R/W-0                                          | U-0             | R/W-0         | R/W-0        | R/W-0         | R/W-0                                   | R/W-0  |

|         | INTSRC                           | PLLEN <sup>(1)</sup>                           | _               | TUN4          | TUN3         | TUN2          | TUN1                                    | TUN0   |

|         | bit 7                            |                                                |                 |               |              |               |                                         | bit 0  |

| bit 7   | 1 = <b>31.25</b>                 | nternal Oscil<br>kHz device o<br>z device cloo | clock derive    | d from 8 MH   | z INTOSC s   | ource (divid  | •                                       | abled) |

| bit 6   |                                  | equency Mu<br>nabled for IN<br>sabled          | -               |               |              | )             |                                         |        |

|         | Note 1:                          | Available o<br>and reads a                     | •               |               | •            |               | e, this bit is<br>e <b>s</b> " for deta |        |

| bit 5   | Unimplem                         | ented: Read                                    | <b>d as</b> '0' |               |              |               |                                         |        |

| bit 4-0 | TUN<4:0>:                        | : Frequency                                    | Tuning bits     |               |              |               |                                         |        |

|         | 01111 <b>= M</b>                 | laximum free                                   | quency          |               |              |               |                                         |        |

|         | •                                | •                                              |                 |               |              |               |                                         |        |

|         | •                                | •                                              |                 |               |              |               |                                         |        |

|         | 00001<br>00000 = C<br>11111<br>• | enter freque                                   | ncy. Oscilla    | tor module is | s running at | the calibrate | ed frequency                            | Į.     |

|         | 10000 <b>= M</b>                 | linimum freq                                   | uency           |               |              |               |                                         |        |

|         |                                  |                                                |                 |               |              |               |                                         |        |

|         | Logondy                          |                                                |                 |               |              |               |                                         |        |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 6.1.2.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

#### 6.1.3 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers, to provide a "fast return" option for interrupts. The stack for each register is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the Stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 6-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

#### EXAMPLE 6-1: FAST REGISTER STACK CODE EXAMPLE

| CALL | SUB1, FAST<br>•        | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|------|------------------------|---------------------------------------------------------|

| SUB1 | •<br>•<br>RETURN, FAS: | F ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK      |

### 6.1.4 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 6.1.4.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 6-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 6-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVE  | OFFSET, | W |

|-------|-------|---------|---|

|       | CALL  | TABLE   |   |

| ORG   | nn00h |         |   |

| TABLE | ADDWF | PCL     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       |       |         |   |

|       | •     |         |   |

|       | •     |         |   |

|       |       |         |   |

#### 6.1.4.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 7.1 "Table Reads and Table Writes".

| File Name | Bit 7                                                                                                                                                                                                      | Bit 6                 | Bit 5           | Bit 4         | Bit 3          | Bit 2          | Bit 1            | Bit 0                                 | Value on<br>POR, BOR | Details or<br>page: |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|---------------|----------------|----------------|------------------|---------------------------------------|----------------------|---------------------|

| TOSU      | _                                                                                                                                                                                                          | _                     | _               | Top-of-Stack  | Upper Byte (T  | OS<20:16>)     |                  |                                       | 0 0000               | 55, 60              |

| TOSH      | Top-of-Stack High Byte (TOS<15:8>)                                                                                                                                                                         |                       |                 |               |                |                |                  |                                       | 0000 0000            | 55, 60              |

| TOSL      | Top-of-Stack                                                                                                                                                                                               | Low Byte (TO          | S<7:0>)         |               |                |                |                  |                                       | 0000 0000            | 55, 60              |

| STKPTR    | STKFUL <sup>(6)</sup>                                                                                                                                                                                      | STKUNF <sup>(6)</sup> | _               | SP4           | SP3            | SP2            | SP1              | SP0                                   | 00-0 0000            | 55, 61              |

| PCLATU    | _                                                                                                                                                                                                          | _                     | Holding Regi    | ster for PC<2 | 1:16>          |                |                  |                                       | 00 0000              | 55, 60              |

| PCLATH    | Holding Register for PC<15:8>                                                                                                                                                                              |                       |                 |               |                |                |                  |                                       | 0000 0000            | 55, 60              |

| PCL       | PC Low Byte                                                                                                                                                                                                | (PC<7:0>)             |                 |               |                |                |                  |                                       | 0000 0000            | 55, 60              |

| TBLPTRU   | _                                                                                                                                                                                                          | _                     | bit 21          | Program Mei   | mory Table Poi | inter Upper By | te (TBLPTR<20    | ):16>)                                | 00 0000              | 55, 82              |

| TBLPTRH   | Program Mer                                                                                                                                                                                                | nory Table Poi        | inter High Byte | e (TBLPTR<1   | 5:8>)          |                |                  |                                       | 0000 0000            | 55, 82              |

| TBLPTRL   | Program Men                                                                                                                                                                                                | nory Table Poi        | inter Low Byte  | (TBLPTR<7:0   | 0>)            |                |                  |                                       | 0000 0000            | 55, 82              |

| TABLAT    | Program Men                                                                                                                                                                                                | nory Table Lat        | ch              |               |                |                |                  |                                       | 0000 0000            | 55, 82              |

| PRODH     | Product Regi                                                                                                                                                                                               | ster High Byte        |                 |               |                |                |                  |                                       | XXXX XXXX            | 55, 95              |

| PRODL     | Product Regi                                                                                                                                                                                               | ster Low Byte         |                 |               |                |                |                  |                                       | XXXX XXXX            | 55, 95              |

| INTCON    | GIE/GIEH                                                                                                                                                                                                   | PEIE/GIEL             | TMR0IE          | INTOIE        | RBIE           | TMR0IF         | <b>INT0IF</b>    | RBIF                                  | 0000 000x            | 55, 99              |

| INTCON2   | RBPU                                                                                                                                                                                                       | INTEDG0               | INTEDG1         | INTEDG2       | _              | TMR0IP         | _                | RBIP                                  | 1111 -1-1            | 55, 100             |

| INTCON3   | INT2IP                                                                                                                                                                                                     | INT1IP                | _               | INT2IE        | INT1IE         | _              | INT2IF           | INT1IF                                | 11-0 0-00            | 55, 101             |

| INDF0     |                                                                                                                                                                                                            | s of FSR0 to a        | uddress data n  |               |                | changed (not a | a physical regis |                                       | N/A                  | 55, 74              |

| POSTINCO  |                                                                                                                                                                                                            |                       |                 | -             |                |                |                  | · · · · · · · · · · · · · · · · · · · | N/A                  | 55, 74              |

| POSTDEC0  |                                                                                                                                                                                                            |                       |                 |               |                |                |                  |                                       | N/A                  | 55, 74              |

| PREINC0   | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register)                                                                                                     |                       |                 |               |                |                |                  |                                       | N/A                  | 55, 74              |

| PLUSW0    | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register) – value of FSR0 offset by W                                                                         |                       |                 |               |                |                |                  |                                       | N/A                  | 55, 74              |

| FSR0H     | _                                                                                                                                                                                                          | _                     | _               | _             | Indirect Data  | Memory Addre   | ess Pointer 0 H  | igh Byte                              | 0000                 | 55, 74              |

| FSR0L     | Indirect Data                                                                                                                                                                                              | Memory Addr           | ess Pointer 0   | Low Byte      |                |                |                  |                                       | XXXX XXXX            | 55, 74              |

| WREG      | Working Regi                                                                                                                                                                                               | ster                  |                 |               |                |                |                  |                                       | XXXX XXXX            | 55                  |

| INDF1     |                                                                                                                                                                                                            |                       | ddress data n   | nemory – valu | e of FSR1 not  | changed (not   | a physical regis | ter)                                  | N/A                  | 55, 74              |

| POSTINC1  | Uses content                                                                                                                                                                                               | s of FSR1 to a        | ddress data n   | nemory – valu | e of FSR1 pos  | t-incremented  | (not a physical  | register)                             | N/A                  | 55, 74              |

| POSTDEC1  |                                                                                                                                                                                                            |                       |                 |               |                |                | I (not a physica |                                       | N/A                  | 55, 74              |

| PREINC1   |                                                                                                                                                                                                            |                       |                 | -             |                |                | not a physical r |                                       | N/A                  | 55, 74              |

| PLUSW1    |                                                                                                                                                                                                            | s of FSR1 to a        |                 | -             |                |                | not a physical r |                                       | N/A                  | 55, 74              |

| FSR1H     | _                                                                                                                                                                                                          | _                     | _               | _             | Indirect Data  | Memory Addre   | ess Pointer 1 H  | igh Byte                              | 0000                 | 56, 74              |

| FSR1L     | Indirect Data                                                                                                                                                                                              | Memory Addr           | ess Pointer 1   | Low Byte      |                |                |                  |                                       | XXXX XXXX            | 56, 74              |

| BSR       | _                                                                                                                                                                                                          | _                     | _               | _             | Bank Select I  | Register       |                  |                                       | 0000                 | 56, 65              |

| INDF2     | Uses content                                                                                                                                                                                               | s of FSR2 to a        | ddress data n   | nemory – valu | 1              | <u> </u>       | a physical regis | ter)                                  | N/A                  | 56, 74              |

| POSTINC2  | Uses contents of FSR2 to address data memory – value of FSR2 not changed (not a physical register) Uses contents of FSR2 to address data memory – value of FSR2 post-incremented (not a physical register) |                       |                 |               |                |                |                  | ,                                     | N/A                  | 56, 74              |

| POSTDEC2  | Uses content                                                                                                                                                                                               | s of FSR2 to a        | address data n  | nemory – valu | e of FSR2 pos  | t-decremented  | I (not a physica | l register)                           | N/A                  | 56, 74              |

| PREINC2   |                                                                                                                                                                                                            |                       |                 |               |                |                | not a physical r |                                       | N/A                  | 56, 74              |

| PLUSW2    |                                                                                                                                                                                                            | s of FSR2 to a        |                 |               |                |                | not a physical r |                                       | N/A                  | 56, 74              |

| FSR2H     | _                                                                                                                                                                                                          | _                     | _               | _             | Indirect Data  | Memory Addre   | ess Pointer 2 H  | igh Byte                              | 0000                 | 56, 74              |

| FSR2L     | Indirect Data                                                                                                                                                                                              | Memory Addr           | ess Pointer 2   | Low Byte      |                | , .            |                  |                                       | XXXX XXXX            | 56, 74              |

|           |                                                                                                                                                                                                            |                       |                 | -             |                |                |                  |                                       |                      | ,                   |

#### **TABLE 6-2**: **REGISTER FILE SUMMARY (PIC18F2221/2321/4221/4321)**

Note

The SBOREN bit is only available when the BOREN<1:0> Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)". 1:

2: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in 3: INTOSC Modes".

4: The RE3 bit is only available when Master Clear Reset is disabled (MCLRE Configuration bit = 0); otherwise, RE3 reads as '0'. This bit is read-only.

RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. 5: When disabled, these bits read as '0'.

6: Bit 7 and bit 6 are cleared by user software or by a POR.

#### 9.0 8 x 8 HARDWARE MULTIPLIER

#### 9.1 Introduction

All PIC18 devices include an 8 x 8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 9-1.

#### 9.2 Operation

Example 9-1 shows the instruction sequence for an 8 x 8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 9-2 shows the sequence to do an 8 x 8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 9-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, W | ;                |

|-------|---------|------------------|

| MULWF | ARG2    | ; ARG1 * ARG2 -> |

|       |         | ; PRODH:PRODL    |

|       |         |                  |

### EXAMPLE 9-2: 8 x 8 SIGNED MULTIPLY

|      |         |     | 111 | JOINE          |

|------|---------|-----|-----|----------------|

| MOVF | ARG1,   | W   |     |                |

| MULW | F ARG2  |     | ;   | ARG1 * ARG2 -> |

|      |         |     | ;   | PRODH:PRODL    |

| BTFS | C ARG2, | SB  | ;   | Test Sign Bit  |

| SUBW | F PRODH | , F | ;   | PRODH = PRODH  |

|      |         |     | ;   | - ARG1         |

| MOVF | ARG2,   | W   |     |                |

| BTFS | C ARG1, | SB  | ;   | Test Sign Bit  |

| SUBW | F PRODH | , F | ;   | PRODH = PRODH  |

|      |         |     | ;   | - ARG2         |

|      |         |     |     |                |

|                  |                           | Program           | Cycles | Time     |          |         |  |

|------------------|---------------------------|-------------------|--------|----------|----------|---------|--|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |

|                  | Without hardware multiply | 13                | 69     | 6.9 μs   | 27.6 μs  | 69 μs   |  |

| 8 x 8 unsigned   | Hardware multiply         | 1                 | 1      | 100 ns   | 400 ns   | 1 μs    |  |

| 8 x 8 signed     | Without hardware multiply | 33                | 91     | 9.1 μs   | 36.4 μs  | 91 μs   |  |

|                  | Hardware multiply         | 6                 | 6      | 600 ns   | 2.4 μs   | 6 μs    |  |

| 16 x 16 uppigned | Without hardware multiply | 21                | 242    | 24.2 μs  | 96.8 μs  | 242 μs  |  |

| 16 x 16 unsigned | Hardware multiply         | 28                | 28     | 2.8 μs   | 11.2 μs  | 28 μs   |  |

| 16 v 16 signad   | Without hardware multiply | 52                | 254    | 25.4 μs  | 102.6 μs | 254 μs  |  |

| 16 x 16 signed   | Hardware multiply         | 35                | 40     | 4.0 μs   | 16.0 μs  | 40 μs   |  |

#### TABLE 9-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

| INTCON3:                 | INTERRU                      | PICONII         | ROL REGI    | SIER 3       |              |        |        |

|--------------------------|------------------------------|-----------------|-------------|--------------|--------------|--------|--------|

| R/W-1                    | R/W-1                        | U-0             | R/W-0       | R/W-0        | U-0          | R/W-0  | R/W-0  |

| INT2IP                   | INT1IP                       | —               | INT2IE      | INT1IE       | —            | INT2IF | INT1IF |

| bit 7                    |                              |                 |             |              |              |        | bit 0  |

| INT2IP: IN               | T2 External                  | nterrupt Pri    | ority bit   |              |              |        |        |

| 1 = High p<br>0 = Low pr | •                            |                 |             |              |              |        |        |

| INT1IP: IN               | T1 External                  | nterrupt Pri    | ority bit   |              |              |        |        |

| 1 = High p<br>0 = Low pr |                              |                 |             |              |              |        |        |

| Unimplem                 | ented: Read                  | <b>l as</b> '0' |             |              |              |        |        |

| INT2IE: IN               | T2 External                  | nterrupt En     | able bit    |              |              |        |        |

|                          | es the INT2 e                |                 | •           |              |              |        |        |

|                          | es the INT2                  |                 | •           |              |              |        |        |

|                          | T1 External                  | •               |             |              |              |        |        |

|                          | es the INT1 e<br>es the INT1 |                 | •           |              |              |        |        |

| Unimplem                 | ented: Read                  | <b>l as</b> '0' |             |              |              |        |        |

| INT2IF: IN               | T2 External I                | nterrupt Fla    | ıg bit      |              |              |        |        |

|                          | IT2 external                 | •               | •           | t be cleared | in software) | )      |        |

| 0 = The IN               | IT2 external                 | interrupt dic   | d not occur |              |              |        |        |

|                          | T1 External I                | •               | •           |              |              |        |        |

|                          | IT1 external                 |                 | · ·         | t be cleared | in software) | )      |        |

| 0 = 1  ne IN             | IT1 external                 | interrupt aic   | not occur   |              |              |        |        |

#### REGISTER 10-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### 15.2 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 15-2). When the RD16 control bit (T3CON<7>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

#### 15.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in Section 13.0 "Timer1 Module".

#### 15.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE (PIE2<1>).

#### 15.5 Resetting Timer3 Using the CCP Special Event Trigger

If either of the CCP modules is configured to use Timer3 and to generate a Special Event Trigger in Compare mode (CCP1M<3:0> or CCP2M<3:0> = 1011), this signal will reset Timer3. It will also start an A/D conversion if the A/D module is enabled (see **Section 16.3.4** "**Special Event Trigger**" for more information).

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPR2H:CCPR2L register pair effectively becomes a period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from a CCP module, the write will take precedence.

Note: The Special Event Triggers from the CCP2 module will not set the TMR3IF interrupt flag bit (PIR2<1>).

| Name   | Bit 7      | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|------------|---------------|---------|---------|---------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH   | PEIE/GIEL     | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR2   | OSCFIF     | CMIF          | _       | EEIF    | BCLIF   | HLVDIF | TMR3IF | CCP2IF | 58                         |

| PIE2   | OSCFIE     | CMIE          | _       | EEIE    | BCLIE   | HLVDIE | TMR3IE | CCP2IE | 58                         |

| IPR2   | OSCFIP     | CMIP          | _       | EEIP    | BCLIP   | HLVDIP | TMR3IP | CCP2IP | 58                         |

| TMR3L  | Timer3 Reg | gister Low B  | yte     |         |         |        |        |        | 57                         |

| TMR3H  | Timer3 Reg | gister High B | yte     |         |         |        |        |        | 57                         |

| T1CON  | RD16       | T1RUN         | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 56                         |

| T3CON  | RD16       | T3CCP2        | T3CKPS1 | T3CKPS0 | T3CCP1  | T3SYNC | TMR3CS | TMR3ON | 57                         |

TABLE 15-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

| Name    | Bit 7                         | Bit 6                 | Bit 5        | Bit 4     | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|-------------------------------|-----------------------|--------------|-----------|---------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                      | PEIE/GIEL             | TMR0IE       | INT0IE    | RBIE    | TMR0IF | INT0IF | RBIF   | 55                         |

| RCON    | IPEN                          | SBOREN <sup>(1)</sup> | _            | RI        | TO      | PD     | POR    | BOR    | 54                         |

| PIR1    | PSPIF <sup>(2)</sup>          | ADIF                  | RCIF         | TXIF      | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1    | PSPIE <sup>(2)</sup>          | ADIE                  | RCIE         | TXIE      | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1    | PSPIP <sup>(2)</sup>          | ADIP                  | RCIP         | TXIP      | SSPIP   | CCP1IP | TMR2IP | TMR1IP | 58                         |

| PIR2    | OSCFIF                        | CMIF                  | —            | EEIF      | BCLIF   | HLVDIF | TMR3IF | CCP2IF | 58                         |

| PIE2    | OSCFIE                        | CMIE                  | _            | EEIE      | BCLIE   | HLVDIE | TMR3IE | CCP2IE | 58                         |

| IPR2    | OSCFIP                        | CMIP                  | —            | EEIP      | BCLIP   | HLVDIP | TMR3IP | CCP2IP | 58                         |

| TRISB   | PORTB Data Direction Register |                       |              |           |         |        |        |        | 58                         |

| TRISC   | PORTC Data Direction Register |                       |              |           |         |        |        |        | 58                         |

| TMR1L   | Timer1 Reg                    | gister Low By         | /te          |           |         |        |        |        | 56                         |

| TMR1H   | Timer1 Reg                    | gister High B         | yte          |           |         |        |        |        | 56                         |

| T1CON   | RD16                          | T1RUN                 | T1CKPS1      | T1CKPS0   | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 56                         |

| TMR3H   | Timer3 Reg                    | gister High B         | yte          |           |         |        |        |        | 57                         |

| TMR3L   | Timer3 Reg                    | gister Low B          | /te          |           |         |        |        |        | 57                         |

| T3CON   | RD16                          | T3CCP2                | T3CKPS1      | T3CKPS0   | T3CCP1  | T3SYNC | TMR3CS | TMR3ON | 57                         |

| CCPR1L  | Capture/Co                    | mpare/PWN             | 1 Register 1 | Low Byte  |         |        |        |        | 57                         |

| CCPR1H  | Capture/Co                    | mpare/PWN             | 1 Register 1 | High Byte |         |        |        |        | 57                         |

| CCP1CON | P1M1 <sup>(2)</sup>           | P1M0 <sup>(2)</sup>   | DC1B1        | DC1B0     | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0 | 57                         |

| CCPR2L  | Capture/Co                    | mpare/PWN             | 1 Register 2 | Low Byte  |         |        |        |        | 57                         |

| CCPR2H  | Capture/Co                    | mpare/PWN             | 1 Register 2 | High Byte |         |        |        |        | 57                         |

| CCP2CON | _                             | _                     | DC2B1        | DC2B0     | CCP2M3  | CCP2M2 | CCP2M1 | CCP2M0 | 57                         |

| TABLE 16-3: | <b>REGISTERS ASSOCIATED WITH CAPTURE</b> | COMPARE, TIMER1 AND TIMER3 |

|-------------|------------------------------------------|----------------------------|

|             |                                          |                            |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by Capture/Compare, Timer1 or Timer3.

Note 1: The SBOREN bit is only available when the BOREN<1:0> Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

**2:** These bits are unimplemented on 28-pin devices and read as '0'.

#### 17.4.7.1 Auto-Shutdown and Automatic Restart

The auto-shutdown feature can be configured to allow automatic restarts of the module following a shutdown event. This is enabled by setting the PRSEN bit of the ECCP1DEL register (ECCP1DEL<7>).

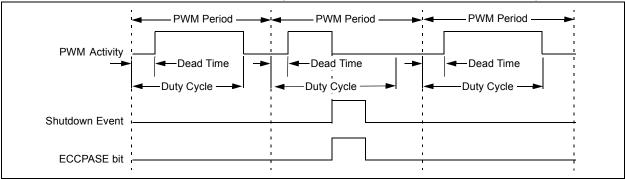

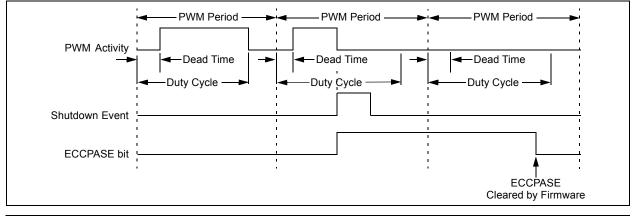

In Shutdown mode with PRSEN = 1 (Figure 17-10), the ECCPASE bit will remain set for as long as the cause of the shutdown continues. When the shutdown condition clears, the ECCP1ASE bit is cleared. If PRSEN = 0 (Figure 17-11), once a shutdown condition occurs, the ECCPASE bit will remain set until it is cleared by firmware. Once ECCPASE is cleared, the Enhanced PWM will resume at the beginning of the next PWM period.

| Note: | Writing to the ECCPASE bit is disabled |

|-------|----------------------------------------|

|       | while a shutdown condition is active.  |

Independent of the PRSEN bit setting, if the autoshutdown source is one of the comparators, the shutdown condition is a level. The ECCPASE bit cannot be cleared as long as the cause of the shutdown persists.

The Auto-Shutdown mode can be forced by writing a '1' to the ECCPASE bit.

#### 17.4.8 START-UP CONSIDERATIONS

When the ECCP module is used in the PWM mode, the application hardware must use the proper external pullup and/or pull-down resistors on the PWM output pins. When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the OFF state until the microcontroller drives the I/O pins with the proper signal levels, or activates the PWM output(s).

The CCP1M<1:0> bits (CCP1CON<1:0>) allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pins are configured as outputs. Changing the polarity configuration while the PWM pins are configured as outputs is not recommended, since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pins for output at the same time as the ECCP module may cause damage to the application circuit. The ECCP module must be enabled in the proper output mode and complete a full PWM cycle before configuring the PWM pins as outputs. The completion of a full PWM cycle is indicated by the TMR2IF bit being set as the second PWM period begins.

#### FIGURE 17-10: PWM AUTO-SHUTDOWN (PRSEN = 1, AUTO-RESTART ENABLED)

#### FIGURE 17-11: PWM AUTO-SHUTDOWN (PRSEN = 0, AUTO-RESTART DISABLED)

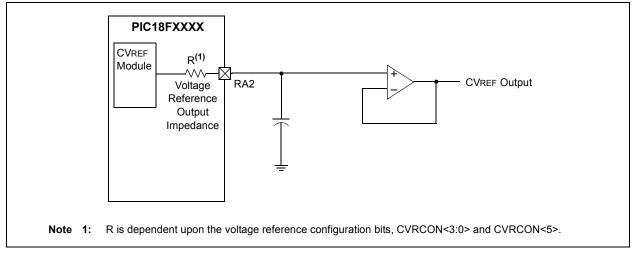

#### FIGURE 22-2: COMPARATOR VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 22-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7                 | Bit 6                 | Bit 5   | Bit 4                                | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on page |

|--------|-----------------------|-----------------------|---------|--------------------------------------|-------|-------|-------|-------|----------------------------|

| CVRCON | CVREN                 | CVROE                 | CVRR    | CVRSS                                | CVR3  | CVR2  | CVR1  | CVR0  | 57                         |

| CMCON  | C2OUT                 | C10UT                 | C2INV   | C1INV                                | CIS   | CM2   | CM1   | CM0   | 57                         |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA D | ORTA Data Direction Control Register |       |       |       |       | 58                         |

Legend: Shaded cells are not used with the comparator voltage reference.

Note 1: PORTA pins are enabled based on oscillator configuration.

| REGISTER 24-2: | CONFIG                                                                                                                                | 2L: CONF                   | IGURATI          | ON REGIS                  | TER 2 LOV            | V (BYTE AD            | DRESS 300       | 002h)                 |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------|---------------------------|----------------------|-----------------------|-----------------|-----------------------|

|                | U-0                                                                                                                                   | U-0                        | U-0              | R/P-1                     | R/P-1                | R/P-1                 | R/P-1           | R/P-1                 |

|                | _                                                                                                                                     | _                          | _                | BORV1 <sup>(1)</sup>      | BORV0 <sup>(1)</sup> | BOREN1 <sup>(2)</sup> | BOREN0(2)       | PWRTEN <sup>(2)</sup> |

|                | bit 7                                                                                                                                 |                            |                  |                           |                      |                       |                 | bit 0                 |

| bit 7-5        | Unimplem                                                                                                                              | nented: Re                 | <b>ad as</b> '0' |                           |                      |                       |                 |                       |

| bit 4-3        | BORV<1:0                                                                                                                              | 0>: Brown-                 | out Reset        | Voltage bits <sup>(</sup> | 1)                   |                       |                 |                       |

|                | 11 <b>= Minin</b>                                                                                                                     | num setting                | J                |                           |                      |                       |                 |                       |

|                | •                                                                                                                                     |                            |                  |                           |                      |                       |                 |                       |

|                | •                                                                                                                                     |                            |                  |                           |                      |                       |                 |                       |

|                | 00 <b>= Maxi</b> i                                                                                                                    | mum settin                 | g                |                           |                      |                       |                 |                       |

| bit 2-1        | BOREN<1                                                                                                                               | I: <b>0&gt;:</b> Browr     | n-out Rese       | t Enable bits             | ;(2)                 |                       |                 |                       |

|                |                                                                                                                                       |                            |                  |                           | •                    | REN is disable        | ,               |                       |

|                |                                                                                                                                       |                            |                  | in hardware               | only and dis         | sabled in Slee        | ep mode         |                       |

|                |                                                                                                                                       | OREN is dis<br>/n-out Rese |                  | and controlle             | ed by softwa         | are (SBOREN           | is enabled)     |                       |

|                |                                                                                                                                       |                            |                  | in hardware               | •                    | •                     | ,               |                       |

| bit 0          | PWRTEN:                                                                                                                               | Power-up                   | Timer Ena        | able bit <sup>(2)</sup>   |                      |                       |                 |                       |

|                | 1 = PWRT                                                                                                                              |                            |                  |                           |                      |                       |                 |                       |

|                | 0 <b>= PWRT</b>                                                                                                                       |                            |                  |                           |                      |                       |                 |                       |

|                | Note 1:                                                                                                                               | See Sect                   | ion 27.1 '       | 'DC Charac                | teristics" fo        | or the specific       | ations.         |                       |

|                | <ol> <li>The Power-up Timer is decoupled from Brown-out Reset, allowing these features to<br/>be independently controlled.</li> </ol> |                            |                  |                           |                      |                       |                 |                       |

|                | Legend:                                                                                                                               |                            |                  |                           |                      |                       |                 |                       |

|                | R = Reada                                                                                                                             | able bit                   | P = Pr           | ogrammable                | ebit U=l             | Jnimplemente          | ed bit, read as | s 'O'                 |

| <b>.</b>                               | •                                   |

|----------------------------------------|-------------------------------------|

| -n = Value when device is unprogrammed | u = Unchanged from programmed state |

### 24.5 Program Verification and Code Protection

The overall structure of the code protection on the PIC18 Flash devices differs significantly from other  $\text{PIC}^{\texttt{R}}$  devices.

The user program memory is divided into three blocks. One of these is a boot block of variable size. The remainder of the memory is divided into two blocks on binary boundaries. Each of the three blocks has three code protection bits associated with them. They are:

- Code-Protect bit (CPn)

- Write-Protect bit (WRTn)

- External Block Table Read bit (EBTRn)

Figure 24-5 shows the program memory organization for 4 and 8-Kbyte devices and the specific code protection bit associated with each block. The actual locations of the bits are summarized in Table 24-3.

#### FIGURE 24-5: CODE-PROTECTED PROGRAM MEMORY FOR PIC18F2221/2321/4221/4321 FAMILY DEVICES

|                     | MEMORY SIZE/DEVICE              |                         |                                 |                         |                               | Block Code Protection<br>Controlled By: |  |

|---------------------|---------------------------------|-------------------------|---------------------------------|-------------------------|-------------------------------|-----------------------------------------|--|

|                     | 8 Kbytes<br>(PIC18FX321)        |                         |                                 | oytes<br>FX221)         |                               |                                         |  |

|                     |                                 | BBSIZ<1:0>              |                                 |                         | -                             |                                         |  |

| 11/10               | 01                              | 00                      | 11/10/01                        | 00                      |                               |                                         |  |

|                     | Boot Block                      | Boot Block<br>256 words | Boot Block                      | Boot Block<br>256 words | 000000h<br>0001FFh            | CPB, WRTB, EBTRB                        |  |

| Boot Block          | 512 words                       |                         | 512 words                       | 512 words               |                               |                                         |  |

| 1K word             |                                 | -                       | Block 0<br>0.5K words           | Block 0<br>0.75K words  | 0003FFh<br>000400h            |                                         |  |

|                     |                                 |                         |                                 |                         | 0007FFh                       | CP0, WRT0, EBTR0                        |  |

| Block 0<br>1K word  | Block 0<br>1.5K words           | Block 0<br>1.75K words  | Block 1<br>1K word              | Block 1<br>1K word      | 000800h<br>000FFFh<br>001000h |                                         |  |

| Block 1<br>2K words | Block 1<br>2K words             | Block 1<br>2K words     | Unimplemented<br>Reads all '0's |                         |                               | CP1, WRT1, EBTR1                        |  |

|                     | Unimplemented<br>Reads all '0's |                         |                                 |                         | 001FFFh<br>002000h<br>1FFFFFh | (Unimplemented Memory<br>Space)         |  |

| GOT         | ю                        | Uncondit                                | ional Brar                                                                 | ch             |                                        | INCF             |                                                | Incremer                                                                                  | nt f                                                                  |                                                                       |                                                |

|-------------|--------------------------|-----------------------------------------|----------------------------------------------------------------------------|----------------|----------------------------------------|------------------|------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------|

| Synta       | ax:                      | GOTO k                                  |                                                                            |                |                                        | Synta            | x:                                             | INCF f{,                                                                                  | d {,a}}                                                               |                                                                       |                                                |

| Oper        | ands:                    | $0 \le k \le 104$                       | 8575                                                                       |                |                                        | Opera            | inds:                                          | $0 \le f \le 255$                                                                         |                                                                       |                                                                       |                                                |

| Oper        | ation:                   | $k \rightarrow PC<20$                   | ):1>                                                                       |                |                                        |                  |                                                | $d \in [0, 1]$                                                                            |                                                                       |                                                                       |                                                |

| Statu       | s Affected:              | None                                    |                                                                            |                |                                        | Opera            | tion:                                          | $a \in [0, 1]$                                                                            | (f) + 1 $\rightarrow$ dest                                            |                                                                       |                                                |

|             | ord (k<7:0>)             | 1110                                    |                                                                            | ,kkk           | kkkk <sub>0</sub>                      | Status           | Affected:                                      | $(1) \downarrow \downarrow \downarrow \downarrow 0$ $C, DC, N,$                           |                                                                       |                                                                       |                                                |

| 2nd ۱       | word(k<19:8>)            | 1111                                    | k <sub>19</sub> kkk k                                                      | kkk            | kkkk <sub>8</sub>                      | Encod            | ling:                                          | 0010                                                                                      | 10da                                                                  | ffff                                                                  | ffff                                           |

| Desc        | ription:                 | anywhere v<br>2-Mbyte m<br>value 'k' is | vs an uncon<br>within entire<br>emory range<br>loaded into<br>ways a two-r | . The<br>PC<20 | 20-bit                                 | Descr            | iption:                                        | The conter<br>incremente<br>placed in V<br>placed bac<br>If 'a' is '0',<br>If 'a' is '1', | ed. If 'd' is<br>V. If 'd' is<br>k in regis<br>the Acces<br>the BSR i | 6 '0', the r<br>'1', the re<br>ter 'f' (de<br>ss Bank is<br>s used to | esult is<br>esult is<br>fault).<br>s selected. |

| Word        | ls:                      | 2                                       |                                                                            |                |                                        |                  |                                                | GPR bank<br>If 'a' is '0' a                                                               | · ,                                                                   |                                                                       | nstruction                                     |

| Cycle       | es:                      | 2                                       |                                                                            |                |                                        |                  |                                                | set is enab                                                                               | oled, this i                                                          | nstructio                                                             | n operates                                     |

| QC          | ycle Activity:           |                                         |                                                                            |                |                                        |                  |                                                | in Indexed<br>mode whe                                                                    |                                                                       |                                                                       |                                                |

|             | Q1                       | Q2                                      | Q3                                                                         |                | Q4                                     |                  |                                                | Section 2                                                                                 |                                                                       | · · ·                                                                 |                                                |

|             | Decode                   | Read literal<br>'k'<7:0>,               | No<br>operation                                                            | ʻk             | ead literal<br>c'<19:8>,<br>rite to PC |                  |                                                | Bit-Orient<br>Literal Off                                                                 |                                                                       |                                                                       |                                                |

|             | No                       | No                                      | No                                                                         | vv             | No                                     | Words            | 8:                                             | 1                                                                                         |                                                                       |                                                                       |                                                |

|             | operation                | operation                               | operation                                                                  | 0              | peration                               | Cycle            | s:                                             | 1                                                                                         |                                                                       |                                                                       |                                                |

|             |                          |                                         |                                                                            |                |                                        | Q Cy             | cle Activity:                                  |                                                                                           |                                                                       |                                                                       |                                                |

| <u>Exan</u> | nple:                    | GOTO THE                                | RE                                                                         |                |                                        | -                | Q1                                             | Q2                                                                                        | Q3                                                                    |                                                                       | Q4                                             |

|             | After Instructio<br>PC = | n<br>Address (T                         | HERE)                                                                      |                |                                        |                  | Decode                                         | Read<br>register 'f'                                                                      | Proce<br>Data                                                         |                                                                       | Write to estination                            |

|             |                          |                                         |                                                                            |                |                                        | <u>Exam</u><br>E | <u>ple:</u><br>Before Instruc<br>CNT<br>Z<br>C | INCF<br>etion<br>= FFh<br>= 0<br>= ?                                                      | CNT,                                                                  | 1, 0                                                                  |                                                |

|             |                          |                                         |                                                                            |                |                                        |                  | DC<br>After Instructi                          | = ?                                                                                       |                                                                       |                                                                       |                                                |

After Instruction

=

= = = 1 1 1

00h

CNT Z C DC

| MOVFF                                                | Move f to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | o f              |   |    |  |  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---|----|--|--|--|

| Syntax:                                              | MOVFF f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | s,f <sub>d</sub> |   |    |  |  |  |

| Operands:                                            | $\begin{array}{l} 0 \leq f_s \leq 40 \\ 0 \leq f_d \leq 40 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |   |    |  |  |  |