Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

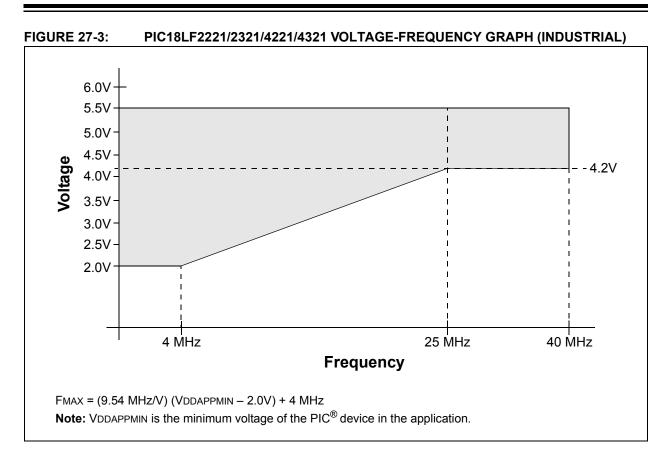

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4221t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

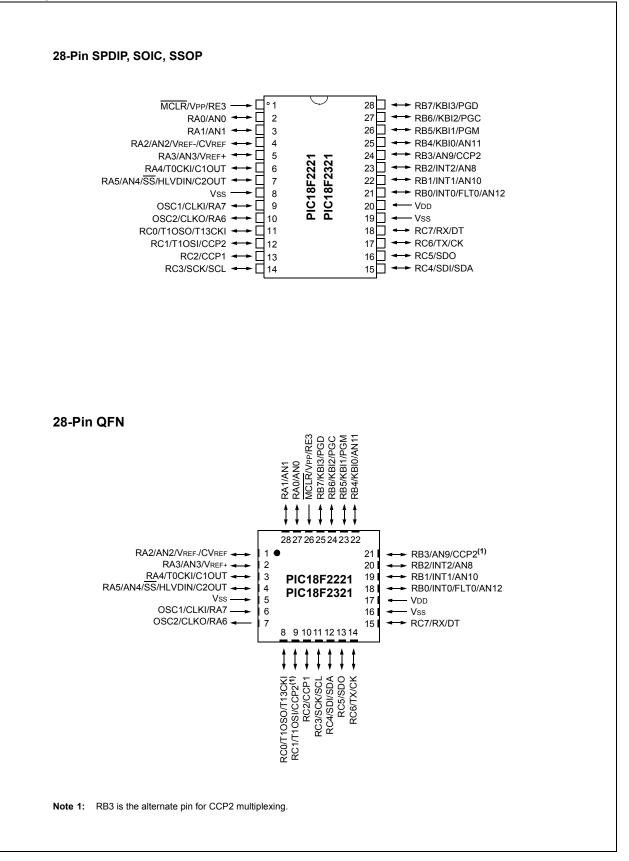

#### **Pin Diagrams**

### 6.1.1 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU register are performed through the PCLATH register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 6.1.4.1 "Computed GOTO"**).

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

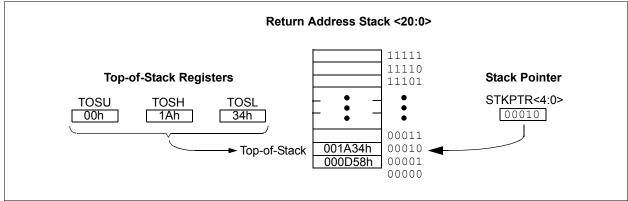

### 6.1.2 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack Special Function Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack; the Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack; the contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full or has overflowed or has underflowed.

### 6.1.2.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 6-2). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

# FIGURE 6-2: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

### 6.3.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy the top half of Bank 15 (F80h to FFFh). A list of these registers is given in Table 6-1 and Table 6-2. The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The reset and interrupt registers are described in their respective chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of a peripheral feature are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's.

# TABLE 6-1: SPECIAL FUNCTION REGISTER MAP FOR PIC18F2221/2321/4221/4321 FAMILY DEVICES

| Address | Name                    | Address | Name                    | Address | Name                    | Address | Name                 |

|---------|-------------------------|---------|-------------------------|---------|-------------------------|---------|----------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | CCPR1H                  | F9Fh    | IPR1                 |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | CCPR1L                  | F9Eh    | PIR1                 |

| FFDh    | TOSL                    | FDDh    | POSTDEC2 <sup>(1)</sup> | FBDh    | CCP1CON                 | F9Dh    | PIE1                 |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | CCPR2H                  | F9Ch    | (2)                  |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | CCPR2L                  | F9Bh    | OSCTUNE              |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | CCP2CON                 | F9Ah    | (2)                  |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | (2)                     | F99h    | (2)                  |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | BAUDCON                 | F98h    | (2)                  |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | ECCP1DEL <sup>(3)</sup> | F97h    | (2)                  |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | ECCP1AS <sup>(3)</sup>  | F96h    | TRISE <sup>(3)</sup> |

| FF5h    | TABLAT                  | FD5h    | T0CON                   | FB5h    | CVRCON                  | F95h    | TRISD <sup>(3)</sup> |

| FF4h    | PRODH                   | FD4h    | (2)                     | FB4h    | CMCON                   | F94h    | TRISC                |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | TMR3H                   | F93h    | TRISB                |

| FF2h    | INTCON                  | FD2h    | HLVDCON                 | FB2h    | TMR3L                   | F92h    | TRISA                |

| FF1h    | INTCON2                 | FD1h    | WDTCON                  | FB1h    | T3CON                   | F91h    | (2)                  |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRGH                  | F90h    | (2)                  |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | SPBRG                   | F8Fh    | (2)                  |

| FEEh    | POSTINC0 <sup>(1)</sup> | FCEh    | TMR1L                   | FAEh    | RCREG                   | F8Eh    | (2)                  |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXREG                   | F8Dh    | LATE <sup>(3)</sup>  |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2                    | FACh    | TXSTA                   | F8Ch    | LATD <sup>(3)</sup>  |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2                     | FABh    | RCSTA                   | F8Bh    | LATC                 |

| FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | (2)                     | F8Ah    | LATB                 |

| FE9h    | FSR0L                   | FC9h    | SSPBUF                  | FA9h    | EEADR                   | F89h    | LATA                 |

| FE8h    | WREG                    | FC8h    | SSPADD                  | FA8h    | EEDATA                  | F88h    | (2)                  |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | SSPSTAT                 | FA7h    | EECON2 <sup>(1)</sup>   | F87h    | (2)                  |

| FE6h    | POSTINC1 <sup>(1)</sup> | FC6h    | SSPCON1                 | FA6h    | EECON1                  | F86h    | (2)                  |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | SSPCON2                 | FA5h    | (2)                     | F85h    | (2)                  |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                  | FA4h    | (2)                     | F84h    | PORTE                |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                  | FA3h    | (2)                     | F83h    | PORTD <sup>(3)</sup> |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2                    | F82h    | PORTC                |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2                    | F81h    | PORTB                |

| FE0h    | BSR                     | FC0h    | ADCON2                  | FA0h    | PIE2                    | F80h    | PORTA                |

Note 1: This is not a physical register.

**2:** Unimplemented registers are read as '0'.

3: This register is not available on 28-pin devices.

| R/V        |                  | R/W-0                          | U-0                    | R/W-0                       | EST (FLAG<br>R/W-0           | R/W-0         | R/W-0         | R/W-0       |

|------------|------------------|--------------------------------|------------------------|-----------------------------|------------------------------|---------------|---------------|-------------|

| 050        |                  | CMIF                           | <u> </u>               | EEIF                        | BCLIF                        | HLVDIF        | TMR3IF        | CCP2IF      |

| bit 7      |                  |                                |                        |                             | DOLI                         |               |               | bit 0       |

|            |                  | scillator Fail                 | •                      | •                           |                              |               |               |             |

|            |                  | oscillator fa<br>clock opera   |                        | nput has cha                | anged to INT                 | OSC (must     | be cleared i  | n software) |

|            |                  | parator Inte                   |                        |                             |                              |               |               |             |

|            |                  | rator input h<br>rator input h |                        |                             | leared in sof                | tware)        |               |             |

| Unim       | pleme            | ented: Read                    | <b>l as</b> '0'        |                             |                              |               |               |             |

| EEIF:      | Data             | EEPROM/F                       | lash Write (           | Operation In                | terrupt Flag                 | bit           |               |             |

|            |                  |                                |                        |                             | leared in so<br>not been sta |               |               |             |

| BCLI       | F: Bus           | Collision In                   | iterrupt Flag          | bit                         |                              |               |               |             |

|            |                  | collision occ                  |                        | be cleared i                | n software)                  |               |               |             |

| HLVC       | IF: Hi           | gh/Low-Volt                    | age Detect             | Interrupt Fla               | g bit                        |               |               |             |

|            |                  | low-voltage<br>CON<7>)         | condition of           | ccurred; dire               | ction determ                 | nined by VD   | IRMAG bit     |             |

|            | •                | •                              |                        | as not occur                | red                          |               |               |             |

|            |                  | MR3 Overflo                    | •                      | •                           |                              |               |               |             |

|            |                  | register over<br>register did  |                        |                             | d in software                | e)            |               |             |

| CCP2       | 2 <b>IF</b> : C0 | CP2 Interrup                   | ot Flag bit            |                             |                              |               |               |             |

| 1 = A      |                  |                                |                        |                             | e cleared in                 | software)     |               |             |

| 1 = A      |                  | 1 register co                  |                        | ch occurred<br>atch occurre | (must be cle                 | eared in soft | ware)         |             |

| <u>PWM</u> | mode             | •                              | ·                      |                             |                              |               |               |             |

| Lege       |                  | ble bit                        | $\Delta A = \Delta A $ | itable bit                  |                              | plemented I   | pit read as " | <b>`</b>    |

'1' = Bit is set

'0' = Bit is cleared

# REGISTER 10-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

-n = Value at POR

x = Bit is unknown

|       | R/W-0                     | R/W-0         | U-0               | R/W-0        | R/W-0           | R/W-0       | R/W-0         | R/W-0  |

|-------|---------------------------|---------------|-------------------|--------------|-----------------|-------------|---------------|--------|

|       | OSCFIE                    | CMIE          | _                 | EEIE         | BCLIE           | HLVDIE      | TMR3IE        | CCP2IE |

|       | bit 7                     |               |                   |              |                 |             |               | bit 0  |

|       |                           |               |                   |              |                 |             |               |        |

| bit 7 | OSCFIE: O                 | scillator Fa  | il Interrupt E    | nable bit    |                 |             |               |        |

|       | 1 = Enable<br>0 = Disable |               |                   |              |                 |             |               |        |

| bit 6 | CMIE: Com                 | nparator Inte | errupt Enable     | e bit        |                 |             |               |        |

|       | 1 = Enable<br>0 = Disable |               |                   |              |                 |             |               |        |

| bit 5 | Unimplem                  | ented: Rea    | <b>d as</b> '0'   |              |                 |             |               |        |

| bit 4 | EEIE: Data                | EEPROM/       | Flash Write       | Operation Ir | terrupt Enal    | ble bit     |               |        |

|       | 1 = Enable<br>0 = Disable |               |                   |              |                 |             |               |        |

| bit 3 |                           |               | nterrupt Ena      | bla bit      |                 |             |               |        |

| DIL 3 | 1 = Enable                |               | niterrupt Ena     |              |                 |             |               |        |

|       | 0 = Disable               |               |                   |              |                 |             |               |        |

| bit 2 | HLVDIE: H                 | igh/Low-Vo    | ltage Detect      | Interrupt Er | able bit        |             |               |        |

|       | 1 = Enable                |               |                   |              |                 |             |               |        |

|       | 0 = Disable               |               |                   |              |                 |             |               |        |

| bit 1 |                           |               | ow Interrupt      | Enable bit   |                 |             |               |        |

|       | 1 = Enable<br>0 = Disable |               |                   |              |                 |             |               |        |

| bit 0 |                           |               | nt Enchlo hi      | +            |                 |             |               |        |

| DILU  | 1 = Enable                |               | pt Enable bi      | L            |                 |             |               |        |

|       | 0 = Disable               |               |                   |              |                 |             |               |        |

|       | Logondi                   |               |                   |              |                 |             |               | ]      |

|       | Legend:<br>R = Readal     | bla hit       | ۱۸/ <b>–</b> ۱۸/۰ | itable bit   | <b>-</b>    nim | nlomonted b | nit road co " | 0,     |

|       | R = Reada                 |               | vv = vvr          |              | 0 = 0nim        | plemented b | n, reau as t  | J      |

'1' = Bit is set

'0' = Bit is cleared

#### REGISTER 10-7: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

-n = Value at POR

x = Bit is unknown

### 10.5 RCON Register

The RCON register contains flag bits which are used to determine the cause of the last Reset or wake-up from Idle or Sleep modes. RCON also contains the IPEN bit which enables interrupt priorities.

The operation of the SBOREN bit and the Reset flag bits is discussed in more detail in **Section 5.1 "RCON Register**".

### REGISTER 10-10: RCON: RESET CONTROL REGISTER

| R/W-0 | R/W-1 <sup>(1)</sup> | U-0 | R/W-1 | R-1 | R-1 | R/W-0 <sup>(2)</sup> | R/W-0 |

|-------|----------------------|-----|-------|-----|-----|----------------------|-------|

| IPEN  | SBOREN               | _   | RI    | TO  | PD  | POR                  | BOR   |

| bit 7 |                      |     |       |     |     |                      | bit 0 |

|       |                      |     |       |     |     |                      |       |

- bit 7 IPEN: Interrupt Priority Enable bit

- 1 = Enable priority levels on interrupts

- 0 = Disable priority levels on interrupts (PIC16XXX Compatibility mode)

- bit 6 **SBOREN:** Software BOR Enable bit<sup>(1)</sup> For details of bit operation, see Register 5-1.

- bit 5 Unimplemented: Read as '0'

- bit 4 **RI:** RESET Instruction Flag bit For details of bit operation, see Register 5-1.

- bit 3 **TO:** Watchdog Time-out Flag bit For details of bit operation, see Register 5-1.

- bit 2 **PD:** Power-down Detection Flag bit For details of bit operation, see Register 5-1.

- bit 1 **POR:** Power-on Reset Status bit<sup>(2)</sup> For details of bit operation, see Register 5-1.

- bit 0 **BOR:** Brown-out Reset Status bit For details of bit operation, see Register 5-1.

- Note 1: If SBOREN is enabled, its Reset state is '1'; otherwise, it is '0'.

- **2:** Actual Reset values are determined by device configuration and the nature of the device Reset. See Register 5-1 for additional information.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | pit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 12.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

#### 12.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

# 12.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name   | Bit 7                                         | Bit 6              | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on page |

|--------|-----------------------------------------------|--------------------|--------|--------|-------|--------|--------|-------|----------------------------|

| TMR0L  | MR0L Timer0 Register Low Byte                 |                    |        |        |       |        |        |       |                            |

| TMR0H  | Timer0 Reg                                    | ister High By      | /te    |        |       |        |        |       | 56                         |

| INTCON | GIE/GIEH                                      | PEIE/GIEL          | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 55                         |

| TOCON  | TMR0ON T08BIT T0CS T0SE PSA T0PS2 T0PS1 T0PS0 |                    |        |        |       |        |        |       | 56                         |

| TRISA  | RA7 <sup>(1)</sup>                            | RA6 <sup>(1)</sup> | RA5    | RA4    | RA3   | RA2    | RA1    | RA0   | 58                         |

TABLE 12-1:

REGISTERS ASSOCIATED WITH TIMER0

Legend: Shaded cells are not used by Timer0.

**Note 1:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

|         | -          |              |                  | -                | -               | _              | -               | _      | -                          |

|---------|------------|--------------|------------------|------------------|-----------------|----------------|-----------------|--------|----------------------------|

| Name    | Bit 7      | Bit 6        | Bit 5            | Bit 4            | Bit 3           | Bit 2          | Bit 1           | Bit 0  | Reset<br>Values<br>on page |

| INTCON  | GIE/GIEH   | PEIE/GIEL    | TMR0IE           | INT0IE           | RBIE            | TMR0IF         | INT0IF          | RBIF   | 55                         |

| PIR1    | PSPIF      | ADIF         | RCIF             | TXIF             | SSPIF           | CCP1IF         | TMR2IF          | TMR1IF | 58                         |

| PIE1    | PSPIE      | ADIE         | RCIE             | TXIE             | SSPIE           | CCP1IE         | TMR2IE          | TMR1IE | 58                         |

| IPR1    | PSPIP      | ADIP         | RCIP             | TXIP             | SSPIP           | CCP1IP         | TMR2IP          | TMR1IP | 58                         |

| PIR2    | OSCFIF     | CMIF         | _                | EEIF             | BCLIF           | HLVDIF         | TMR3IF          | CCP2IF | 58                         |

| PIE2    | OSCFIE     | CMIE         | _                | EEIE             | BCLIE           | HLVDIE         | TMR3IE          | CCP2IE | 58                         |

| IPR2    | OSCFIP     | CMIP         | _                | EEIP             | BCLIP           | HLVDIP         | TMR3IP          | CCP2IP | 58                         |

| TRISC   | TRISC7     | TRISC6       | TRISC5           | TRISC4           | TRISC3          | TRISC2         | TRISC1          | TRISC0 | 58                         |

| TRISD   | TRISD7     | TRISD6       | TRISD5           | TRISD4           | TRISD3          | TRISD2         | TRISD1          | TRISD0 | 58                         |

| SSPBUF  | MSSP Rec   | eive Buffer/ | Fransmit Re      | gister           |                 |                |                 |        | 56                         |

| SSPADD  | ADD7       | ADD6         | ADD5             | ADD4             | ADD3            | ADD2           | ADD1            | ADD0   | 56                         |

| TMR2    | Timer2 Reg | gister       |                  |                  |                 |                |                 |        | 56                         |

| PR2     | Timer2 Per | iod Register |                  |                  |                 |                |                 |        | 56                         |

| SSPCON1 | WCOL       | SSPOV        | SSPEN            | CKP              | SSPM3           | SSPM2          | SSPM1           | SSPM0  | 56                         |

| SSPCON2 | GCEN       | ACKSTAT      | ACKDT/<br>ADMSK5 | ACKEN/<br>ADMSK5 | RCEN/<br>ADMSK5 | PEN/<br>ADMSK5 | RSEN/<br>ADMSK5 | SEN    | 56                         |

| SSPSTAT | SMP        | CKE          | D/A              | Р                | S               | R/W            | UA              | BF     | 56                         |

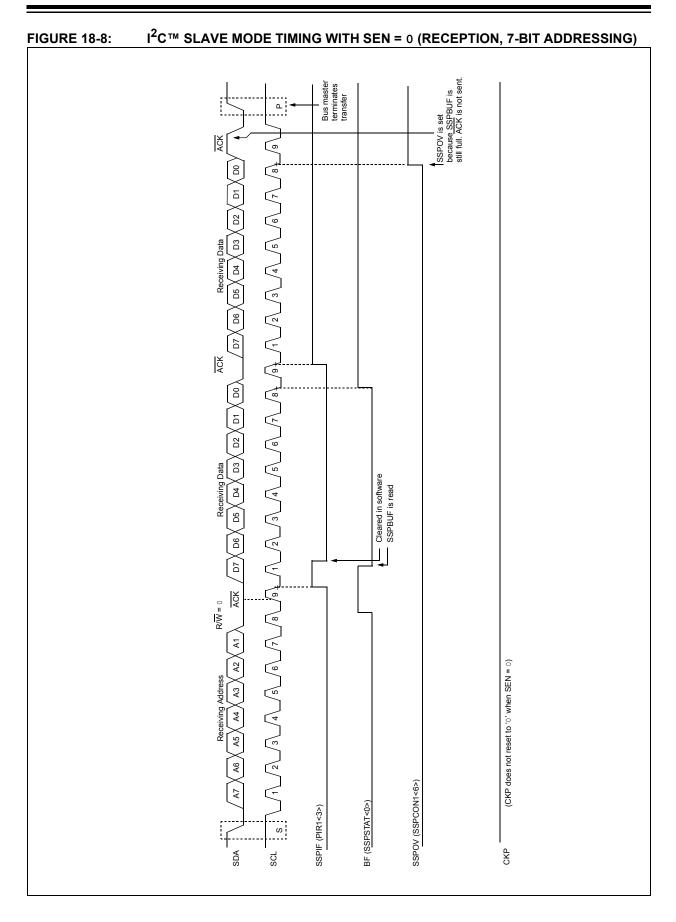

# TABLE 18-4: REGISTERS ASSOCIATED WITH I<sup>2</sup>C<sup>™</sup> OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C$  mode.

|                         |               | ·                     |                                                                                       |                       |

|-------------------------|---------------|-----------------------|---------------------------------------------------------------------------------------|-----------------------|

| BRG Value               | XXXXh         | 0000h                 | <u> </u>                                                                              | 001Ch                 |

| RX pin                  |               | Start                 | -Edge #1 -Edge #2 -Edge #3 Edge #4<br>Bit 0 Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 Bit 7 | – Edge #5<br>Stop Bit |

| BRG Clock               |               |                       |                                                                                       |                       |

| ABDEN bit               | Set by User — | ,<br>,<br>,           |                                                                                       | Auto-Cleared          |

| RCIF bit<br>(Interrupt) |               | 1<br>1<br>1<br>1      |                                                                                       |                       |

| Read<br>RCREG           |               | ,<br>,<br>,<br>,<br>, |                                                                                       |                       |

| SPBRG                   |               | ı                     | xxxxh X                                                                               | 1Ch                   |

| SPBRGH                  |               |                       | XXXXh                                                                                 | 00h                   |

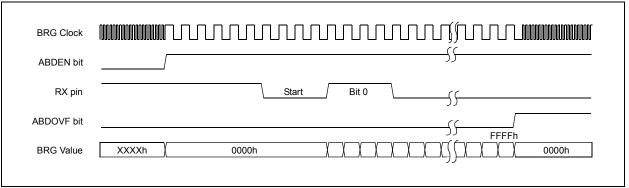

#### FIGURE 19-2: BRG OVERFLOW SEQUENCE

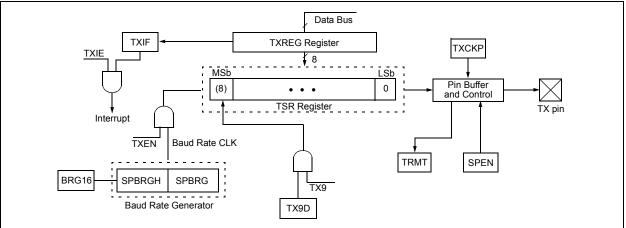

### FIGURE 19-3: EUSART TRANSMIT BLOCK DIAGRAM

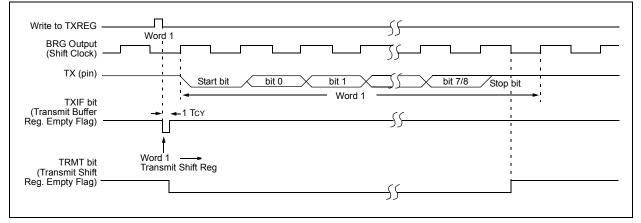

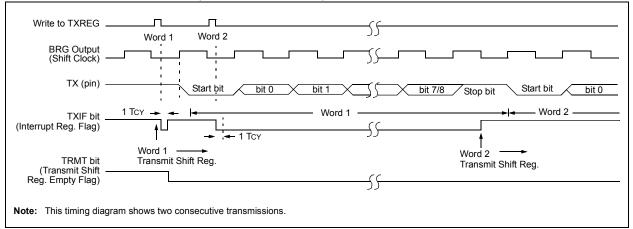

#### FIGURE 19-4: ASYNCHRONOUS TRANSMISSION, TXCKP = 0 (TX NOT INVERTED)

#### FIGURE 19-5: ASYNCHRONOUS TRANSMISSION (BACK TO BACK), TXCKP = 0 (TX NOT INVERTED)

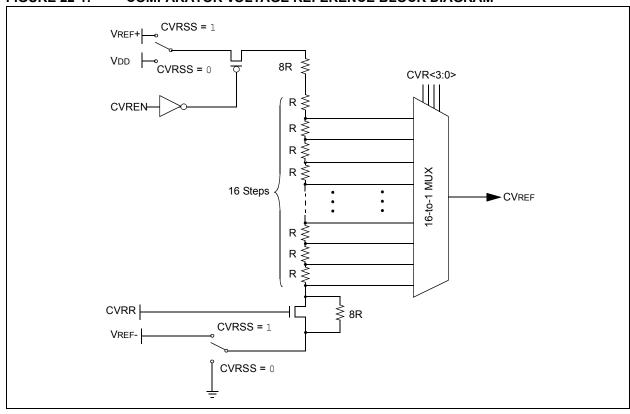

### FIGURE 22-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

# 22.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 22-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in **Section 27.0 "Electrical Characteristics"**.

# 22.3 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

# 22.4 Effects of a Reset

A device Reset disables the voltage reference by clearing bit, CVREN (CVRCON<7>). This Reset also disconnects the reference from the RA2 pin by clearing bit, CVROE (CVRCON<6>) and selects the high-voltage range by clearing bit, CVRR (CVRCON<5>). The CVR value select bits are also cleared.

# 22.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the CVROE bit is set. Enabling the voltage reference output onto RA2 when it is configured as a digital input will increase current consumption. Connecting RA2 as a digital output with CVRSS enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. Figure 22-2 shows an example buffering technique.

| ANDWF                                                   | AND W w                                                                                                                                                                             | ith f                                                                                                                                                                                     |                                                                                                                                                                   | BC                                                          | Branch i                                                                                                                    | f Carry                                                |                                                                     |  |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------|--|

| Syntax:                                                 | ANDWF                                                                                                                                                                               | f {,d {,a}}                                                                                                                                                                               |                                                                                                                                                                   | Syntax:                                                     | BC n                                                                                                                        |                                                        |                                                                     |  |

| Operands:                                               | $0 \le f \le 255$                                                                                                                                                                   |                                                                                                                                                                                           |                                                                                                                                                                   | Operands:                                                   | -128 ≤ n ≤                                                                                                                  | 127                                                    |                                                                     |  |

|                                                         | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                              |                                                                                                                                                                                           |                                                                                                                                                                   | Operation:                                                  |                                                                                                                             | If Carry bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC |                                                                     |  |

| Operation:                                              | (W) .AND. (                                                                                                                                                                         | (f) $\rightarrow$ dest                                                                                                                                                                    |                                                                                                                                                                   | Status Affected                                             | d: None                                                                                                                     |                                                        |                                                                     |  |

| Status Affected:                                        | N, Z                                                                                                                                                                                |                                                                                                                                                                                           |                                                                                                                                                                   | Encoding:                                                   | 1110                                                                                                                        | 0010 nni                                               | nn nnnn                                                             |  |

| Encoding:<br>Description:                               | register 'f. I<br>in W. If 'd' is<br>in register 'f<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode when<br>Section 25 | s '1', the result<br>f' (default).<br>he Access Ba<br>he BSR is use<br>(default).<br>nd the extend<br>ed, this instru-<br>Literal Offset A<br>never $f \le 95$ (5<br><b>.2.3 "Byte-Or</b> | NDed with<br>result is stored<br>is stored back<br>nk is selected.<br>d to select the<br>ed instruction<br>ction operates<br>Addressing<br>Fh). See<br>iented and | Words:<br>Cycles:<br>Q Cycle Activi<br>If Jump:             | If the Carr<br>will branch<br>The 2's cc<br>added to ti<br>increment<br>instruction<br>PC + 2 + 2<br>two-cycle<br>1<br>1(2) | y bit is '1', then                                     | the program<br>ber '2n' is<br>e PC will have<br>next<br>ess will be |  |

|                                                         |                                                                                                                                                                                     | ed Instruction<br>set Mode" for                                                                                                                                                           |                                                                                                                                                                   | Q1                                                          | Q2                                                                                                                          | Q3                                                     | Q4                                                                  |  |

| Words:                                                  | 1                                                                                                                                                                                   |                                                                                                                                                                                           |                                                                                                                                                                   | Decod                                                       | le Read literal<br>'n'                                                                                                      | Process<br>Data                                        | Write to<br>PC                                                      |  |

| Cycles:                                                 | 1                                                                                                                                                                                   |                                                                                                                                                                                           |                                                                                                                                                                   | No                                                          | No                                                                                                                          | No                                                     | No                                                                  |  |

| Q Cycle Activity:                                       | ,                                                                                                                                                                                   |                                                                                                                                                                                           |                                                                                                                                                                   | operatio                                                    |                                                                                                                             | operation                                              | operation                                                           |  |

| Q1                                                      | Q2                                                                                                                                                                                  | Q3                                                                                                                                                                                        | Q4                                                                                                                                                                | If No Jump:                                                 |                                                                                                                             |                                                        |                                                                     |  |

| Decode                                                  | Read                                                                                                                                                                                | Process                                                                                                                                                                                   | Write to                                                                                                                                                          | Q1                                                          | Q2                                                                                                                          | Q3                                                     | Q4                                                                  |  |

|                                                         | register 'f'                                                                                                                                                                        | Data                                                                                                                                                                                      | destination                                                                                                                                                       | Decod                                                       | le Read literal<br>'n'                                                                                                      | Process<br>Data                                        | No<br>operation                                                     |  |

| Example:<br>Before Instru<br>W<br>REG<br>After Instruct | = 17h<br>= C2h                                                                                                                                                                      | REG, 0, 0                                                                                                                                                                                 |                                                                                                                                                                   | <u>Example:</u><br>Before Ins<br>PC<br>After Instr<br>If Ca | = a                                                                                                                         | BC 5                                                   | )                                                                   |  |

| BCF                         | Bit Clear f                                                                                                                                                                                                                                                                                                                                                                                  | BN                                                                                           | Branch if Negative                                                                                                                                                                                                                                                                         |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                     | BCF f, b {,a}                                                                                                                                                                                                                                                                                                                                                                                | Syntax:                                                                                      | BN n                                                                                                                                                                                                                                                                                       |

| Operands:                   | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                            | Operands:                                                                                    | $-128 \le n \le 127$                                                                                                                                                                                                                                                                       |

|                             | 0 ≤ b ≤ 7<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                       | Operation:                                                                                   | If Negative bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                  |

| Operation:                  | $0 \rightarrow f < b >$                                                                                                                                                                                                                                                                                                                                                                      | Status Affected:                                                                             | None                                                                                                                                                                                                                                                                                       |

| Status Affected:            | None                                                                                                                                                                                                                                                                                                                                                                                         | Encoding:                                                                                    | 1110 0110 nnnn nnnn                                                                                                                                                                                                                                                                        |

| Encoding:<br>Description:   | 1001bbbaffffffffBit 'b' in register 'f' is cleared.If 'a' is '0', the Access Bank is selected.If 'a' is '1', the BSR is used to select theGPR bank (default).If 'a' is '0' and the extended instructionset is enabled, this instruction operatesin Indexed Literal Offset Addressingmode whenever $f \le 95$ (5Fh). SeeSection 25.2.3 "Byte-Oriented andBit-Oriented Instructions in Indexed | Description:<br>Words:<br>Cycles:                                                            | If the Negative bit is '1', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |

|                             | Literal Offset Mode" for details.                                                                                                                                                                                                                                                                                                                                                            | Q Cycle Activity:                                                                            | (2)                                                                                                                                                                                                                                                                                        |

| Words:                      | 1                                                                                                                                                                                                                                                                                                                                                                                            | If Jump:                                                                                     |                                                                                                                                                                                                                                                                                            |

| Cycles:                     | 1                                                                                                                                                                                                                                                                                                                                                                                            | Q1                                                                                           | Q2 Q3 Q4                                                                                                                                                                                                                                                                                   |

| Q Cycle Activity:           |                                                                                                                                                                                                                                                                                                                                                                                              | Decode                                                                                       | Read literal Process Write to<br>'n' Data PC                                                                                                                                                                                                                                               |

| Q1<br>Decode                | Q2     Q3     Q4       Read     Process     Write                                                                                                                                                                                                                                                                                                                                            | No<br>operation                                                                              | No No No<br>operation operation                                                                                                                                                                                                                                                            |

|                             | register 'f' Data register 'f'                                                                                                                                                                                                                                                                                                                                                               | If No Jump:                                                                                  |                                                                                                                                                                                                                                                                                            |

| Example:                    | BCF FLAG REG, 7, 0                                                                                                                                                                                                                                                                                                                                                                           | Q1                                                                                           | Q2 Q3 Q4                                                                                                                                                                                                                                                                                   |

| Before Instruct<br>FLAG_RE  | ion                                                                                                                                                                                                                                                                                                                                                                                          | Decode                                                                                       | Read literalProcessNo'n'Dataoperation                                                                                                                                                                                                                                                      |

| After Instructio<br>FLAG_RE | n                                                                                                                                                                                                                                                                                                                                                                                            | Example:<br>Before Instruc<br>PC<br>After Instructic<br>If Negativ<br>Pd<br>If Negativ<br>Pd | = address (HERE)<br>on<br>ve = 1;<br>C = address (Jump)<br>ve = 0;                                                                                                                                                                                                                         |

| CLRF                                                                                                                            | Clear f                                                                   |                 |                       | CLRWDT                                | Clear Wat                                                    | tchdog Time              | ər          |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------|-----------------------|---------------------------------------|--------------------------------------------------------------|--------------------------|-------------|--|--|--|

| Syntax:                                                                                                                         | CLRF f {,a}                                                               |                 | Syntax:               | CLRWDT                                | CLRWDT<br>None                                               |                          |             |  |  |  |

| Operands:                                                                                                                       | $0 \le f \le 255$                                                         |                 |                       | Operands:                             |                                                              |                          |             |  |  |  |

|                                                                                                                                 | <b>a</b> ∈[0,1]                                                           |                 |                       |                                       |                                                              | $000h \rightarrow WDT$ , |             |  |  |  |

| Operation:                                                                                                                      | $\begin{array}{l} 000h \rightarrow f, \\ 1 \rightarrow Z \end{array}$     |                 |                       |                                       | $000h \rightarrow Wl$ $1 \rightarrow TO,$ $1 \rightarrow PD$ | DT postscaler,           |             |  |  |  |

| Status Affected:                                                                                                                | Z                                                                         |                 |                       | Status Affected:                      | $T \rightarrow PD$<br>TO, PD                                 |                          |             |  |  |  |

| Encoding:                                                                                                                       | 0110                                                                      | 101a fff        | ff ffff               |                                       |                                                              |                          | 0.0.0.1.0.0 |  |  |  |

| Description:                                                                                                                    |                                                                           | ontents of the  | specified             | Encoding:                             | 0000                                                         | 0000 00                  |             |  |  |  |

| register.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default). |                                                                           |                 | Description:          | ts the<br>esets the<br>tatus bits, TO |                                                              |                          |             |  |  |  |

|                                                                                                                                 |                                                                           | nd the extende  |                       | Words:                                | 1                                                            |                          |             |  |  |  |

|                                                                                                                                 |                                                                           | iteral Offset A | tion operates         | Cycles:                               | 1                                                            |                          |             |  |  |  |

|                                                                                                                                 |                                                                           | ever f ≤ 95 (5F | 0                     | Q Cycle Activity                      |                                                              |                          |             |  |  |  |

|                                                                                                                                 |                                                                           | 2.3 "Byte-Ori   |                       | Q1                                    | Q2                                                           | Q3                       | Q4          |  |  |  |

|                                                                                                                                 | Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                 |                       | Decode                                | No                                                           | Process                  | No          |  |  |  |

| Words:                                                                                                                          | 1                                                                         |                 |                       |                                       | operation                                                    | Data                     | operation   |  |  |  |

| Cycles:                                                                                                                         | 1                                                                         |                 |                       | Example:                              | CLRWDT                                                       |                          |             |  |  |  |

| Q Cycle Activity:                                                                                                               |                                                                           |                 |                       | Before Inst                           |                                                              |                          |             |  |  |  |

| Q1                                                                                                                              | Q2                                                                        | Q3              | Q4                    |                                       | Counter =                                                    | ?                        |             |  |  |  |

| Decode                                                                                                                          | Read<br>register 'f'                                                      | Process<br>Data | Write<br>register 'f' |                                       | ction<br>Counter =<br>Postscaler =                           | 00h<br>0                 |             |  |  |  |

| Example:                                                                                                                        | CLRF                                                                      | FLAG_REG,       | 1                     | TO<br>PD                              | =                                                            | 1<br>1                   |             |  |  |  |

| Before Instru<br>FLAG_F<br>After Instruct<br>FLAG_F                                                                             | REG = 5Ah                                                                 |                 |                       |                                       |                                                              |                          |             |  |  |  |

| COMF                    | COMF Complement f                                                           |                                 |                 | CPFSEQ              | Compare f with W, Skip if f = W |                                     |                                    |  |

|-------------------------|-----------------------------------------------------------------------------|---------------------------------|-----------------|---------------------|---------------------------------|-------------------------------------|------------------------------------|--|

| Syntax:                 | COMF f {,d {,a}}                                                            |                                 | Syntax:         | CPFSEQ f {,a}       |                                 |                                     |                                    |  |

| Operands:               | $0 \le f \le 255$                                                           |                                 | Operands:       | $0 \leq f \leq 255$ |                                 |                                     |                                    |  |

|                         | $d \in [0,1]$                                                               |                                 |                 |                     | <b>a</b> ∈[0,1]                 |                                     |                                    |  |

|                         | <b>a</b> ∈[0,1]                                                             |                                 |                 | Operation:          | (f) - (W),                      | (14/)                               |                                    |  |

| Operation:              | $(\overline{f}) \rightarrow dest$                                           |                                 |                 |                     | skip if (f) = (unsigned of      | (vv)<br>comparison)                 |                                    |  |

| Status Affected:        | N, Z                                                                        |                                 |                 | Status Affected:    | None                            | ompanoon)                           |                                    |  |

| Encoding:               | 0001                                                                        | 11da ff                         | ff ffff         | Encoding:           | 0110 001a ffff ffff             |                                     |                                    |  |

| Description:            | The contents of register 'f' are complemented. If 'd' is '0', the result is |                                 |                 | Description:        | Compares                        | the contents of                     | f data memory                      |  |

|                         |                                                                             | /. If 'd' is '1', th            |                 |                     |                                 | o the contents                      |                                    |  |

|                         |                                                                             | ( in register 'f'               |                 |                     |                                 | an unsigned s<br>en the fetched     |                                    |  |

|                         | lf 'a' is '0', t                                                            | he Access Ba                    | nk is selected. |                     |                                 | and a NOP is e                      |                                    |  |

|                         | -                                                                           |                                 | d to select the |                     | instead, ma                     | king this a two                     | o-cycle                            |  |

|                         | GPR bank                                                                    | (default).<br>Ind the extend    | ed instruction  |                     | instruction.                    |                                     |                                    |  |

|                         |                                                                             |                                 | ction operates  |                     | ,                               |                                     | nk is selected.<br>d to select the |  |

|                         | in Indexed                                                                  | Literal Offset /                | Addressing      |                     | GPR bank                        |                                     |                                    |  |

|                         |                                                                             | never f ≤ 95 (5                 |                 |                     |                                 | nd the extend                       | ed instruction                     |  |

|                         |                                                                             | .2.3 "Byte-Or<br>ed Instruction |                 |                     |                                 | ed, this instruc                    | •                                  |  |

|                         |                                                                             | set Mode" for                   |                 |                     |                                 | Literal Offset A<br>never f ≤ 95 (5 | -                                  |  |

| Words:                  | 1                                                                           |                                 |                 |                     |                                 | .2.3 "Byte-Or                       | ,                                  |  |

| Cycles:                 | 1                                                                           |                                 |                 |                     |                                 | ed Instruction<br>set Mode" for     |                                    |  |

| Q Cycle Activity:       |                                                                             |                                 |                 | Words:              | 1                               |                                     | uelans.                            |  |

| Q1                      | Q2                                                                          | Q3                              | Q4              | Cycles:             | 1(2)                            |                                     |                                    |  |