Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

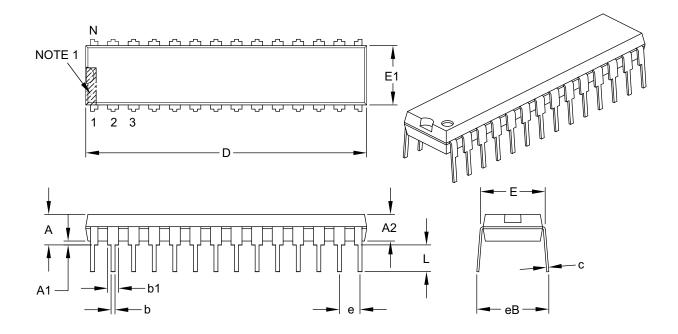

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2321-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18F MICROCONTROLLERS

# 2.1 Basic Connection Requirements

Getting started with the PIC18F2221/2321/4221/4321 family family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin

(see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.4 "ICSP Pins"**)

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for analog modules is implemented

| Note: | The AVDD and AVSS pins must always be   |

|-------|-----------------------------------------|

|       | connected, regardless of whether any of |

|       | the analog modules are being used.      |

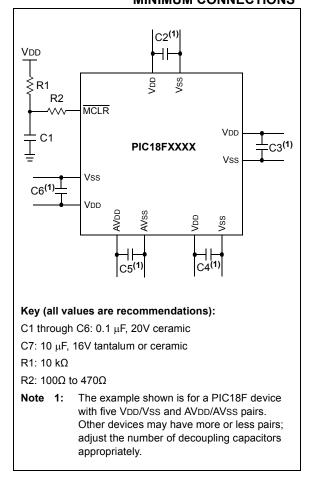

The minimum mandatory connections are shown in Figure 2-1.

## FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

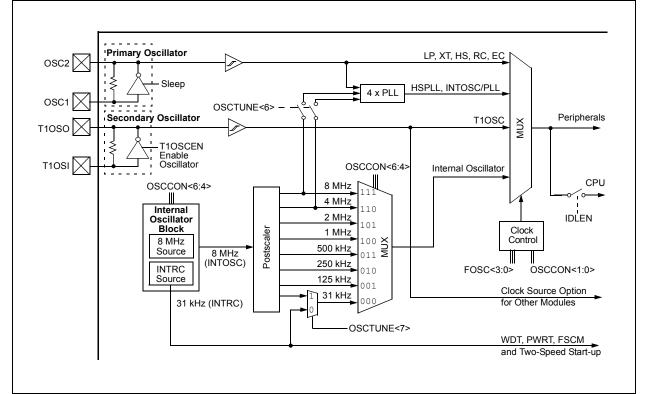

# 3.7 Clock Sources and Oscillator Switching

The PIC18F2221/2321/4221/4321 family of devices includes a feature that allows the device clock source to be switched from the main oscillator to an alternate clock source. These devices also offer two alternate clock sources. When an alternate clock source is enabled, the various power-managed operating modes are available.

Essentially, there are three clock sources for these devices:

- Primary oscillators

- · Secondary oscillators

- · Internal oscillator block

The **primary oscillators** include the External Crystal and Resonator modes, the External RC modes, the External Clock modes and the internal oscillator block. The particular mode is defined by the FOSC<3:0> Configuration bits. The details of these modes are covered earlier in this chapter. The **secondary oscillators** are those external sources not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode.

The PIC18F2221/2321/4221/4321 family of devices offers the Timer1 oscillator as a secondary oscillator. This oscillator, in all power-managed modes, is often the time base for functions such as a Real-Time Clock.

Most often, a 32.768 kHz watch crystal is connected between the RC0/T1OSO/T13CKI and RC1/T1OSI pins. Like the LP mode oscillator circuit, loading capacitors are also connected from each pin to ground.

The Timer1 oscillator is discussed in greater detail in **Section 13.3 "Timer1 Oscillator"**.

In addition to being a primary clock source, the **internal oscillator block** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor.

The clock sources for the PIC18F2221/2321/4221/4321 family of devices are shown in Figure 3-11. See **Section 24.0 "Special Features of the CPU"** for Configuration register details.

#### FIGURE 3-11: PIC18F2221/2321/4221/4321 FAMILY CLOCK DIAGRAM

#### 6.1.2.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

#### 6.1.3 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers, to provide a "fast return" option for interrupts. The stack for each register is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the Stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 6-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

#### EXAMPLE 6-1: FAST REGISTER STACK CODE EXAMPLE

| CALL | SUB1, FAST             | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|------|------------------------|---------------------------------------------------------|

| SUB1 | •<br>•<br>RETURN, FAS: | F ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK      |

# 6.1.4 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 6.1.4.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 6-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 6-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVE  | OFFSET, | W |

|-------|-------|---------|---|

|       | CALL  | TABLE   |   |

| ORG   | nn00h |         |   |

| TABLE | ADDWF | PCL     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       |       |         |   |

|       | •     |         |   |

|       | •     |         |   |

|       |       |         |   |

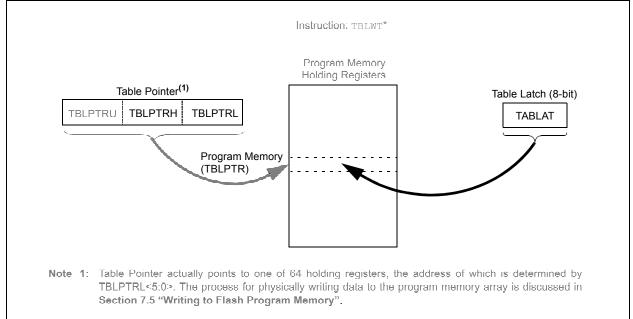

#### 6.1.4.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 7.1 "Table Reads and Table Writes".

# FIGURE 7-2: TABLE WRITE OPERATION

# 7.2 Control Registers

Several control registers are used in conjunction with the  ${\tt TBLRD}$  and  ${\tt TBLWT}$  instructions. These include the:

- EECON1 register

- · EECON2 register

- TABLAT register

- TBLPTR registers

#### 7.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 7-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on Configuration registers regardless of EEPGD (see **Section 24.0 "Special Features of the CPU"**). When clear, memory selection access is determined by EEPGD. The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR bit     |

|-------|--------------------------------------------|

|       | may read as '1'. This can indicate that a  |

|       | write operation was prematurely termi-     |

|       | nated by a Reset, or a write operation was |

|       | attempted improperly.                      |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

| Note: | The EEIF interrupt flag bit (PIR2<4>) is set |

|-------|----------------------------------------------|

|       | when the write is complete. It must be       |

|       | cleared in software.                         |

# **10.0 INTERRUPTS**

The PIC18F2221/2321/4221/4321 family devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the lowpriority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2

- PIE1, PIE2

- IPR1, IPR2

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a lowpriority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while any interrupt is enabled. Doing so may cause erratic microcontroller behavior.

| TABLE 11-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|-------------|--------------------------------------------|

|-------------|--------------------------------------------|

| Name    | Bit 7                                                       | Bit 6     | Bit 5   | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|-------------------------------------------------------------|-----------|---------|---------|--------|--------|--------|--------|----------------------------|

| PORTB   | RB7                                                         | RB6       | RB5     | RB4     | RB3    | RB2    | RB1    | RB0    | 58                         |

| LATB    | TB PORTB Data Latch Register (Read and Write to Data Latch) |           |         |         |        |        |        |        | 58                         |

| TRISB   | PORTB Data Direction Register                               |           |         |         |        |        |        | 58     |                            |

| INTCON  | GIE/GIEH                                                    | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE   | TMR0IF | INT0IF | RBIF   | 55                         |

| INTCON2 | RBPU                                                        | INTEDG0   | INTEDG1 | INTEDG2 | _      | TMR0IP | _      | RBIP   | 55                         |

| INTCON3 | INT2IP                                                      | INT1IP    | _       | INT2IE  | INT1IE | _      | INT2IF | INT1IF | 55                         |

| ADCON1  |                                                             | _         | VCFG1   | VCFG0   | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 57                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTB.

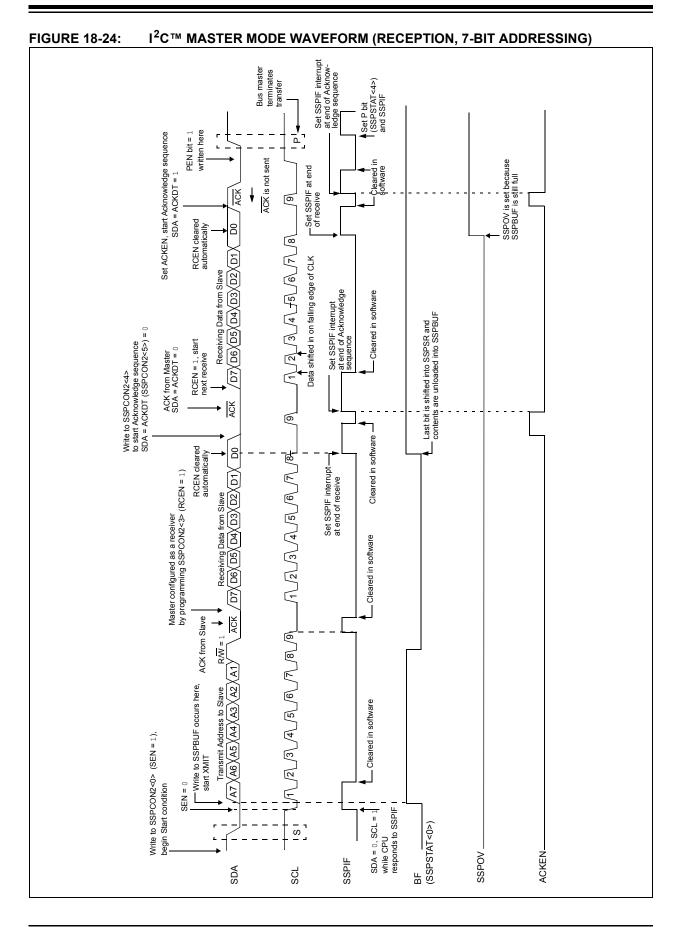

### 18.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 18.4.7 "Baud Rate"** for more detail.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPCON2<0>).

- SSPIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- 4. Address is shifted out the SDA pin until all 8 bits are transmitted.

- 5. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register.

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 7. The user loads the SSPBUF with eight bits of data.

- 8. Data is shifted out the SDA pin until all 8 bits are transmitted.

- 9. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register.

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPCON2<2>).

- 12. Interrupt is generated once the Stop condition is complete.

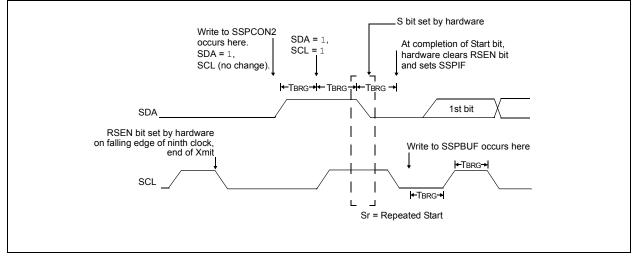

### 18.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

#### 18.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

# FIGURE 18-22: REPEATED START CONDITION WAVEFORM

#### 18.4.14 SLEEP OPERATION

While in Sleep mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 18.4.15 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 18.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit (SSPSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

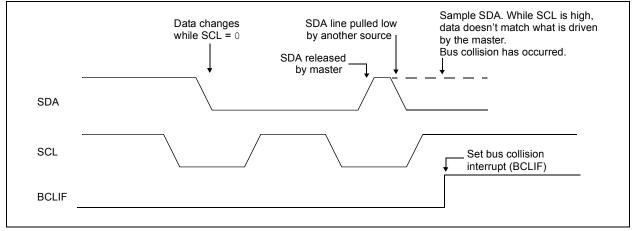

#### 18.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the  $I^2C$  port to its Idle state (Figure 18-27).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 18-27: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

# 19.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of the two serial I/O modules. (Generically, the USART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a halfduplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN/J2602 bus) systems.

The EUSART can be configured in the following modes:

- Asynchronous (full duplex) with:

- Auto-wake-up on Break signal

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half duplex) with selectable clock polarity

- Synchronous Slave (half duplex) with selectable clock polarity

The pins of the Enhanced USART are multiplexed with PORTC. In order to configure RC6/TX/CK and RC7/RX/DT as an EUSART:

- bit SPEN (RCSTA<7>) must be set (= 1)

- bit TRISC<7> must be set (= 1)

- bit TRISC<6> must be set (= 1)

| Note: | The EUSART control will automatically               |

|-------|-----------------------------------------------------|

|       | reconfigure the pin from input to output as needed. |

The operation of the Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These are detailed on the following pages in Register 19-1, Register 19-2 and Register 19-3, respectively.

| Name    | Bit 7                                         | Bit 6      | Bit 5       | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|-----------------------------------------------|------------|-------------|--------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                      | PEIE/GIEL  | TMR0IE      | INT0IE       | RBIE  | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1    | PSPIF <sup>(1)</sup>                          | ADIF       | RCIF        | TXIF         | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1    | PSPIE <sup>(1)</sup>                          | ADIE       | RCIE        | TXIE         | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1    | PSPIP <sup>(1)</sup>                          | ADIP       | RCIP        | TXIP         | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                         |

| RCSTA   | SPEN                                          | RX9        | SREN        | CREN         | ADDEN | FERR   | OERR   | RX9D   | 57                         |

| TXREG   | EUSART Transmit Register                      |            |             |              |       |        |        | 57     |                            |

| TXSTA   | CSRC                                          | TX9        | TXEN        | SYNC         | SENDB | BRGH   | TRMT   | TX9D   | 57                         |

| BAUDCON | ABDOVF                                        | RCIDL      | RXDTP       | TXCKP        | BRG16 | —      | WUE    | ABDEN  | 57                         |

| SPBRGH  | EUSART Baud Rate Generator Register High Byte |            |             |              |       |        |        | 57     |                            |

| SPBRG   | EUSART B                                      | aud Rate G | enerator Re | gister Low E | Byte  |        |        |        | 57                         |

#### TABLE 19-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

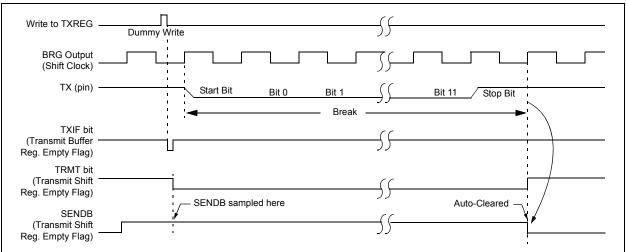

### 19.2.5 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 19-10 for the timing of the Break character sequence.

#### 19.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 19.2.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in **Section 19.2.4 "Auto-Wake-up on Sync Break Character"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit once the TXIF interrupt is observed.

#### FIGURE 19-10: SEND BREAK CHARACTER SEQUENCE

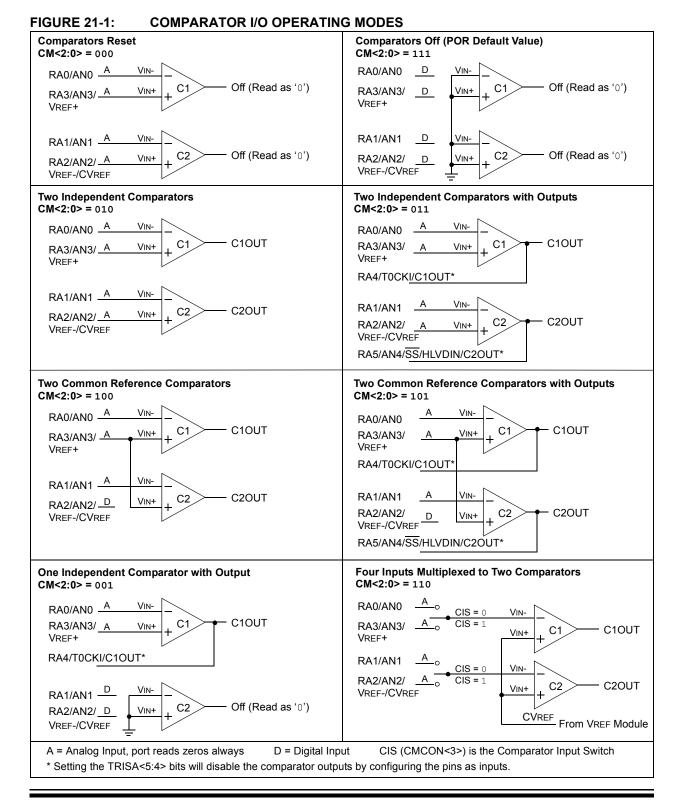

# 21.1 Comparator Configuration

There are eight modes of operation for the comparators, shown in Figure 21-1. Bits CM<2:0> of the CMCON register are used to select these modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the

comparator output level may not be valid for the specified mode change delay shown in **Section 27.0 "Electrical Characteristics"**.

Note: Comparator interrupts should be disabled during a Comparator mode change; otherwise, a false interrupt may occur.

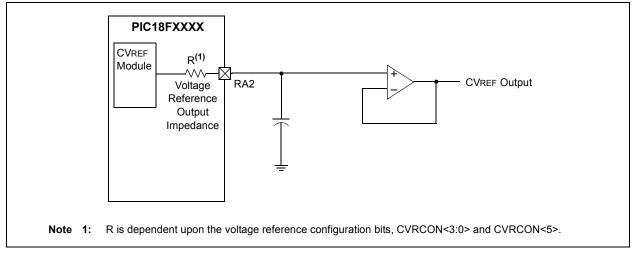

### FIGURE 22-2: COMPARATOR VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 22-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7                 | Bit 6                 | Bit 5   | Bit 4        | Bit 3        | Bit 2   | Bit 1 | Bit 0 | Reset<br>Values<br>on page |

|--------|-----------------------|-----------------------|---------|--------------|--------------|---------|-------|-------|----------------------------|

| CVRCON | CVREN                 | CVROE                 | CVRR    | CVRSS        | CVR3         | CVR2    | CVR1  | CVR0  | 57                         |

| CMCON  | C2OUT                 | C10UT                 | C2INV   | C1INV        | CIS          | CM2     | CM1   | CM0   | 57                         |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA D | ata Directio | on Control R | egister |       |       | 58                         |

Legend: Shaded cells are not used with the comparator voltage reference.

Note 1: PORTA pins are enabled based on oscillator configuration.

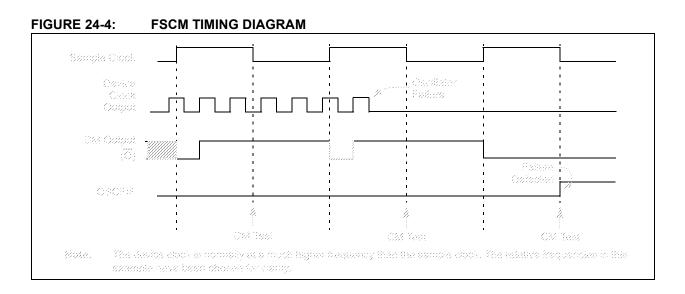

### 24.4.3 FSCM INTERRUPTS IN POWER-MANAGED MODES

By entering a power-managed mode, the clock multiplexer selects the clock source selected by the OSCCON register. Fail-Safe Monitoring of the powermanaged clock source resumes in the power-managed mode.

If an oscillator failure occurs during power-managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTOSC multiplexer. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, subsequent interrupts while in Idle mode will cause the CPU to begin executing instructions while being clocked by the INTOSC source.

### 24.4.4 POR OR WAKE FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited Power-on Reset (POR) or low-power Sleep mode. When the primary device clock is EC, RC or INTRC modes, monitoring can begin immediately following these events.

For oscillator modes involving a crystal or resonator (HS, HSPLL, LP or XT), the situation is somewhat different. Since the oscillator may require a start-up time considerably longer than the FCSM sample clock time, a false clock failure may be detected. To prevent this, the internal oscillator block is automatically configured as the device clock and functions until the primary clock is stable (the OST and PLL timers have timed out). This is identical to Two-Speed Start-up mode. Once the primary clock is stable, the INTRC returns to its role as the FSCM source.

| Note: | The same logic that prevents false oscilla-<br>tor failure interrupts on POR, or wake from<br>Sleep, will also prevent the detection of |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

|       | the oscillator's failure to start at all follow-<br>ing these events. This can be avoided by                                            |

|       | monitoring the OSTS bit and using a timing routine to determine if the oscillator                                                       |

|       | is taking too long to start. Even so, no oscillator failure interrupt will be flagged.                                                  |

As noted in Section 24.3.1 "Special Considerations for Using Two-Speed Start-up", it is also possible to select another clock configuration and enter an alternate power-managed mode while waiting for the primary clock to become stable. When the new powermanaged mode is selected, the primary clock is disabled.

| тѕт       | FSZ                                          | Test f, Skip if 0                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |  |  |  |  |  |

|-----------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Syntax:   |                                              | TSTFSZ f {                                                                                                                                                                                        | TSTFSZ f {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |  |  |  |  |  |

| Operands: |                                              | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |  |  |  |  |  |

| Oper      | ation:                                       | skip if f = 0                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |  |  |  |  |  |

| Statu     | s Affected:                                  | None                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |  |  |  |  |  |

| Enco      | ding:                                        | 0110                                                                                                                                                                                              | 011a fff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | f ffff          |  |  |  |  |  |

| Desc      | ription:                                     | during the c<br>is discarded<br>making this<br>If 'a' is '0', th<br>If 'a' is '1', th<br>GPR bank (<br>If 'a' is '0' an<br>set is enabl<br>in Indexed I<br>mode when<br>Section 25<br>Bit-Oriente | If 'f' = 0, the next instruction fetched<br>during the current instruction execution<br>is discarded and a NOP is executed,<br>making this a two-cycle instruction.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '0', the ASR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                 |  |  |  |  |  |

| Word      | ls:                                          | 1                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |  |  |  |  |  |

| Cycle     | es:                                          |                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |  |  |  |  |  |

| QC        | ycle Activity:                               | ,                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |  |  |  |  |  |

|           | Q1                                           | Q2                                                                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Q4              |  |  |  |  |  |

|           | Decode                                       | Read<br>register 'f'                                                                                                                                                                              | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | No<br>operation |  |  |  |  |  |

| lf sk     | ip:                                          |                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |  |  |  |  |  |

|           | Q1                                           | Q2                                                                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Q4              |  |  |  |  |  |

|           | No                                           | No                                                                                                                                                                                                | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | No              |  |  |  |  |  |

| lfek      | operation                                    | operation                                                                                                                                                                                         | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | operation       |  |  |  |  |  |

| 11 31     | Q1                                           | Q2                                                                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Q4              |  |  |  |  |  |

|           | No                                           | No                                                                                                                                                                                                | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | No              |  |  |  |  |  |

|           | operation                                    | operation                                                                                                                                                                                         | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | operation       |  |  |  |  |  |

|           | No<br>operation                              | No<br>operation                                                                                                                                                                                   | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | No<br>operation |  |  |  |  |  |

|           |                                              |                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |  |  |  |  |  |

| Example:  |                                              | NZERO :                                                                                                                                                                                           | NZERO :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |  |  |  |  |  |

|           | Before Instruc<br>PC<br>After Instructio     | = Ad                                                                                                                                                                                              | dress (HERE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | )               |  |  |  |  |  |

|           | If CNT<br>PC<br>If CNT<br>PC<br>If CNT<br>PC | = 00<br>= Ad<br>≠ 00                                                                                                                                                                              | dress (ZERO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |  |  |  |  |  |

| XOR               | LW             | Exclusiv            | Exclusive OR Literal with W                                                        |      |            |  |  |  |  |

|-------------------|----------------|---------------------|------------------------------------------------------------------------------------|------|------------|--|--|--|--|

| Synta             | ax:            | XORLW               | XORLW k                                                                            |      |            |  |  |  |  |

| Oper              | ands:          | $0 \le k \le 25$    | $0 \le k \le 255$                                                                  |      |            |  |  |  |  |

| Operation:        |                | (W) .XOF            | (W) .XOR. $k \rightarrow W$                                                        |      |            |  |  |  |  |

| Status Affected:  |                | N, Z                | N, Z                                                                               |      |            |  |  |  |  |

| Enco              | ding:          | 0000                | 1010                                                                               | kkkk | kkkk       |  |  |  |  |

| Description:      |                |                     | The contents of W are XORed with the 8-bit literal 'k'. The result is placed in W. |      |            |  |  |  |  |

| Words:            |                | 1                   | 1                                                                                  |      |            |  |  |  |  |

| Cycles:           |                | 1                   |                                                                                    |      |            |  |  |  |  |

| Q Cycle Activity: |                |                     |                                                                                    |      |            |  |  |  |  |

| Q1                |                | Q2                  | Q3                                                                                 |      | Q4         |  |  |  |  |

|                   | Decode         | Read<br>literal 'k' | Proce<br>Data                                                                      |      | /rite to W |  |  |  |  |

| <u>Exan</u>       | <u>iple:</u>   | XORLW               | 0AFh                                                                               |      |            |  |  |  |  |

|                   | Before Instruc | tion                |                                                                                    |      |            |  |  |  |  |

W = B5h After Instruction

W = 1Ah

© 2009 Microchip Technology Inc.

# 25.2 Extended Instruction Set

In addition to the standard 75 instructions of the PIC18 instruction set, PIC18F2221/2321/4221/4321 family devices also provide an optional extension to the core CPU functionality. The added features include eight additional instructions that augment indirect and indexed addressing operations and the implementation of Indexed Literal Offset Addressing mode for many of the standard PIC18 instructions.

The additional features of the extended instruction set are disabled by default. To enable them, users must set the XINST Configuration bit.

The instructions in the extended set (with the exception of CALLW, MOVSF and MOVSS) can all be classified as literal operations, which either manipulate the File Select Registers, or use them for indexed addressing. Two of the instructions, ADDFSR and SUBFSR, each have an additional special instantiation for using FSR2. These versions (ADDULNK and SUBULNK) allow for automatic return after execution.

The extended instructions are specifically implemented to optimize re-entrant program code (that is, code that is recursive or that uses a software stack) written in high-level languages, particularly C. Among other things, they allow users working in high-level languages to perform certain operations on data structures more efficiently. These include:

- Dynamic allocation and deallocation of software stack space when entering and leaving subroutines

- Function Pointer invocation

- Software Stack Pointer manipulation

- Manipulation of variables located in a software stack

A summary of the instructions in the extended instruction set is provided in Table 25-3. Detailed descriptions are provided in **Section 25.2.2** "**Extended Instruction Set**". The opcode field descriptions in Table 25-1 (page 280) apply to both the standard and extended PIC18 instruction sets.

Note: The instruction set extension and the Indexed Literal Offset Addressing mode were designed for optimizing applications written in C; the user may likely never use these instructions directly in the assembler. The syntax for these commands is provided as a reference for users who may be reviewing code that has been generated by a compiler.

# 25.2.1 EXTENDED INSTRUCTION SYNTAX

Most of the extended instructions use indexed arguments, using one of the File Select Registers and some offset to specify a source or destination register. When an argument for an instruction serves as part of indexed addressing, it is enclosed in square brackets ("[]"). This is done to indicate that the argument is used as an index or offset. The MPASM<sup>™</sup> Assembler will flag an error if it determines that an index or offset value is not bracketed.

When the extended instruction set is enabled, brackets are also used to indicate index arguments in byteoriented and bit-oriented instructions. This is in addition to other changes in their syntax. For more details, see Section 25.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands".

Note: In the past, square brackets have been used to denote optional arguments in the PIC18 and earlier instruction sets. In this text and going forward, optional arguments are denoted by braces ("{ }").

| Mnemonic,<br>Operands |                                 | Description                              | Cycles | 16-Bit Instruction Word |      |         |      | Status   |

|-----------------------|---------------------------------|------------------------------------------|--------|-------------------------|------|---------|------|----------|

|                       |                                 | Description                              | Cycles | MSb                     |      |         | LSb  | Affected |

| ADDFSR                | f, k                            | Add Literal to FSR                       | 1      | 1110                    | 1000 | ffkk    | kkkk | None     |

| ADDULNK               | k                               | Add Literal to FSR2 and Return           | 2      | 1110                    | 1000 | 11kk    | kkkk | None     |

| CALLW                 |                                 | Call Subroutine using WREG               | 2      | 0000                    | 0000 | 0001    | 0100 | None     |

| MOVSF                 | z <sub>s</sub> , f <sub>d</sub> | Move z <sub>s</sub> (source) to 1st Word | 2      | 1110                    | 1011 | 0 z z z | ZZZZ | None     |

|                       |                                 | f <sub>d</sub> (destination) 2nd Word    |        | 1111                    | ffff | ffff    | ffff |          |

| MOVSS                 | z <sub>s</sub> , z <sub>d</sub> | Move z <sub>s</sub> (source) to 1st word | 2      | 1110                    | 1011 | 1zzz    | ZZZZ | None     |

|                       |                                 | z <sub>d</sub> (destination) 2nd Word    |        | 1111                    | XXXX | XZZZ    | ZZZZ |          |

| PUSHL                 | k                               | Store Literal at FSR2,                   | 1      | 1110                    | 1010 | kkkk    | kkkk | None     |

|                       |                                 | Decrement FSR2                           |        |                         |      |         |      |          |

| SUBFSR                | f, k                            | Subtract Literal from FSR                | 1      | 1110                    | 1001 | ffkk    | kkkk | None     |

| SUBULNK               | k                               | Subtract Literal from FSR2 and           | 2      | 1110                    | 1001 | 11kk    | kkkk | None     |

|                       |                                 | Return                                   |        |                         |      |         |      |          |

# TABLE 25-3: EXTENSIONS TO THE PIC18 INSTRUCTION SET

# 27.3 DC Characteristics: PIC18F2221/2321/4221/4321 (Industrial) PIC18LF2221/2321/4221/4321 (Industrial)

| DC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature } -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |                    |          |       |                                                                 |

|--------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|-------|-----------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                                           | Min                | Мах      | Units | Conditions                                                      |

|                    | VIL    | Input Low Voltage                                                                                                                                                                                                                                        |                    |          |       |                                                                 |

|                    |        | I/O Ports:                                                                                                                                                                                                                                               |                    |          |       |                                                                 |

| D030               |        | with TTL Buffer                                                                                                                                                                                                                                          | Vss                | 0.15 Vdd | V     | VDD < 4.5V                                                      |

| D030A              |        |                                                                                                                                                                                                                                                          | —                  | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                |

| D031               |        | with Schmitt Trigger Buffer                                                                                                                                                                                                                              | Vss                | 0.2 VDD  | V     |                                                                 |

| D031A              |        | RC3 and RC4                                                                                                                                                                                                                                              | Vss                | 0.3 Vdd  | V     | I <sup>2</sup> C™ enabled                                       |

| D031B              |        |                                                                                                                                                                                                                                                          | Vss                | 0.8      | V     | SMBus enabled                                                   |

| D032               |        | MCLR                                                                                                                                                                                                                                                     | Vss                | 0.2 Vdd  | V     |                                                                 |

| D033               |        | OSC1                                                                                                                                                                                                                                                     | Vss                | 0.3 Vdd  | V     | HS, HSPLL modes                                                 |

| D033A              |        | OSC1                                                                                                                                                                                                                                                     | Vss                | 0.2 Vdd  | V     | RC, EC modes <sup>(1)</sup>                                     |

| D033B              |        | OSC1                                                                                                                                                                                                                                                     | Vss                | 0.3      | V     | XT, LP modes                                                    |

| D034               |        | T13CKI                                                                                                                                                                                                                                                   | Vss                | 0.3      | V     |                                                                 |

|                    | Viн    | Input High Voltage                                                                                                                                                                                                                                       |                    |          |       |                                                                 |

|                    |        | I/O Ports:                                                                                                                                                                                                                                               |                    |          |       |                                                                 |

| D040               |        | with TTL Buffer                                                                                                                                                                                                                                          | 0.25 VDD +<br>0.8V | Vdd      | V     | Vdd < 4.5V                                                      |

| D040A              |        |                                                                                                                                                                                                                                                          | 2.0                | Vdd      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                |

| D041               |        | with Schmitt Trigger Buffer                                                                                                                                                                                                                              | 0.8 Vdd            | Vdd      | V     |                                                                 |

| D041A              |        | RC3 and RC4                                                                                                                                                                                                                                              | 0.7 Vdd            | Vdd      | V     | I <sup>2</sup> C™ enabled                                       |

| D041B              |        |                                                                                                                                                                                                                                                          | 2.1                | Vdd      | V     | SMBus enabled,<br>Vss ≥ 3V                                      |

| D042               |        | MCLR                                                                                                                                                                                                                                                     | 0.8 Vdd            | Vdd      | V     |                                                                 |

| D043               |        | OSC1                                                                                                                                                                                                                                                     | 0.7 Vdd            | Vdd      | V     | HS, HSPLL modes                                                 |