#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2321-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F2221 PIC18LF2221

- PIC18F2321 PIC18LF2321

- PIC18F4221 PIC18LF4221

- PIC18F4321 PIC18LF4321

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of highendurance, Enhanced Flash program memory. On top of these features, the PIC18F2221/2321/4221/4321 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

### 1.1 New Core Features

### 1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F2221/2321/4221/4321 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- **Multiple Idle Modes:** The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- On-the-Fly Mode Switching: The power-managed modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 27.0 "Electrical Characteristics" for values.

### 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F2221/2321/4221/4321 family offer ten different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators.

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O).

- Two External RC Oscillator modes with the same pin options as the External Clock modes.

- Two Internal Oscillator modes which provide an 8 MHz clock and an INTRC source (approximately 31 kHz), as well as a range of 6 user-selectable clock frequencies, between 125 kHz to 4 MHz, for a total of 8 clock frequencies. One or both of the oscillator pins can be used for general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both the high-speed crystal and internal oscillator modes, which allows clock speeds of up to 40 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 32 MHz – all without using an external crystal or clock circuit.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

## 1.2 Other Special Features

- **Memory Endurance:** The Enhanced Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles – up to 100,000 for program memory and 1,000,000 for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

- Self-Programmability: These devices can write to their own program memory spaces under internal software control. By using a bootloader routine, located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

- Extended Instruction Set: The PIC18F2221/ 2321/4221/4321 family introduces an optional extension to the PIC18 instruction set, which adds 8 new instructions and an Indexed Addressing mode. This extension, enabled as a device configuration option, has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

- Enhanced CCP Module: In PWM mode, this module provides 1, 2 or 4 modulated outputs for controlling half-bridge and full-bridge drivers. Other features include auto-shutdown, for disabling PWM outputs on interrupt or other select conditions and auto-restart, to reactivate outputs once the condition has cleared.

- Enhanced Addressable USART: This serial communication module is capable of standard RS-232 operation and provides support for the LIN/J2602 bus protocol. Other enhancements include automatic baud rate detection and a 16-bit Baud Rate Generator for improved resolution. When the microcontroller is using the internal oscillator block, the EUSART provides stable operation for applications that talk to the outside world without using an external crystal (or its accompanying power requirement).

- **10-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reducing code overhead.

- Extended Watchdog Timer (WDT): This Enhanced version incorporates a 16-bit prescaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 27.0 "Electrical Characteristics" for time-out periods.

## 1.3 Details on Individual Family Members

Devices in the PIC18F2221/2321/4221/4321 family are available in 28-pin and 40/44-pin packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2.

The devices are differentiated from each other in five ways:

- 1. Flash program memory (4 Kbytes for PIC18F2221/4221 devices, 8 Kbytes for PIC18F2321/4321).

- 2. A/D channels (10 for 28-pin devices, 13 for 40/44-pin devices).

- 3. I/O ports (3 bidirectional ports on 28-pin devices, 5 bidirectional ports on 40/44-pin devices).

- CCP and Enhanced CCP implementation (28-pin devices have 2 standard CCP modules, 40/44-pin devices have one standard CCP module and one ECCP module).

- 5. Parallel Slave Port (present only on 40/44-pin devices).

All other features for devices in this family are identical. These are summarized in Table 1-1.

The pinouts for all devices are listed in Table 1-2 and Table 1-3.

Like all Microchip PIC18 devices, members of the PIC18F2221/2321/4221/4321 family are available as both standard and low-voltage devices. Standard devices with Enhanced Flash memory, designated with an "F" in the part number (such as PIC18F2321), accommodate an operating VDD range of 4.2V to 5.5V. Low-voltage parts, designated by "LF" (such as PIC18LF2321), function over an extended VDD range of 2.0V to 5.5V.

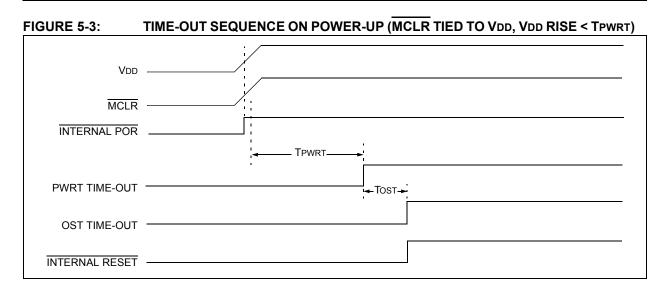

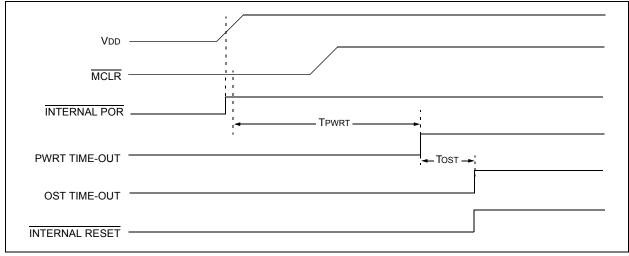

### FIGURE 5-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

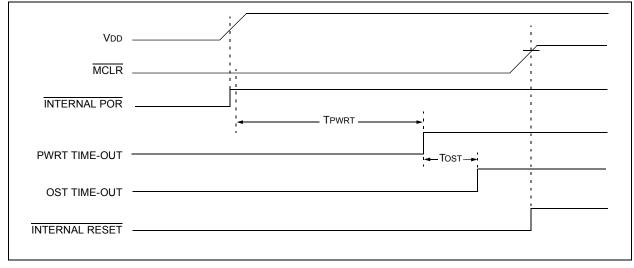

## FIGURE 5-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

| File Name            | Bit 7                 | Bit 6                                        | Bit 5                           | Bit 4                                  | Bit 3              | Bit 2              | Bit 1              | Bit 0              | Value on<br>POR, BOR | Details on page: |  |  |  |

|----------------------|-----------------------|----------------------------------------------|---------------------------------|----------------------------------------|--------------------|--------------------|--------------------|--------------------|----------------------|------------------|--|--|--|

| SPBRGH               | EUSART Bau            | ud Rate Gener                                | ator Register                   | High Byte                              |                    |                    |                    |                    | 0000 0000            | 57, 216          |  |  |  |

| SPBRG                | EUSART Bau            | EUSART Baud Rate Generator Register Low Byte |                                 |                                        |                    |                    |                    |                    |                      |                  |  |  |  |

| RCREG                | EUSART Red            |                                              | 0000 0000                       | 57, 224                                |                    |                    |                    |                    |                      |                  |  |  |  |

| TXREG                | EUSART Tra            | 0000 0000                                    | 57, 221                         |                                        |                    |                    |                    |                    |                      |                  |  |  |  |

| TXSTA                | CSRC                  | TX9                                          | TXEN                            | SYNC                                   | SENDB              | BRGH               | TRMT               | TX9D               | 0000 0010            | 57, 212          |  |  |  |

| RCSTA                | SPEN                  | RX9                                          | SREN                            | CREN                                   | ADDEN              | FERR               | OERR               | RX9D               | 0000 000x            | 57, 213          |  |  |  |

| EEADR                | EEPROM Ad             | dress Registe                                | r                               |                                        |                    |                    |                    |                    | 0000 0000            | 57, 80, 89       |  |  |  |

| EEDATA               | EEPROM Da             | ta Register                                  |                                 |                                        |                    |                    |                    |                    | 0000 0000            | 57, 80, 89       |  |  |  |

| EECON2               | EEPROM Co             | ntrol Register                               | 2 (not a physi                  | cal register)                          |                    |                    |                    |                    | 0000 0000            | 57, 80, 89       |  |  |  |

| EECON1               | EEPGD                 | CFGS                                         | —                               | FREE                                   | WRERR              | WREN               | WR                 | RD                 | xx-0 x000            | 57, 81, 90       |  |  |  |

| IPR2                 | OSCFIP                | CMIP                                         | —                               | EEIP                                   | BCLIP              | HLVDIP             | TMR3IP             | CCP2IP             | 11-1 1111            | 58, 107          |  |  |  |

| PIR2                 | OSCFIF                | CMIF                                         | —                               | EEIF                                   | BCLIF              | HLVDIF             | TMR3IF             | CCP2IF             | 00-0 0000            | 58, 103          |  |  |  |

| PIE2                 | OSCFIE                | CMIE                                         | EEIE BCLIE HLVDIE TMR3IE CCP2IE |                                        |                    |                    |                    |                    |                      | 58, 105          |  |  |  |

| IPR1                 | PSPIP <sup>(2)</sup>  | ADIP                                         | RCIP                            | RCIP TXIP SSPIP CCP1IP TMR2IP TMR1IP   |                    |                    |                    |                    |                      |                  |  |  |  |

| PIR1                 | PSPIF <sup>(2)</sup>  | ADIF                                         | RCIF                            | RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF   |                    |                    |                    |                    |                      | 58, 102          |  |  |  |

| PIE1                 | PSPIE <sup>(2)</sup>  | ADIE                                         | RCIE                            | RCIE TXIE SSPIE CCP1IE TMR2IE TMR1IE 0 |                    |                    |                    |                    |                      | 58, 104          |  |  |  |

| OSCTUNE              | INTSRC                | PLLEN <sup>(3)</sup>                         | —                               | TUN4                                   | TUN3               | TUN2               | TUN1               | TUN0               | 00-0 0000            | 33, 58           |  |  |  |

| TRISE <sup>(2)</sup> | IBF                   | OBF                                          | IBOV                            | PSPMODE                                | _                  | TRISE2             | TRISE1             | TRISE0             | 0000 -111            | 58, 124          |  |  |  |

| TRISD <sup>(2)</sup> | PORTD Data            | Direction Con                                | trol Register                   |                                        |                    |                    |                    |                    | 1111 1111            | 58, 120          |  |  |  |

| TRISC                | PORTC Data            | Direction Con                                | trol Register                   |                                        |                    |                    |                    |                    | 1111 1111            | 58, 117          |  |  |  |

| TRISB                | PORTB Data            | Direction Con                                | trol Register                   |                                        |                    |                    |                    |                    | 1111 1111            | 58, 114          |  |  |  |

| TRISA                | TRISA7 <sup>(5)</sup> | TRISA6 <sup>(5)</sup>                        | PORTA Data                      | Direction Con                          | trol Register      |                    |                    |                    | 1111 1111            | 58, 111          |  |  |  |

| LATE <sup>(2)</sup>  | -                     | —                                            | —                               | —                                      | _                  |                    | Latch Register     |                    | xxx                  | 58, 123          |  |  |  |

| LATD <sup>(2)</sup>  | PORTD Data            | Latch Registe                                | er (Read and V                  | Vrite to Data L                        | atch)              |                    |                    |                    | XXXX XXXX            | 58, 120          |  |  |  |

| LATC                 | PORTC Data            | Latch Registe                                | er (Read and V                  | Vrite to Data L                        | atch)              |                    |                    |                    | XXXX XXXX            | 58, 117          |  |  |  |

| LATB                 | PORTB Data            | Latch Registe                                | er (Read and V                  | Vrite to Data La                       | atch)              |                    |                    |                    | XXXX XXXX            | 58, 114          |  |  |  |

| LATA                 | LATA7 <sup>(5)</sup>  | XXXX XXXX                                    | 58, 111                         |                                        |                    |                    |                    |                    |                      |                  |  |  |  |

| PORTE                | —                     | —                                            | —                               | _                                      | RE3 <sup>(4)</sup> | RE2 <sup>(2)</sup> | RE1 <sup>(2)</sup> | RE0 <sup>(2)</sup> | xxxx                 | 58, 123          |  |  |  |

| PORTD <sup>(2)</sup> | RD7                   | RD6                                          | RD5                             | RD4                                    | RD3                | RD2                | RD1                | RD0                | XXXX XXXX            | 58, 120          |  |  |  |

| PORTC                | RC7                   | RC6                                          | RC5                             | RC4                                    | RC3                | RC2                | RC1                | RC0                | XXXX XXXX            | 58, 117          |  |  |  |

| PORTB                | RB7                   | RB6                                          | RB5                             | RB4                                    | RB3                | RB2                | RB1                | RB0                | XXXX XXXX            | 58, 114          |  |  |  |

| PORTA                | RA7 <sup>(5)</sup>    | RA6 <sup>(5)</sup>                           | RA5                             | RA4                                    | RA3                | RA2                | RA1                | RA0                | xx0x 0000            | 58, 111          |  |  |  |

### TABLE 6-2:REGISTER FILE SUMMARY (PIC18F2221/2321/4221/4321) (CONTINUED)

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

1: The SBOREN bit is only available when the BOREN<1:0> Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

2: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

3: The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 3.6.4 "PLL in INTOSC Modes".

4: The RE3 bit is only available when Master Clear Reset is disabled (MCLRE Configuration bit = 0); otherwise, RE3 reads as '0'. This bit is read-only.

5: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

6: Bit 7 and bit 6 are cleared by user software or by a POR.

Note

### EXAMPLE 7-3: WRITING TO FLASH PROGRAM MEMORY (CONTINUED)

| PROGRAM_MEMORY |              |                             |

|----------------|--------------|-----------------------------|

| BCF            | INTCON, GIE  | ; disable interrupts        |

| MOVLW          | 55h          | ; required sequence         |

| MOVWF          | EECON2       | ; write 55h                 |

| MOVLW          | 0AAh         |                             |

| MOVWF          | EECON2       | ; write AAh                 |

| BSF            | EECON1, WR   | ; start program (CPU stall) |

| NOP            |              |                             |

| BSF            | INTCON, GIE  | ; re-enable interrupts      |

| DECFSZ         | COUNTER_HI   | ; loop until done           |

| GOTO           | PROGRAM_LOOP |                             |

| BCF            | EECON1, WREN | ; disable write to memory   |

|                |              |                             |

### 7.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

## 7.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

### 7.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See Section 24.0 "Special Features of the CPU" for more detail.

### 7.6 Flash Program Operation During Code Protection

See Section 24.5 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7                                         | Bit 6                                               | Bit 5       | Bit 4                                                          | Bit 3      | Bit 2  | Bit 1         | Bit 0  | Reset<br>Values on<br>page |

|---------|-----------------------------------------------|-----------------------------------------------------|-------------|----------------------------------------------------------------|------------|--------|---------------|--------|----------------------------|

| TBLPTRU | _                                             |                                                     | bit 21      | bit 21 Program Memory Table Pointer Upper Byte (TBLPTR<20:16>) |            |        |               |        |                            |

| TBPLTRH | Program Me                                    | emory Table                                         | Pointer H   | ligh Byte (TE                                                  | BLPTR<15:8 | >)     |               |        | 55                         |

| TBLPTRL | Program Me                                    | Program Memory Table Pointer Low Byte (TBLPTR<7:0>) |             |                                                                |            |        |               |        |                            |

| TABLAT  | Program Memory Table Latch                    |                                                     |             |                                                                |            |        |               |        | 55                         |

| INTCON  | GIE/GIEH                                      | PEIE/GIEL                                           | TMR0IE      | INT0IE                                                         | RBIE       | TMR0IF | <b>INT0IF</b> | RBIF   | 55                         |

| EECON2  | EEPROM C                                      | Control Regis                                       | ster 2 (not | t a physical r                                                 | egister)   |        |               |        | 57                         |

| EECON1  | EEPGD                                         | CFGS                                                | _           | FREE                                                           | WRERR      | WREN   | WR            | RD     | 57                         |

| IPR2    | OSCFIP CMIP — EEIP BCLIP HLVDIP TMR3IP CCP2IP |                                                     |             |                                                                |            |        |               | 58     |                            |

| PIR2    | OSCFIF                                        | CMIF                                                |             | EEIF                                                           | BCLIF      | HLVDIF | TMR3IF        | CCP2IF | 58                         |

| PIE2    | OSCFIE                                        | CMIE                                                |             | EEIE                                                           | BCLIE      | HLVDIE | TMR3IE        | CCP2IE | 58                         |

TABLE 7-2:

REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

Example 9-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 9-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES3:RES0).

### EQUATION 9-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 |   | ARG1H:ARG1L • ARG2H:ARG2L                |

|-----------|---|------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2L)$                  |

### EXAMPLE 9-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, W    |                   |

|---|--------|-------------|-------------------|

|   | MULWF  | ARG2L       | ; ARG1L * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES1 | ;                 |

|   | MOVFF  | PRODL, RESO | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1H * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES3 | ;                 |

|   | MOVFF  | PRODL, RES2 | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1L, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1L * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     |                   |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    | ;                 |

|   | MULWF  | ARG2L       | ; ARG1H * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   |        | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

|   |        |             |                   |

Example 9-4 shows the sequence to do a 16 x 16 signed multiply. Equation 9-2 shows the algorithm used. The 32-bit result is stored in four registers (RES3:RES0). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

### EQUATION 9-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 = ARG1H:ARG1L • ARG2H:ARG2L                           |

|-----------------------------------------------------------------|

| $= (ARG1H \bullet ARG2H \bullet 2^{16}) +$                      |

| $(ARG1H \bullet ARG2L \bullet 2^8) +$                           |

| $(ARG1L \bullet ARG2H \bullet 2^8) +$                           |

| $(ARG1L \bullet ARG2L) +$                                       |

| $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) +$ |

| $(-1 \bullet ARG1H < 7 > \bullet ARG2H:ARG2L \bullet 2^{16})$   |

### EXAMPLE 9-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|     |        |             | •• |                  |

|-----|--------|-------------|----|------------------|

|     | MOVF   | ARG1L, W    |    |                  |

|     | MULWF  | ARG2L       | ;  | ARG1L * ARG2L -> |

|     |        |             | ;  | PRODH:PRODL      |

|     | NOVER  | DDODU DDO1  |    | TRODIT. TRODE    |

|     | MOVFF  | PRODH, RES1 | ;  |                  |

|     | MOVFF  | PRODL, RESO | ;  |                  |

| ;   |        |             |    |                  |

|     | MOVF   | ARG1H, W    |    |                  |

|     | MULWF  | ARG2H       | ;  | ARG1H * ARG2H -> |

|     |        |             |    | PRODH: PRODL     |

|     | MOVEE  |             |    | TRODIT: TRODE    |

|     | MOVFF  | PRODH, RES3 | ;  |                  |

|     | MOVFF  | PRODL, RES2 | ;  |                  |

| ;   |        |             |    |                  |

|     | MOVF   | ARG1L, W    |    |                  |

|     | MULWF  | ARG2H       | ;  | ARG1L * ARG2H -> |

|     |        |             | ;  | PRODH:PRODL      |

|     | MOVF   | PRODL, W    | ;  |                  |

|     |        |             |    |                  |

|     | ADDWF  | RES1, F     |    | Add cross        |

|     | MOVF   | PRODH, W    | ;  | products         |

|     | ADDWFC | RES2, F     | ;  |                  |

|     | CLRF   | WREG        | ;  |                  |

|     | ADDWFC | RES3, F     | ;  |                  |

| ;   |        | ,           |    |                  |

| '   | MOVF   | ARG1H, W    |    |                  |

|     |        |             | ;  |                  |

|     | MULWF  | ARG2L       | ;  | ARG1H * ARG2L -> |

|     |        |             | ;  | PRODH:PRODL      |

|     | MOVF   | PRODL, W    | ;  |                  |

|     | ADDWF  | RES1, F     | ;  | Add cross        |

|     | MOVF   | PRODH, W    |    | products         |

|     | ADDWFC | RES2, F     | ;  | 1                |

|     | CLRF   | WREG        |    |                  |

|     |        |             | ;  |                  |

|     | ADDWFC | RES3, F     | ;  |                  |

| ;   |        |             |    |                  |

|     | BTFSS  | ARG2H, 7    | ;  | ARG2H:ARG2L neg? |

|     | BRA    | SIGN ARG1   | ;  | no, check ARG1   |

|     | MOVF   | ARG1L, W    | ;  |                  |

|     | SUBWF  | RES2        | ;  |                  |

|     | MOVF   | ARG1H, W    |    |                  |

|     |        |             | ;  |                  |

|     | SUBWFB | RES3        |    |                  |

| ;   |        |             |    |                  |

| SIG | N_ARG1 |             |    |                  |

|     | BTFSS  | ARG1H, 7    | ;  | ARG1H:ARG1L neg? |

|     | BRA    | CONT CODE   | ;  | no, done         |

|     | MOVF   | ARG2L, W    | ;  |                  |

|     | SUBWF  | RES2        | ;  |                  |

|     |        |             |    |                  |

|     | MOVF   | ARG2H, W    | ;  |                  |

|     | SUBWFB | RES3        |    |                  |

| ;   |        |             |    |                  |

| CON | T_CODE |             |    |                  |

|     | :      |             |    |                  |

|     |        |             |    |                  |

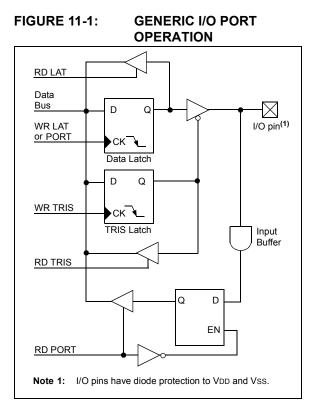

## 11.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (Data Latch register)

The Data Latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 11-1.

## 11.1 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin). Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The Data Latch (LATA) register is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input and one of the comparator outputs to become the RA4/T0CKI/C1OUT pin. Pins RA6 and RA7 are multiplexed with the main oscillator pins. They are enabled as oscillator or I/O pins by the selection of the main oscillator in the Configuration register (see **Section 24.1 "Configuration Bits**" for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs and the comparator voltage reference output. The operation of pins RA<3:0> and RA5 as A/D converter inputs is selected by clearing or setting the control bits in the ADCON1 register (A/D Control Register 1).

Pins RA0 through RA5 may also be used as comparator inputs or outputs by setting the appropriate bits in the CMCON register. To use RA<3:0> as digital inputs, it is also necessary to turn off the comparators.

| Note: | On a Power-on Reset, RA5 and RA<3:0>          |

|-------|-----------------------------------------------|

|       | are configured as analog inputs and read      |

|       | as '0'. RA4 is configured as a digital input. |

The RA4/T0CKI/C1OUT pin is a Schmitt Trigger input. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

### EXAMPLE 11-1: INITIALIZING PORTA

| CLRF  | PORTA  | ; | Initialize PORTA by       |

|-------|--------|---|---------------------------|

|       |        | ; | clearing output           |

|       |        | ; | data latches              |

| CLRF  | LATA   | ; | Alternate method          |

|       |        | ; | to clear output           |

|       |        | ; | data latches              |

| MOVLW | OFh    | ; | Configure all A/D         |

| MOVWF | ADCON1 | ; | for digital inputs        |

| MOVWF | 07h    | ; | Configure comparators     |

| MOVWF | CMCON  | ; | for digital input         |

| MOVLW | OCFh   | ; | Value used to             |

|       |        | ; | initialize data           |

|       |        | ; | direction                 |

| MOVWF | TRISA  | ; | Set RA<7:6,3:0> as inputs |

|       |        | ; | RA<5:4> as outputs        |

| 1     |        |   |                           |

| Name   | Bit 7                 | Bit 6                 | Bit 5    | Bit 4                                                   | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on page |  |

|--------|-----------------------|-----------------------|----------|---------------------------------------------------------|-------|-------|-------|-------|----------------------------|--|

| PORTA  | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5      | RA4                                                     | RA3   | RA2   | RA1   | RA0   | 58                         |  |

| LATA   | LATA7 <sup>(1)</sup>  |                       |          | ORTA Data Latch Register (Read and Write to Data Latch) |       |       |       |       |                            |  |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA Da | ORTA Data Direction Register                            |       |       |       |       |                            |  |

| ADCON1 | _                     | _                     | VCFG1    | VCFG0                                                   | PCFG3 | PCFG2 | PCFG1 | PCFG0 | 57                         |  |

| CMCON  | C2OUT                 | C10UT                 | C2INV    | C2INV C1INV CIS CM2 CM1 CM0                             |       |       |       |       |                            |  |

| CVRCON | CVREN                 | CVROE                 | CVRR     | CVRSS                                                   | CVR3  | CVR2  | CVR1  | CVR0  | 57                         |  |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA<7:6> and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

## 15.0 TIMER3 MODULE

The Timer3 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR3H and TMR3L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Module Reset on CCP Special Event Trigger

#### A simplified block diagram of the Timer3 module is shown in Figure 15-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 15-2.

The Timer3 module is controlled through the T3CON register (Register 15-1). It also selects the clock source options for the CCP modules (see **Section 16.1.1** "**CCP Modules and Timer Resources**" for more information).

### REGISTER 15-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|--------|---------|---------|--------|--------|--------|--------|

| RD16  | T3CCP2 | T3CKPS1 | T3CKPS0 | T3CCP1 | T3SYNC | TMR3CS | TMR3ON |

| bit 7 |        |         |         |        |        |        | bit 0  |

- bit 7 RD16: 16-Bit Read/Write Mode Enable bit

- 1 = Enables register read/write of Timer3 in one 16-bit operation

- 0 = Enables register read/write of Timer3 in two 8-bit operations

- bit 6,3 T3CCP<2:1>: Timer3 and Timer1 to CCPx Enable bits

- 1x = Timer3 is the capture/compare clock source for the CCP modules

- 01 = Timer3 is the capture/compare clock source for CCP2; Timer1 is the capture/compare clock source for CCP1

- 00 = Timer1 is the capture/compare clock source for the CCP modules

- bit 5-4 T3CKPS<1:0>: Timer3 Input Clock Prescale Select bits

- 11 = 1:8 Prescale value

- 10 = 1:4 Prescale value

- 01 = 1:2 Prescale value

- 00 = 1:1 Prescale value

- bit 2 **T3SYNC:** Timer3 External Clock Input Synchronization Control bit (Not usable if the device clock comes from Timer1/Timer3.)

- $M_{\text{box}} = MD_{2}^{2}CS = 1$

- When TMR3CS = 1:

- 1 = Do not synchronize external clock input

- 0 = Synchronize external clock input

- When TMR3CS = 0:

- This bit is ignored. Timer3 uses the internal clock when TMR3CS = 0.

- bit 1 TMR3CS: Timer3 Clock Source Select bit

- 1 = External clock input from Timer1 oscillator or T13CKI (on the rising edge after the first falling edge)

- 0 = Internal clock (Fosc/4)

- bit 0 **TMR3ON:** Timer3 On bit

- 1 = Enables Timer3

- 0 = Stops Timer3

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Name    | Bit 7                                         | Bit 6                                    | Bit 5        | Bit 4     | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|-----------------------------------------------|------------------------------------------|--------------|-----------|---------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                      | PEIE/GIEL                                | TMR0IE       | INT0IE    | RBIE    | TMR0IF | INT0IF | RBIF   | 55                         |

| RCON    | IPEN                                          | SBOREN <sup>(1)</sup>                    | _            | RI        | TO      | PD     | POR    | BOR    | 54                         |

| PIR1    | PSPIF <sup>(2)</sup>                          | ADIF                                     | RCIF         | TXIF      | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1    | PSPIE <sup>(2)</sup>                          | ADIE                                     | RCIE         | TXIE      | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1    | PSPIP <sup>(2)</sup>                          | ADIP                                     | RCIP         | TXIP      | SSPIP   | CCP1IP | TMR2IP | TMR1IP | 58                         |

| PIR2    | OSCFIF                                        | CMIF                                     | —            | EEIF      | BCLIF   | HLVDIF | TMR3IF | CCP2IF | 58                         |

| PIE2    | OSCFIE                                        | CMIE                                     | _            | EEIE      | BCLIE   | HLVDIE | TMR3IE | CCP2IE | 58                         |

| IPR2    | OSCFIP CMIP — EEIP BCLIP HLVDIP TMR3IP CCP2IP |                                          |              |           |         |        | 58     |        |                            |

| TRISB   | PORTB Da                                      | PORTB Data Direction Register            |              |           |         |        |        | 58     |                            |

| TRISC   | PORTC Da                                      | PORTC Data Direction Register            |              |           |         |        |        | 58     |                            |

| TMR1L   | Timer1 Reg                                    | gister Low By                            | /te          |           |         |        |        |        | 56                         |

| TMR1H   | Timer1 Reg                                    | gister High B                            | yte          |           |         |        |        |        | 56                         |

| T1CON   | RD16                                          | T1RUN                                    | T1CKPS1      | T1CKPS0   | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 56                         |

| TMR3H   | Timer3 Reg                                    | gister High B                            | yte          |           |         |        |        |        | 57                         |

| TMR3L   | Timer3 Reg                                    | gister Low B                             | /te          |           |         |        |        |        | 57                         |

| T3CON   | RD16                                          | T3CCP2                                   | T3CKPS1      | T3CKPS0   | T3CCP1  | T3SYNC | TMR3CS | TMR3ON | 57                         |

| CCPR1L  | Capture/Co                                    | mpare/PWN                                | 1 Register 1 | Low Byte  |         |        |        |        | 57                         |

| CCPR1H  | Capture/Co                                    | Capture/Compare/PWM Register 1 High Byte |              |           |         |        | 57     |        |                            |

| CCP1CON | P1M1 <sup>(2)</sup>                           | P1M0 <sup>(2)</sup>                      | DC1B1        | DC1B0     | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0 | 57                         |

| CCPR2L  | Capture/Co                                    | mpare/PWN                                | 1 Register 2 | Low Byte  |         |        |        |        | 57                         |

| CCPR2H  | Capture/Co                                    | mpare/PWN                                | 1 Register 2 | High Byte |         |        |        |        | 57                         |

| CCP2CON | _                                             | _                                        | DC2B1        | DC2B0     | CCP2M3  | CCP2M2 | CCP2M1 | CCP2M0 | 57                         |

| TABLE 16-3: | <b>REGISTERS ASSOCIATED WITH CAPTURE</b> | . COMPARE. TIMER1 AND TIMER3 |

|-------------|------------------------------------------|------------------------------|

|             |                                          |                              |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by Capture/Compare, Timer1 or Timer3.

Note 1: The SBOREN bit is only available when the BOREN<1:0> Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 5.4 "Brown-out Reset (BOR)".

**2:** These bits are unimplemented on 28-pin devices and read as '0'.

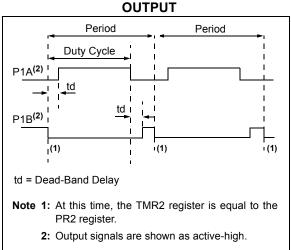

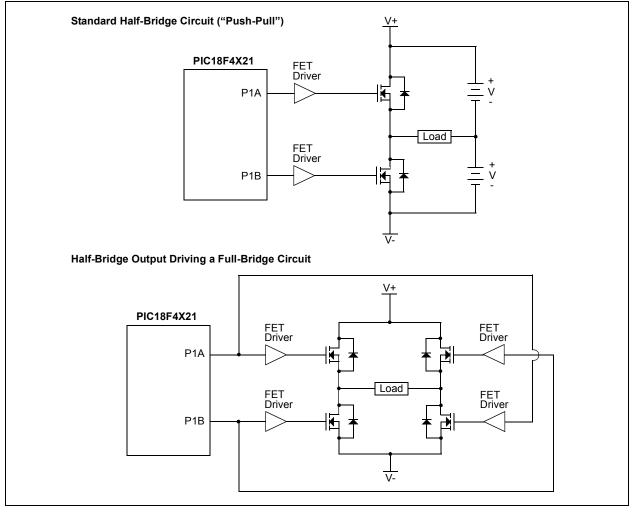

## 17.4.4 HALF-BRIDGE MODE

In the Half-Bridge Output mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the P1A pin, while the complementary PWM output signal is output on the P1B pin (Figure 17-4). This mode can be used for half-bridge applications, as shown in Figure 17-5, or for full-bridge applications where four power switches are being modulated with two PWM signals.

In Half-Bridge Output mode, the programmable deadband delay can be used to prevent shoot-through current in half-bridge power devices. The value of bits, PDC<6:0>, sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 17.4.6 "Programmable Dead-Band Delay"** for more details of the dead-band delay operations.

Since the P1A and P1B outputs are multiplexed with the PORTC<2> and PORTD<5> data latches, the TRISC<2> and TRISD<5> bits must be cleared to configure P1A and P1B as outputs.

## FIGURE 17-4: HALF-BRIDGE PWM

### FIGURE 17-5: EXAMPLES OF HALF-BRIDGE OUTPUT MODE APPLICATIONS

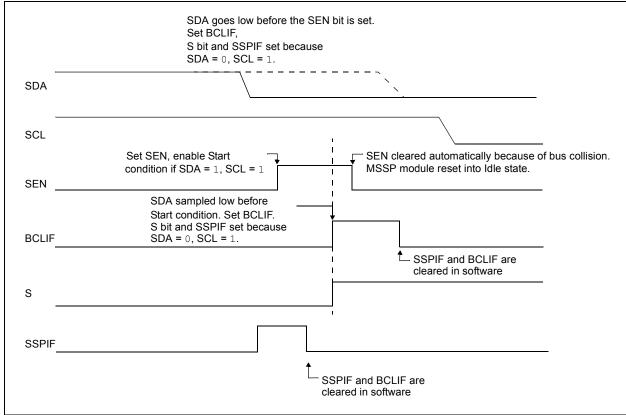

## 18.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 18-28).

- b) SCL is sampled low before SDA is asserted low (Figure 18-29).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 18-28).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 18-30). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

### FIGURE 18-28: BUS COLLISION DURING START CONDITION (SDA ONLY)

## 19.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of the two serial I/O modules. (Generically, the USART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a halfduplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN/J2602 bus) systems.

The EUSART can be configured in the following modes:

- Asynchronous (full duplex) with:

- Auto-wake-up on Break signal

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half duplex) with selectable clock polarity

- Synchronous Slave (half duplex) with selectable clock polarity

The pins of the Enhanced USART are multiplexed with PORTC. In order to configure RC6/TX/CK and RC7/RX/DT as an EUSART:

- bit SPEN (RCSTA<7>) must be set (= 1)

- bit TRISC<7> must be set (= 1)

- bit TRISC<6> must be set (= 1)

| Note: | The EUSART control will automatically               |

|-------|-----------------------------------------------------|

|       | reconfigure the pin from input to output as needed. |

The operation of the Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- · Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These are detailed on the following pages in Register 19-1, Register 19-2 and Register 19-3, respectively.

| Name    | Bit 7                | Bit 6                                         | Bit 5       | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------|-----------------------------------------------|-------------|--------------|-------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL                                     | TMR0IE      | INT0IE       | RBIE  | TMR0IF | INT0IF | RBIF   | 55                         |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF                                          | RCIF        | TXIF         | SSPIF | CCP1IF | TMR2IF | TMR1IF | 58                         |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE                                          | RCIE        | TXIE         | SSPIE | CCP1IE | TMR2IE | TMR1IE | 58                         |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP                                          | RCIP        | TXIP         | SSPIP | CCP1IP | TMR2IP | TMR1IP | 58                         |

| RCSTA   | SPEN                 | RX9                                           | SREN        | CREN         | ADDEN | FERR   | OERR   | RX9D   | 57                         |

| TXREG   | EUSART T             | EUSART Transmit Register                      |             |              |       |        |        | 57     |                            |

| TXSTA   | CSRC                 | TX9                                           | TXEN        | SYNC         | SENDB | BRGH   | TRMT   | TX9D   | 57                         |

| BAUDCON | ABDOVF               | RCIDL                                         | RXDTP       | TXCKP        | BRG16 | —      | WUE    | ABDEN  | 57                         |

| SPBRGH  | EUSART B             | EUSART Baud Rate Generator Register High Byte |             |              |       |        |        | 57     |                            |

| SPBRG   | EUSART B             | aud Rate G                                    | enerator Re | gister Low E | Byte  |        |        |        | 57                         |

### TABLE 19-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

### 19.2.2 EUSART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 19-6. The data is received on the RX pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

The RXDTP bit (BAUDCON<5>) allows the RX signal to be inverted (polarity reversed). Devices that buffer signals from RS-232 to TTL levels also perform an inversion of the signal (when RS-232 = positive, TTL = 0). Inverting the polarity of the RX pin data by setting the RXDTP bit allows for the use of circuits that provide buffering without inverting the signal.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If the signal at the RX pin is to be inverted, set the RXDTP bit.

- 4. If interrupts are desired, set enable bit, RCIE.

- 5. If 9-bit reception is desired, set bit, RX9.

- 6. Enable the reception by setting bit, CREN.

- Flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCIE, was set.

- 8. Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing enable bit, CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

### 19.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- If the signal at the RX pin is to be inverted, set the RXDTP bit. If the signal from the TX pin is to be inverted, set the TXCKP bit.

- 4. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 5. Set the RX9 bit to enable 9-bit reception.

- 6. Set the ADDEN bit to enable address detect.

- 7. Enable reception by setting the CREN bit.

- 8. The RCIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCIE and GIE bits are set.

- 9. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 10. Read RCREG to determine if the device is being addressed.

- 11. If any error occurred, clear the CREN bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

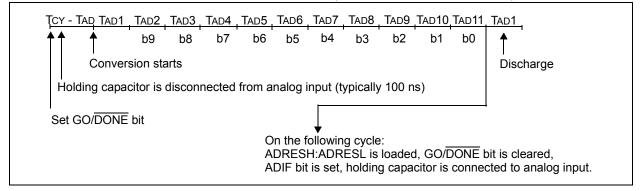

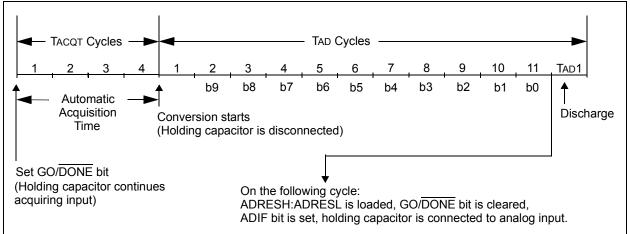

## 20.6 A/D Conversions

Figure 20-4 shows the operation of the A/D converter after the GO/DONE bit has been set and the ACQT<2:0> bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins.

Figure 20-5 shows the operation of the A/D converter after the GO/DONE bit has been set and the ACQT<2:0> bits are set to '010' and selecting a 4 TAD acquisition time before the conversion starts.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

### 20.7 Discharge

The discharge phase is used to initialize the value of the capacitor array. The array is discharged before every sample. This feature helps to optimize the unitygain amplifier, as the circuit always needs to charge the capacitor array, rather than charge/discharge based on previous measure values.

### FIGURE 20-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

## FIGURE 20-5: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

## 27.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                               | 40°C to +125°C       |

|--------------------------------------------------------------|----------------------|

| Storage temperature                                          | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD and MCLR) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                           | -0.3V to +7.5V       |

| Voltage on MCLR with respect to Vss (Note 2)                 | 0V to +13.25V        |

| Total power dissipation (Note 1)                             | 1.0W                 |

| Maximum current out of Vss pin                               |                      |

| Maximum current into VDD pin                                 | 250 mA               |

| Input clamp current, Iικ (Vι < 0 or Vι > VDD)                | ±20 mA               |

| Output clamp current, loк (Vo < 0 or Vo > VDD)               | ±20 mA               |

| Maximum output current sunk by any I/O pin                   | 25 mA                |

| Maximum output current sourced by any I/O pin                | 25 mA                |

| Maximum current sunk by all ports                            | 200 mA               |

| Maximum current sourced by all ports                         | 200 mA               |

- **Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD  $- \sum$  IOH} +  $\sum$  {(VDD - VOH) x IOH} +  $\sum$ (VOL x IOL)

- **2:** Voltage spikes below Vss at the MCLR/VPP/RE3 pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP/ RE3 pin, rather than pulling this pin directly to Vss.

**† NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

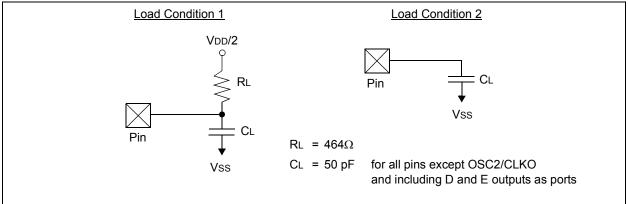

### 27.4.2 TIMING CONDITIONS

The temperature and voltages specified in Table 27-5 apply to all timing specifications unless otherwise noted. Figure 27-5 specifies the load conditions for the timing specifications.

Note: Because of space limitations, the generic terms "PIC18FXXXX" and "PIC18LFXXXX" are used throughout this section to refer to the PIC18F2221/2321/4221/4321 and PIC18LF2221/2321/4221/4321 families of devices specifically and only those devices.

### TABLE 27-5: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

|                    | Standard Operating Conditions (unless otherwise stated)                     |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------|--|--|--|--|

|                    | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |  |  |  |  |

| AC CHARACTERISTICS | $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended                        |  |  |  |  |

| AC CHARACTERISTICS | Operating voltage VDD range as described in DC spec Section 27.1 and        |  |  |  |  |

|                    | Section 27.3.                                                               |  |  |  |  |

|                    | LF parts operate for industrial temperatures only.                          |  |  |  |  |

### FIGURE 27-5: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

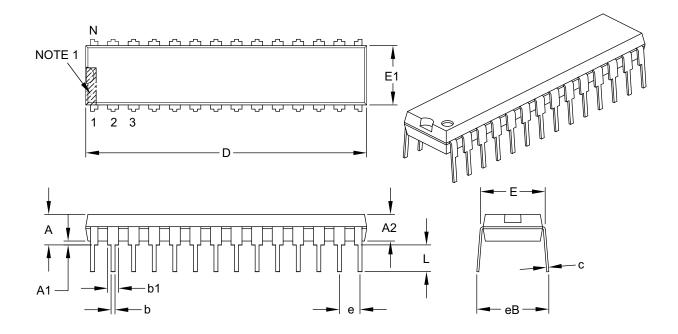

### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units      |       | INCHES   |       |

|----------------------------|------------|-------|----------|-------|

| Dimens                     | ion Limits | MIN   | NOM      | MAX   |

| Number of Pins             | Ν          |       | 28       |       |

| Pitch                      | е          |       | .100 BSC |       |

| Top to Seating Plane       | Α          | -     | -        | .200  |

| Molded Package Thickness   | A2         | .120  | .135     | .150  |

| Base to Seating Plane      | A1         | .015  | -        | -     |

| Shoulder to Shoulder Width | Е          | .290  | .310     | .335  |

| Molded Package Width       | E1         | .240  | .285     | .295  |

| Overall Length             | D          | 1.345 | 1.365    | 1.400 |

| Tip to Seating Plane       | L          | .110  | .130     | .150  |

| Lead Thickness             | С          | .008  | .010     | .015  |

| Upper Lead Width           | b1         | .040  | .050     | .070  |

| Lower Lead Width           | b          | .014  | .018     | .022  |

| Overall Row Spacing §      | eB         | -     | _        | .430  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

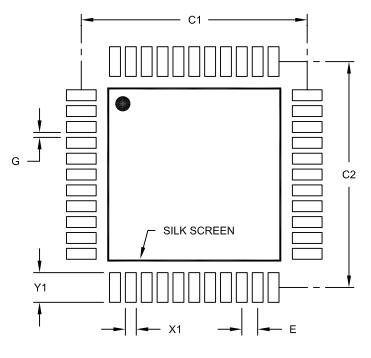

## 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**RECOMMENDED LAND PATTERN**

|                          | MILLIM                    | ETERS    |       |      |

|--------------------------|---------------------------|----------|-------|------|

| Dimension                | Units<br>Dimension Limits |          |       | MAX  |

| Contact Pitch E          |                           | 0.80 BSC |       |      |

| Contact Pad Spacing      | C1                        |          | 11.40 |      |

| Contact Pad Spacing      | C2                        |          | 11.40 |      |

| Contact Pad Width (X44)  | X1                        |          |       | 0.55 |

| Contact Pad Length (X44) | Y1                        |          |       | 1.50 |

| Distance Between Pads    | G                         | 0.25     |       |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076A